Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gp506-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

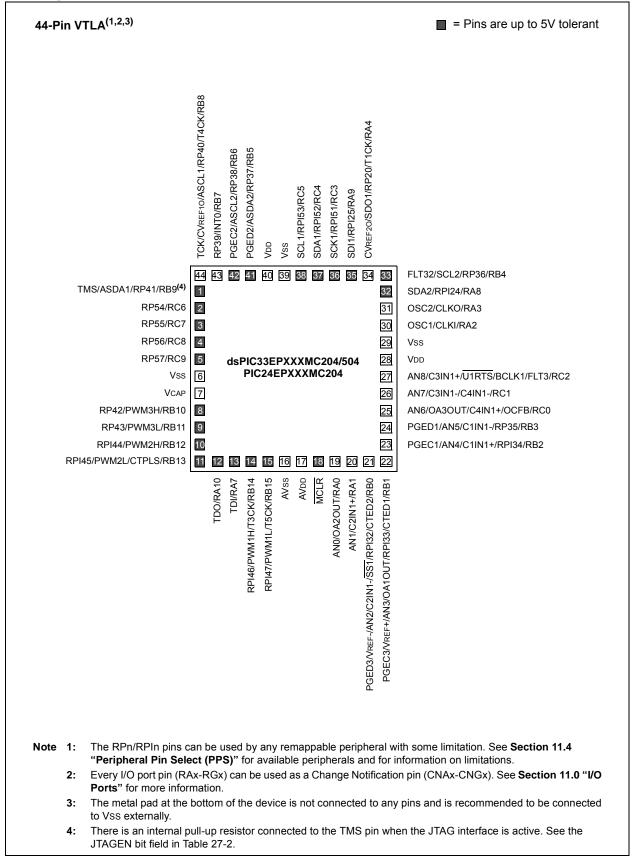

#### Pin Diagrams (Continued)

## TABLE 4-19: SPI1 AND SPI2 REGISTER MAP

| SFR Name | Addr. | Bit 15                                    | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8        | Bit 7       | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------|-------------------------------------------|--------|---------|--------|--------|--------|------------|--------------|-------------|------------|--------|-------|------------|-------|--------|--------|---------------|

| SPI1STAT | 0240  | SPIEN                                     | _      | SPISIDL | _      | _      | 5      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242  | _                                         | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>  |       |        | <1:0>  | 0000          |

| SPI1CON2 | 0244  | FRMEN                                     | SPIFSD | FRMPOL  | _      | _      | -      | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI1BUF  | 0248  |                                           |        |         |        |        |        | SPI1 Tra   | insmit and R | eceive Buff | er Registe | r      |       |            |       |        |        | 0000          |

| SPI2STAT | 0260  | SPIEN                                     | _      | SPISIDL | _      | _      | ŝ      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262  | _                                         | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264  | FRMEN                                     | SPIFSD | FRMPOL  | _      | _      | -      | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI2BUF  | 0268  | SPI2 Transmit and Receive Buffer Register |        |         |        |        |        |            |              |             |            |        | 0000  |            |       |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-34: NVM REGISTER MAP

| File Name | Addr.                     | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7         | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|---------------------------|--------|--------|--------|---------|--------|--------|-------|-------|---------------|-------|-------|-------|-------|-------|-------|-------|---------------|

| NVMCON    | 0728                      | WR     | WREN   | WRERR  | NVMSIDL | _      | _      | —     | _     | _             | _     | _     | —     |       | 0000  |       |       |               |

| NVMADRL   | NVMADRL 072A NVMADR<15:0> |        |        |        |         |        |        |       |       |               |       |       |       |       | 0000  |       |       |               |

| NVMADRH   | 072C                      | _      | _      | _      | _       | -      | _      | _     | _     | NVMADR<23:16> |       |       |       |       |       |       |       | 0000          |

| NVMKEY    | 072E                      |        |        | _      | —       | _      |        | —     | -     | NVMKEY<7:0>   |       |       |       |       |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-35: SYSTEM CONTROL REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8       | Bit 7                      | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|-----------|--------|--------|--------|-----------|-------------|----------------------------|--------|--------|-------|-------|-------|-------|-------|---------------|

| RCON      | 0740  | TRAPR  | IOPUWR | _         | _      | VREGSF | _      | СМ        | VREGS       | EXTR                       | SWR    | SWDTEN | WDTO  | SLEEP | IDLE  | BOR   | POR   | Note 1        |

| OSCCON    | 0742  | _      | 0      | COSC<2:0> |        | —      |        | NOSC<2:0> |             | CLKLOCK                    | IOLOCK | LOCK   | _     | CF    | _     | _     | OSWEN | Note 2        |

| CLKDIV    | 0744  | ROI    | [      | OOZE<2:0> |        | DOZEN  | F      | RCDIV<2:0 | >           | PLLPOST<1:0> — PLLPRE<4:0> |        |        |       |       |       | 0030  |       |               |

| PLLFBD    | 0746  | _      | _      | _         | _      | —      | _      | _         | PLLDIV<8:0> |                            |        |        |       | 0030  |       |       |       |               |

| OSCTUN    | 0748  | _      | _      | _         | _      | —      | _      | _         | TUN<5:0>    |                            |        |        |       | 0000  |       |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration Fuses.

#### TABLE 4-36: REFERENCE CLOCK REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10     | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| REFOCON   | 074E  | ROON   | —      | ROSSLP | ROSEL  |        | RODIV<3:0> |       |       | _     | _     | —     | _     | _     | —     | _     | -     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

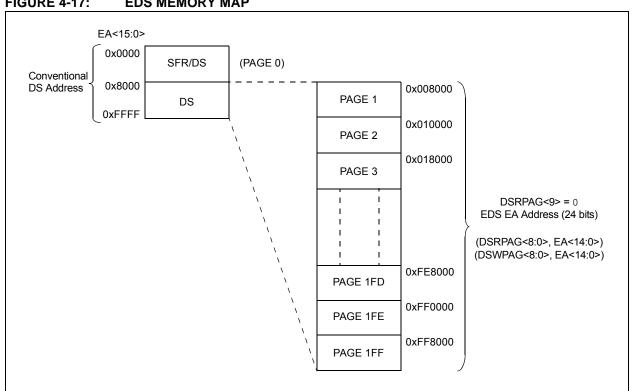

#### 4.4.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-17.

For more information on the PSV page access using Data Space Page registers, refer to the "**Program Space Visibility from Data Space**" section in "**Program Memory**" (DS70613) of the "*dsPIC33/ PIC24 Family Reference Manual*".

#### FIGURE 4-17: EDS MEMORY MAP

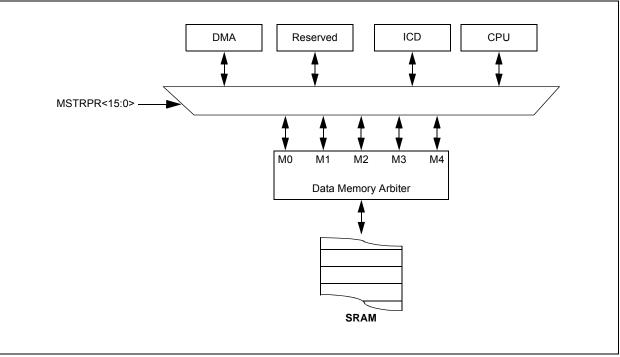

# 4.4.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below

### FIGURE 4-18: ARBITER ARCHITECTURE

that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-62.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

| TABLE 4-62: | DATA MEMORY BUS  |

|-------------|------------------|

|             | ARBITER PRIORITY |

| Drierity     | MSTRPR<15:0 | > Bit Setting <sup>(1)</sup> |

|--------------|-------------|------------------------------|

| Priority     | 0x0000      | 0x0020                       |

| M0 (highest) | CPU         | DMA                          |

| M1           | Reserved    | CPU                          |

| M2           | Reserved    | Reserved                     |

| M3           | DMA         | Reserved                     |

| M4 (lowest)  | ICD         | ICD                          |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

| R/W-0                | R/W-0                   | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|-------------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                      | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                         |                      |       |       |       |       | bit 8 |

|                      |                         |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA    | Ν     | OV    | Z     | С     |

| bit 7                |                         |                      |       |       |       |       | bit 0 |

|                      |                         |                      |       |       |       |       |       |

## REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/S-0                                          | U-0                                                                                              | U-0                            | U-0                   | U-0              | U-0              | U-0             | U-0     |  |  |  |  |  |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------|-----------------------|------------------|------------------|-----------------|---------|--|--|--|--|--|--|--|

| FORCE <sup>(1)</sup>                           |                                                                                                  | _                              | _                     | —                |                  | _               |         |  |  |  |  |  |  |  |

| bit 15                                         |                                                                                                  |                                |                       |                  |                  |                 | bit 8   |  |  |  |  |  |  |  |

|                                                |                                                                                                  |                                |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

| R/W-0                                          | R/W-0                                                                                            | R/W-0                          | R/W-0                 | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |  |  |  |

| IRQSEL7                                        | IRQSEL6                                                                                          | IRQSEL5                        | IRQSEL4               | IRQSEL3          | IRQSEL2          | IRQSEL1         | IRQSEL0 |  |  |  |  |  |  |  |

| bit 7                                          |                                                                                                  |                                |                       |                  |                  |                 | bit     |  |  |  |  |  |  |  |

| Legend:                                        |                                                                                                  | S = Settable b                 | oit                   |                  |                  |                 |         |  |  |  |  |  |  |  |

| R = Readable                                   | bit                                                                                              | W = Writable                   | bit                   | U = Unimpler     | mented bit, read | d as '0'        |         |  |  |  |  |  |  |  |

| -n = Value at F                                | POR                                                                                              | '1' = Bit is set               |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |  |  |  |  |  |  |  |

|                                                |                                                                                                  |                                |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

| bit 15                                         | FORCE: Force                                                                                     | e DMA Transfe                  | er bit <sup>(1)</sup> |                  |                  |                 |         |  |  |  |  |  |  |  |

| 1 = Forces a single DMA transfer (Manual mode) |                                                                                                  |                                |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                | 0 = Automatic DMA transfer initiation by DMA request                                             |                                |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

| bit 14-8                                       | Unimplemen                                                                                       | ted: Read as 'd                | )'                    |                  |                  |                 |         |  |  |  |  |  |  |  |

| bit 7-0                                        | IRQSEL<7:0>: DMA Peripheral IRQ Number Select bits                                               |                                |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                | 01000110 = ECAN1 – TX Data Request <sup>(2)</sup>                                                |                                |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                | 00100110 = IC4 – Input Capture 4                                                                 |                                |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                | 00100101 <b>= IC3 – Input Capture 3</b><br>00100010 <b>= ECAN1 – RX Data Ready<sup>(2)</sup></b> |                                |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                |                                                                                                  | SPI2 Transfer I                | -                     |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                |                                                                                                  | UART2TX – UA                   |                       | itter            |                  |                 |         |  |  |  |  |  |  |  |

|                                                |                                                                                                  | UART2RX – U                    |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                |                                                                                                  | TMR5 – Timer5                  |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                | 00011011 =                                                                                       | TMR4 – Timer4                  | 1                     |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                |                                                                                                  | OC4 – Output (                 |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                |                                                                                                  | OC3 – Output (                 |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                |                                                                                                  | ADC1 – ADC1                    |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                |                                                                                                  | UART1TX – UA                   |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                |                                                                                                  | UART1RX – U/<br>SPI1 – Transfe |                       | er               |                  |                 |         |  |  |  |  |  |  |  |

|                                                |                                                                                                  | TMR3 – Timer3                  |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                |                                                                                                  | TMR2 – Timer2                  |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                |                                                                                                  | OC2 – Output (                 |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                |                                                                                                  | IC2 – Input Ca                 |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                | 0000010 =                                                                                        | OC1 – Output (                 | Compare 1             |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                |                                                                                                  | IC1 – Input Ca                 |                       |                  |                  |                 |         |  |  |  |  |  |  |  |

|                                                | 00000000 =                                                                                       | INT0 – Externa                 | I Interrupt 0         |                  |                  |                 |         |  |  |  |  |  |  |  |

#### REGISTER 8-2: DMAXREQ: DMA CHANNEL x IRQ SELECT REGISTER

- **Note 1:** The FORCE bit cannot be cleared by user software. The FORCE bit is cleared by hardware when the forced DMA transfer is complete or the channel is disabled (CHEN = 0).

- 2: This selection is available in dsPIC33EPXXXGP/MC50X devices only.

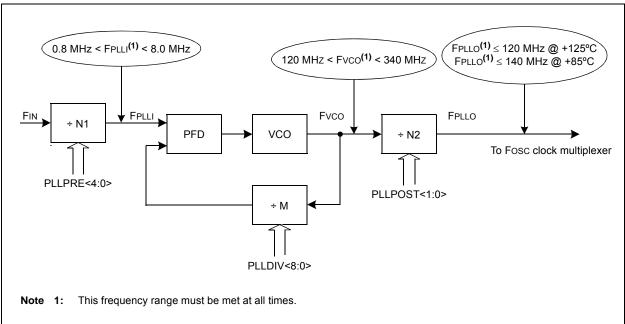

## 9.1 CPU Clocking System

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices provides six system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with Phase Locked Loop (PLL)

- · FRC Oscillator with Postscaler

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

Instruction execution speed or device operating frequency, FCY, is given by Equation 9-1.

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

FCY = Fosc/2

Figure 9-2 is a block diagram of the PLL module.

Equation 9-2 provides the relationship between input frequency (FIN) and output frequency (FPLLO). In clock modes S1 and S3, when the PLL output is selected, FOSC = FPLLO.

Equation 9-3 provides the relationship between input frequency (FIN) and VCO frequency (FVCO).

#### EQUATION 9-2: FPLLO CALCULATION

$$FPLLO = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2) \times 2(PLLPOST + 1)}\right)$$

Where:

N1 = PLLPRE + 2 $N2 = 2 \times (PLLPOST + 1)$

M = PLLDIV + 2

#### EQUATION 9-3: Fvco CALCULATION

$$Fvco = FIN \times \left(\frac{M}{N1}\right) = FIN \times \left(\frac{(PLLDIV+2)}{(PLLPRE+2)}\right)$$

DS70000657H-page 154

#### © 2011-2013 Microchip Technology Inc.

## FIGURE 9-2: PLL BLOCK DIAGRAM

#### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- $\label{eq:constraint} \textbf{2:} \quad \text{This bit is cleared when the ROI bit is set and an interrupt occurs.}$

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0        | R/W-0                               | R/W-0 | R/W-0                              | R/W-0         | R/W-0           | R/W-0 |  |  |  |

|-----------------|------------|-------------------------------------|-------|------------------------------------|---------------|-----------------|-------|--|--|--|

| —               | —          |                                     |       | RP57                               | R<5:0>        |                 |       |  |  |  |

| bit 15          |            |                                     |       |                                    |               |                 | bit 8 |  |  |  |

|                 |            |                                     |       |                                    |               |                 |       |  |  |  |

| U-0             | U-0        | R/W-0                               | R/W-0 | R/W-0                              | R/W-0         | R/W-0           | R/W-0 |  |  |  |

| _               | —          |                                     |       | RP56                               | R<5:0>        |                 |       |  |  |  |

| bit 7           |            |                                     |       |                                    |               |                 | bit 0 |  |  |  |

|                 |            |                                     |       |                                    |               |                 |       |  |  |  |

| Legend:         |            |                                     |       |                                    |               |                 |       |  |  |  |

| R = Readable I  | bit        | W = Writable                        | bit   | U = Unimplemented bit, read as '0' |               |                 |       |  |  |  |

| -n = Value at P | OR         | '1' = Bit is set                    | :     | '0' = Bit is clea                  | ared          | x = Bit is unkr | iown  |  |  |  |

|                 |            |                                     |       |                                    |               |                 |       |  |  |  |

| bit 15-14       | Unimplemen | ted: Read as '                      | 0'    |                                    |               |                 |       |  |  |  |

| bit 13-8        |            | : Peripheral Ou<br>-3 for periphera |       | is Assigned to<br>mbers)           | RP57 Output F | Pin bits        |       |  |  |  |

| bit 7-6         | Unimplemen | ted: Read as '                      | 0'    |                                    |               |                 |       |  |  |  |

#### REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| (see Table 11-3 for peripheral function numbers) |

|--------------------------------------------------|

|                                                  |

#### REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP97  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | —   | —   |     | _   |     |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-0 Unimplemented: Read as '0'

bit 5-0

NOTES:

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| Legend:<br>R = Readable bi | t     | W = Writable bit |       | U = Unimpler | nented bit, reac | l as '0' |       |

|----------------------------|-------|------------------|-------|--------------|------------------|----------|-------|

| bit 7                      |       |                  |       |              |                  |          | bit 0 |

|                            |       |                  | PTPE  | R<7:0>       |                  |          |       |

| R/W-1                      | R/W-1 | R/W-1            | R/W-1 | R/W-1        | R/W-0            | R/W-0    | R/W-0 |

| bit 15                     |       |                  |       |              |                  |          | bit 8 |

|                            |       |                  | PTPE  | R<15:8>      |                  |          |       |

| R/W-1                      | R/W-1 | R/W-1            | R/W-1 | R/W-1        | R/W-1            | R/W-1    | R/W-1 |

'0' = Bit is cleared

x = Bit is unknown

#### REGISTER 16-3: PTPER: PWMx PRIMARY MASTER TIME BASE PERIOD REGISTER

bit 15-0 **PTPER<15:0>:** Primary Master Time Base (PMTMR) Period Value bits

'1' = Bit is set

#### REGISTER 16-4: SEVTCMP: PWMx PRIMARY SPECIAL EVENT COMPARE REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0                                         | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

|-----------------|-------|------------------|-----------------------------------------------|--------------|-----------------|-----------|-------|

|                 |       |                  | SEVTC                                         | MP<15:8>     |                 |           |       |

| bit 15          |       |                  |                                               |              |                 |           | bit 8 |

|                 |       |                  |                                               |              |                 |           |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0                                         | R/W-0        | R/W-0           | R/W-0     | R/W-0 |

|                 |       |                  | SEVT                                          | CMP<7:0>     |                 |           |       |

| bit 7           |       |                  |                                               |              |                 |           | bit 0 |

|                 |       |                  |                                               |              |                 |           |       |

| Legend:         |       |                  |                                               |              |                 |           |       |

| R = Readable    | bit   | W = Writable bi  | t                                             | U = Unimplem | nented bit, rea | id as '0' |       |

| -n = Value at P | OR    | '1' = Bit is set | s set '0' = Bit is cleared x = Bit is unknown |              |                 | nown      |       |

bit 15-0 SEVTCMP<15:0>: Special Event Compare Count Value bits

-n = Value at POR

| U-0       U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0          BCH <sup>(1)</sup> BCL <sup>(1)</sup> BPHH       BPHL       BPLH       BPLH         bit 7        B       Readable bit       U = Unimplemented bit, read as '0'           n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Reading-Edge Blanking ignores rising edge of PWMxH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0         | R/W-0                                                                                                                                                                                     | R/W-0            | R/W-0           | R/W-0             | R/W-0            | U-0             | U-0          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|-------------------|------------------|-----------------|--------------|

| U-0       U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0          BCH <sup>(1)</sup> BCL <sup>(1)</sup> BPHH       BPHL       BPLH       BPLH         bit 7        B       Readable bit       U = Unimplemented bit, read as '0'           n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Reading-Edge Blanking ignores rising edge of PWMxH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PHR           | PHF                                                                                                                                                                                       | PLR              | PLF             | FLTLEBEN          | CLLEBEN          | _               |              |

| —         BCH <sup>(1)</sup> BCL <sup>(1)</sup> BPHH         BPHL         BPLH         BPLH         BPLH           bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15        |                                                                                                                                                                                           |                  |                 |                   |                  |                 | bit          |

| —         BCH <sup>(1)</sup> BCL <sup>(1)</sup> BPHH         BPHL         BPLH         BPLH         BPLH           bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U-0           | U-0                                                                                                                                                                                       | R/W-0            | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0        |

| bit 7 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 PHR: PWMxH Rising Edge Trigger Enable bit 1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter 0 = Leading-Edge Blanking ignores rising edge of PWMxH bit 1 PHF: PWMxH Raling Edge Trigger Enable bit 1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter 0 = Leading-Edge Blanking ignores falling edge of PWMxH bit 1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter 0 = Leading-Edge Blanking ignores falling edge of PWMxH bit 1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter 0 = Leading-Edge Blanking ignores rising edge of PWMxL bit 1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter 0 = Leading-Edge Blanking ignores rising edge of PWMxL bit 1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter 0 = Leading-Edge Blanking is applied to selected Fault input 1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter 0 = Leading-Edge Blanking is applied to selected Fault input 0 = Leading-Edge Blanking is applied to selected Fault input 0 = Leading-Edge Blanking is applied to selected Fault input 0 = Leading-Edge Blanking is applied to selected Crurent-limit input 0 = Leading-Edge Blanking is not applied to selected crurent-limit input 0 = Leading-Edge Blanking is not applied to selected crurent-limit input 0 = Leading-Edge Blanking is not applied to selected crurent-limit input 0 = Leading-Edge Blanking is not applied to selected Crurent-limit input 0 = Leading-Edge Blanking Signal High Enable bit 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high 0 = No blanking when selected blanking signal is low 0 = No blanking when selected blanking signal is low 0 = No blanking when selected blanking signal is low 0 = No blanking when selected blanking signal is low 0 = No blanking when PWMxH upt Enable bit 1 = Stat | _             | _                                                                                                                                                                                         |                  |                 | 1                 | r                | 1               | BPLL         |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PVMxH Rising Edge Trigger Enable bit       1 = Rising edge of PVMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PVMxH         bit 14       PHF: PVMxH Falling Edge Trigger Enable bit       1 = Falling edge of PVMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores falling edge of PVMxH         bit 13       PLR: PVMxL Rising Edge Trigger Enable bit       1 = Rising edge of PVMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PVMxL         bit 12       PLF: PVMxL Falling Edge Trigger Enable bit       1 = Falling edge of PVMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PVMxL         bit 11       FLTEBEN: Fault Input Leading-Edge Blanking Enable bit       1 = Falling edge of PVMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking is not applied to selected Fault input         bit 10       CLLEBEN: Current-Limit Leading-Edge Blanking Enable bit       1 = Leading-Edge Blanking is not applied to selected current-limit input         bit 5       BCH: Blanking in Selected Blanking Signal High Enable bit       1 = Leading-Edge Blanking is not applied to selected current-limit input         bit 6       BCL: Blanking in Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | bit 7         |                                                                                                                                                                                           |                  |                 |                   |                  |                 | bit          |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PVMxH Rising Edge Trigger Enable bit       1 = Rising edge of PVMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PVMxH         bit 14       PHF: PVMxH Falling Edge Trigger Enable bit       1 = Falling edge of PVMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores falling edge of PVMxH         bit 13       PLR: PVMxL Rising Edge Trigger Enable bit       1 = Rising edge of PVMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PVMxL         bit 12       PLF: PVMxL Falling Edge Trigger Enable bit       1 = Falling edge of PVMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PVMxL         bit 11       FLTEBEN: Fault Input Leading-Edge Blanking Enable bit       1 = Falling edge of PVMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking is not applied to selected Fault input         bit 10       CLLEBEN: Current-Limit Leading-Edge Blanking Enable bit       1 = Leading-Edge Blanking is not applied to selected current-limit input         bit 5       BCH: Blanking in Selected Blanking Signal High Enable bit       1 = Leading-Edge Blanking is not applied to selected current-limit input         bit 6       BCL: Blanking in Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Legend:       |                                                                                                                                                                                           |                  |                 |                   |                  |                 |              |

| <ul> <li>PHR: PWMxH Rising Edge Trigger Enable bit         <ul> <li>I = Rising edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>I = Raiding-Edge Blanking ignores rising edge of PWMxH</li> </ul> </li> <li>PHF: PWMxH Falling Edge Trigger Enable bit         <ul> <li>I = Falling edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>I = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>I = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>I = Rising edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>I = cading-Edge Blanking ignores rising edge of PWMxL</li> </ul> </li> <li>PLF: PWMxL Falling Edge Trigger Enable bit         <ul> <li>I = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>I = Leading-Edge Blanking ignores raling edge of PWMxL</li> </ul> </li> <li>DE: PWMxL Falling Edge Trigger Enable bit         <ul> <li>I = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>I = Leading-Edge Blanking is applied to selected Fault input</li> <li>I = Leading-Edge Blanking is not applied to selected Fault input</li> <li>I = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>I = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>I = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>I = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>I = Leading-Edge Blanking is not applied to selected blanking signal is high</li> <li>I = State blanking of current-limit and/or Fault input signals) when selected blanking signal is high</li> <li>I = State blanking (of current-limit and/or Fault input signals) when selected</li></ul></li></ul>                                                                                                                                                                                                                                                                      | -             | e bit                                                                                                                                                                                     | W = Writable     | bit             | U = Unimpler      | mented bit, read | as '0'          |              |

| 1 = Rising edge of PWMxH will rigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores rising edge of PWMxH         bit 14       PHF: PWMxH Falling Edge Trigger Enable bit         1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxH         bit 13       PLR: PWMxL Rising Edge Trigger Enable bit         1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores rising edge of PWMxL         bit 12       PLF: PWMxL Falling Edge Trigger Enable bit         1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 12       PLF: PWMxL Falling Edge Trigger Enable bit         1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking is applied to selected Fault input         0 = Leading-Edge Blanking is applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking Signal High Enable bit <sup>(1)</sup> 1 = Leading-Edge Blanking Signal Low Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high         bit 4       BCL: Blanking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -n = Value at | POR                                                                                                                                                                                       | '1' = Bit is set | :               | '0' = Bit is cle  | ared             | x = Bit is unkr | nown         |

| <ul> <li>1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxH</li> <li>bit 13 PLR: PWMxL Rising Edge Trigger Enable bit</li> <li>1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>bit 12 PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxL</li> <li>bit 12 PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxL</li> <li>bit 11 FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit</li> <li>1 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking Signal High Enable bit</li> <li>1 = State blanking (or current-limit and/or Fault input signals) when selected blanking signal is high</li> <li>bit 4 BCL: Blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>bit 3 BPHH: Blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>No blanking when PWMxH output is high</li> <li>bit 2 BPHL: Blanking in PWMxH</li></ul>                                                                                                   | bit 15        | 1 = Rising ed                                                                                                                                                                             | ge of PWMxH      | will trigger Le | ading-Edge Bla    |                  |                 |              |

| <ul> <li>1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>bit 12 PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxL</li> <li>bit 11 FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit</li> <li>1 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when selected blanking signal is high</li> <li>bit 4 BCL: Blanking in Selected Blanking Signal Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when Selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>bit 3 BPHH: Blanking in PWMxH dutput is high</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 =</li></ul>                                                                                               | bit 14        | 1 = Falling ed                                                                                                                                                                            | lge of PWMxH     | will trigger Le | eading-Edge Bla   | 0                |                 |              |

| 1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit         1 = Leading-Edge Blanking is applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = No blanking in Selected Blanking Signal High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         bit 3       BPHH: Blanking in PWMxH High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high         bit 2       BPHL: Blanking in PWMxH Low Enable bit         1 = State blanking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 13        | 1 = Rising ed                                                                                                                                                                             | ge of PWMxL      | will trigger Le | ading-Edge Bla    |                  |                 |              |

| <ul> <li>1 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>1 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking Signal High Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL dutput is high</li> <li>0 = No blanking when PWMxL cutput is high</li> <li>0 = No blanking when PWMxL cutput is high</li> <li>0 = No blanking when PWMxL cutput is high</li> </ul>                                                                                                  | bit 12        | <b>PLF:</b> PWMxL Falling Edge Trigger Enable bit<br>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter                                                                 |                  |                 |                   |                  |                 |              |

| <ul> <li>1 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>bit 9-6</li> <li>Unimplemented: Read as '0'</li> <li>BCH: Blanking in Selected Blanking Signal High Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is hig</li> <li>0 = No blanking when selected blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking in Current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 2</li> <li>BPHL: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>bit 0</li> <li>BPLL: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking (of curr</li></ul>                                                                                             | bit 11        | 1 = Leading-E                                                                                                                                                                             | Edge Blanking    | is applied to   | selected Fault in | nput             |                 |              |

| bit 5       BCH: Blanking in Selected Blanking Signal High Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high         bit 4       BCL: Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         bit 4       BCL: Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         bit 3       BPHH: Blanking in PWMxH High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high         0 = No blanking when PWMxH output is high         bit 2       BPHL: Blanking in PWMxH Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low         0 = No blanking when PWMxH output is low         bit 1       BPLH: Blanking in PWMxH tigh Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         bit 1       BPLH: Blanking in PWMxL High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         bit 0       BPLL: Blanking in PWMxL Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         bit 0<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 10        | 1 = Leading-E                                                                                                                                                                             | Edge Blanking    | is applied to   | selected current  | t-limit input    |                 |              |

| <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high</li> <li>bit 4 BCL: Blanking in Selected Blanking Signal Low Enable bit<sup>(1)</sup> <ol> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking when PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> </ol> </li> <li>bit 2 BPHL: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1 BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>bit 1 BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>bit 0 BPLL: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>bit 0 BPLL: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 9-6       | Unimplemen                                                                                                                                                                                | ted: Read as '   | 0'              |                   |                  |                 |              |