Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 512KB (170K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 24K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512gp506t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

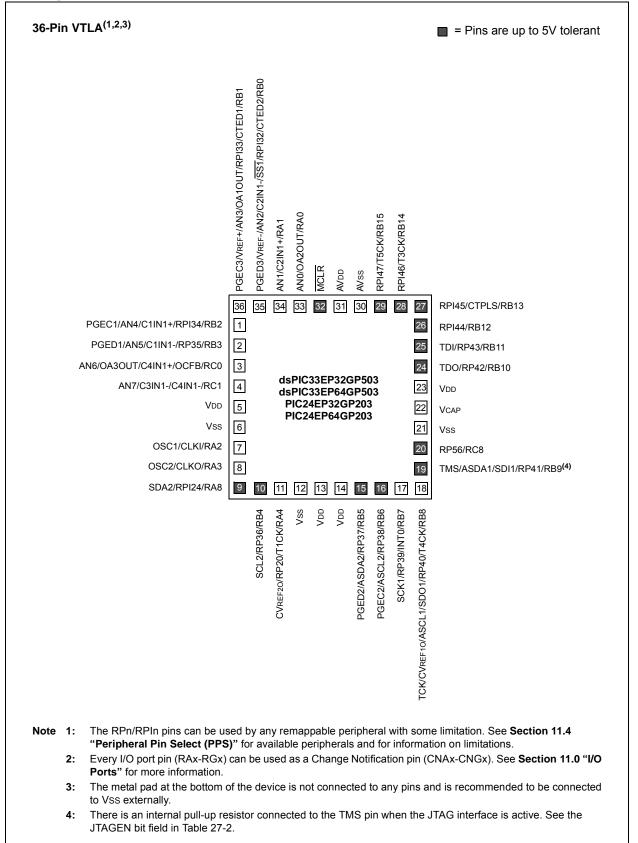

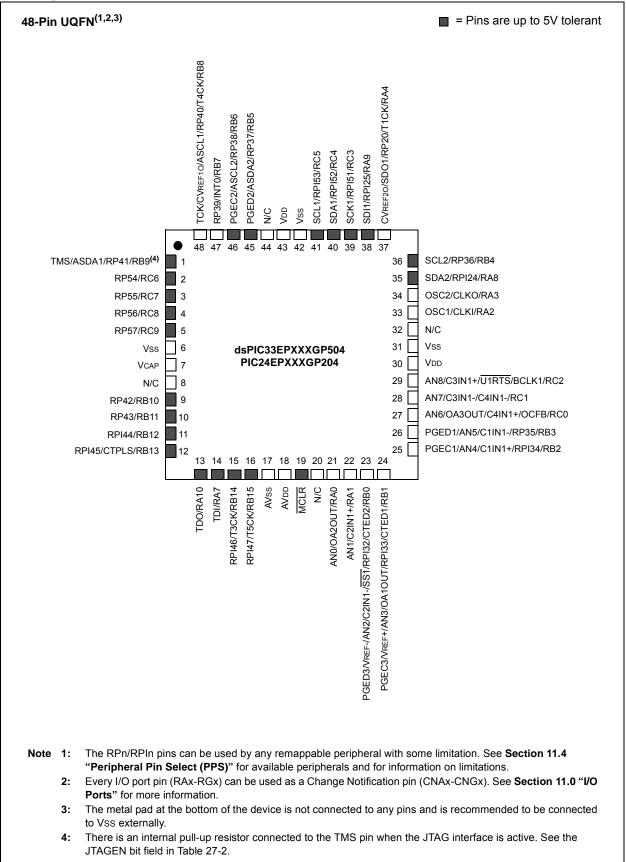

#### **Pin Diagrams (Continued)**

#### Pin Diagrams (Continued)

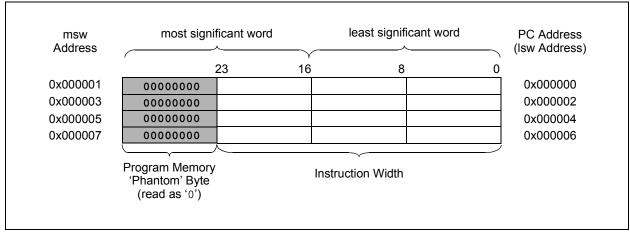

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-6).

Program memory addresses are always word-aligned on the lower word and addresses are incremented, or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

#### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices reserve the addresses between 0x000000 and 0x000200 for hardcoded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-6: PROGRAM MEMORY ORGANIZATION

|                                               | Vector | IRQ        |                   | Inte     | errupt Bit L | ocation     |

|-----------------------------------------------|--------|------------|-------------------|----------|--------------|-------------|

| Interrupt Source                              | #      | #          | IVT Address       | Flag     | Enable       | Priority    |

|                                               | High   | est Natura | I Order Priority  |          |              |             |

| INT0 – External Interrupt 0                   | 8      | 0          | 0x000014          | IFS0<0>  | IEC0<0>      | IPC0<2:0>   |

| IC1 – Input Capture 1                         | 9      | 1          | 0x000016          | IFS0<1>  | IEC0<1>      | IPC0<6:4>   |

| OC1 – Output Compare 1                        | 10     | 2          | 0x000018          | IFS0<2>  | IEC0<2>      | IPC0<10:8>  |

| T1 – Timer1                                   | 11     | 3          | 0x00001A          | IFS0<3>  | IEC0<3>      | IPC0<14:12> |

| DMA0 – DMA Channel 0                          | 12     | 4          | 0x00001C          | IFS0<4>  | IEC0<4>      | IPC1<2:0>   |

| IC2 – Input Capture 2                         | 13     | 5          | 0x00001E          | IFS0<5>  | IEC0<5>      | IPC1<6:4>   |

| OC2 – Output Compare 2                        | 14     | 6          | 0x000020          | IFS0<6>  | IEC0<6>      | IPC1<10:8>  |

| T2 – Timer2                                   | 15     | 7          | 0x000022          | IFS0<7>  | IEC0<7>      | IPC1<14:12> |

| T3 – Timer3                                   | 16     | 8          | 0x000024          | IFS0<8>  | IEC0<8>      | IPC2<2:0>   |

| SPI1E – SPI1 Error                            | 17     | 9          | 0x000026          | IFS0<9>  | IEC0<9>      | IPC2<6:4>   |

| SPI1 – SPI1 Transfer Done                     | 18     | 10         | 0x000028          | IFS0<10> | IEC0<10>     | IPC2<10:8>  |

| U1RX – UART1 Receiver                         | 19     | 11         | 0x00002A          | IFS0<11> | IEC0<11>     | IPC2<14:12> |

| U1TX – UART1 Transmitter                      | 20     | 12         | 0x00002C          | IFS0<12> | IEC0<12>     | IPC3<2:0>   |

| AD1 – ADC1 Convert Done                       | 21     | 13         | 0x00002E          | IFS0<13> | IEC0<13>     | IPC3<6:4>   |

| DMA1 – DMA Channel 1                          | 22     | 14         | 0x000030          | IFS0<14> | IEC0<14>     | IPC3<10:8>  |

| Reserved                                      | 23     | 15         | 0x000032          |          |              | _           |

| SI2C1 – I2C1 Slave Event                      | 24     | 16         | 0x000034          | IFS1<0>  | IEC1<0>      | IPC4<2:0>   |

| MI2C1 – I2C1 Master Event                     | 25     | 17         | 0x000036          | IFS1<1>  | IEC1<1>      | IPC4<6:4>   |

| CM – Comparator Combined Event                | 26     | 18         | 0x000038          | IFS1<2>  | IEC1<2>      | IPC4<10:8>  |

| CN – Input Change Interrupt                   | 27     | 19         | 0x00003A          | IFS1<3>  | IEC1<3>      | IPC4<14:12> |

| INT1 – External Interrupt 1                   | 28     | 20         | 0x00003C          | IFS1<4>  | IEC1<4>      | IPC5<2:0>   |

| Reserved                                      | 29-31  | 21-23      | 0x00003E-0x000042 |          |              | _           |

| DMA2 – DMA Channel 2                          | 32     | 24         | 0x000044          | IFS1<8>  | IEC1<8>      | IPC6<2:0>   |

| OC3 – Output Compare 3                        | 33     | 25         | 0x000046          | IFS1<9>  | IEC1<9>      | IPC6<6:4>   |

| OC4 – Output Compare 4                        | 34     | 26         | 0x000048          | IFS1<10> | IEC1<10>     | IPC6<10:8>  |

| T4 – Timer4                                   | 35     | 27         | 0x00004A          | IFS1<11> | IEC1<11>     | IPC6<14:12> |

| T5 – Timer5                                   | 36     | 28         | 0x00004C          | IFS1<12> | IEC1<12>     | IPC7<2:0>   |

| INT2 – External Interrupt 2                   | 37     | 29         | 0x00004E          | IFS1<13> | IEC1<13>     | IPC7<6:4>   |

| U2RX – UART2 Receiver                         | 38     | 30         | 0x000050          | IFS1<14> | IEC1<14>     | IPC7<10:8>  |

| U2TX – UART2 Transmitter                      | 39     | 31         | 0x000052          | IFS1<15> | IEC1<15>     | IPC7<14:12> |

| SPI2E – SPI2 Error                            | 40     | 32         | 0x000054          | IFS2<0>  | IEC2<0>      | IPC8<2:0>   |

| SPI2 – SPI2 Transfer Done                     | 41     | 33         | 0x000056          | IFS2<1>  | IEC2<1>      | IPC8<6:4>   |

| C1RX – CAN1 RX Data Ready <sup>(1)</sup>      | 42     | 34         | 0x000058          | IFS2<2>  | IEC2<2>      | IPC8<10:8>  |

| C1 – CAN1 Event <sup>(1)</sup>                | 43     | 35         | 0x00005A          | IFS2<3>  | IEC2<3>      | IPC8<14:12> |

| DMA3 – DMA Channel 3                          | 44     | 36         | 0x00005C          | IFS2<4>  | IEC2<4>      | IPC9<2:0>   |

| IC3 – Input Capture 3                         | 45     | 37         | 0x00005E          | IFS2<5>  | IEC2<5>      | IPC9<6:4>   |

| IC4 – Input Capture 4                         | 46     | 38         | 0x000060          | IFS2<6>  | IEC2<6>      | IPC9<10:8>  |

| Reserved                                      | 47-56  | 39-48      | 0x000062-0x000074 | —        | —            | —           |

| SI2C2 – I2C2 Slave Event                      | 57     | 49         | 0x000076          | IFS3<1>  | IEC3<1>      | IPC12<6:4>  |

| MI2C2 – I2C2 Master Event                     | 58     | 50         | 0x000078          | IFS3<2>  | IEC3<2>      | IPC12<10:8> |

| Reserved                                      | 59-64  | 51-56      | 0x00007A-0x000084 |          | _            |             |

| PSEM – PWM Special Event Match <sup>(2)</sup> | 65     | 57         | 0x000086          | IFS3<9>  | IEC3<9>      | IPC14<6:4>  |

#### TABLE 7-1: INTERRUPT VECTOR DETAILS

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

| U-0          | U-0          | U-0                                    | U-0           | U-0                | U-0              | U-0             | U-0    |

|--------------|--------------|----------------------------------------|---------------|--------------------|------------------|-----------------|--------|

| _            | —            | —                                      | —             | —                  | —                | —               | —      |

| bit 15       |              |                                        |               |                    |                  |                 | bit 8  |

|              |              |                                        |               |                    |                  |                 |        |

| U-0          | U-0          | U-0                                    | U-0           | R-0                | R-0              | R-0             | R-0    |

|              |              | <u> </u>                               | _             | PWCOL3             | PWCOL2           | PWCOL1          | PWCOL0 |

| bit 7        |              |                                        |               |                    |                  |                 | bit 0  |

|              |              |                                        |               |                    |                  |                 |        |

| Legend:      |              |                                        |               |                    |                  |                 |        |

| R = Readab   | le bit       | W = Writable                           | bit           | U = Unimpler       | mented bit, read | as '0'          |        |

| -n = Value a | t POR        | '1' = Bit is set                       |               | '0' = Bit is cle   | ared             | x = Bit is unkr | nown   |

|              |              |                                        |               |                    |                  |                 |        |

| bit 15-4     | Unimplemen   | ted: Read as '                         | 0'            |                    |                  |                 |        |

| bit 3        | PWCOL3: DI   | MA Channel 3 F                         | Peripheral Wi | rite Collision Fla | ag bit           |                 |        |

|              |              | lision is detecte                      |               |                    |                  |                 |        |

|              |              | collision is dete                      |               |                    |                  |                 |        |

| bit 2        |              |                                        | •             | rite Collision Fla | ag bit           |                 |        |

|              |              | lision is detecte<br>collision is dete |               |                    |                  |                 |        |

| bit 1        |              |                                        |               | rite Collision Fla | a hit            |                 |        |

| DILI         |              | lision is detecte                      | •             |                    |                  |                 |        |

|              |              | collision is dete                      |               |                    |                  |                 |        |

| bit 0        | PWCOL0: DI   | MA Channel 0 F                         | Peripheral Wi | rite Collision Fla | ag bit           |                 |        |

|              |              | lision is detecte                      | •             | -                  | <b>č</b>         |                 |        |

|              | 0 = No write | collision is dete                      | ected         |                    |                  |                 |        |

|              |              |                                        |               |                    |                  |                 |        |

### REGISTER 8-11: DMAPWC: DMA PERIPHERAL WRITE COLLISION STATUS REGISTER

# **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 4 Unimplemented: Read as '0'

- bit 3 **CF:** Clock Fail Detect bit<sup>(3)</sup>

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **"Oscillator"** (DS70580) in the *"dsPIC33/ PIC24 Family Reference Manual"* (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

| U-0     | U-0 | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

|---------|-----|-------|-------|-------|-------|-------|-------|

| —       | —   | —     | —     | —     | —     | —     | —     |

| bit 15  |     |       |       |       |       |       | bit 8 |

|         |     |       |       |       |       |       |       |

| U-0     | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —       | —   | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7   |     |       |       |       |       |       | bit 0 |

|         |     |       |       |       |       |       |       |

| Logondi |     |       |       |       |       |       |       |

#### REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **TUN<5:0>:** FRC Oscillator Tuning bits 011111 = Maximum frequency deviation of 1.453% (7.477 MHz) 011110 = Center frequency + 1.406% (7.474 MHz) •••• 000001 = Center frequency + 0.047% (7.373 MHz) 000000 = Center frequency (7.37 MHz nominal) 111111 = Center frequency - 0.047% (7.367 MHz) ••• 100001 = Center frequency - 1.453% (7.263 MHz) 100000 = Minimum frequency deviation of -1.5% (7.259 MHz)

#### REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7- | 6  | DTC<1:0>: Dead-Time Control bits                                                                                                    |

|--------|----|-------------------------------------------------------------------------------------------------------------------------------------|

|        |    | 11 = Dead-Time Compensation mode                                                                                                    |

|        |    | 10 = Dead-time function is disabled                                                                                                 |

|        |    | 01 = Negative dead time is actively applied for Complementary Output mode                                                           |

|        |    | 00 = Positive dead time is actively applied for all output modes                                                                    |

| bit 5  |    | <b>DTCP:</b> Dead-Time Compensation Polarity bit <sup>(3)</sup>                                                                     |

|        |    | When Set to '1':                                                                                                                    |

|        |    | If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.                                                                          |

|        |    | If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                                          |

|        |    | <u>When Set to '0':</u><br>If DTCMPx = 0, PWMxH is shortened and PWMxL is lengthened.                                               |

|        |    | If DTCMPx = 1, PWMxL is shortened and PWMxH is lengthened.                                                                          |

| bit 4  |    | Unimplemented: Read as '0'                                                                                                          |

| bit 3  |    | MTBS: Master Time Base Select bit                                                                                                   |

|        |    | 1 = PWM generator uses the secondary master time base for synchronization and as the clock source                                   |

|        |    | for the PWM generation logic (if secondary time base is available)                                                                  |

|        |    | 0 = PWM generator uses the primary master time base for synchronization and as the clock source                                     |

|        |    | for the PWM generation logic                                                                                                        |

| bit 2  |    | CAM: Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                |

|        |    | 1 = Center-Aligned mode is enabled                                                                                                  |

|        |    | 0 = Edge-Aligned mode is enabled                                                                                                    |

| bit 1  |    | <b>XPRES:</b> External PWMx Reset Control bit <sup>(5)</sup>                                                                        |

|        |    | <ul> <li>1 = Current-limit source resets the time base for this PWM generator if it is in Independent Time Base<br/>mode</li> </ul> |

|        |    | 0 = External pins do not affect PWMx time base                                                                                      |

| bit 0  |    | IUE: Immediate Update Enable bit <sup>(2)</sup>                                                                                     |

|        |    | 1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate                                                      |

|        |    | <ul> <li>Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the<br/>PWMx period boundary</li> </ul>   |

| Note   | 1: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.                        |

|        | 2: | These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                              |

|        | 3: | DTC<1:0> = 11 for DTCP to be effective; otherwise, DTCP is ignored.                                                                 |

|        | 4: | The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.            |

**5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

#### REGISTER 17-17: INT1TMRH: INTERVAL 1 TIMER HIGH WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | INTTM | R<31:24>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INTTM | R<23:16>          |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 INTTMR<31:16>: High Word Used to Form 32-Bit Interval Timer Register (INT1TMR) bits

#### REGISTER 17-18: INT1TMRL: INTERVAL 1 TIMER LOW WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | INTTM | IR<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INTT  | /IR<7:0>         |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable I  | bit   | W = Writable b   | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 INTTMR<15:0>: Low Word Used to Form 32-Bit Interval Timer Register (INT1TMR) bits

#### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER (CONTINUED)

- bit 1 **RBIF:** RX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 **TBIF:** TX Buffer Interrupt Flag bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

#### BUFFER 21-5: ECAN™ MESSAGE BUFFER WORD 4

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x            | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | Ву    | /te 3             |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x            | R/W-x           | R/W-x |

|                 |       |                  | Ву    | /te 2             |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-8 Byte 3<15:8>: ECAN Message Byte 3 bits

bit 7-0 Byte 2<7:0>: ECAN Message Byte 2 bits

#### BUFFER 21-6: ECAN™ MESSAGE BUFFER WORD 5

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | В     | yte 5            |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|                 |       |                  |       | yte 4            |                 |                 |       |

| bit 7           |       |                  |       | -                |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable I  | oit   | W = Writable     | bit   | U = Unimplen     | nented bit, rea | ad as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unki | nown  |

bit 15-8 Byte 5<15:8>: ECAN Message Byte 5 bits

bit 7-0 Byte 4<7:0>: ECAN Message Byte 4 bits

| REGISTER      | 25-3: CM40                                              | CON: COMPA                             | RATOR 4 CO        | ONTROL RE        | GISTER             |                                            |                     |

|---------------|---------------------------------------------------------|----------------------------------------|-------------------|------------------|--------------------|--------------------------------------------|---------------------|

| R/W-0         | R/W-0                                                   | R/W-0                                  | U-0               | U-0              | U-0                | R/W-0                                      | R/W-0               |

| CON           | COE                                                     | CPOL                                   | —                 | —                | _                  | CEVT                                       | COUT                |

| bit 15        |                                                         |                                        |                   |                  |                    |                                            | bit 8               |

| R/W-0         | DAM 0                                                   | U-0                                    |                   | U-0              | U-0                |                                            | R/W-0               |

|               | R/W-0                                                   | 0-0                                    | R/W-0             | 0-0              | 0-0                | R/W-0                                      |                     |

| EVPOL1        | EVPOL0                                                  | —                                      | CREF              | —                | _                  | CCH1 <sup>(1)</sup>                        | CCH0 <sup>(1)</sup> |

| bit 7         |                                                         |                                        |                   |                  |                    |                                            | bit (               |

| Legend:       |                                                         |                                        |                   |                  |                    |                                            |                     |

| R = Readable  | e bit                                                   | W = Writable                           | bit               | U = Unimple      | mented bit, rea    | d as '0'                                   |                     |

| -n = Value at |                                                         | '1' = Bit is se                        |                   | '0' = Bit is cle |                    | x = Bit is unkr                            | iown                |

|               |                                                         |                                        | •                 |                  |                    |                                            |                     |

| bit 15        | CON: Comp                                               | arator Enable b                        | bit               |                  |                    |                                            |                     |

|               |                                                         | ator is enabled                        |                   |                  |                    |                                            |                     |

|               |                                                         | ator is disabled                       |                   |                  |                    |                                            |                     |

| bit 14        | COE: Comp                                               | arator Output E                        | nable bit         |                  |                    |                                            |                     |

|               |                                                         | ator output is pr<br>ator output is in |                   | xOUT pin         |                    |                                            |                     |

| bit 13        | CPOL: Com                                               | parator Output                         | Polarity Select   | bit              |                    |                                            |                     |

|               |                                                         | ator output is in                      |                   |                  |                    |                                            |                     |

|               | 0 = Compara                                             | ator output is no                      | ot inverted       |                  |                    |                                            |                     |

| bit 12-10     | Unimpleme                                               | nted: Read as                          | '0'               |                  |                    |                                            |                     |

| bit 9         | CEVT: Com                                               | parator Event b                        | it                |                  |                    |                                            |                     |

|               | interrup                                                | ts until the bit is                    | cleared           | POL<1:0> set     | tings occurred;    | disables future                            | triggers and        |

|               | •                                                       | ator event did i                       |                   |                  |                    |                                            |                     |

| bit 8         |                                                         | parator Output                         |                   |                  |                    |                                            |                     |

|               | $\frac{\text{VVnen CPOL}}{1 = \text{VIN} + > \text{V}}$ | <u>. = 0 (non-inver</u><br>/N-         | ted polarity):    |                  |                    |                                            |                     |

|               | 0 = VIN + < V                                           |                                        |                   |                  |                    |                                            |                     |

|               | When CPOL                                               | = 1 (inverted p                        | olarity):         |                  |                    |                                            |                     |

|               | 1 = VIN+ < V                                            |                                        |                   |                  |                    |                                            |                     |

|               | 0 = VIN + > V                                           | 'IN-                                   |                   |                  |                    |                                            |                     |

| bit 7-6       |                                                         | >: Trigger/Ever                        |                   | -                |                    |                                            |                     |

|               | 10 = Trigger                                            |                                        | generated only    |                  |                    | or output (while (<br>ne polarity selected |                     |

|               |                                                         | L = 1 (inverted)<br>-high transition   |                   | ator output.     |                    |                                            |                     |

|               |                                                         | L = 0 (non-inve<br>-low transition     |                   | ator output.     |                    |                                            |                     |

|               |                                                         | /event/interrupt<br>(while CEVT =      |                   | v on low-to-higl | n transition of th | e polarity selecte                         | ed comparato        |

|               |                                                         | L = 1 (inverted                        |                   | ator output.     |                    |                                            |                     |

|               |                                                         | L = 0 (non-inve<br>-high transition    |                   | ator output.     |                    |                                            |                     |

|               | 00 = Trigger                                            | /event/interrupt                       | generation is     | disabled         |                    |                                            |                     |

| Note 1: In    | puts that are se                                        | lected and not a                       | available will be | e tied to Vss. S | See the "Pin Dia   | agrams" sectior                            | n for available     |

Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

## 26.3 Programmable CRC Registers

#### REGISTER 26-1: CRCCON1: CRC CONTROL REGISTER 1

| R/W-0                            | U-0                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                  | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R-0                                                                                      | R-0                                                | R-0             | R-0            |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------|----------------|

| CRCEN                            | —                                                                                                                                                                                                                                                             | CSIDL                                                                                                                                                                                                                                                                  | VWORD4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | VWORD3                                                                                   | VWORD2                                             | VWORD1          | VWORD0         |

| bit 15                           | ·                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                          |                                                    |                 | bit 8          |

| R-0                              | R-1                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                    | U-0                                                | U-0             | U-0            |

| CRCFUL                           | CRCMPT                                                                                                                                                                                                                                                        | CRCISEL                                                                                                                                                                                                                                                                | CRCGO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | LENDIAN                                                                                  | _                                                  | _               | _              |

| bit 7                            | •                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                          |                                                    |                 | bit (          |

| Legend:                          |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                          |                                                    |                 |                |

| R = Readable                     | e bit                                                                                                                                                                                                                                                         | W = Writable                                                                                                                                                                                                                                                           | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U = Unimplen                                                                             | nented bit, read                                   | d as '0'        |                |

| -n = Value at                    | POR                                                                                                                                                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | '0' = Bit is cle                                                                         | ared                                               | x = Bit is unkr | nown           |

| bit 15                           | 0 = CRC mo                                                                                                                                                                                                                                                    | dule is enabled                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | chines, pointer                                                                          | s and CRCWD                                        | AT/CRCDAT a     | re reset, othe |

| bit 14                           | Unimplemen                                                                                                                                                                                                                                                    | ted: Read as '                                                                                                                                                                                                                                                         | 0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                          |                                                    |                 |                |

| bit 13                           | CSIDL: CRC                                                                                                                                                                                                                                                    | Stop in Idle Mo                                                                                                                                                                                                                                                        | ode bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                          |                                                    |                 |                |

|                                  |                                                                                                                                                                                                                                                               | nues module op<br>es module opera                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                          | Idle mode                                          |                 |                |

|                                  |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | oue                                                                                      |                                                    |                 |                |

| bit 12-8                         | VWORD<4:0                                                                                                                                                                                                                                                     | >: Pointer Value                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | oue                                                                                      |                                                    |                 |                |

| bit 12-8                         | Indicates the                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                        | e bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                          | naximum value                                      | of 8 when PLE   | N<4:0> > 7     |

|                                  | Indicates the<br>or 16 when P                                                                                                                                                                                                                                 | number of valio                                                                                                                                                                                                                                                        | e bits<br>d words in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                          | naximum value                                      | of 8 when PLE   | N<4:0> > 7     |

|                                  | Indicates the<br>or 16 when P                                                                                                                                                                                                                                 | number of valic<br>LEN<4:0> $\leq$ 7.<br>C FIFO Full bit<br>ull                                                                                                                                                                                                        | e bits<br>d words in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                          | naximum value                                      | of 8 when PLE   | N<4:0> > 7     |

| bit 7                            | Indicates the<br>or 16 when P<br><b>CRCFUL</b> : CR<br>1 = FIFO is fi<br>0 = FIFO is r                                                                                                                                                                        | number of valic<br>LEN<4:0> $\leq$ 7.<br>C FIFO Full bit<br>ull                                                                                                                                                                                                        | e bits<br>d words in the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                          | naximum value                                      | of 8 when PLE   | N<4:0> > 7     |