Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detalls                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I²C, IrDA, LINbus, QEI, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc202-e-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

# 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

### 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

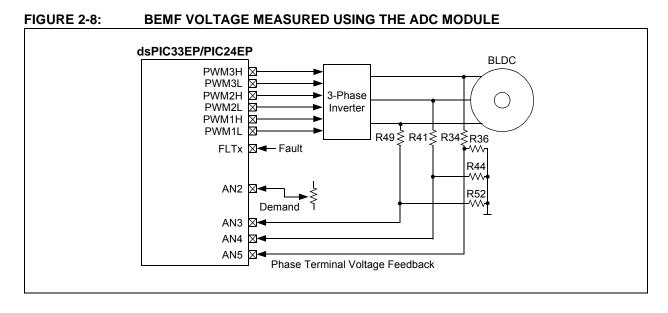

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

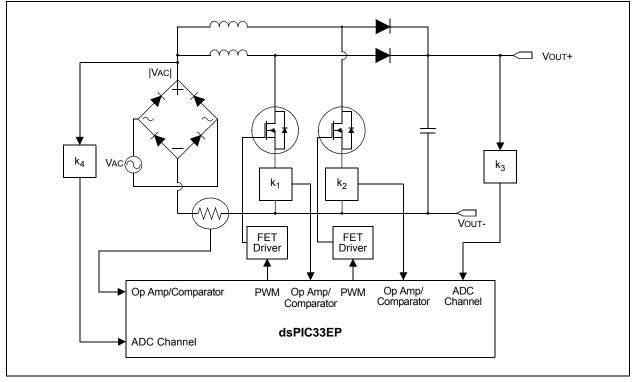

#### FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

#### FIGURE 2-7: INTERLEAVED PFC

| R/W-0               | U-0                          | R/W-0                                                    | R/W-0                   | R/W-0                       | R-0                       | R-0                | R-0                |

|---------------------|------------------------------|----------------------------------------------------------|-------------------------|-----------------------------|---------------------------|--------------------|--------------------|

| VAR                 | —                            | US1 <sup>(1)</sup>                                       | US0 <sup>(1)</sup>      | EDT <sup>(1,2)</sup>        | DL2 <sup>(1)</sup>        | DL1 <sup>(1)</sup> | DL0 <sup>(1)</sup> |

| bit 15              |                              |                                                          |                         |                             |                           |                    | bit                |

| R/W-0               | R/W-0                        | R/W-1                                                    | R/W-0                   | R/C-0                       | R-0                       | R/W-0              | R/W-0              |

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup>          | SATDW <sup>(1)</sup>                                     | ACCSAT <sup>(1)</sup>   | IPL3(3)                     | SFA                       | RND <sup>(1)</sup> | IF(1)              |

| bit 7               | I                            |                                                          |                         |                             | 1                         | 1                  | bit                |

| Legend:             |                              | C = Clearable                                            | e bit                   |                             |                           |                    |                    |

| R = Readabl         | e bit                        | W = Writable                                             | bit                     | U = Unimpler                | mented bit, read          | d as '0'           |                    |

| -n = Value at       | POR                          | '1' = Bit is set                                         | t                       | '0' = Bit is cle            | ared                      | x = Bit is unkr    | nown               |

| bit 15              | 1 = Variable                 | le Exception Pro<br>exception proce                      | essing latency          | is enabled                  |                           |                    |                    |

| bit 14              |                              | nted: Read as '                                          |                         |                             |                           |                    |                    |

| bit 13-12           | -                            | SP Multiply Uns                                          |                         | Control bits <sup>(1)</sup> |                           |                    |                    |

|                     | 01 = DSP er<br>00 = DSP er   | ngine multiplies<br>ngine multiplies<br>ngine multiplies | are unsigned are signed |                             |                           |                    |                    |

| bit 11              | •                            | O Loop Terminatives executing Dot<br>t                   |                         |                             | iteration                 |                    |                    |

| bit 10-8            |                              | Loop Nesting<br>oops are active                          |                         | (1)                         |                           |                    |                    |

|                     | •                            |                                                          |                         |                             |                           |                    |                    |

|                     | •                            |                                                          |                         |                             |                           |                    |                    |

|                     | 001 = 1 DO k<br>000 = 0 DO k | oop is active<br>oops are active                         |                         |                             |                           |                    |                    |

| bit 7               | SATA: ACCA                   | A Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |

|                     |                              | ator A saturatio<br>ator A saturatio                     |                         |                             |                           |                    |                    |

| bit 6               | SATB: ACCE                   | B Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |

|                     |                              | ator B saturatio<br>ator B saturatio                     |                         |                             |                           |                    |                    |

| bit 5               | SATDW: Dat                   | ta Space Write                                           | from DSP Engi           | ne Saturation               | Enable bit <sup>(1)</sup> |                    |                    |

|                     |                              | ace write satura<br>ace write satura                     |                         | I                           |                           |                    |                    |

| bit 4               |                              | cumulator Satu                                           |                         | elect bit <sup>(1)</sup>    |                           |                    |                    |

|                     |                              | uration (super s<br>uration (normal                      | ,                       |                             |                           |                    |                    |

| bit 3               |                              | nterrupt Priority                                        |                         |                             |                           |                    |                    |

|                     |                              | errupt Priority Le<br>errupt Priority Le                 |                         |                             |                           |                    |                    |

|                     | nis bit is availabl          |                                                          | PXXXMC20X/              | 50X and dsPl                | C33EPXXXGP                | 50X devices on     | ly.                |

| 2: Th               | nis bit is always            | reau as 0.                                               |                         |                             |                           |                    |                    |

# REGISTER 3-2: CORCON: CORE CONTROL REGISTER

**3:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

| TABLE 4   | -12:     | PWM RI         | EGISTE      | R MAP      | FOR de      | sPIC33E      | PXXXN   | AC20X/50 | DX AND F | PIC24EP | PXXXM | C20X [ | DEVICE  | S ONI | _Y    |            |       |               |

|-----------|----------|----------------|-------------|------------|-------------|--------------|---------|----------|----------|---------|-------|--------|---------|-------|-------|------------|-------|---------------|

| File Name | Addr.    | Bit 15         | Bit 14      | Bit 13     | Bit 12      | Bit 11       | Bit 10  | Bit 9    | Bit 8    | Bit 7   | Bit 6 | Bit 5  | Bit 4   | Bit 3 | Bit 2 | Bit 1      | Bit 0 | All<br>Resets |

| PTCON     | 0C00     | PTEN           | —           | PTSIDL     | SESTAT      | SEIEN        | EIPU    | SYNCPOL  | SYNCOEN  | SYNCEN  | SY    | NCSRC< | 2:0>    |       | SEV   | /TPS<3:0>  |       | 0000          |

| PTCON2    | 0C02     | _              | —           | _          | _           | _            | —       | _        | —        | —       | _     | —      | _       | —     |       | PCLKDIV<2: | 0>    | 0000          |

| PTPER     | 0C04     |                |             |            |             |              |         |          | PTPER<15 | :0>     |       |        |         |       |       |            |       | 00F8          |

| SEVTCMP   | 0C06     |                |             |            |             |              |         |          | SEVTCMP< | 5:0>    |       |        |         |       |       |            |       | 0000          |

| MDC       | 0C0A     |                |             |            |             |              |         |          | MDC<15:  | )>      |       |        |         |       |       |            |       | 0000          |

| CHOP      | 0C1A     | CHPCLKEN       | _           | _          | _           | _            | _       |          |          |         |       | CHOPCI | _K<9:0> |       |       |            |       | 0000          |

| PWMKEY    | 0C1E     |                |             |            |             |              |         |          | PWMKEY<1 | 5:0>    |       |        |         |       |       |            |       | 0000          |

| Legend: - | – = unir | mplemented, re | ead as '0'. | Reset valu | es are show | vn in hexade | ecimal. |          |          |         |       |        |         |       |       |            |       |               |

### TABLE 4-13: PWM GENERATOR 1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

|           | 10.   |         |        |         |                                                                                     |       | I OIT U |          |           |          |       | 1102- |               |         |          |         |         |      |

|-----------|-------|---------|--------|---------|-------------------------------------------------------------------------------------|-------|---------|----------|-----------|----------|-------|-------|---------------|---------|----------|---------|---------|------|

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 |       |         |          |           |          |       |       | All<br>Resets |         |          |         |         |      |

| PWMCON1   | 0C20  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN                                                                              | CLIEN | TRGIEN  | ITB      | MDCS      | DTC<     | :1:0> | DTCP  | _             | MTBS    | CAM      | XPRES   | IUE     | 0000 |

| IOCON1    | 0C22  | PENH    | PENL   | POLH    | POLL PMOD<1:0> OVRENH OVRENL OVRDAT<1:0> FLTDAT<1:0> CLDAT<1:0> SWAP OSYNC          |       |         |          |           |          |       | C000  |               |         |          |         |         |      |

| FCLCON1   | 0C24  | _       |        | (       | CLSRC<4:0> CLPOL CLMOD FLTSRC<4:0> FLTPOL FLTMOD<1:0>                               |       |         |          |           |          |       |       | 0000          |         |          |         |         |      |

| PDC1      | 0C26  |         |        |         | PDC1<15:0> F1                                                                       |       |         |          |           |          |       | FFF8  |               |         |          |         |         |      |

| PHASE1    | 0C28  |         |        |         |                                                                                     |       |         |          | PHASE1<15 | :0>      |       |       |               |         |          |         |         | 0000 |

| DTR1      | 0C2A  | _       | _      |         |                                                                                     |       |         |          |           | DTR1<13: | 0>    |       |               |         |          |         |         | 0000 |

| ALTDTR1   | 0C2C  | _       | _      |         |                                                                                     |       |         |          | А         | LTDTR1<1 | 3:0>  |       |               |         |          |         |         | 0000 |

| TRIG1     | 0C32  |         |        |         |                                                                                     |       |         |          | TRGCMP<18 | 5:0>     |       |       |               |         |          |         |         | 0000 |

| TRGCON1   | 0C34  |         | TRGDI  | V<3:0>  |                                                                                     | _     | _       | _        | _         | _        | _     |       |               | TRG     | STRT<5:0 | >       |         | 0000 |

| LEBCON1   | 0C3A  | PHR     | PHF    | PLR     | PLR PLF FLTLEBEN CLLEBEN — — — — BCH BCL BPHH BPHL BPLH BPLL C                      |       |         |          |           |          |       | 0000  |               |         |          |         |         |      |

| LEBDLY1   | 0C3C  | _       | _      | —       | LEB<11:0>000                                                                        |       |         |          |           |          |       | 0000  |               |         |          |         |         |      |

| AUXCON1   | 0C3E  | —       | —      | _       |                                                                                     |       | BLANKS  | SEL<3:0> |           | _        | _     |       | CHOPS         | EL<3:0> |          | CHOPHEN | CHOPLEN | 0000 |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

### 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

| R/W-0                | R/W-0                   | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|-------------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                      | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                         |                      |       |       |       |       | bit 8 |

|                      |                         |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA    | Ν     | OV    | Z     | С     |

| bit 7                |                         |                      |       |       |       |       | bit 0 |

|                      |                         |                      |       |       |       |       |       |

# REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                                                  | U-0   | U-0              | U-0   | U-0              | U-0   | U-0             | U-0   |  |

|----------------------------------------------------------------------|-------|------------------|-------|------------------|-------|-----------------|-------|--|

| —                                                                    | —     | —                | —     | —                | —     | _               | —     |  |

| bit 15                                                               |       |                  |       |                  | •     |                 | bit 8 |  |

|                                                                      |       |                  |       |                  |       |                 |       |  |

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0 | R/W-0           | R/W-0 |  |

|                                                                      |       |                  | STB<  | 23:16>           |       |                 |       |  |

| bit 7                                                                |       |                  |       |                  |       |                 | bit 0 |  |

|                                                                      |       |                  |       |                  |       |                 |       |  |

| Legend:                                                              |       |                  |       |                  |       |                 |       |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       |                  |       |                 |       |  |

| -n = Value at P                                                      | POR   | '1' = Bit is set |       | '0' = Bit is cle | eared | x = Bit is unkr | nown  |  |

|                                                                      |       |                  |       |                  |       |                 |       |  |

#### REGISTER 8-5: DMAXSTBH: DMA CHANNEL X START ADDRESS REGISTER B (HIGH)

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STB<23:16>: Secondary Start Address bits (source or destination)

#### REGISTER 8-6: DMAXSTBL: DMA CHANNEL X START ADDRESS REGISTER B (LOW)

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | STB   | <15:8>            |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STE   | 3<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkı | nown  |

bit 15-0 STB<15:0>: Secondary Start Address bits (source or destination)

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER     | <u>R 10-2: PMD</u> 2 | 2: PERIPHER                                         | AL MODULE       | DISABLE C         | ONTROL RE       | GISTER 2        |       |

|--------------|----------------------|-----------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|

| U-0          | U-0                  | U-0                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| _            |                      | _                                                   |                 | IC4MD             | IC3MD           | IC2MD           | IC1MD |

| bit 15       |                      |                                                     |                 |                   |                 |                 | bit   |

| U-0          | U-0                  | U-0                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|              |                      |                                                     |                 | OC4MD             | OC3MD           | OC2MD           | OC1MD |

| bit 7        |                      |                                                     |                 |                   |                 |                 | bit   |

|              |                      |                                                     |                 |                   |                 |                 |       |

| Legend:      | 1.1.1                |                                                     |                 |                   |                 |                 |       |

| R = Readab   |                      | W = Writable b                                      | Dit             | •                 | nented bit, rea |                 |       |

| -n = Value a | at POR               | '1' = Bit is set                                    |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

| bit 15-12    | Unimplemen           | ted: Read as '0                                     | ,               |                   |                 |                 |       |

| bit 11       | -                    | t Capture 4 Mod                                     |                 |                   |                 |                 |       |

|              | •                    | oture 4 module is                                   |                 |                   |                 |                 |       |

|              | 0 = Input Cap        | oture 4 module is                                   | s enabled       |                   |                 |                 |       |

| bit 10       | IC3MD: Input         | t Capture 3 Mod                                     | ule Disable bit |                   |                 |                 |       |

|              |                      | oture 3 module is                                   |                 |                   |                 |                 |       |

|              |                      | oture 3 module is                                   |                 |                   |                 |                 |       |

| bit 9        |                      | Capture 2 Mod                                       |                 |                   |                 |                 |       |

|              |                      | oture 2 module is<br>oture 2 module is              |                 |                   |                 |                 |       |

| bit 8        | IC1MD: Input         | t Capture 1 Mod                                     | ule Disable bit |                   |                 |                 |       |

|              | 1 = Input Cap        | oture 1 module is<br>oture 1 module is              | s disabled      |                   |                 |                 |       |

| bit 7-4      |                      | ted: Read as '0                                     |                 |                   |                 |                 |       |

| bit 3        | OC4MD: Out           | put Compare 4                                       | Module Disable  | e bit             |                 |                 |       |

|              |                      | ompare 4 modul                                      |                 |                   |                 |                 |       |

|              | -                    | ompare 4 modu                                       |                 |                   |                 |                 |       |

| bit 2        |                      | put Compare 3                                       |                 | e bit             |                 |                 |       |

|              | •                    | ompare 3 modul                                      |                 |                   |                 |                 |       |

| L:1 4        | -                    | ompare 3 modul                                      |                 | . h.:4            |                 |                 |       |

| bit 1        |                      | put Compare 2                                       |                 |                   |                 |                 |       |

|              | $\perp$ – Output Co  | ompare 2 modu                                       |                 |                   |                 |                 |       |

|              | 0 = Output Co        | ompare 2 modul                                      | le is enabled   |                   |                 |                 |       |

| bit 0        | •                    | ompare 2 modul<br>put Compare 1                     |                 | e bit             |                 |                 |       |

| bit 0        | OC1MD: Out           | ompare 2 modul<br>put Compare 1 l<br>ompare 1 modul | Module Disable  | e bit             |                 |                 |       |

#### ~

# 11.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-11, under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 30.0 "Electrical Characteristics" for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | TRGC  | MP<15:8>          |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | TRGC  | MP<7:0>           |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable t   | oit   | U = Unimplem      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

# REGISTER 16-14: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

When the primary PWMx functions in local time base, this register contains the compare values that can trigger the ADC module.

# 17.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data.

The operational features of the QEI module include:

- 32-Bit Position Counter

- 32-Bit Index Pulse Counter

- 32-Bit Interval Timer

- 16-Bit Velocity Counter

- 32-Bit Position Initialization/Capture/Compare High register

- 32-Bit Position Compare Low register

- x4 Quadrature Count mode

- External Up/Down Count mode

- External Gated Count mode

- External Gated Timer mode

- Internal Timer mode

Figure 17-1 illustrates the QEI block diagram.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | INDXH | LD<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INDXF | ILD<7:0>         |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimpler     | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

# REGISTER 17-10: INDX1HLD: INDEX COUNTER 1 HOLD REGISTER

bit 15-0 INDXHLD<15:0>: Hold Register for Reading and Writing INDX1CNTH bits

### REGISTER 17-11: QEI1ICH: QEI1 INITIALIZATION/CAPTURE HIGH WORD REGISTER

| R/W-0                                                                | R/W-0 | R/W-0                            | R/W-0                               | R/W-0                                                                                 | R/W-0                                                                                                                                                      | R/W-0                                                                                         |

|----------------------------------------------------------------------|-------|----------------------------------|-------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

|                                                                      |       | QEIIC                            | <31:24>                             |                                                                                       |                                                                                                                                                            |                                                                                               |

|                                                                      |       |                                  |                                     |                                                                                       |                                                                                                                                                            | bit 8                                                                                         |

|                                                                      |       |                                  |                                     |                                                                                       |                                                                                                                                                            |                                                                                               |

| R/W-0                                                                | R/W-0 | R/W-0                            | R/W-0                               | R/W-0                                                                                 | R/W-0                                                                                                                                                      | R/W-0                                                                                         |

|                                                                      |       | QEIIC                            | <23:16>                             |                                                                                       |                                                                                                                                                            |                                                                                               |

|                                                                      |       |                                  |                                     |                                                                                       |                                                                                                                                                            | bit 0                                                                                         |

|                                                                      |       |                                  |                                     |                                                                                       |                                                                                                                                                            |                                                                                               |

|                                                                      |       |                                  |                                     |                                                                                       |                                                                                                                                                            |                                                                                               |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                                  |                                     |                                                                                       |                                                                                                                                                            |                                                                                               |

| -n = Value at POR '1' = B                                            |       |                                  | '0' = Bit is clea                   | ared                                                                                  | x = Bit is unkr                                                                                                                                            | nown                                                                                          |

|                                                                      | R/W-0 | R/W-0 R/W-0<br>it W = Writable I | QEIIC<br>R/W-0 R/W-0 QEIIC<br>QEIIC | QEIIC<31:24><br>R/W-0 R/W-0 R/W-0<br>QEIIC<23:16><br>it W = Writable bit U = Unimplem | QEIIC<31:24>           R/W-0         R/W-0         R/W-0           QEIIC<23:16>            it         W = Writable bit         U = Unimplemented bit, real | QEIIC<31:24>           R/W-0         R/W-0         R/W-0         R/W-0           QEIIC<23:16> |

bit 15-0 **QEIIC<31:16>:** High Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

#### REGISTER 17-12: QEI1ICL: QEI1 INITIALIZATION/CAPTURE LOW WORD REGISTER

| R/W-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |

|-------------------|-------|------------------|-------|-------------------|-----------------|--------------------|-------|--|

|                   |       |                  | QEII  | C<15:8>           |                 |                    |       |  |

| bit 15            |       |                  |       |                   |                 |                    | bit 8 |  |

| R/W-0             | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |

|                   |       |                  | QEI   | C<7:0>            |                 |                    |       |  |

| bit 7             |       |                  |       |                   |                 |                    | bit C |  |

| Legend:           |       |                  |       |                   |                 |                    |       |  |

| R = Readable      | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, rea | ad as '0'          |       |  |

| -n = Value at POR |       | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unknown |       |  |

bit 15-0 **QEIIC<15:0>:** Low Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

| R/W-0         | R/W-0                                                                                                  | R/W-0                                    | U-0         | U-0                  | U-0             | U-0               | U-0                |  |  |

|---------------|--------------------------------------------------------------------------------------------------------|------------------------------------------|-------------|----------------------|-----------------|-------------------|--------------------|--|--|

| FRMEN         | SPIFSD                                                                                                 | FRMPOL                                   | —           | —                    | _               | —                 | —                  |  |  |

| bit 15        |                                                                                                        |                                          |             |                      |                 |                   | bit 8              |  |  |

|               |                                                                                                        |                                          |             |                      |                 |                   |                    |  |  |

| U-0           | U-0                                                                                                    | U-0                                      | U-0         | U-0                  | U-0             | R/W-0             | R/W-0              |  |  |

| —             | —                                                                                                      | —                                        | —           | —                    | _               | FRMDLY            | SPIBEN             |  |  |

| bit 7         |                                                                                                        |                                          |             |                      |                 |                   | bit 0              |  |  |

|               |                                                                                                        |                                          |             |                      |                 |                   |                    |  |  |

| Legend:       |                                                                                                        |                                          |             |                      |                 |                   |                    |  |  |

| R = Readable  | e bit                                                                                                  | W = Writable b                           | bit         | U = Unimpler         | nented bit, rea | ad as '0'         |                    |  |  |

| -n = Value at | POR                                                                                                    | '1' = Bit is set                         |             | '0' = Bit is cleared |                 |                   | x = Bit is unknown |  |  |

|               |                                                                                                        |                                          |             |                      |                 |                   |                    |  |  |

| bit 15        |                                                                                                        | med SPIx Suppo                           |             |                      |                 |                   |                    |  |  |

|               |                                                                                                        | SPIx support is e<br>SPIx support is d   |             | sx pin is used as    | Frame Sync      | pulse input/outpu | it)                |  |  |

| bit 14        |                                                                                                        | me Sync Pulse I                          |             | ontrol bit           |                 |                   |                    |  |  |

|               | 1 = Frame S                                                                                            | ync pulse input (                        | slave)      |                      |                 |                   |                    |  |  |

|               |                                                                                                        | ync pulse output                         | . ,         |                      |                 |                   |                    |  |  |

| bit 13        |                                                                                                        | ame Sync Pulse                           |             | t                    |                 |                   |                    |  |  |

|               |                                                                                                        | ync pulse is activ<br>ync pulse is activ |             |                      |                 |                   |                    |  |  |

| bit 12-2      | •                                                                                                      | nted: Read as '0                         |             |                      |                 |                   |                    |  |  |

| bit 1         | -                                                                                                      |                                          |             | et hit               |                 |                   |                    |  |  |

|               | <b>FRMDLY:</b> Frame Sync Pulse Edge Select bit<br>1 = Frame Sync pulse coincides with first bit clock |                                          |             |                      |                 |                   |                    |  |  |

|               |                                                                                                        | ync pulse preced                         |             |                      |                 |                   |                    |  |  |

| bit 0         |                                                                                                        | hanced Buffer Ei                         |             |                      |                 |                   |                    |  |  |

|               | 1 = Enhance                                                                                            | d buffer is enabl                        | ed          |                      |                 |                   |                    |  |  |

|               | 0 = Enhance                                                                                            | d buffer is disabl                       | led (Standa | rd mode)             |                 |                   |                    |  |  |

|               |                                                                                                        |                                          |             |                      |                 |                   |                    |  |  |

#### REGISTER 18-3: SPIxCON2: SPIx CONTROL REGISTER 2

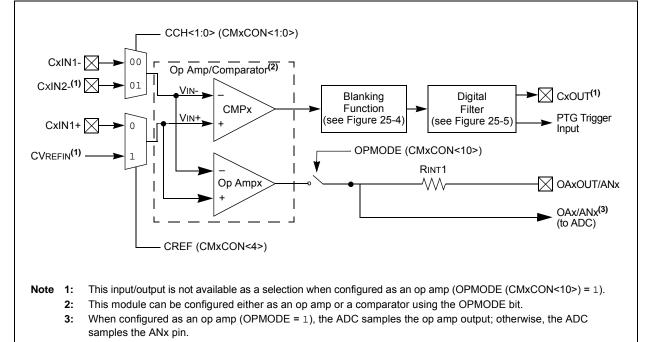

# 25.0 OP AMP/COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain up to four comparators, which can be configured in various ways. Comparators, CMP1, CMP2 and CMP3, also have the option to be configured as op amps, with the output being brought to an external pin for gain/filtering connections. As shown in Figure 25-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

Note: Op Amp/Comparator 3 is not available on the dsPIC33EPXXXGP502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

These options allow users to:

- · Select the edge for trigger and interrupt generation

- · Configure the comparator voltage reference

- · Configure output blanking and masking

- Configure as a comparator or op amp (CMP1, CMP2 and CMP3 only)

Note: Not all op amp/comparator input/output connections are available on all devices. See the "Pin Diagrams" section for available connections.

### FIGURE 25-1: OP AMP/COMPARATOR x MODULE BLOCK DIAGRAM (MODULES 1, 2 AND 3)

# 28.0 INSTRUCTION SET SUMMARY

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EP instruction set is almost identical to that of the dsPIC30F and dsPIC33F. The PIC24EP instruction set is almost identical to that of the PIC24F and PIC24H.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 28-1 lists the general symbols used in describing the instructions.

The dsPIC33E instruction set summary in Table 28-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand, which is typically a register 'Wb' without any address modifier

- The second source operand, which is typically a register 'Ws' with or without an address modifier

- The destination of the result, which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could be either the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/ shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement can use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand, which is a register 'Wb' without any address modifier

- The second source operand, which is a literal value

- The destination of the result (only if not the same as the first source operand), which is typically a register 'Wd' with or without an address modifier

The MAC class of DSP instructions can use some of the following operands:

- The accumulator (A or B) to be used (required operand)

- The W registers to be used as the two operands

- · The X and Y address space prefetch operations

- The X and Y address space prefetch destinations

- The accumulator write back destination

The other DSP instructions do not involve any multiplication and can include:

- The accumulator to be used (required)

- The source or destination operand (designated as Wso or Wdo, respectively) with or without an address modifier

- The amount of shift specified by a W register 'Wn' or a literal value

The control instructions can use some of the following operands:

- A program memory address

- The mode of the Table Read and Table Write instructions

# FIGURE 30-11: TIMERQ (QEI MODULE) EXTERNAL CLOCK TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

### TABLE 30-30: QEI MODULE EXTERNAL CLOCK TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |           |                                                              |                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |      |       |                                  |  |

|--------------------|-----------|--------------------------------------------------------------|-----------------------------|-------------------------------------------------------|------|------|-------|----------------------------------|--|

| Param<br>No.       | Symbol    | Charao                                                       | cteristic <sup>(1)</sup>    | Min.                                                  | Тур. | Max. | Units | Conditions                       |  |

| TQ10               | TtQH      | TQCK High<br>Time                                            | Synchronous, with prescaler | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25        |      |      | ns    | Must also meet<br>Parameter TQ15 |  |

| TQ11               | TtQL      | TQCK Low<br>Time                                             | Synchronous, with prescaler | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25        | —    | _    | ns    | Must also meet<br>Parameter TQ15 |  |

| TQ15               | TtQP      | TQCP Input<br>Period                                         | Synchronous, with prescaler | Greater of 25 + 50<br>or<br>(1 Tcy/N) + 50            | —    | _    | ns    |                                  |  |

| TQ20               | TCKEXTMRL | Delay from External TQCK<br>Clock Edge to Timer<br>Increment |                             | _                                                     | 1    | Тсү  | —     |                                  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

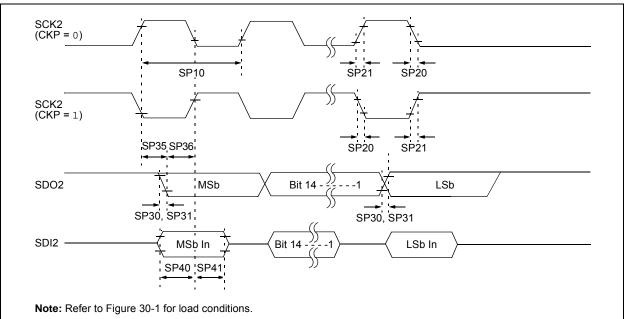

#### FIGURE 30-17: SPI2 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-36:SPI2 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHA | RACTERIST             | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |                     |      |       |                             |

|--------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|-------|-----------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                           | Min. | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |

| SP10   | FscP                  | Maximum SCK2 Frequency                                                                                                                                                                                                                                                                  |      | —                   | 9    | MHz   | -40°C to +125°C<br>(Note 3) |

| SP20   | TscF                  | SCK2 Output Fall Time                                                                                                                                                                                                                                                                   | _    | —                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP21   | TscR                  | SCK2 Output Rise Time                                                                                                                                                                                                                                                                   | _    | —                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                                                                                                                                                                                                                                                              | _    | —                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP31   | TdoR                  | SDO2 Data Output Rise Time                                                                                                                                                                                                                                                              | _    | —                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after SCK2 Edge                                                                                                                                                                                                                                                  | _    | 6                   | 20   | ns    |                             |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge                                                                                                                                                                                                                                            | 30   | —                   | _    | ns    |                             |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data<br>Input to SCK2 Edge                                                                                                                                                                                                                                           | 30   | —                   | _    | ns    |                             |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge                                                                                                                                                                                                                                               | 30   | —                   |      | ns    |                             |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

# TABLE 30-40:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                 | Standard Op<br>(unless othe<br>Operating te | erwise st | <b>ated)</b><br>e -40° | C ≤ TA ≤   | <b>V to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |

|--------------------|-----------------------|-------------------------------------------------|---------------------------------------------|-----------|------------------------|------------|-----------------------------------------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                   | Min. Typ. <sup>(2)</sup> Max.               |           | Units                  | Conditions |                                                                 |

| SP70               | FscP                  | Maximum SCK2 Input Frequency                    | —                                           | —         | 11                     | MHz        | (Note 3)                                                        |

| SP72               | TscF                  | SCK2 Input Fall Time                            | —                                           | —         | _                      | ns         | See Parameter DO32 (Note 4)                                     |

| SP73               | TscR                  | SCK2 Input Rise Time                            | —                                           | —         | _                      | ns         | See Parameter DO31 (Note 4)                                     |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                      | —                                           | _         | _                      | ns         | See Parameter DO31<br>(Note 4)                                  |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                      | —                                           | _         | _                      | ns         | See Parameter DO31 (Note 4)                                     |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge       | —                                           | 6         | 20                     | ns         |                                                                 |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge    | 30                                          | —         | _                      | ns         |                                                                 |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge      | 30                                          | —         | _                      | ns         |                                                                 |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge       | 30                                          | —         | _                      | ns         |                                                                 |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SS2}$ ↓ to SCK2 ↑ or SCK2 ↓<br>Input | 120                                         | —         | _                      | ns         |                                                                 |

| SP51               | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance          | 10                                          | —         | 50                     | ns         | (Note 4)                                                        |

| SP52               | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                           | 1.5 TCY + 40                                | —         |                        | ns         | (Note 4)                                                        |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 91 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]