Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

|                           | Activo                                                                           |

| Product Status            | Active                                                                           |

| Core Processor            | dsPIC                                                                            |

| Core Size                 | 16-Bit                                                                           |

| Speed                     | 60 MIPs                                                                          |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals               | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| lumber of I/O             | 21                                                                               |

| rogram Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type       | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| RAM Size                  | 24K x 16                                                                         |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| ata Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type           | Internal                                                                         |

| perating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Nounting Type             | Surface Mount                                                                    |

| ackage / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package   | 28-SOIC                                                                          |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc202-h-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

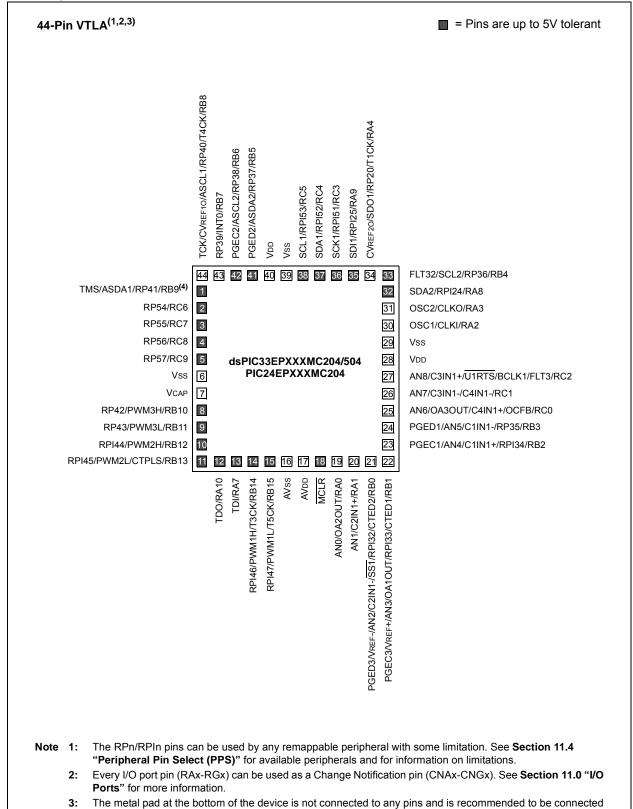

# Pin Diagrams (Continued)

There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the

to Vss externally.

JTAGEN bit field in Table 27-2.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name <sup>(4)</sup>                   | Pin<br>Type | Buffer<br>Type | PPS | Description                                                    |

|-------------------------------------------|-------------|----------------|-----|----------------------------------------------------------------|

| U2CTS                                     | - 1         | ST             | No  | UART2 Clear-To-Send.                                           |

| U2RTS                                     | 0           | _              | No  | UART2 Ready-To-Send.                                           |

| U2RX                                      | - 1         | ST             | Yes | UART2 receive.                                                 |

| U2TX                                      | 0           | _              | Yes | UART2 transmit.                                                |

| BCLK2                                     | 0           | ST             | No  | UART2 IrDA <sup>®</sup> baud clock output.                     |

| SCK1                                      | I/O         | ST             | No  | Synchronous serial clock input/output for SPI1.                |

| SDI1                                      | I           | ST             | No  | SPI1 data in.                                                  |

| SDO1                                      | 0           | _              | No  | SPI1 data out.                                                 |

| SS1                                       | I/O         | ST             | No  | SPI1 slave synchronization or frame pulse I/O.                 |

| SCK2                                      | I/O         | ST             | Yes | Synchronous serial clock input/output for SPI2.                |

| SDI2                                      | I           | ST             | Yes | SPI2 data in.                                                  |

| SDO2                                      | 0           | _              | Yes | SPI2 data out.                                                 |

| SS2                                       | I/O         | ST             | Yes | SPI2 slave synchronization or frame pulse I/O.                 |

| SCL1                                      | I/O         | ST             | No  | Synchronous serial clock input/output for I2C1.                |

| SDA1                                      | I/O         | ST             | No  | Synchronous serial data input/output for I2C1.                 |

| ASCL1                                     | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C1.      |

| ASDA1                                     | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C1.       |

| SCL2                                      | I/O         | ST             | No  | Synchronous serial clock input/output for I2C2.                |

| SDA2                                      | I/O         | ST             | No  | Synchronous serial data input/output for I2C2.                 |

| ASCL2                                     | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C2.      |

| ASDA2                                     | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C2.       |

| TMS <sup>(5)</sup>                        | - 1         | ST             | No  | JTAG Test mode select pin.                                     |

| TCK                                       | I           | ST             | No  | JTAG test clock input pin.                                     |

| TDI                                       | I           | ST             | No  | JTAG test data input pin.                                      |

| TDO                                       | 0           | _              | No  | JTAG test data output pin.                                     |

| C1RX <sup>(2)</sup>                       | - 1         | ST             | Yes | ECAN1 bus receive pin.                                         |

| C1TX <sup>(2)</sup>                       | 0           | _              | Yes | ECAN1 bus transmit pin.                                        |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup> | - 1         | ST             | Yes | PWM Fault Inputs 1 and 2.                                      |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup> | - 1         | ST             | No  | PWM Fault Inputs 3 and 4.                                      |

| FLT32 <sup>(1,3)</sup>                    | - 1         | ST             | No  | PWM Fault Input 32 (Class B Fault).                            |

| DTCMP1-DTCMP3 <sup>(1)</sup>              | - 1         | ST             | Yes | PWM Dead-Time Compensation Inputs 1 through 3.                 |

| PWM1L-PWM3L <sup>(1)</sup>                | 0           | _              | No  | PWM Low Outputs 1 through 3.                                   |

| PWM1H-PWM3H <sup>(1)</sup>                | 0           | _              | No  | PWM High Outputs 1 through 3.                                  |

| SYNCI1 <sup>(1)</sup>                     | - 1         | ST             | Yes | PWM Synchronization Input 1.                                   |

| SYNCO1 <sup>(1)</sup>                     | 0           |                | Yes | PWM Synchronization Output 1.                                  |

| INDX1 <sup>(1)</sup>                      | I           | ST             | Yes | Quadrature Encoder Index1 pulse input.                         |

| HOME1 <sup>(1)</sup>                      | - 1         | ST             | Yes | Quadrature Encoder Home1 pulse input.                          |

| QEA1 <sup>(1)</sup>                       | - 1         | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer |

| (4)                                       |             |                |     | external clock/gate input in Timer mode.                       |

| QEB1 <sup>(1)</sup>                       | I           | ST             | Yes | Quadrature Encoder Phase B input in QEI1 mode. Auxiliary timer |

| ON (TOMB) (1)                             |             |                | .,  | external clock/gate input in Timer mode.                       |

| CNTCMP1 <sup>(1)</sup>                    | 0           | _              | Yes | Quadrature Encoder Compare Output 1.                           |

Legend:CMOS = CMOS compatible input or output<br/>ST = Schmitt Trigger input with CMOS levels<br/>PPS = Peripheral Pin SelectAnalog = Analog input<br/>O = Output<br/>TTL = TTL input bufferP = Power<br/>I = Input

- Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

- 3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

- 4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

- 5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

TABLE 4-42: OP AMP/COMPARATOR REGISTER MAP

| File Name                | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8 | Bit 7 | Bit 6  | Bit 5    | Bit 4 | Bit 3        | Bit 2  | Bit 1     | Bit 0 | All<br>Resets |

|--------------------------|-------|--------|--------|--------|--------|--------|---------|---------|-------|-------|--------|----------|-------|--------------|--------|-----------|-------|---------------|

| CMSTAT                   | 0A80  | PSIDL  | _      | _      | _      | C4EVT  | C3EVT   | C2EVT   | C1EVT | _     | _      | _        | _     | C4OUT        | C3OUT  | C2OUT     | C1OUT | 0000          |

| CVRCON                   | 0A82  | _      | CVR2OE | _      | _      | _      | VREFSEL | _       | _     | CVREN | CVR10E | CVRR     | CVRSS |              | CVR<   | 3:0>      |       | 0000          |

| CM1CON                   | 0A84  | CON    | COE    | CPOL   | _      | _      | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | -            | _      | CCH       | <1:0> | 0000          |

| CM1MSKSRC                | 0A86  | _      | _      | _      | _      |        | SELSRO  | CC<3:0> |       |       | SELSRC | B<3:0>   |       |              | SELSRC | A<3:0>    |       | 0000          |

| CM1MSKCON                | 0A88  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN         | ABNEN  | AAEN      | AANEN | 0000          |

| CM1FLTR                  | A8A0  | _      | _      | _      | _      | _      | _       | _       | _     | _     | С      | FSEL<2:0 | >     | CFLTREN      | C      | CFDIV<2:0 | >     | 0000          |

| CM2CON                   | 0A8C  | CON    | COE    | CPOL   | _      | _      | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | -            | _      | CCH       | <1:0> | 0000          |

| CM2MSKSRC                | 0A8E  | _      | _      | _      | _      |        | SELSRO  | CC<3:0> |       |       | SELSRC | B<3:0>   |       | SELSRCA<3:0> |        |           | 0000  |               |

| CM2MSKCON                | 0A90  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN         | ABNEN  | AAEN      | AANEN | 0000          |

| CM2FLTR                  | 0A92  | ı      | _      | 1      |        | 1      | _       | ı       | _     | _     | С      | FSEL<2:0 | >     | CFLTREN      | C      | CFDIV<2:0 | >     | 0000          |

| CM3CON <sup>(1)</sup>    | 0A94  | CON    | COE    | CPOL   |        | 1      | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | 1        | CREF  | ı            | ı      | CCH       | <1:0> | 0000          |

| CM3MSKSRC <sup>(1)</sup> | 0A96  | ı      | _      | ı      | -      |        | SELSRO  | CC<3:0> |       |       | SELSRC | B<3:0>   |       |              | SELSRC | A<3:0>    |       | 0000          |

| CM3MSKCON <sup>(1)</sup> | 0A98  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN         | ABNEN  | AAEN      | AANEN | 0000          |

| CM3FLTR <sup>(1)</sup>   | 0A9A  | _      | _      | _      | _      | _      | _       | _       | _     | _     | С      | FSEL<2:0 | >     | CFLTREN      | C      | CFDIV<2:0 | >     | 0000          |

| CM4CON                   | 0A9C  | CON    | COE    | CPOL   | _      | _      | _       | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | -            | _      | CCH       | <1:0> | 0000          |

| CM4MSKSRC                | 0A9E  | _      | _      | _      | _      |        | SELSRO  | CC<3:0> |       |       | SELSRC | B<3:0>   |       |              | SELSRC | A<3:0>    |       | 0000          |

| CM4MSKCON                | 0AA0  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN         | ABNEN  | AAEN      | AANEN | 0000          |

| CM4FLTR                  | 0AA2  | _      | _      | _      | _      | _      | _       | _       | _     | _     | С      | FSEL<2:0 | >     | CFLTREN      | C      | CFDIV<2:0 | >     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These registers are unavailable on dsPIC33EPXXXGP502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

### **TABLE 4-43: CTMU REGISTER MAP**

| File Name | Addr. | Bit 15  | Bit 14  | Bit 13   | Bit 12     | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5 | Bit 4  | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|---------|---------|----------|------------|----------|----------|----------|----------|---------|---------|-------|--------|---------|-------|-------|-------|---------------|

| CTMUCON1  | 033A  | CTMUEN  | _       | CTMUSIDL | TGEN       | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | _       | _       | _     | _      | _       | _     | _     | _     | 0000          |

| CTMUCON2  | 033C  | EDG1MOD | EDG1POL |          | EDG1       | SEL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |       | EDG2SI | EL<3:0> |       | _     | _     | 0000          |

| CTMUICON  | 033E  |         |         | ITRIM<5  | ITRIM<5:0> |          |          | IRNG     | <1:0>    | ı       | _       | I     | _      |         |       | _     | _     | 0000          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-44: JTAG INTERFACE REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10        | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|---------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| JDATAH    | 0FF0 | _      | _      | _      | _      |        | JDATAH<27:16> |       |       |       |       |       |       |       | xxxx  |       |       |               |

| JDATAL    | 0FF2 |        |        |        |        |        | JDATAL<15:0>  |       |       |       |       |       |       |       | 0000  |       |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

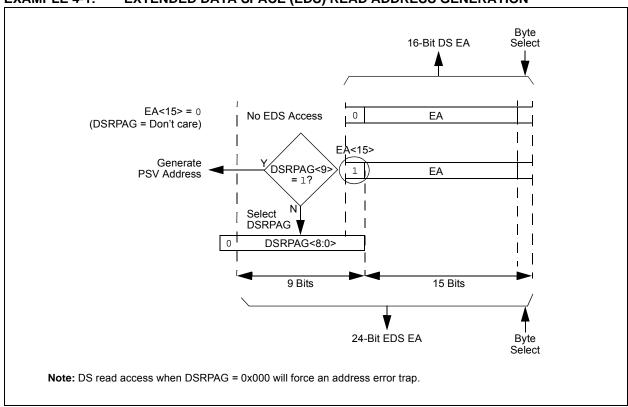

### 4.4.1 PAGED MEMORY SCHEME

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS)

address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

EXAMPLE 4-1: EXTENDED DATA SPACE (EDS) READ ADDRESS GENERATION

## 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

### 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2 where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- · Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0   |

|--------|-----|-----|-----|-----|-----|-----|---------|

| _      | _   | _   | _   | _   | _   | _   | PLLDIV8 |

| bit 15 |     |     |     |     |     |     | bit 8   |

| R/W-0   | R/W-0   | R/W-1   | R/W-1   | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| PLLDIV7 | PLLDIV6 | PLLDIV5 | PLLDIV4 | PLLDIV3 | PLLDIV2 | PLLDIV1 | PLLDIV0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-9 **Unimplemented:** Read as '0'

bit 8-0 PLLDIV<8:0>: PLL Feedback Divisor bits (also denoted as 'M', PLL multiplier)

111111111 **= 513**

Ť

000110000 = 50 (default)

•

•

•

000000010 = 4

00000001 = 3

0000000000 = 2

# 13.2 Timer Control Registers

## REGISTER 13-1: TxCON: (TIMER2 AND TIMER4) CONTROL REGISTER

| R/W-0  | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-------|-----|-----|-----|-----|-------|

| TON    | _   | TSIDL | _   | _   | _   | _   | _     |

| bit 15 |     |       |     |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0  | R/W-0  | R/W-0 | U-0 | R/W-0 | U-0   |

|-------|-------|--------|--------|-------|-----|-------|-------|

| _     | TGATE | TCKPS1 | TCKPS0 | T32   | _   | TCS   | _     |

| bit 7 |       |        |        |       |     |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **TON:** Timerx On bit

When T32 = 1:

1 = Starts 32-bit Timerx/y 0 = Stops 32-bit Timerx/y

When T32 = 0:

1 = Starts 16-bit Timerx

0 = Stops 16-bit Timerx

bit 14 Unimplemented: Read as '0'

bit 13 TSIDL: Timerx Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-7 Unimplemented: Read as '0'

bit 6 TGATE: Timerx Gated Time Accumulation Enable bit

When TCS = 1: This bit is ignored. When TCS = 0:

1 = Gated time accumulation is enabled 0 = Gated time accumulation is disabled

bit 5-4 TCKPS<1:0>: Timerx Input Clock Prescale Select bits

11 = 1:256 10 = 1:64 01 = 1:8

00 = 1:1

bit 3 T32: 32-Bit Timer Mode Select bit

1 = Timerx and Timery form a single 32-bit timer 0 = Timerx and Timery act as two 16-bit timers

bit 2 Unimplemented: Read as '0'

bit 1 TCS: Timerx Clock Source Select bit

1 = External clock is from pin, TxCK (on the rising edge)

0 = Internal clock (FP)

bit 0 Unimplemented: Read as '0'

# REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

```

bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

11111 = No Sync or Trigger source for ICx

```

11110 = Reserved

11101 = Reserved

11100 = CTMU module synchronizes or triggers ICx

11011 = ADC1 module synchronizes or triggers  $ICx^{(5)}$

11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

11001 = CMP2 module synchronizes or triggers ICx<sup>(5)</sup>

11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

10111 = Reserved

10110 = Reserved

10101 = Reserved

10100 = Reserved

10011 = IC4 module synchronizes or triggers ICx

10010 = IC3 module synchronizes or triggers ICx

10001 = IC2 module synchronizes or triggers ICx

10000 = IC1 module synchronizes or triggers ICx

01111 = Timer5 synchronizes or triggers ICx 01110 = Timer4 synchronizes or triggers ICx

01101 = Timer3 synchronizes or triggers ICx (default)

01100 = Timer2 synchronizes or triggers ICx

01011 = Timer1 synchronizes or triggers ICx

01010 = PTGOx module synchronizes or triggers ICx<sup>(6)</sup>

01001 = Reserved

01000 = Reserved

00111 = Reserved

00110 = Reserved

00101 = Reserved

00100 = OC4 module synchronizes or triggers ICx

00011 = OC3 module synchronizes or triggers ICx

00010 = OC2 module synchronizes or triggers ICx

00001 = OC1 module synchronizes or triggers ICx

00000 = No Sync or Trigger source for ICx

Note 1: The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: Each Input Capture x (ICx) module has one PTG input source. See **Section 24.0** "Peripheral Trigger **Generator (PTG) Module**" for more information.

PTGO8 = IC1

PTGO9 = IC2

PTGO10 = IC3

PTGO11 = IC4

| T TOUGET AAAOT | 30X, d3i 1030 | DEFAXAIVIC20 | X/50X AND | PIOZ4EPAAA | GF/IVICZUX |

|----------------|---------------|--------------|-----------|------------|------------|

| TES:           |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

# 15.2 Output Compare Control Registers

#### REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | R/W-0  |

|--------|-----|--------|---------|---------|---------|-----|--------|

| _      | _   | OCSIDL | OCTSEL2 | OCTSEL1 | OCTSEL0 | _   | ENFLTB |

| bit 15 |     |        |         |         |         |     | bit 8  |

| R/W-0  | U-0 | R/W-0, HSC | R/W-0, HSC | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|------------|------------|----------|-------|-------|-------|

| ENFLTA | _   | OCFLTB     | OCFLTA     | TRIGMODE | OCM2  | OCM1  | OCM0  |

| bit 7  |     |            |            |          |       |       | bit 0 |

Legend:HSC = Hardware Settable/Clearable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13 OCSIDL: Output Compare x Stop in Idle Mode Control bit

1 = Output Compare x Halts in CPU Idle mode

0 = Output Compare x continues to operate in CPU Idle mode

bit 12-10 OCTSEL<2:0>: Output Compare x Clock Select bits

111 = Peripheral clock (FP)

110 = Reserved

101 = PTGOx clock<sup>(2)</sup>

100 = T1CLK is the clock source of the OCx (only the synchronous clock is supported)

011 = T5CLK is the clock source of the OCx

010 = T4CLK is the clock source of the OCx

001 = T3CLK is the clock source of the OCx

000 = T2CLK is the clock source of the OCx

bit 9 **Unimplemented:** Read as '0'

bit 8 **ENFLTB:** Fault B Input Enable bit

1 = Output Compare Fault B input (OCFB) is enabled

0 = Output Compare Fault B input (OCFB) is disabled

bit 7 ENFLTA: Fault A Input Enable bit

1 = Output Compare Fault A input (OCFA) is enabled

0 = Output Compare Fault A input (OCFA) is disabled

bit 6 Unimplemented: Read as '0'

bit 5 OCFLTB: PWM Fault B Condition Status bit

1 = PWM Fault B condition on OCFB pin has occurred

0 = No PWM Fault B condition on OCFB pin has occurred

bit 4 OCFLTA: PWM Fault A Condition Status bit

1 = PWM Fault A condition on OCFA pin has occurred

0 = No PWM Fault A condition on OCFA pin has occurred

Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

2: Each Output Compare x module (OCx) has one PTG clock source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO4 = OC1

PTGO5 = OC2

PTGO6 = OC3

PTG07 = 0C4

## 16.2 PWM Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en555464

### 16.2.1 KEY RESOURCES

- "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

#### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

| U-0    | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0              |

|--------|-----|-----|--------|--------|--------|-------|--------------------|

| _      | _   | _   | DISSCK | DISSDO | MODE16 | SMP   | CKE <sup>(1)</sup> |

| bit 15 |     |     |        |        |        |       | bit 8              |

| R/W-0               | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|---------------------|-------|-------|----------------------|----------------------|----------------------|----------------------|----------------------|

| SSEN <sup>(2)</sup> | CKP   | MSTEN | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |

| bit 7               |       |       |                      |                      |                      |                      | bit 0                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12 **DISSCK:** Disable SCKx Pin bit (SPIx Master modes only)

1 = Internal SPIx clock is disabled, pin functions as I/O

0 = Internal SPIx clock is enabled

bit 11 DISSDO: Disable SDOx Pin bit

1 = SDOx pin is not used by the module; pin functions as I/O

0 = SDOx pin is controlled by the module

bit 10 MODE16: Word/Byte Communication Select bit

1 = Communication is word-wide (16 bits)

0 = Communication is byte-wide (8 bits)

bit 9 SMP: SPIx Data Input Sample Phase bit

Master mode:

1 = Input data is sampled at end of data output time

0 = Input data is sampled at middle of data output time

Slave mode:

SMP must be cleared when SPIx is used in Slave mode.

bit 8 **CKE:** SPIx Clock Edge Select bit<sup>(1)</sup>

1 = Serial output data changes on transition from active clock state to Idle clock state (refer to bit 6)

0 = Serial output data changes on transition from Idle clock state to active clock state (refer to bit 6)

bit 7 SSEN: Slave Select Enable bit (Slave mode)(2)

$1 = \overline{SSx}$  pin is used for Slave mode

$0 = \overline{SSx}$  pin is not used by the module; pin is controlled by port function

bit 6 **CKP:** Clock Polarity Select bit

${\tt 1}$  = Idle state for clock is a high level; active state is a low level

0 = Idle state for clock is a low level; active state is a high level

bit 5 MSTEN: Master Mode Enable bit

1 = Master mode

0 = Slave mode

Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

2: This bit must be cleared when FRMEN = 1.

3: Do not set both primary and secondary prescalers to the value of 1:1.

#### **REGISTER 21-7: CXINTE: ECANX INTERRUPT ENABLE REGISTER**

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | U-0 | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|-------|-------|-------|-----|--------|--------|-------|-------|

| IVRIE | WAKIE | ERRIE | _   | FIFOIE | RBOVIE | RBIE  | TBIE  |

| bit 7 |       |       |     |        |        |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7 IVRIE: Invalid Message Interrupt Enable bit

> 1 = Interrupt request is enabled 0 = Interrupt request is not enabled

bit 6 WAKIE: Bus Wake-up Activity Interrupt Enable bit

> 1 = Interrupt request is enabled 0 = Interrupt request is not enabled

bit 5 **ERRIE:** Error Interrupt Enable bit

> 1 = Interrupt request is enabled 0 = Interrupt request is not enabled

bit 4 Unimplemented: Read as '0'

bit 3 FIFOIE: FIFO Almost Full Interrupt Enable bit

> 1 = Interrupt request is enabled 0 = Interrupt request is not enabled

bit 2 RBOVIE: RX Buffer Overflow Interrupt Enable bit

> 1 = Interrupt request is enabled 0 = Interrupt request is not enabled RBIE: RX Buffer Interrupt Enable bit

bit 1

1 = Interrupt request is enabled 0 = Interrupt request is not enabled

bit 0 TBIE: TX Buffer Interrupt Enable bit

> 1 = Interrupt request is enabled 0 = Interrupt request is not enabled

| T TOUGET AAAOT | 30X, d3i 1030 | DEFAXAIVIC20 | X/50X AND | PIOZ4EPAAA | GF/IVICZUX |

|----------------|---------------|--------------|-----------|------------|------------|

| TES:           |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

|                |               |              |           |            |            |

# REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER (1,2)

W = Writable bit

'1' = Bit is set

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADCTS4 | ADCTS3 | ADCTS2 | ADCTS1 | IC4TSS | IC3TSS | IC2TSS | IC1TSS |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|-------|-------|--------|--------|--------|--------|

| OC4CS | OC3CS | OC2CS | OC1CS | OC4TSS | OC3TSS | OC2TSS | OC1TSS |

| bit 7 |       |       |       |        |        |        | bit 0  |

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

| bit 15 | ADCTS4: Sample Trigger PTGO15 for ADC bit                                                                                                                                                      |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 1 = Generates Trigger when the broadcast command is executed                                                                                                                                   |

|        | 0 = Does not generate Trigger when the broadcast command is executed                                                                                                                           |

| bit 14 | ADCTS3: Sample Trigger PTGO14 for ADC bit                                                                                                                                                      |

|        | 1 = Generates Trigger when the broadcast command is executed                                                                                                                                   |

|        | 0 = Does not generate Trigger when the broadcast command is executed                                                                                                                           |

| bit 13 | ADCTS2: Sample Trigger PTGO13 for ADC bit                                                                                                                                                      |

|        | 1 = Generates Trigger when the broadcast command is executed                                                                                                                                   |

|        | 0 = Does not generate Trigger when the broadcast command is executed                                                                                                                           |

| bit 12 | ADCTS1: Sample Trigger PTGO12 for ADC bit                                                                                                                                                      |

|        | 1 = Generates Trigger when the broadcast command is executed                                                                                                                                   |

|        | 0 = Does not generate Trigger when the broadcast command is executed                                                                                                                           |

| bit 11 | IC4TSS: Trigger/Synchronization Source for IC4 bit                                                                                                                                             |

|        | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 10 | IC3TSS: Trigger/Synchronization Source for IC3 bit                                                                                                                                             |

|        | 1 = Generates Trigger/Synchronization when the broadcast command is executed                                                                                                                   |

|        | 0 = Does not generate Trigger/Synchronization when the broadcast command is executed                                                                                                           |

| bit 9  | IC2TSS: Trigger/Synchronization Source for IC2 bit                                                                                                                                             |

|        | 1 = Generates Trigger/Synchronization when the broadcast command is executed                                                                                                                   |

|        | 0 = Does not generate Trigger/Synchronization when the broadcast command is executed                                                                                                           |

| bit 8  | IC1TSS: Trigger/Synchronization Source for IC1 bit                                                                                                                                             |

- 1 = Generates clock pulse when the broadcast command is executed

- 0 = Does not generate clock pulse when the broadcast command is executed

1 = Generates Trigger/Synchronization when the broadcast command is executed

0 = Does not generate Trigger/Synchronization when the broadcast command is executed

bit 6 OC3CS: Clock Source for OC3 bit

OC4CS: Clock Source for OC4 bit

- 1 = Generates clock pulse when the broadcast command is executed

- 0 = Does not generate clock pulse when the broadcast command is executed

- bit 5 OC2CS: Clock Source for OC2 bit

- 1 = Generates clock pulse when the broadcast command is executed

- 0 = Does not generate clock pulse when the broadcast command is executed

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: This register is only used with the PTGCTRL OPTION = 1111 Step command.

Legend:

bit 7

R = Readable bit

-n = Value at POR

#### REGISTER 25-7: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| U-0    | R/W-0                 | U-0 | U-0 | U-0 | R/W-0   | U-0 | U-0   |

|--------|-----------------------|-----|-----|-----|---------|-----|-------|

| _      | CVR20E <sup>(1)</sup> | _   | _   | _   | VREFSEL | _   | _     |

| bit 15 |                       |     |     |     |         |     | bit 8 |

| R/W-0 | R/W-0                 | R/W-0 | R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----------------------|-------|----------------------|-------|-------|-------|-------|

| CVREN | CVR10E <sup>(1)</sup> | CVRR  | CVRSS <sup>(2)</sup> | CVR3  | CVR2  | CVR1  | CVR0  |

| bit 7 |                       |       |                      |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14 CVR20E: Comparator Voltage Reference 2 Output Enable bit<sup>(1)</sup>

1 = (AVDD – AVSS)/2 is connected to the CVREF20 pin 0 = (AVDD – AVSS)/2 is disconnected from the CVREF20 pin

bit 13-11 **Unimplemented:** Read as '0'

bit 10 VREFSEL: Comparator Voltage Reference Select bit

1 = CVREFIN = VREF+

0 = CVREFIN is generated by the resistor network

bit 9-8 Unimplemented: Read as '0'

bit 7 **CVREN:** Comparator Voltage Reference Enable bit

1 = Comparator voltage reference circuit is powered on0 = Comparator voltage reference circuit is powered down

bit 6 **CVR10E**: Comparator Voltage Reference 1 Output Enable bit<sup>(1)</sup>

1 = Voltage level is output on the CVREF10 pin

0 = Voltage level is disconnected from then CVREF10 pin

bit 5 CVRR: Comparator Voltage Reference Range Selection bit

1 = CVRSRC/24 step-size

0 = CVRSRC/32 step-size

bit 4 **CVRSS:** Comparator Voltage Reference Source Selection bit<sup>(2)</sup>

1 = Comparator voltage reference source, CVRSRC = (VREF+) - (AVSS)

0 = Comparator voltage reference source, CVRSRC = AVDD - AVSS

bit 3-0 CVR<3:0> Comparator Voltage Reference Value Selection 0 ≤ CVR<3:0> ≤ 15 bits

When CVRR = 1:

CVREFIN = (CVR<3:0>/24) • (CVRSRC)

When CVRR = 0:

CVREFIN = (CVRSRC/4) + (CVR<3:0>/32) • (CVRSRC)

Note 1: CVRxOE overrides the TRISx and the ANSELx bit settings.

2: In order to operate with CVRSS = 1, at least one of the comparator modules must be enabled.

TABLE 28-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| Field | Description                                                                                                                                                                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm,Wn | Dividend, Divisor working register pair (direct addressing)                                                                                                                                                                                                 |

| Wm*Wm | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                               |

| Wm*Wn | Multiplicand and Multiplier working register pair for DSP instructions ∈ {W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                                  |

| Wn    | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                                                       |

| Wnd   | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                                                           |

| Wns   | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                                                |

| WREG  | W0 (working register used in file register instructions)                                                                                                                                                                                                    |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                                |

| Wso   | Source W register ∈ { Wns, [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                                       |

| Wx    | X Data Space Prefetch Address register for DSP instructions ∈ {[W8] + = 6, [W8] + = 4, [W8] + = 2, [W8], [W8] - = 6, [W8] - = 4, [W8] - = 2, [W9] + = 6, [W9] + = 4, [W9] + = 2, [W9], [W9] - = 6, [W9] - = 4, [W9] - = 2, [W9 + W12], none}                |

| Wxd   | X Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                    |

| Wy    | Y Data Space Prefetch Address register for DSP instructions ∈ {[W10] + = 6, [W10] + = 4, [W10] + = 2, [W10], [W10] - = 6, [W10] - = 4, [W10] - = 2, [W11] + = 6, [W11] + = 4, [W11] + = 2, [W11], [W11] - = 6, [W11] - = 4, [W11] - = 2, [W11 + W12], none} |

| Wyd   | Y Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                    |

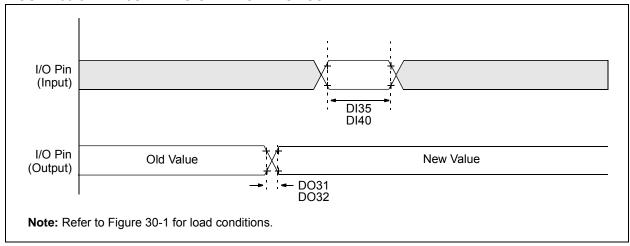

FIGURE 30-3: I/O TIMING CHARACTERISTICS

**TABLE 30-21: I/O TIMING REQUIREMENTS**

| AC CHARACTERISTICS |        |                                   | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                     |      |       |            |

|--------------------|--------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|------------|

| Param<br>No.       | Symbol | Characteristic                    | Min.                                                                                                                                                                                                   | Typ. <sup>(1)</sup> | Max. | Units | Conditions |

| DO31               | TioR   | Port Output Rise Time             | _                                                                                                                                                                                                      | 5                   | 10   | ns    |            |

| DO32               | TioF   | Port Output Fall Time             | _                                                                                                                                                                                                      | 5                   | 10   | ns    |            |

| DI35               | TINP   | INTx Pin High or Low Time (input) | 20                                                                                                                                                                                                     | _                   |      | ns    |            |

| DI40               | TRBP   | CNx High or Low Time (input)      | 2                                                                                                                                                                                                      | _                   | _    | Tcy   |            |

Note 1: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

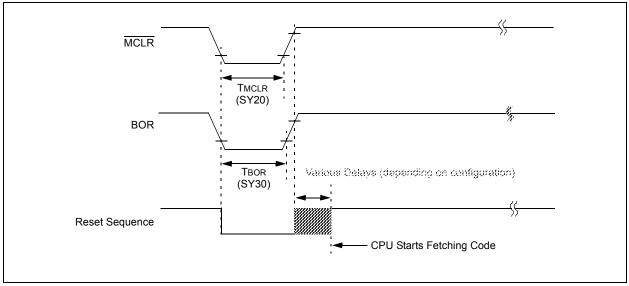

FIGURE 30-4: BOR AND MASTER CLEAR RESET TIMING CHARACTERISTICS

| PMD (PIC24EPXXXMC20X Devices)94          | CMxMSKCON (Comparator x Mask              |     |

|------------------------------------------|-------------------------------------------|-----|

| PORTA (PIC24EPXXXGP/MC202,               | Gating Control)                           | 368 |

| dsPIC33EPXXXGP/MC202/502 Devices) 104    | CMxMSKSRC (Comparator x Mask Source       |     |

| PORTA (PIC24EPXXXGP/MC203,               | Select Control)                           | 366 |

| dsPIC33EPXXXGP/MC203/503 Devices) 103    | CORCON (Core Control)42                   |     |

| PORTA (PIC24EPXXXGP/MC204,               | CRCCON1 (CRC Control 1)                   |     |

| dsPIC33EPXXXGP/MC204/504 Devices) 102    | CRCCON2 (CRC Control 2)                   |     |

| PORTA (PIC24EPXXXGP/MC206,               | CRCXORH (CRC XOR Polynomial High)         |     |

| ,                                        |                                           |     |

| dsPIC33EPXXXGP/MC206/506 Devices) 99     | CRCXORL (CRC XOR Polynomial Low)          |     |

| PORTB (PIC24EPXXXGP/MC202,               | CTMUCON1 (CTMU Control 1)                 |     |

| dsPIC33EPXXXGP/MC202/502 Devices) 104    | CTMUCON2 (CTMU Control 2)                 |     |

| PORTB (PIC24EPXXXGP/MC203,               | CTMUICON (CTMU Current Control)           | 319 |

| dsPIC33EPXXXGP/MC203/503 Devices) 103    | CVRCON (Comparator Voltage                |     |

| PORTB (PIC24EPXXXGP/MC204,               | Reference Control)                        | 371 |

| dsPIC33EPXXXGP/MC204/504 Devices) 102    | CxBUFPNT1 (ECANx Filter 0-3               |     |

| PORTB (PIC24EPXXXGP/MC206,               | Buffer Pointer 1)                         | 300 |

| dsPIC33EPXXXGP/MC206/506 Devices) 99     | CxBUFPNT2 (ECANx Filter 4-7               |     |

| PORTC (PIC23EPXXXGP/MC203,               | Buffer Pointer 2)                         | 301 |

| dsPIC33EPXXXGP/MC203/503 Devices) 103    | CxBUFPNT3 (ECANx Filter 8-11              |     |

| PORTC (PIC24EPXXXGP/MC204,               | Buffer Pointer 3)                         | 301 |

| dsPIC33EPXXXGP/MC204/504 Devices) 102    | CxBUFPNT4 (ECANx Filter 12-15             |     |

| PORTC (PIC24EPXXXGP/MC206,               | Buffer Pointer 4)                         | 302 |

| dsPIC33EPXXXGP/MC206/506 Devices) 99     | CxCFG1 (ECANx Baud Rate Configuration 1)  |     |

| PORTD (PIC24EPXXXGP/MC206,               | CxCFG2 (ECANx Baud Rate Configuration 2)  |     |

| dsPIC33EPXXXGP/MC206/506 Devices) 100    | CxCTRL1 (ECANx Control 1)                 |     |

| PORTE (PIC24EPXXXGP/MC206,               | CxCTRL2 (ECANx Control 2)                 |     |

| dsPIC33EPXXXGP/MC206/506 Devices) 100    | CxEC (ECANx Transmit/Receive Error Count) |     |

| PORTF (PIC24EPXXXGP/MC206,               | CXFCTRL (ECANX FIFO Control)              |     |

| dsPIC33EPXXXGP/MC206/506 Devices) 100    | CxFEN1 (ECANx Acceptance Filter Enable 1) |     |

| PORTG (PIC24EPXXXGP/MC206 and            | CxFIFO (ECANx FIFO Status)                |     |

| dsPIC33EPXXXGP/MC206/506 Devices) 101    | CxFMSKSEL1 (ECANx Filter 7-0              | 204 |

| PTG78                                    | Mask Selection 1)                         | 304 |

| PWM (dsPIC33EPXXXMC20X/50X,              | CxFMSKSEL2 (ECANx Filter 15-8             | 504 |

| · ·                                      |                                           | 205 |

| PIC24EPXXXMC20X Devices)79               | Mask Selection 2)                         |     |

| PWM Generator 1 (dsPIC33EPXXXMC20X/50X,  | CXINTE (ECANX Interrupt Enable)           |     |

| PIC24EPXXXMC20X Devices)79               | CxINTF (ECANx Interrupt Flag)             | 295 |

| PWM Generator 2 (dsPIC33EPXXXMC20X/50X,  | CxRXFnEID (ECANx Acceptance Filter n      | 004 |

| PIC24EPXXXMC20X Devices)80               | Extended Identifier)                      | 304 |

| PWM Generator 3 (dsPIC33EPXXXMC20X/50X,  | CxRXFnSID (ECANx Acceptance Filter n      | 000 |

| PIC24EPXXXMC20X Devices)80               | Standard Identifier)                      |     |

| QEI1 (dsPIC33EPXXXMC20X/50X,             | CxRXFUL1 (ECANx Receive Buffer Full 1)    |     |

| PIC24EPXXXMC20X Devices)81               | CxRXFUL2 (ECANx Receive Buffer Full 2)    | 307 |

| Reference Clock93                        | CxRXMnEID (ECANx Acceptance Filter Mask n |     |

| SPI1 and SPI283                          | Extended Identifier)                      | 306 |

| System Control93                         | CxRXMnSID (ECANx Acceptance Filter Mask n |     |

| Time1 through Time575                    | Standard Identifier)                      | 306 |

| UART1 and UART282                        | CxRXOVF1 (ECANx Receive                   |     |

| Registers                                | Buffer Overflow 1)                        | 308 |

| AD1CHS0 (ADC1 Input Channel 0 Select)333 | CxRXOVF2 (ECANx Receive                   |     |

| AD1CHS123 (ADC1 Input                    | Buffer Overflow 2)                        | 308 |

| Channel 1, 2, 3 Select)                  | CxTRmnCON (ECANx TX/RX                    |     |

| AD1CON1 (ADC1 Control 1)                 | Buffer mn Control)                        | 309 |

| AD1CON2 (ADC1 Control 2)                 | CxVEC (ECANx Interrupt Code)              |     |

| AD1CON3 (ADC1 Control 3)                 | DEVID (Device ID)                         |     |

| AD1CON4 (ADC1 Control 4)                 | DEVREV (Device Revision)                  |     |

| AD1CSSH (ADC1 Input Scan Select High)    | DMALCA (DMA Last Channel Active Status)   |     |

| AD1CSSL (ADC1 Input Scan Select Low)     | DMAPPS (DMA Ping-Pong Status)             |     |

| ALTDTRx (PWMx Alternate Dead-Time)       | DMAPWC (DMA Peripheral Write              |     |

| AUXCONx (PWMx Auxiliary Control)247      | Collision Status)                         | 1⊿Ω |

| CHOP (PWMx Chop Clock Generator)234      | DMARQC (DMA Request Collision Status)     |     |

| CLKDIV (Clock Divisor)158                | DMAXCNT (DMA Channel x Transfer Count)    |     |

| ,                                        |                                           |     |

| CMSTAT (On Amp/Comparator Status) 360    | DMAXCON (DMA Channel x Control)           | 142 |

| CMSTAT (Op Amp/Comparator Status)        | DMAxPAD (DMA Channel x                    | 146 |

| CMxCON (Comparator x Control, x = 1,2,3) | Peripheral Address)                       |     |

| CMxFLTR (Comparator x Filter Control)370 | DMAxREQ (DMA Channel x IRQ Select)        | 143 |