Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                     |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                          |

| Supplier Device Package    | 28-SPDIP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc202-h-sp |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8 | Bit 7         | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|-------|---------------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >     |               | —       | _           | _       | —       | _      | —           |        | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>  |               | PT      | GSTEPIP<2   | :0>     | —       | —      | _           | -      | 4440          |

| IPC37        | 088A  | _      | —      | —          | _      | _      | F      | PTG3IP<2:0 | )>    |               |         | PTG2IP<2:0> | >       | _       |        | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     |        |        |        | _          | _     | _             | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     | _      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      | _      |        |            | —     |               | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | —      | —          | _      | _      |        |            | —     |               | _       | DAE         | DOOVR   | _       | —      | —           |        | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _      | _      | -      | _          | —     | _             | _       | _           | _       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | Ι      | _      | _          | _      |        | ILR<   | 3:0>       |       | VECNUM<7:0> 0 |         |             |         |         | 0000   |             |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE 4   | -14:  | PVVIVI G | ENERA  | IUR Z R | EGIST           |                                                  | FOR as  | PIC33EP |            | 202/202   |         | 16246   | PXXX    |       |          | CES ONL | _ T    |               |

|-----------|-------|----------|--------|---------|-----------------|--------------------------------------------------|---------|---------|------------|-----------|---------|---------|---------|-------|----------|---------|--------|---------------|

| File Name | Addr. | Bit 15   | Bit 14 | Bit 13  | Bit 12          | Bit 11                                           | Bit 10  | Bit 9   | Bit 8      | Bit 7     | Bit 6   | Bit 5   | Bit 4   | Bit 3 | Bit 2    | Bit 1   | Bit 0  | All<br>Resets |

| PWMCON2   | 0C40  | FLTSTAT  | CLSTAT | TRGSTAT | FLTIEN          | CLIEN                                            | TRGIEN  | ITB     | MDCS       | DTC       | <1:0>   | DTCP    | _       | MTBS  | CAM      | XPRES   | IUE    | 0000          |

| IOCON2    | 0C42  | PENH     | PENL   | POLH    | POLL            | PMOD                                             | 0<1:0>  | OVRENH  | OVRENL     | OVRDA     | \T<1:0> | FLTD    | \T<1:0> | CLDA  | AT<1:0>  | SWAP    | OSYNC  | C000          |

| FCLCON2   | 0C44  | _        |        | (       | CLSRC<4:0       | )>                                               |         | CLPOL   | CLMOD      |           | FLT     | SRC<4:0 | >       |       | FLTPOL   | FLTMO   | D<1:0> | 00F8          |

| PDC2      | 0C46  |          |        |         |                 |                                                  |         |         | PDC2<15:0> |           |         |         |         |       |          |         |        | 0000          |

| PHASE2    | 0C48  |          |        |         | PHASE2<15:0> 00 |                                                  |         |         |            |           |         |         |         | 0000  |          |         |        |               |

| DTR2      | 0C4A  | _        | _      |         |                 |                                                  |         |         | [          | DTR2<13:0 | >       |         |         |       |          |         |        | 0000          |

| ALTDTR2   | 0C4C  | _        | _      |         |                 |                                                  |         |         | AL         | TDTR2<13  | :0>     |         |         |       |          |         |        | 0000          |

| TRIG2     | 0C52  |          |        |         |                 |                                                  |         | TI      | RGCMP<15:0 | )>        |         |         |         |       |          |         |        | 0000          |

| TRGCON2   | 0C54  |          | TRGDI  | V<3:0>  |                 | _                                                | —       | _       | _          | _         | -       |         |         | TRO   | GSTRT<5: | 0>      |        | 0000          |

| LEBCON2   | 0C5A  | PHR      | PHF    | PLR     | PLF             | FLTLEBEN                                         | CLLEBEN | _       | _          | _         | -       | BCH     | BCL     | BPHH  | BPHL     | BPLH    | BPLL   | 0000          |

| LEBDLY2   | 0C5C  | _        | _      | _       | LEB<11:0> 000   |                                                  |         |         |            |           |         | 0000    |         |       |          |         |        |               |

| AUXCON2   | 0C5E  | _        | _      | —       | —               | - BLANKSEL<3:0> — — CHOPSEL<3:0> CHOPHEN CHOPLEN |         |         |            |           |         | 0000    |         |       |          |         |        |               |

I- DIGGOEDV/VMOGOV/EGV AND DIGGAEDV/VMOGOV DEVICED ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-15: PWM GENERATOR 3 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12           | Bit 11                                           | Bit 10  | Bit 9  | Bit 8      | Bit 7     | Bit 6  | Bit 5   | Bit 4   | Bit 3 | Bit 2    | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------|---------|--------|---------|------------------|--------------------------------------------------|---------|--------|------------|-----------|--------|---------|---------|-------|----------|-------|--------|---------------|

| PWMCON3   | 0C60  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN           | CLIEN                                            | TRGIEN  | ITB    | MDCS       | DTC<      | <1:0>  | DTCP    | —       | MTBS  | CAM      | XPRES | IUE    | 0000          |

| IOCON3    | 0C62  | PENH    | PENL   | POLH    | POLL             | PMOD                                             | )<1:0>  | OVRENH | OVRENL     | OVRDA     | T<1:0> | FLTD    | AT<1:0> | CLD   | AT<1:0>  | SWAP  | OSYNC  | C000          |

| FCLCON3   | 0C64  |         |        | (       | CLSRC<4:0        | )>                                               |         | CLPOL  | CLMOD      |           | FLT    | SRC<4:0 | >       |       | FLTPOL   | FLTMO | D<1:0> | 00F8          |

| PDC3      | 0C66  |         |        |         |                  |                                                  |         |        | PDC3<15:0> | •         |        |         |         |       |          |       |        | 0000          |

| PHASE3    | 0C68  |         |        |         | PHASE3<15:0> 000 |                                                  |         |        |            |           |        |         | 0000    |       |          |       |        |               |

| DTR3      | 0C6A  |         | —      |         |                  |                                                  |         |        | [          | DTR3<13:0 | >      |         |         |       |          |       |        | 0000          |

| ALTDTR3   | 0C6C  |         | —      |         |                  |                                                  |         |        | AL         | TDTR3<13  | :0>    |         |         |       |          |       |        | 0000          |

| TRIG3     | 0C72  |         |        |         |                  |                                                  |         | Т      | RGCMP<15:  | 0>        |        |         |         |       |          |       |        | 0000          |

| TRGCON3   | 0C74  |         | TRGDI  | V<3:0>  |                  | _                                                | _       | _      | _          | _         | _      |         |         | TR    | GSTRT<5: | 0>    |        | 0000          |

| LEBCON3   | 0C7A  | PHR     | PHF    | PLR     | PLF              | FLTLEBEN                                         | CLLEBEN | —      | —          |           | —      | BCH     | BCL     | BPHH  | BPHL     | BPLH  | BPLL   | 0000          |

| LEBDLY3   | 0C7C  |         | —      | _       | _                | LEB<11:0> 000                                    |         |        |            |           |        |         | 0000    |       |          |       |        |               |

| AUXCON3   | 0C7E  |         | —      | —       | —                | BLANKSEL<3:0> — — CHOPSEL<3:0> CHOPHEN CHOPLEN ( |         |        |            |           | 0000   |         |         |       |          |       |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

.

----

.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0                                                                                                                                | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-------------------|------------------|-----------------|-------|--|--|

| —               | —                                                                                                                                  |                  |       | RP57              | R<5:0>           |                 |       |  |  |

| bit 15          |                                                                                                                                    |                  |       |                   |                  |                 | bit 8 |  |  |

|                 |                                                                                                                                    |                  |       |                   |                  |                 |       |  |  |

| U-0             | U-0                                                                                                                                | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |  |

| _               | —                                                                                                                                  |                  |       | RP56              | R<5:0>           |                 |       |  |  |

| bit 7           |                                                                                                                                    |                  |       |                   |                  |                 | bit 0 |  |  |

|                 |                                                                                                                                    |                  |       |                   |                  |                 |       |  |  |

| Legend:         |                                                                                                                                    |                  |       |                   |                  |                 |       |  |  |

| R = Readable I  | bit                                                                                                                                | W = Writable     | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |

| -n = Value at P | OR                                                                                                                                 | '1' = Bit is set | :     | '0' = Bit is clea | ared             | x = Bit is unkr | iown  |  |  |

|                 |                                                                                                                                    |                  |       |                   |                  |                 |       |  |  |

| bit 15-14       | Unimplemen                                                                                                                         | ted: Read as '   | 0'    |                   |                  |                 |       |  |  |

| bit 13-8        | 3-8 RP57R<5:0>: Peripheral Output Function is Assigned to RP57 Output Pin bits<br>(see Table 11-3 for peripheral function numbers) |                  |       |                   |                  |                 |       |  |  |

| bit 7-6         | Unimplemented: Read as '0'                                                                                                         |                  |       |                   |                  |                 |       |  |  |

#### REGISTER 11-24: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6

| (see Table 11-3 for peripheral function numbers) |

|--------------------------------------------------|

|                                                  |

#### REGISTER 11-25: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP97  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

RP56R<5:0>: Peripheral Output Function is Assigned to RP56 Output Pin bits

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   |     | —   | —   |     | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP97R<5:0>:** Peripheral Output Function is Assigned to RP97 Output Pin bits (see Table 11-3 for peripheral function numbers)

bit 7-0 Unimplemented: Read as '0'

bit 5-0

NOTES:

# 14.2 Input Capture Registers

#### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | —   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 |     | —     |

| bit 15 |     |        |         |         |         |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/HC/HS-0 | R/HC/HS-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----------|-----------|-------|-------|-------|

| —     | ICI1  | ICI0  | ICOV      | ICBNE     | ICM2  | ICM1  | ICM0  |

| bit 7 |       |       |           |           |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit |                    |  |

|-------------------|-----------------------------|----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re  | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared       | x = Bit is unknown |  |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Stop in Idle Control bit                                                                                                              |

|           | 1 = Input capture will Halt in CPU Idle mode                                                                                                                |

|           | 0 = Input capture will continue to operate in CPU Idle mode                                                                                                 |

| bit 12-10 | ICTSEL<2:0>: Input Capture Timer Select bits                                                                                                                |

|           | 111 = Peripheral clock (FP) is the clock source of the ICx                                                                                                  |

|           | 110 = Reserved                                                                                                                                              |

|           | 101 = Reserved                                                                                                                                              |

|           | 100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)<br>011 = T5CLK is the clock source of the ICx                          |

|           | 010 = T4CLK is the clock source of the ICx                                                                                                                  |

|           | 001 = T2CLK is the clock source of the ICx                                                                                                                  |

|           | 000 = T3CLK is the clock source of the ICx                                                                                                                  |

| bit 9-7   | Unimplemented: Read as '0'                                                                                                                                  |

| bit 6-5   | ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)                                                    |

|           | 11 = Interrupt on every fourth capture event                                                                                                                |

|           | 10 = Interrupt on every third capture event                                                                                                                 |

|           | 01 = Interrupt on every second capture event<br>00 = Interrupt on every capture event                                                                       |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                    |

| bit 4     | 1 = Input capture buffer overflow occurred                                                                                                                  |

|           | 0 = No input capture buffer overflow occurred                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                |

|           | 1 = Input capture buffer is not empty, at least one more capture value can be read                                                                          |

|           | 0 = Input capture buffer is empty                                                                                                                           |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                    |

|           | 111 = Input capture functions as interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable)        |

|           | 110 = Unused (module is disabled)                                                                                                                           |

|           | 101 = Capture mode, every 16th rising edge (Prescaler Capture mode)                                                                                         |

|           | <ul> <li>100 = Capture mode, every 4th rising edge (Prescaler Capture mode)</li> <li>011 = Capture mode, every rising edge (Simple Capture mode)</li> </ul> |

|           | 010 = Capture mode, every falling edge (Simple Capture mode)                                                                                                |

|           | 001 = Capture mode, every edge rising and falling (Edge Detect mode (ICI<1:0>) is not used in this mode)                                                    |

|           | 000 = Input capture module is turned off                                                                                                                    |

| R/W-0           | U-0   | U-0              | U-0   | U-0              | U-0              | R/W-0              | R/W-0   |  |  |  |

|-----------------|-------|------------------|-------|------------------|------------------|--------------------|---------|--|--|--|

| CHPCLKEN        | —     | —                | —     | —                | —                | CHOPC              | LK<9:8> |  |  |  |

| bit 15          |       |                  |       |                  |                  |                    | bit 8   |  |  |  |

|                 |       |                  |       |                  |                  |                    |         |  |  |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0              | R/W-0   |  |  |  |

| CHOPCLK<7:0>    |       |                  |       |                  |                  |                    |         |  |  |  |

| bit 7           |       |                  |       |                  |                  |                    | bit 0   |  |  |  |

|                 |       |                  |       |                  |                  |                    |         |  |  |  |

| Legend:         |       |                  |       |                  |                  |                    |         |  |  |  |

| R = Readable I  | bit   | W = Writable     | bit   | U = Unimplei     | mented bit, read | ad as '0'          |         |  |  |  |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | eared            | x = Bit is unknown |         |  |  |  |

|                 |       |                  |       |                  |                  |                    |         |  |  |  |

## REGISTER 16-5: CHOP: PWMx CHOP CLOCK GENERATOR REGISTER

#### REGISTER 16-6: MDC: PWMx MASTER DUTY CYCLE REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|------------------------------------|-------|-------|-------|-----------------------------------------|-------|-------|-------|--|--|

|                                    |       |       | MDC   | <15:8>                                  |       |       |       |  |  |

| bit 15                             |       |       |       |                                         |       |       | bit 8 |  |  |

|                                    |       |       |       |                                         |       |       |       |  |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                    |       |       | MD    | C<7:0>                                  |       |       |       |  |  |

| bit 7                              |       |       |       |                                         |       |       | bit 0 |  |  |

|                                    |       |       |       |                                         |       |       |       |  |  |

| Legend:                            |       |       |       |                                         |       |       |       |  |  |

| R = Readable bit W = Writable bit  |       |       |       | U = Unimplemented bit, read as '0'      |       |       |       |  |  |

| -n = Value at POR (1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |

bit 15-0 MDC<15:0>: PWMx Master Duty Cycle Value bits

# 17.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data.

The operational features of the QEI module include:

- 32-Bit Position Counter

- 32-Bit Index Pulse Counter

- 32-Bit Interval Timer

- 16-Bit Velocity Counter

- 32-Bit Position Initialization/Capture/Compare High register

- 32-Bit Position Compare Low register

- x4 Quadrature Count mode

- External Up/Down Count mode

- External Gated Count mode

- External Gated Timer mode

- Internal Timer mode

Figure 17-1 illustrates the QEI block diagram.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 17-17: INT1TMRH: INTERVAL 1 TIMER HIGH WORD REGISTER

| R/W-0                                                                      | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|----------------------------------------------------------------------------|-------|----------------|-------|--------------|-----------------|----------|-------|

|                                                                            |       |                | INTTM | R<31:24>     |                 |          |       |

| bit 15                                                                     |       |                |       |              |                 |          | bit 8 |

|                                                                            |       |                |       |              |                 |          |       |

| R/W-0                                                                      | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0           | R/W-0    | R/W-0 |

|                                                                            |       |                | INTTM | R<23:16>     |                 |          |       |

| bit 7                                                                      |       |                |       |              |                 |          | bit 0 |

|                                                                            |       |                |       |              |                 |          |       |

| Legend:                                                                    |       |                |       |              |                 |          |       |

| R = Readable                                                               | bit   | W = Writable b | oit   | U = Unimplem | nented bit, rea | d as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |                |       |              | nown            |          |       |

bit 15-0 INTTMR<31:16>: High Word Used to Form 32-Bit Interval Timer Register (INT1TMR) bits

#### REGISTER 17-18: INT1TMRL: INTERVAL 1 TIMER LOW WORD REGISTER

| R/W-0                                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|----------------------------------------------------------------------------|-------|-------|-------|----------|-------|-------|-------|

|                                                                            |       |       | INTTM | IR<15:8> |       |       |       |

| bit 15                                                                     |       |       |       |          |       |       | bit 8 |

|                                                                            |       |       |       |          |       |       |       |

| R/W-0                                                                      | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|                                                                            |       |       | INTT  | /IR<7:0> |       |       |       |

| bit 7                                                                      |       |       |       |          |       |       | bit 0 |

|                                                                            |       |       |       |          |       |       |       |

| Legend:                                                                    |       |       |       |          |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |       |       |       |          |       |       |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |       |       |          | nown  |       |       |

bit 15-0 INTTMR<15:0>: Low Word Used to Form 32-Bit Interval Timer Register (INT1TMR) bits

| U-0                 | U-0                                                                                                                                | U-0                                                                                                                                                                                                                                              | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------|----------------------|----------------------|----------------------|--|--|--|--|

|                     | —                                                                                                                                  | _                                                                                                                                                                                                                                                | DISSCK                                | DISSDO               | MODE16               | SMP                  | CKE <sup>(1)</sup>   |  |  |  |  |

| bit 15              |                                                                                                                                    | •                                                                                                                                                                                                                                                |                                       | •                    | •                    | •                    | bit                  |  |  |  |  |

| R/W-0               | R/W-0                                                                                                                              | R/W-0                                                                                                                                                                                                                                            | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |  |  |  |  |

| SSEN <sup>(2)</sup> | CKP                                                                                                                                | MSTEN                                                                                                                                                                                                                                            | SPRE2 <sup>(3)</sup>                  | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |  |  |  |  |

| bit 7               | CKF                                                                                                                                | WIGTEN                                                                                                                                                                                                                                           | SFREZ 7                               | SFREI?               | SFREU 7              | FFREN                | bit                  |  |  |  |  |

|                     |                                                                                                                                    |                                                                                                                                                                                                                                                  |                                       |                      |                      |                      |                      |  |  |  |  |

| Legend:             |                                                                                                                                    |                                                                                                                                                                                                                                                  |                                       |                      |                      |                      |                      |  |  |  |  |

| R = Readabl         | le bit                                                                                                                             | W = Writable                                                                                                                                                                                                                                     | bit                                   | U = Unimpler         | mented bit, read     | d as '0'             |                      |  |  |  |  |

| -n = Value at       | t POR                                                                                                                              | '1' = Bit is se                                                                                                                                                                                                                                  | t                                     | '0' = Bit is cle     | ared                 | x = Bit is unkr      | nown                 |  |  |  |  |

|                     |                                                                                                                                    |                                                                                                                                                                                                                                                  |                                       |                      |                      |                      |                      |  |  |  |  |

| bit 15-13           | Unimplemen                                                                                                                         | ted: Read as                                                                                                                                                                                                                                     | 0'                                    |                      |                      |                      |                      |  |  |  |  |

| bit 12              |                                                                                                                                    |                                                                                                                                                                                                                                                  | bit (SPIx Mas                         | -                    | ()                   |                      |                      |  |  |  |  |

|                     |                                                                                                                                    | PIx clock is di                                                                                                                                                                                                                                  | sabled, pin fun                       | ctions as I/O        |                      |                      |                      |  |  |  |  |

| oit 11              |                                                                                                                                    | able SDOx Pir                                                                                                                                                                                                                                    |                                       |                      |                      |                      |                      |  |  |  |  |

|                     |                                                                                                                                    |                                                                                                                                                                                                                                                  |                                       | oin functions as     | s I/O                |                      |                      |  |  |  |  |

|                     | <ul> <li>1 = SDOx pin is not used by the module; pin functions as I/O</li> <li>0 = SDOx pin is controlled by the module</li> </ul> |                                                                                                                                                                                                                                                  |                                       |                      |                      |                      |                      |  |  |  |  |

| bit 10              | MODE16: Wo                                                                                                                         | ord/Byte Comn                                                                                                                                                                                                                                    | nunication Sele                       | ect bit              |                      |                      |                      |  |  |  |  |

|                     |                                                                                                                                    | 1 = Communication is word-wide (16 bits)                                                                                                                                                                                                         |                                       |                      |                      |                      |                      |  |  |  |  |

|                     |                                                                                                                                    | ication is byte-                                                                                                                                                                                                                                 | . ,                                   |                      |                      |                      |                      |  |  |  |  |

| bit 9               | SMP: SPIx Data Input Sample Phase bit                                                                                              |                                                                                                                                                                                                                                                  |                                       |                      |                      |                      |                      |  |  |  |  |

|                     | Master mode                                                                                                                        | -                                                                                                                                                                                                                                                | end of data o                         | utout time           |                      |                      |                      |  |  |  |  |

|                     |                                                                                                                                    |                                                                                                                                                                                                                                                  |                                       |                      |                      |                      |                      |  |  |  |  |

|                     | 0 = Input data is sampled at middle of data output time<br><u>Slave mode:</u>                                                      |                                                                                                                                                                                                                                                  |                                       |                      |                      |                      |                      |  |  |  |  |

|                     | SMP must be cleared when SPIx is used in Slave mode.                                                                               |                                                                                                                                                                                                                                                  |                                       |                      |                      |                      |                      |  |  |  |  |

| bit 8               |                                                                                                                                    | lock Edge Sele                                                                                                                                                                                                                                   |                                       |                      |                      |                      |                      |  |  |  |  |

|                     |                                                                                                                                    | <ul> <li>1 = Serial output data changes on transition from active clock state to Idle clock state (refer to bit 6)</li> <li>0 = Serial output data changes on transition from Idle clock state to active clock state (refer to bit 6)</li> </ul> |                                       |                      |                      |                      |                      |  |  |  |  |

| bit 7               |                                                                                                                                    |                                                                                                                                                                                                                                                  | bit (Slave mod                        |                      |                      | ve clock state (I    |                      |  |  |  |  |

|                     |                                                                                                                                    | sused for Slav                                                                                                                                                                                                                                   |                                       |                      |                      |                      |                      |  |  |  |  |

|                     |                                                                                                                                    |                                                                                                                                                                                                                                                  |                                       | is controlled b      | by port function     |                      |                      |  |  |  |  |

| bit 6               | CKP: Clock F                                                                                                                       | Polarity Select                                                                                                                                                                                                                                  | bit                                   |                      |                      |                      |                      |  |  |  |  |

|                     |                                                                                                                                    |                                                                                                                                                                                                                                                  | nigh level; activ<br>ow level; active |                      |                      |                      |                      |  |  |  |  |

| bit 5               | MSTEN: Mas                                                                                                                         | ter Mode Enat                                                                                                                                                                                                                                    | ole bit                               |                      |                      |                      |                      |  |  |  |  |

|                     | 1 = Master m<br>0 = Slave mo                                                                                                       |                                                                                                                                                                                                                                                  |                                       |                      |                      |                      |                      |  |  |  |  |

| Note 1: T           | he CKE bit is not                                                                                                                  | used in Frame                                                                                                                                                                                                                                    | d SPI modes. I                        | Program this bi      | it to '0' for Fram   | ed SPI modes (       | FRMEN = 1            |  |  |  |  |

|                     | his bit must be cl                                                                                                                 |                                                                                                                                                                                                                                                  |                                       |                      |                      |                      |                      |  |  |  |  |

| <b>0</b>            |                                                                                                                                    |                                                                                                                                                                                                                                                  |                                       |                      |                      |                      |                      |  |  |  |  |

### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

#### REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

| bit 7-5 | SSRC<2:0>: Sample Trigger Source Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If SSRCG = 1:<br>111 = Reserved<br>110 = PTGO15 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>101 = PTGO14 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>100 = PTGO13 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>011 = PTGO12 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion <sup>(2)</sup> |

|         | If SSRCG = 0:<br>111 = Internal counter ends sampling and starts conversion (auto-convert)<br>110 = CTMU ends sampling and starts conversion<br>101 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>101 - Reserved</li> <li>100 = Timer5 compare ends sampling and starts conversion</li> <li>011 = PWM primary Special Event Trigger ends sampling and starts conversion</li> <li>010 = Timer3 compare ends sampling and starts conversion</li> <li>001 = Active transition on the INT0 pin ends sampling and starts conversion</li> <li>000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)</li> </ul>                                                                                                                                                                                                                                                                        |

| bit 4   | SSRCG: Sample Trigger Source Group bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | See SSRC<2:0> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 3   | <ul> <li>SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS&lt;1:0&gt; = 01 or 1x)</li> <li><u>In 12-bit mode (AD21B = 1), SIMSAM is Unimplemented and is Read as '0':</u></li> <li>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01)</li> <li>0 = Samples multiple channels individually in sequence</li> </ul>                                                                                                                                                                                                                                                                                              |

| bit 2   | ASAM: ADC1 Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Sampling begins immediately after the last conversion; SAMP bit is auto-set</li> <li>0 = Sampling begins when the SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 1   | SAMP: ADC1 Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = ADC Sample-and-Hold amplifiers are sampling</li> <li>0 = ADC Sample-and-Hold amplifiers are holding</li> <li>If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1. If SSRC&lt;2:0&gt; = 000, software can write '0' to end sampling and start conversion. If SSRC&lt;2:0&gt; ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>                                                                                                                                                                                                                                                                                         |

| bit 0   | DONE: ADC1 Conversion Status bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = ADC conversion cycle has completed</li> <li>0 = ADC conversion has not started or is in progress</li> <li>Automatically set by hardware when the ADC conversion is complete. Software can write '0' to clear the DONE status bit (software is not allowed to write '1'). Clearing this bit does NOT affect any operation in progress. Automatically cleared by hardware at the start of a new conversion.</li> </ul>                                                                                                                                                                                                                                                                                       |

| Note 1: | See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

- 2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- **3:** Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

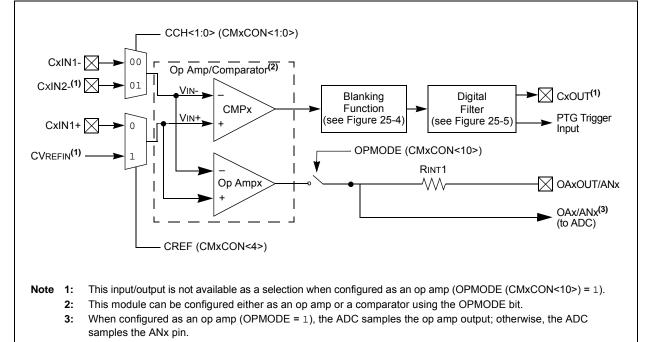

# 25.0 OP AMP/COMPARATOR MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain up to four comparators, which can be configured in various ways. Comparators, CMP1, CMP2 and CMP3, also have the option to be configured as op amps, with the output being brought to an external pin for gain/filtering connections. As shown in Figure 25-1, individual comparator options are specified by the comparator module's Special Function Register (SFR) control bits.

Note: Op Amp/Comparator 3 is not available on the dsPIC33EPXXXGP502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

These options allow users to:

- · Select the edge for trigger and interrupt generation

- · Configure the comparator voltage reference

- · Configure output blanking and masking

- Configure as a comparator or op amp (CMP1, CMP2 and CMP3 only)

Note: Not all op amp/comparator input/output connections are available on all devices. See the "Pin Diagrams" section for available connections.

#### FIGURE 25-1: OP AMP/COMPARATOR x MODULE BLOCK DIAGRAM (MODULES 1, 2 AND 3)

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | R/W-0                                                                                            | U-0              | U-0                                    | U-0              | R/W-0                        | U-0             | U-0            |  |  |  |

|-----------------|--------------------------------------------------------------------------------------------------|------------------|----------------------------------------|------------------|------------------------------|-----------------|----------------|--|--|--|

|                 | CVR2OE <sup>(1)</sup>                                                                            | _                | _                                      | _                | VREFSEL                      | _               | _              |  |  |  |

| bit 15          |                                                                                                  |                  |                                        |                  |                              |                 | bit            |  |  |  |

| <b>D</b> 444 0  | DAALO                                                                                            | DAALO            |                                        | <b>D</b> 444 0   | DAALO                        | DANA            | <b>D</b> 444 0 |  |  |  |

| R/W-0           | R/W-0                                                                                            | R/W-0            | R/W-0                                  | R/W-0            | R/W-0                        | R/W-0           | R/W-0          |  |  |  |

| CVREN           | CVR10E <sup>(1)</sup>                                                                            | CVRR             | CVRSS <sup>(2)</sup>                   | CVR3             | CVR2                         | CVR1            | CVR0           |  |  |  |

| bit 7           |                                                                                                  |                  |                                        |                  |                              |                 | bit            |  |  |  |

| Legend:         |                                                                                                  |                  |                                        |                  |                              |                 |                |  |  |  |

| R = Readable    | bit                                                                                              | W = Writable     | bit                                    | U = Unimple      | mented bit, read             | as '0'          |                |  |  |  |

| -n = Value at F | POR                                                                                              | '1' = Bit is set | t                                      | '0' = Bit is cle | eared                        | x = Bit is unkn | iown           |  |  |  |

|                 |                                                                                                  |                  |                                        |                  |                              |                 |                |  |  |  |

| bit 15          | Unimplement                                                                                      |                  |                                        |                  |                              |                 |                |  |  |  |

| bit 14          |                                                                                                  | •                | ige Reference                          | •                | ble bit <sup>(1)</sup>       |                 |                |  |  |  |

|                 |                                                                                                  |                  | nected to the C<br>onnected from       |                  | nin                          |                 |                |  |  |  |

| bit 13-11       | Unimplement                                                                                      |                  |                                        |                  | <b>F</b>                     |                 |                |  |  |  |

| bit 10          | -                                                                                                |                  | age Reference                          | e Select bit     |                              |                 |                |  |  |  |

|                 | 1 = CVREFIN =                                                                                    | -                | C                                      |                  |                              |                 |                |  |  |  |

|                 | 0 = CVREFIN is                                                                                   | s generated by   | y the resistor ne                      | etwork           |                              |                 |                |  |  |  |

| bit 9-8         | Unimplement                                                                                      | ted: Read as '   | 0'                                     |                  |                              |                 |                |  |  |  |

| bit 7           |                                                                                                  |                  | e Reference E                          |                  |                              |                 |                |  |  |  |

|                 |                                                                                                  |                  | erence circuit is<br>erence circuit is |                  | wn                           |                 |                |  |  |  |

| bit 6           | CVR1OE: Co                                                                                       | mparator Volta   | ige Reference                          | 1 Output Ena     | ble bit <sup>(1)</sup>       |                 |                |  |  |  |

|                 |                                                                                                  |                  | n the CVREF1C                          |                  | n                            |                 |                |  |  |  |

| bit 5           | <b>CVRR:</b> Comparator Voltage Reference Range Selection bit                                    |                  |                                        |                  |                              |                 |                |  |  |  |

|                 | 1 = CVRSRC/2<br>0 = CVRSRC/3                                                                     |                  |                                        |                  |                              |                 |                |  |  |  |

| bit 4           | CVRSS: Com                                                                                       | parator Voltag   | e Reference S                          | ource Selecti    | on bit <sup>(2)</sup>        |                 |                |  |  |  |

|                 |                                                                                                  | 0                | erence source,<br>erence source,       | · ·              | ref+) – (AVss)<br>/dd – AVss |                 |                |  |  |  |

| bit 3-0         | <b>CVR&lt;3:0&gt;</b> Comparator Voltage Reference Value Selection $0 \le CVR<3:0 > \le 15$ bits |                  |                                        |                  |                              |                 |                |  |  |  |

|                 | When CVRR = CVREFIN = (CV                                                                        |                  | (CVRSRC)                               |                  |                              |                 |                |  |  |  |

|                 | When CVRR = CVREFIN = (CV                                                                        | = 0:             |                                        | $(\mathbf{C})$   |                              |                 |                |  |  |  |

#### REGISTER 25-7: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

- 2: In order to operate with CVRSS = 1, at least one of the comparator modules must be enabled.

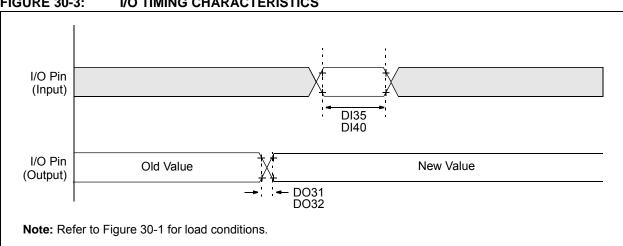

#### **FIGURE 30-3: I/O TIMING CHARACTERISTICS**

#### TABLE 30-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |   |    |     | +85°C for Industrial |

|--------------------|--------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|-----|----------------------|

| Param<br>No.       | Symbol | Characteristic                    | Min. Typ. <sup>(1)</sup> Max. Units Conditions                                                                                                                                                                  |   |    |     |                      |

| DO31               | TioR   | Port Output Rise Time             |                                                                                                                                                                                                                 | 5 | 10 | ns  |                      |

| DO32               | TIOF   | Port Output Fall Time             | — 5 10 ns                                                                                                                                                                                                       |   |    |     |                      |