Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 512КВ (170К х 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

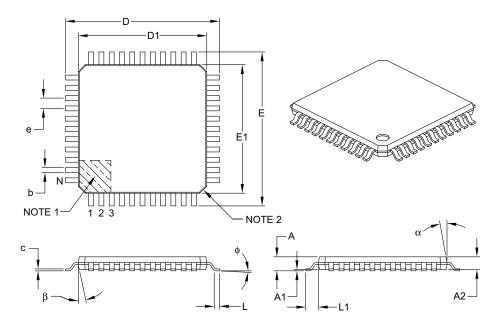

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc202-i-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

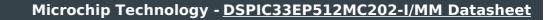

### **Pin Diagrams (Continued)**

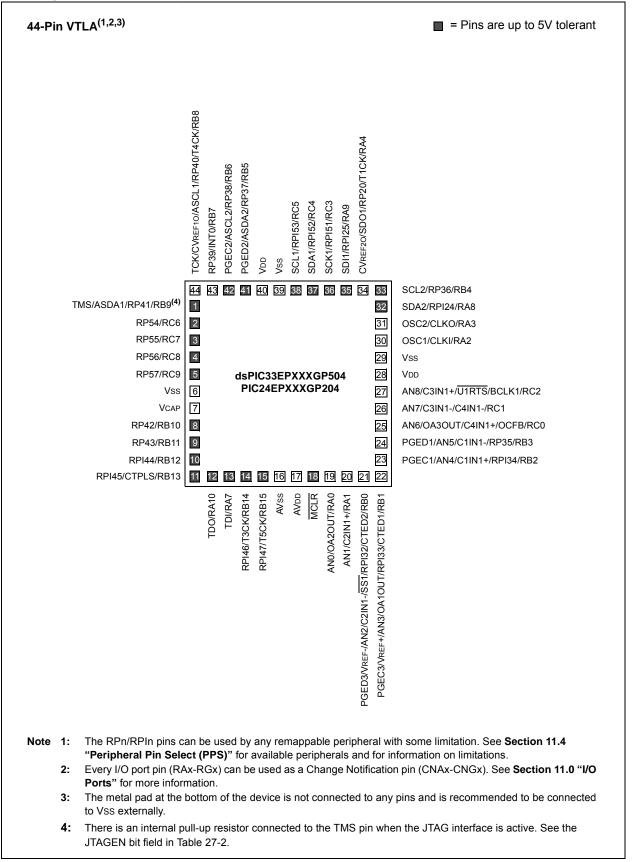

# FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33EP32MC20X/50X AND dsPIC33EP32GP50X DEVICES

| IABLE 4-2  | 23: E                 | CAN1 I | REGIST | ER MA  | P WHE  | N WIN  | (CICIE | <l1<0></l1<0> | •) = 1 FC | OR dsPIC | 33EPX    | XXMC/G | P50X D | EVICES | ONLY ( |       | NUED) |               |

|------------|-----------------------|--------|--------|--------|--------|--------|--------|---------------|-----------|----------|----------|--------|--------|--------|--------|-------|-------|---------------|

| File Name  | Addr                  | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9         | Bit 8     | Bit 7    | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11EID | XF11EID 046E EID<7:0> |        |        |        |        |        |        |               |           | xxxx     |          |        |        |        |        |       |       |               |

| C1RXF12SID | 0470                  |        |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | _      | EID<1 | 7:16> | xxxx          |

| C1RXF12EID | 0472                  |        |        |        | EID<   | :15:8> |        |               |           | EID<7:0> |          |        |        |        |        | xxxx  |       |               |

| C1RXF13SID | 0474                  |        |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF13EID | 0476                  |        |        |        | EID<   | :15:8> |        |               |           | EID<7:0> |          |        |        |        |        | xxxx  |       |               |

| C1RXF14SID | 0478                  |        |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A                  |        |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF15SID | 047C                  |        |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | _      | EID<1 | 7:16> | xxxx          |

| C1RXF15EID | 047E                  |        |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

#### ECANI DECISTED MAD WHEN WIN (CICTDI 1 -0.) 1 EOD doDIC22EDXXXMC/CDE0X DEVICES ONLY (CONTINUED) TARIE 1 22.

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory and to program two instruction words at a time. See the General Purpose and Motor Control Family tables (Table 1 and Table 2, respectively) for the page sizes of each device.

For more information on erasing and programming Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

### 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time) in Table 30-14 in **Section 30.0 "Electrical Characteristics"**.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to **Flash Programming**" (DS70609) in the "*dsPIC33/PIC24 Family Reference Manual*" for details and codes examples on programming using RTSP.

### 5.4 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

### 5.4.1 KEY RESOURCES

- "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### 5.5 Control Registers

Four SFRs are used to erase and write the program Flash memory: NVMCON, NVMKEY, NVMADRH and NVMADRL.

The NVMCON register (Register 5-1) enables and initiates Flash memory erase and write operations.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRH and NVMADRL. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations or the selected page for erase operations.

The NVMADRH register is used to hold the upper 8 bits of the EA, while the NVMADRL register is used to hold the lower 16 bits of the EA.

## **REGISTER 8-7:** DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0                                                                      | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|----------------------------------------------------------------------------|-------|--------------|-------|--------------|------------------|----------|-------|

|                                                                            |       |              | PAD   | <15:8>       |                  |          |       |

| bit 15                                                                     |       |              |       |              |                  |          | bit 8 |

|                                                                            |       |              |       |              |                  |          |       |

| R/W-0                                                                      | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

|                                                                            |       |              | PAE   | )<7:0>       |                  |          |       |

| bit 7                                                                      |       |              |       |              |                  |          | bit 0 |

|                                                                            |       |              |       |              |                  |          |       |

| Legend:                                                                    |       |              |       |              |                  |          |       |

| R = Readable                                                               | bit   | W = Writable | bit   | U = Unimplen | nented bit, read | d as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |       |              |       |              |                  |          | nown  |

### bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

### REGISTER 8-8: DMAXCNT: DMA CHANNEL X TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0                                                                      | U-0   | R/W-0            | R/W-0 | R/W-0                                   | R/W-0            | R/W-0 | R/W-0 |

|--------------------------------------------------------------------------|-------|------------------|-------|-----------------------------------------|------------------|-------|-------|

| —                                                                        |       |                  |       | CNT<                                    | 13:8> <b>(2)</b> |       |       |

| bit 15                                                                   |       |                  |       |                                         |                  |       | bit 8 |

| R/W-0                                                                    | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0            | R/W-0 | R/W-0 |

|                                                                          |       |                  | CNT<  | <7:0> <b>(2)</b>                        |                  |       |       |

| bit 7                                                                    |       |                  |       |                                         |                  |       | bit 0 |

| Legend:                                                                  |       |                  |       |                                         |                  |       |       |

| R = Readable bit $W$ = Writable bit $U$ = Unimplemented bit, read as '0' |       |                  |       |                                         |                  |       |       |

| -n = Value at P                                                          | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                  |       |       |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

### 11.4.4.2 Output Mapping

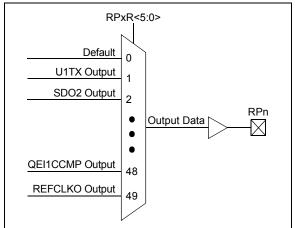

In contrast to inputs, the outputs of the Peripheral Pin Select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 6-bit fields, with each set associated with one RPn pin (see Register 11-18 through Register 11-27). The value of the bit field corresponds to one of the peripherals and that peripheral's output is mapped to the pin (see Table 11-3 and Figure 11-3).

A null output is associated with the output register Reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

### FIGURE 11-3: MULTIPLEXING REMAPPABLE OUTPUT FOR RPn

### 11.4.4.3 Mapping Limitations

The control schema of the peripheral select pins is not limited to a small range of fixed peripheral configurations. There are no mutual or hardware-enforced lockouts between any of the peripheral mapping SFRs. Literally any combination of peripheral mappings across any or all of the RPn pins is possible. This includes both many-toone and one-to-many mappings of peripheral inputs and outputs to pins. While such mappings may be technically possible from a configuration point of view, they may not be supportable from an electrical point of view.

### TABLE 11-3: OUTPUT SELECTION FOR REMAPPABLE PINS (RPn)

| Function                | RPxR<5:0> | Output Name                                   |

|-------------------------|-----------|-----------------------------------------------|

| Default PORT            | 000000    | RPn tied to Default Pin                       |

| U1TX                    | 000001    | RPn tied to UART1 Transmit                    |

| U2TX                    | 000011    | RPn tied to UART2 Transmit                    |

| SDO2                    | 001000    | RPn tied to SPI2 Data Output                  |

| SCK2                    | 001001    | RPn tied to SPI2 Clock Output                 |

| SS2                     | 001010    | RPn tied to SPI2 Slave Select                 |

| C1TX <sup>(2)</sup>     | 001110    | RPn tied to CAN1 Transmit                     |

| OC1                     | 010000    | RPn tied to Output Compare 1 Output           |

| OC2                     | 010001    | RPn tied to Output Compare 2 Output           |

| OC3                     | 010010    | RPn tied to Output Compare 3 Output           |

| OC4                     | 010011    | RPn tied to Output Compare 4 Output           |

| C1OUT                   | 011000    | RPn tied to Comparator Output 1               |

| C2OUT                   | 011001    | RPn tied to Comparator Output 2               |

| C3OUT                   | 011010    | RPn tied to Comparator Output 3               |

| SYNCO1 <sup>(1)</sup>   | 101101    | RPn tied to PWM Primary Time Base Sync Output |

| QEI1CCMP <sup>(1)</sup> | 101111    | RPn tied to QEI 1 Counter Comparator Output   |

| REFCLKO                 | 110001    | RPn tied to Reference Clock Output            |

| C4OUT                   | 110010    | RPn tied to Comparator Output 4               |

Note 1: This function is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This function is available in dsPIC33EPXXXGP/MC50X devices only.

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|--------------|------------------------------------------|------------------------------------------------------------------------------|---------------|-------------------|---------------|-----------------|--------|

| —            |                                          |                                                                              |               | SCK2INR<6:0       | >             |                 |        |

| bit 15       |                                          |                                                                              |               |                   |               |                 | bit 8  |

|              |                                          |                                                                              |               |                   | 5444.6        | <b>D</b> 444 A  | 5444.6 |

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|              |                                          |                                                                              |               | SDI2R<6:0>        |               |                 |        |

| bit 7        |                                          |                                                                              |               |                   |               |                 | bit 0  |

|              |                                          |                                                                              |               |                   |               |                 |        |

| Legend:      |                                          |                                                                              |               |                   |               |                 |        |

| R = Readab   |                                          | W = Writable                                                                 |               | U = Unimplen      |               |                 |        |

| -n = Value a | t POR                                    | '1' = Bit is set                                                             |               | '0' = Bit is clea | ared          | x = Bit is unkr | nown   |

|              |                                          | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss                     | P1            |                   |               |                 |        |

| bit 7        | Unimpleme                                | nted: Read as 'o                                                             | כי            |                   |               |                 |        |

| bit 6-0      | (see Table 1 <sup>^</sup><br>1111001 = I | : Assign SPI2 D<br>1-2 for input pin<br>nput tied to RPI<br>nput tied to CMI | selection num | ,                 | esponding RPi | ר Pin bits      |        |

### REGISTER 11-12: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

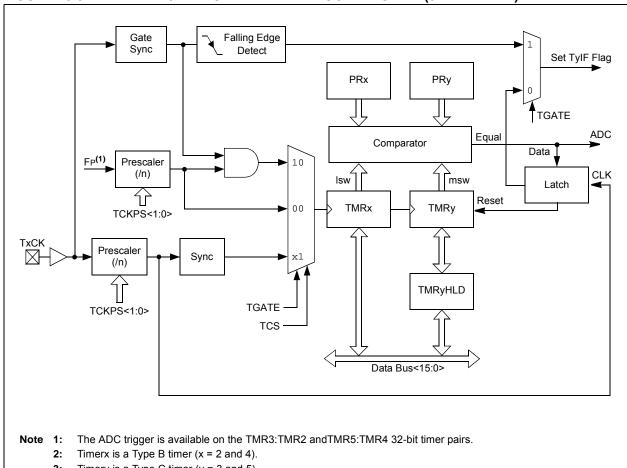

#### **FIGURE 13-3:** TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

3: Timery is a Type C timer (y = 3 and 5).

#### **Timerx/y Resources** 13.1

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/                                                                                      |

|       | wwwproducts/Devices.aspx?d<br>DocName=en555464                                                                 |

#### **KEY RESOURCES** 13.1.1

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| R/W-0         | R/W-0       | R/W-0                                                                                                                   | U-0        | U-0              | U-0             | U-0                | U-0    |  |  |  |  |

|---------------|-------------|-------------------------------------------------------------------------------------------------------------------------|------------|------------------|-----------------|--------------------|--------|--|--|--|--|

| FRMEN         | SPIFSD      | FRMPOL                                                                                                                  | —          | —                | _               | —                  | _      |  |  |  |  |

| bit 15        |             |                                                                                                                         |            |                  |                 |                    | bit 8  |  |  |  |  |

|               |             |                                                                                                                         |            |                  |                 |                    |        |  |  |  |  |

| U-0           | U-0         | U-0                                                                                                                     | U-0        | U-0              | U-0             | R/W-0              | R/W-0  |  |  |  |  |

| _             | <u> </u>    | —                                                                                                                       | _          |                  | _               | FRMDLY             | SPIBEN |  |  |  |  |

| bit 7         |             |                                                                                                                         |            |                  |                 |                    | bit 0  |  |  |  |  |

|               |             |                                                                                                                         |            |                  |                 |                    |        |  |  |  |  |

| Legend:       |             |                                                                                                                         |            |                  |                 |                    |        |  |  |  |  |

| R = Readable  | e bit       | W = Writable b                                                                                                          | pit        | U = Unimpler     | nented bit, rea | ad as '0'          |        |  |  |  |  |

| -n = Value at | POR         | '1' = Bit is set                                                                                                        |            | '0' = Bit is cle | ared            | x = Bit is unknown |        |  |  |  |  |

|               |             |                                                                                                                         |            |                  |                 |                    |        |  |  |  |  |

| bit 15        | FRMEN: Fra  | FRMEN: Framed SPIx Support bit<br>L = Framed SPIx support is enabled (SSx pin is used as Frame Sync pulse input/output) |            |                  |                 |                    |        |  |  |  |  |

|               |             | SPIx support is e<br>SPIx support is d                                                                                  |            | x pin is used as | Frame Sync      | oulse input/outpu  | it)    |  |  |  |  |

| bit 14        | SPIFSD: Fra | SPIFSD: Frame Sync Pulse Direction Control bit                                                                          |            |                  |                 |                    |        |  |  |  |  |

|               |             | ync pulse input (<br>ync pulse output                                                                                   |            |                  |                 |                    |        |  |  |  |  |

| bit 13        | FRMPOL: Fr  | FRMPOL: Frame Sync Pulse Polarity bit                                                                                   |            |                  |                 |                    |        |  |  |  |  |

|               |             | 1 = Frame Sync pulse is active-high                                                                                     |            |                  |                 |                    |        |  |  |  |  |

|               |             | ync pulse is activ                                                                                                      |            |                  |                 |                    |        |  |  |  |  |

| bit 12-2      | -           | nted: Read as '0                                                                                                        |            |                  |                 |                    |        |  |  |  |  |

| bit 1         |             | ame Sync Pulse                                                                                                          | -          |                  |                 |                    |        |  |  |  |  |

|               |             | ync pulse coincio<br>ync pulse preceo                                                                                   |            |                  |                 |                    |        |  |  |  |  |

| bit 0         | SPIBEN: En  | hanced Buffer Er                                                                                                        | nable bit  |                  |                 |                    |        |  |  |  |  |

|               |             | d buffer is enable                                                                                                      |            |                  |                 |                    |        |  |  |  |  |

|               | 0 = Enhance | d buffer is disabl                                                                                                      | ed (Standa | rd mode)         |                 |                    |        |  |  |  |  |

|               |             |                                                                                                                         |            |                  |                 |                    |        |  |  |  |  |

### REGISTER 18-3: SPIXCON2: SPIX CONTROL REGISTER 2

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0                              |       |              |       |                                        |       |        |       |  |  |

|------------------------------------|-------|--------------|-------|----------------------------------------|-------|--------|-------|--|--|

|                                    | R/W-0 | R/W-0        | R/W-0 | R/W-0                                  | R/W-0 | R/W-0  | R/W-0 |  |  |

|                                    | F7BF  | °<3:0>       |       |                                        | F6BF  | P<3:0> |       |  |  |

| bit 15                             |       |              |       |                                        |       |        | bit 8 |  |  |

| R/W-0                              | R/W-0 | R/W-0        | R/W-0 | R/W-0                                  | R/W-0 | R/W-0  | R/W-0 |  |  |

|                                    | F5BF  | °<3:0>       |       |                                        | F4BF  | P<3:0> |       |  |  |

| bit 7                              |       |              |       | •                                      |       |        | bit 0 |  |  |

| Legend:                            |       |              |       |                                        |       |        |       |  |  |

| R = Readable bi                    | t     | W = Writable | bit   | U = Unimplemented bit, read as '0'     |       |        |       |  |  |

| -n = Value at POR '1' = Bit is set |       |              |       | 0' = Bit is cleared x = Bit is unknown |       |        |       |  |  |

|          | 1110 = Filter hits received in RX Buffer 14                              |

|----------|--------------------------------------------------------------------------|

|          |                                                                          |

|          | •                                                                        |

|          | 0001 = Filter hits received in RX Buffer 1                               |

|          | 0000 = Filter hits received in RX Buffer 0                               |

| bit 11-8 | F6BP<3:0>: RX Buffer Mask for Filter 6 bits (same values as bits<15:12>) |

| bit 7-4  | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits<15:12>) |

| bit 3-0  | F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits<15:12>) |

### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0                              | R/W-0          | R/W-0           | R/W-0 |  |  |  |

|---------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------|----------------|-----------------|-------|--|--|--|

|               | F11BF                                              | P<3:0>                                                                                        |                                                |                                    | F10B           | SP<3:0>         |       |  |  |  |

| bit 15        |                                                    |                                                                                               |                                                |                                    |                |                 | bit 8 |  |  |  |

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0                              | R/W-0          | R/W-0           | R/W-0 |  |  |  |

|               | F9BP                                               | 2<3:0>                                                                                        |                                                | F8BP<3:0>                          |                |                 |       |  |  |  |

| bit 7         |                                                    |                                                                                               |                                                |                                    |                |                 | bit 0 |  |  |  |

| Legend:       |                                                    |                                                                                               |                                                |                                    |                |                 |       |  |  |  |

| R = Readabl   | le bit                                             | W = Writable                                                                                  | bit                                            | U = Unimplemented bit, read as '0' |                |                 |       |  |  |  |

| -n = Value at | t POR                                              | '1' = Bit is set                                                                              |                                                | '0' = Bit is cle                   | ared           | x = Bit is unkr | nown  |  |  |  |

| bit 15-12     | 1111 = Filter<br>1110 = Filter<br>•<br>•<br>•<br>• | RX Buffer Mar<br>hits received ir<br>hits received ir<br>hits received ir<br>hits received ir | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | iffer<br>4                         |                |                 |       |  |  |  |

| bit 11-8      | F10BP<3:0>                                         | : RX Buffer Ma                                                                                | sk for Filter 1                                | 0 bits (same val                   | ues as bits<1  | 5:12>)          |       |  |  |  |

| bit 7-4       | F9BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 9 b                               | oits (same value                   | s as bits<15:1 | 2>)             |       |  |  |  |

| bit 3-0       | F8BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 8 k                               | oits (same value                   | s as bits<15:1 | 2>)             |       |  |  |  |

|               |                                                    |                                                                                               |                                                |                                    |                |                 |       |  |  |  |

© 2011-2013 Microchip Technology Inc.

### FIGURE 22-1: CTMU BLOCK DIAGRAM

5: The switch connected to ADC CH0 is closed when IDISSEN (CTMUCON1<9>) = 1, and opened when IDISSEN = 0.

### 22.1 CTMU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

### 22.1.1 KEY RESOURCES

- "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

| R/W-0         | R/W-0                                                                                       | R/W-0                                                                                                                                                                                  | R/W-0                                                                                                                                    | R/W-0                                                                                    | R/W-0                                 | R/W-0           | R/W-0 |

|---------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------------|-----------------|-------|

| ITRIM5        | ITRIM4                                                                                      | ITRIM3                                                                                                                                                                                 | ITRIM2                                                                                                                                   | ITRIM1                                                                                   | ITRIM0                                | IRNG1           | IRNG0 |

| bit 15        |                                                                                             |                                                                                                                                                                                        |                                                                                                                                          |                                                                                          |                                       |                 | bit   |

|               |                                                                                             |                                                                                                                                                                                        |                                                                                                                                          |                                                                                          |                                       |                 |       |

| U-0           | U-0                                                                                         | U-0                                                                                                                                                                                    | U-0                                                                                                                                      | U-0                                                                                      | U-0                                   | U-0             | U-0   |

|               |                                                                                             | _                                                                                                                                                                                      | _                                                                                                                                        |                                                                                          | _                                     | _               | _     |

| bit 7         |                                                                                             |                                                                                                                                                                                        |                                                                                                                                          |                                                                                          |                                       |                 | bit   |

| Legend:       |                                                                                             |                                                                                                                                                                                        |                                                                                                                                          |                                                                                          |                                       |                 |       |

| R = Readabl   | e bit                                                                                       | W = Writable                                                                                                                                                                           | bit                                                                                                                                      | U = Unimplem                                                                             | nented bit, read                      | 1 as '0'        |       |

| -n = Value at | POR                                                                                         | '1' = Bit is set                                                                                                                                                                       |                                                                                                                                          | '0' = Bit is clea                                                                        |                                       | x = Bit is unkr | nown  |

|               |                                                                                             |                                                                                                                                                                                        |                                                                                                                                          |                                                                                          |                                       |                 |       |

|               | 011110 = Ma<br>•                                                                            |                                                                                                                                                                                        | e change nom                                                                                                                             |                                                                                          | 1 00 /0                               |                 |       |

|               | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | nimum positive<br>nimum positive<br>minal current c<br>nimum negative                                                                                                                  | change from r<br>change from r<br>output specified<br>e change from                                                                      | nominal current<br>nominal current<br>l by IRNG<1:0><br>nominal curren<br>nominal curren | + 4%<br>+ 2%<br>t – 2%                |                 |       |

|               | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                          | nimum positive<br>nimum positive<br>minal current o<br>nimum negative<br>nimum negative<br>ximum negative                                                                              | change from r<br>change from r<br>output specified<br>e change from<br>e change from<br>re change from                                   | nominal current<br>nominal current<br>l by IRNG<1:0><br>nominal curren                   | + 4%<br>+ 2%<br>-<br>t – 2%<br>t – 4% |                 |       |

| bit 9-8       | •<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                          | nimum positive<br>nimum positive<br>minal current o<br>nimum negative<br>nimum negative<br>ximum negative<br>current Source<br>ase Current <sup>(2)</sup><br>se Current <sup>(2)</sup> | change from r<br>change from r<br>output specified<br>e change from<br>e change from<br>re change from<br>re change from<br>Range Select | nominal current<br>nominal current<br>l by IRNG<1:0><br>nominal curren<br>nominal curren | + 4%<br>+ 2%<br>-<br>t – 2%<br>t – 4% |                 |       |

### REGISTER 22-3: CTMUICON: CTMU CURRENT CONTROL REGISTER

2: Refer to the CTMU Current Source Specifications (Table 30-56) in Section 30.0 "Electrical Characteristics" for the current range selection values.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0      | U-0                                      | U-0                                                                                                              | R/W-0                           | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |  |  |  |

|------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------|--------------------------|-----------------------|-----------------------|--|--|--|

| CH0NB      |                                          | _                                                                                                                | CH0SB4 <sup>(1)</sup>           | CH0SB3 <sup>(1)</sup> | CH0SB2 <sup>(1)</sup>    | CH0SB1 <sup>(1)</sup> | CH0SB0 <sup>(1)</sup> |  |  |  |

| bit 15     |                                          | -                                                                                                                |                                 |                       |                          |                       | bit 8                 |  |  |  |

|            |                                          |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

| R/W-0      | U-0                                      | U-0                                                                                                              | R/W-0                           | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |  |  |  |

| CH0NA      |                                          | _                                                                                                                | CH0SA4 <sup>(1)</sup>           | CH0SA3 <sup>(1)</sup> | CH0SA2 <sup>(1)</sup>    | CH0SA1 <sup>(1)</sup> | CH0SA0 <sup>(1)</sup> |  |  |  |

| bit 7      |                                          |                                                                                                                  |                                 |                       |                          |                       | bit C                 |  |  |  |

|            |                                          |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

| Legend:    |                                          |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

| R = Reada  |                                          | W = Writable                                                                                                     |                                 |                       | nented bit, read         |                       |                       |  |  |  |

| -n = Value | e at POR                                 | '1' = Bit is set                                                                                                 |                                 | '0' = Bit is clea     | ared                     | x = Bit is unkn       | own                   |  |  |  |

| hit 15     |                                          | annal O Nagativa                                                                                                 | Input Coloct for                | r Comple MUX          |                          |                       |                       |  |  |  |

| bit 15     |                                          | nannel 0 Negative<br>el 0 negative input                                                                         |                                 |                       |                          |                       |                       |  |  |  |

|            |                                          | el 0 negative input                                                                                              |                                 |                       |                          |                       |                       |  |  |  |

| bit 14-13  | Unimpleme                                | ented: Read as '0                                                                                                | )'                              |                       |                          |                       |                       |  |  |  |

| bit 12-8   | CH0SB<4:0                                | 0>: Channel 0 Po:                                                                                                | sitive Input Sele               | ect for Sample I      | MUXB bits <sup>(1)</sup> |                       |                       |  |  |  |

|            |                                          | pen; use this sele                                                                                               |                                 |                       |                          | ement                 |                       |  |  |  |

|            | 11110 <b>= Ch</b>                        | nannel 0 positive in                                                                                             | put is connected                | to the CTMU te        | mperature meas           | surement diode (      | (CTMU TEMP            |  |  |  |

|            |                                          | 11101 = Reserved                                                                                                 |                                 |                       |                          |                       |                       |  |  |  |

|            |                                          | 11100 = Reserved                                                                                                 |                                 |                       |                          |                       |                       |  |  |  |

|            |                                          | 11011 = Reserved<br>11010 = Channel 0 positive input is the output of OA3/AN6 <sup>(2,3)</sup>                   |                                 |                       |                          |                       |                       |  |  |  |

|            |                                          | nannel 0 positive i                                                                                              |                                 |                       |                          |                       |                       |  |  |  |

|            |                                          | nannel 0 positive i                                                                                              | input is the outp               | out of OA1/AN3        | (2)                      |                       |                       |  |  |  |

|            | 10111 <b>= Re</b>                        | served                                                                                                           |                                 |                       |                          |                       |                       |  |  |  |

|            | •                                        |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

|            | •                                        |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

|            | 10000 <b>= Re</b>                        |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

|            | 01111 = Ch                               | nannel 0 positive i                                                                                              | input is AN15 <sup>(3)</sup>    |                       |                          |                       |                       |  |  |  |

|            | 01110 = Cr                               | nannel 0 positive i<br>nannel 0 positive i                                                                       | input is AN14 <sup>(3)</sup>    |                       |                          |                       |                       |  |  |  |

|            | •                                        |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

|            | •                                        |                                                                                                                  |                                 |                       |                          |                       |                       |  |  |  |

|            | •                                        |                                                                                                                  | (2)                             |                       |                          |                       |                       |  |  |  |

|            | 00010 = Ch                               | 00010 = Channel 0 positive input is AN2 <sup>(3)</sup><br>00001 = Channel 0 positive input is AN1 <sup>(3)</sup> |                                 |                       |                          |                       |                       |  |  |  |

|            |                                          | nannel 0 positive i                                                                                              |                                 |                       |                          |                       |                       |  |  |  |

| bit 7      |                                          | nannel 0 Negative                                                                                                | •                               | r Samole MLIX         | Δ hit                    |                       |                       |  |  |  |

|            | CINIA. OI                                | lanner o Negative                                                                                                | •                               |                       | A DIL                    |                       |                       |  |  |  |

|            | 1 = Channell                             | 1 0 negative input                                                                                               | is AN1(1)                       |                       |                          |                       |                       |  |  |  |

|            |                                          | el 0 negative input<br>el 0 negative input                                                                       |                                 |                       |                          |                       |                       |  |  |  |

| bit 6-5    | 0 = Channe                               | el 0 negative input<br>el 0 negative input<br>ented: Read as '0                                                  | is Vrefl                        |                       |                          |                       |                       |  |  |  |

|            | 0 = Channe<br>Unimpleme<br>AN0 through A | el 0 negative input                                                                                              | is VREFL<br>,'<br>ed when compa |                       |                          |                       |                       |  |  |  |

### REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

3: See the "**Pin Diagrams**" section for the available analog channels for each device.

otherwise, the ANx input is used.

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax               | Description                                                | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|---------|-------------------------------|------------------------------------------------------------|---------------|-------------------------------|--------------------------|

| 9 BTG              |                      | BTG     | f,#bit4                       | Bit Toggle f                                               | 1             | 1                             | None                     |

|                    |                      | BTG     | Ws,#bit4                      | Bit Toggle Ws                                              | 1             | 1                             | None                     |

| 10                 | BTSC                 | BTSC    | f,#bit4                       | Bit Test f, Skip if Clear                                  | 1             | 1<br>(2 or 3)                 | None                     |

|                    |                      | BTSC    | Ws,#bit4                      | Bit Test Ws, Skip if Clear                                 | 1             | 1<br>(2 or 3)                 | None                     |

| 11                 | BTSS                 | BTSS    | f,#bit4                       | Bit Test f, Skip if Set                                    | 1             | 1<br>(2 or 3)                 | None                     |

|                    |                      | BTSS    | Ws,#bit4                      | Bit Test Ws, Skip if Set                                   | 1             | 1<br>(2 or 3)                 | None                     |

| 12                 | BTST                 | BTST    | f,#bit4                       | Bit Test f                                                 | 1             | 1                             | Z                        |

|                    |                      | BTST.C  | Ws,#bit4                      | Bit Test Ws to C                                           | 1             | 1                             | С                        |

|                    |                      | BTST.Z  | Ws,#bit4                      | Bit Test Ws to Z                                           | 1             | 1                             | Z                        |

|                    |                      | BTST.C  | Ws,Wb                         | Bit Test Ws <wb> to C</wb>                                 | 1             | 1                             | С                        |

|                    |                      | BTST.Z  | Ws,Wb                         | Bit Test Ws <wb> to Z</wb>                                 | 1             | 1                             | Z                        |

| 13                 | BTSTS                | BTSTS   | f,#bit4                       | Bit Test then Set f                                        | 1             | 1                             | Z                        |

|                    |                      | BTSTS.C | Ws,#bit4                      | Bit Test Ws to C, then Set                                 | 1             | 1                             | С                        |

|                    |                      | BTSTS.Z | Ws,#bit4                      | Bit Test Ws to Z, then Set                                 | 1             | 1                             | Z                        |

| 14                 | CALL                 | CALL    | lit23                         | Call subroutine                                            | 2             | 4                             | SFA                      |

|                    |                      | CALL    | Wn                            | Call indirect subroutine                                   | 1             | 4                             | SFA                      |

|                    |                      | CALL.L  | Wn                            | Call indirect subroutine (long address)                    | 1             | 4                             | SFA                      |

| 15                 | CLR                  | CLR     | f                             | f = 0x0000                                                 | 1             | 1                             | None                     |

|                    |                      | CLR     | WREG                          | WREG = 0x0000                                              | 1             | 1                             | None                     |

|                    |                      | CLR     | Ws                            | Ws = 0x0000                                                | 1             | 1                             | None                     |

|                    |                      | CLR     | Acc, Wx, Wxd, Wy, Wyd, AWB(1) | Clear Accumulator                                          | 1             | 1                             | OA,OB,SA,SB              |

| 16                 | CLRWDT               | CLRWDT  |                               | Clear Watchdog Timer                                       | 1             | 1                             | WDTO,Sleep               |

| 17                 | COM                  | СОМ     | f                             | $f = \bar{f}$                                              | 1             | 1                             | N,Z                      |

|                    |                      | COM     | f,WREG                        | WREG = $\overline{f}$                                      | 1             | 1                             | N,Z                      |

|                    |                      | СОМ     | Ws,Wd                         | $Wd = \overline{Ws}$                                       | 1             | 1                             | N,Z                      |

| 18                 | CP                   | CP      | f                             | Compare f with WREG                                        | 1             | 1                             | C,DC,N,OV,Z              |

|                    | 01                   | CP      | Wb,#lit8                      | Compare Wb with lit8                                       | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,Ws                         | Compare Wb with Ws (Wb – Ws)                               | 1             | 1                             | C,DC,N,OV,Z              |

| 19                 | CP0                  | CPO     | f                             | Compare f with 0x0000                                      | 1             | 1                             | C,DC,N,OV,Z              |

| 10                 | 010                  | CPO     | Ws                            | Compare Ws with 0x0000                                     | 1             | 1                             | C,DC,N,OV,Z              |

| 20                 | CPB                  | CPB     | f                             | Compare f with WREG, with Borrow                           | 1             | 1                             | C,DC,N,OV,Z              |

|                    | 012                  | CPB     | Wb,#lit8                      | Compare Wb with lit8, with Borrow                          | 1             | 1                             | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,Ws                         | Compare Wb with Ws, with Borrow $(Wb - Ws - \overline{C})$ | 1             | 1                             | C,DC,N,OV,Z              |

| 21                 | CPSEQ                | CPSEQ   | Wb,Wn                         | Compare Wb with Wn, skip if =                              | 1             | 1<br>(2 or 3)                 | None                     |

|                    | CPBEQ                | CPBEQ   | Wb,Wn,Expr                    | Compare Wb with Wn, branch if =                            | 1             | 1 (5)                         | None                     |

| 22                 | CPSGT                | CPSGT   | Wb,Wn                         | Compare Wb with Wn, skip if >                              | 1             | 1<br>(2 or 3)                 | None                     |

|                    | CPBGT                | CPBGT   | Wb,Wn,Expr                    | Compare Wb with Wn, branch if >                            | 1             | 1 (5)                         | None                     |

| 23                 | CPSLT                | CPSLT   | Wb,Wn                         | Compare Wb with Wn, skip if <                              | 1             | 1<br>(2 or 3)                 | None                     |

|                    | CPBLT                | CPBLT   | Wb,Wn,Expr                    | Compare Wb with Wn, branch if <                            | 1             | 1 (5)                         | None                     |

| 24                 | CPSNE                | CPSNE   | Wb,Wn                         | Compare Wb with Wn, skip if $\neq$                         | 1             | 1<br>(2 or 3)                 | None                     |

|                    | CPBNE                | CPBNE   | Wb,Wn,Expr                    | Compare Wb with Wn, branch if ≠                            | 1             | 1 (5)                         | None                     |

| TABLE 28-2: | <b>INSTRUCTION SET OVERVIEW (</b> | CONTINUED | ) |

|-------------|-----------------------------------|-----------|---|

|             |                                   | CONTINUED | , |

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| DC CH        | ARACTE | RISTICS                                 | (unless | d Operating<br>otherwise<br>g temperat | <b>stated)</b><br>ure -40° | C ≤ TA ≤ | <b>/ to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended                                                                               |

|--------------|--------|-----------------------------------------|---------|----------------------------------------|----------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic                          | Min.    | Тур.                                   | Max.                       | Units    | Conditions                                                                                                                                    |

|              | liL    | Input Leakage Current <sup>(1,2)</sup>  |         |                                        |                            |          |                                                                                                                                               |

| DI50         |        | I/O Pins 5V Tolerant <sup>(3)</sup>     | -1      | —                                      | +1                         | μA       | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in at high-impedance} \end{split}$                         |

| DI51         |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1      | _                                      | +1                         | μA       | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ Pin \text{ at high-impedance}, \\ -40^\circC \leq TA \leq +85^\circC \end{array}$ |

| DI51a        |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1      | _                                      | +1                         | μA       | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +85^{\circ}C$                                                 |

| DI51b        |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1      | _                                      | +1                         | μA       | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance,<br>-40°C ≤ TA ≤ +125°C                                                                      |

| DI51c        |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1      | _                                      | +1                         | μA       | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +125^{\circ}C$                                                |

| DI55         |        | MCLR                                    | -5      | —                                      | +5                         | μA       | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                      |

| DI56         |        | OSC1                                    | -5      | —                                      | +5                         | μΑ       | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ XT \text{ and } HS \text{ modes} \end{array}$                                     |

### TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- **5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

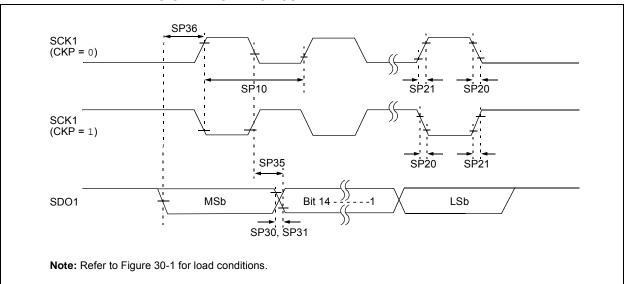

### FIGURE 30-23: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 1) TIMING CHARACTERISTICS

### TABLE 30-42: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                |

|--------------------|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max. | Units | Conditions                     |

| SP10               | FscP                  | Maximum SCK1 Frequency                       | —                                                                                                                                                                                                                                                                                       |                     | 15   | MHz   | (Note 3)                       |

| SP20               | TscF                  | SCK1 Output Fall Time                        | -                                                                                                                                                                                                                                                                                       | _                   | _    | ns    | See Parameter DO32<br>(Note 4) |

| SP21               | TscR                  | SCK1 Output Rise Time                        | —                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4)    |