Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 512KB (170K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 24K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                    |

| Supplier Device Package    | 28-SOIC                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc202t-e-so |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

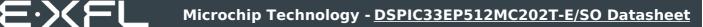

## **Pin Diagrams (Continued)**

| Pin Name <sup>(4)</sup>       | Pin<br>Type | Buffer<br>Type | PPS                            | Description                                                                                     |  |  |  |  |  |

|-------------------------------|-------------|----------------|--------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|

| C1IN1-                        | I           | Analog         | No                             | Op Amp/Comparator 1 Negative Input 1.                                                           |  |  |  |  |  |

| C1IN2-                        | I           | Analog         | Comparator 1 Negative Input 2. |                                                                                                 |  |  |  |  |  |

| C1IN1+                        | I           | Analog         | No                             | Op Amp/Comparator 1 Positive Input 1.                                                           |  |  |  |  |  |

| OA1OUT                        | 0           | Analog         | No                             | Op Amp 1 output.                                                                                |  |  |  |  |  |

| C1OUT                         | 0           | —              | Yes                            | s Comparator 1 output.                                                                          |  |  |  |  |  |

| C2IN1-                        | I           | Analog         | No                             | Op Amp/Comparator 2 Negative Input 1.                                                           |  |  |  |  |  |

| C2IN2-                        | I           | Analog         | No                             | Comparator 2 Negative Input 2.                                                                  |  |  |  |  |  |

| C2IN1+                        | I           | Analog         | No                             | Op Amp/Comparator 2 Positive Input 1.                                                           |  |  |  |  |  |

| OA2OUT                        | 0           | Analog         | No                             | Op Amp 2 output.                                                                                |  |  |  |  |  |

| C2OUT                         | 0           |                | Yes                            | Comparator 2 output.                                                                            |  |  |  |  |  |

| C3IN1-                        | I           | Analog         | No                             | Op Amp/Comparator 3 Negative Input 1.                                                           |  |  |  |  |  |

| C3IN2-                        | I           | Analog         | No                             | Comparator 3 Negative Input 2.                                                                  |  |  |  |  |  |

| C3IN1+                        | I           | Analog         | No                             | Op Amp/Comparator 3 Positive Input 1.                                                           |  |  |  |  |  |

| OA3OUT                        | 0           | Analog         | No                             | Op Amp 3 output.                                                                                |  |  |  |  |  |

| C3OUT                         | 0           |                | Yes                            | Comparator 3 output.                                                                            |  |  |  |  |  |

| C4IN1-                        | I.          | Analog         | No                             | Comparator 4 Negative Input 1.                                                                  |  |  |  |  |  |

| C4IN1+                        | I.          | Analog         | No                             | Comparator 4 Positive Input 1.                                                                  |  |  |  |  |  |

| C4OUT                         | 0           |                | Yes                            | Comparator 4 output.                                                                            |  |  |  |  |  |

| CVREF10                       | 0           | Analog         | No                             | Op amp/comparator voltage reference output.                                                     |  |  |  |  |  |

| CVREF20                       | 0           | Analog         | No                             | Op amp/comparator voltage reference divided by 2 output.                                        |  |  |  |  |  |

| PGED1                         | I/O         | ST             | No                             | Data I/O pin for Programming/Debugging Communication Channel 1.                                 |  |  |  |  |  |

| PGEC1                         | I           | ST             | No                             | Clock input pin for Programming/Debugging Communication Channel 1.                              |  |  |  |  |  |

| PGED2                         | I/O         | ST             | No                             | Data I/O pin for Programming/Debugging Communication Channel 2.                                 |  |  |  |  |  |

| PGEC2                         | I           | ST             | No                             | Clock input pin for Programming/Debugging Communication Channel 2.                              |  |  |  |  |  |

| PGED3                         | I/O         | ST             | No                             | Data I/O pin for Programming/Debugging Communication Channel 3.                                 |  |  |  |  |  |

| PGEC3                         | I           | ST             | No                             | Clock input pin for Programming/Debugging Communication Channel 3.                              |  |  |  |  |  |

| MCLR                          | I/P         | ST             | No                             | Master Clear (Reset) input. This pin is an active-low Reset to the device.                      |  |  |  |  |  |

| AVDD                          | Р           | Р              | No                             | Positive supply for analog modules. This pin must be connected at all times.                    |  |  |  |  |  |

| AVss                          | Р           | Р              | No                             | Ground reference for analog modules. This pin must be connected at all times.                   |  |  |  |  |  |

| Vdd                           | Р           |                | No                             | Positive supply for peripheral logic and I/O pins.                                              |  |  |  |  |  |

| VCAP                          | Р           |                | No                             | CPU logic filter capacitor connection.                                                          |  |  |  |  |  |

| Vss                           | Р           |                | No                             | Ground reference for logic and I/O pins.                                                        |  |  |  |  |  |

| VREF+                         | 1           | Analog         | No                             | Analog voltage reference (high) input.                                                          |  |  |  |  |  |

| VREF-                         | Ι           | Analog         | No                             | Analog voltage reference (low) input.                                                           |  |  |  |  |  |

| Legend: CMOS = C<br>ST = Schn | nitt Trigg  | jer input v    | with CI                        | or output     Analog = Analog input     P = Power       MOS levels     O = Output     I = Input |  |  |  |  |  |

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

PPS = Peripheral Pin Select

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

TTL = TTL input buffer

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS AND MICROCONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Familv Reference Manual", which is available from the Microchip web site (www.microchip.com)

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

## 2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

• VCAP

(see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins are used when external voltage reference for the ADC module is implemented

Note: The AVDD and AVSS pins must be connected, independent of the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of  $0.01 \ \mu\text{F}$  to  $0.001 \ \mu\text{F}$ . Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example,  $0.1 \ \mu\text{F}$  in parallel with  $0.001 \ \mu\text{F}$ .

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

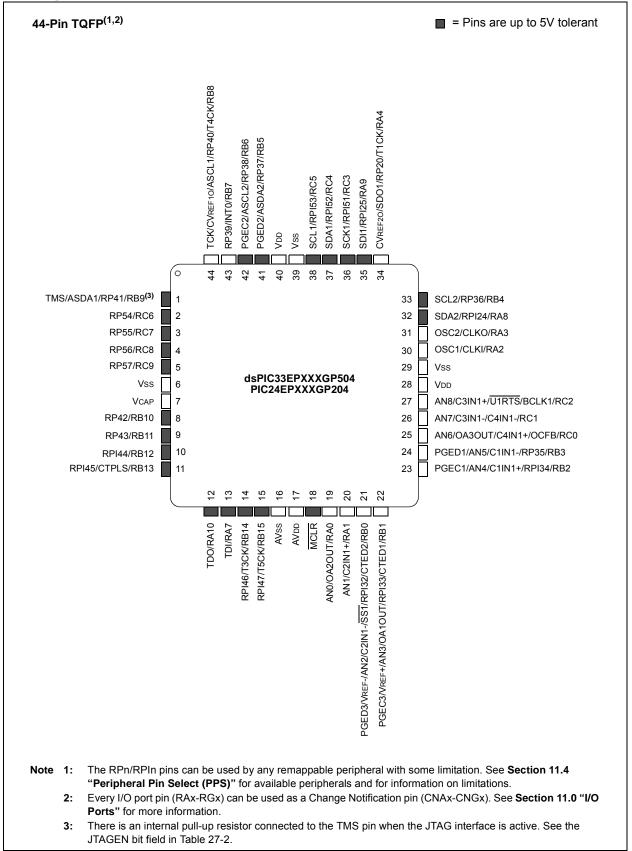

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Program Memory" (DS70613) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

## 4.1 Program Address Space

The program address memory space of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in Section 4.8 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space.

The program memory maps, which are presented by device family and memory size, are shown in Figure 4-1 through Figure 4-5.

# FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EP32GP50X, dsPIC33EP32MC20X/50X AND PIC24EP32GP/MC20X DEVICES

## 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

## REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0                | R/W-0                                      | R/W-0                                           | R/W-0                                      | R/W-0                       | R/W-0         | R/W-0              | R/W-0 |  |

|--------------------|--------------------------------------------|-------------------------------------------------|--------------------------------------------|-----------------------------|---------------|--------------------|-------|--|

|                    |                                            |                                                 |                                            | SYNCI1R<6:03                | >             |                    |       |  |

| bit 15             |                                            |                                                 |                                            |                             |               |                    | bit 8 |  |

|                    |                                            |                                                 |                                            |                             |               |                    |       |  |

| U-0                | U-0                                        | U-0                                             | U-0                                        | U-0                         | U-0           | U-0                | U-0   |  |

| _                  |                                            |                                                 | —                                          |                             |               | <u> </u>           | _     |  |

| bit 7              |                                            |                                                 |                                            |                             |               |                    | bit 0 |  |

|                    |                                            |                                                 |                                            |                             |               |                    |       |  |

| Legend:            |                                            |                                                 |                                            |                             |               |                    |       |  |

| R = Readab         | ole bit                                    | W = Writable                                    | bit                                        | U = Unimplem                | l as '0'      |                    |       |  |

| -n = Value a       | it POR                                     | '1' = Bit is set                                |                                            | '0' = Bit is clea           | ared          | x = Bit is unknown |       |  |

|                    |                                            |                                                 |                                            |                             |               |                    |       |  |

|                    |                                            |                                                 |                                            |                             |               |                    |       |  |

| bit 15             | Unimplemer                                 | nted: Read as '                                 | 0'                                         |                             |               |                    |       |  |

| bit 15<br>bit 14-8 | SYNCI1R<6:                                 |                                                 | M Synchroniz                               | zation Input 1 to<br>nbers) | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | <b>0&gt;:</b> Assign PW                         | M Synchroniz selection nur                 |                             | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                             | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                             | the Correspon | ding RPn Pin b     | its   |  |

|                    | SYNCI1R<6:<br>(see Table 11<br>1111001 = I | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz<br>selection nur<br>121<br>P1 |                             | the Correspon | ding RPn Pin b     | its   |  |

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = No Sync or Trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = CTMU module synchronizes or triggers ICx

- 11011 = ADC1 module synchronizes or triggers  $ICx^{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- $11001 = CMP2 \text{ module synchronizes or triggers ICx}^{(5)}$

- 11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module synchronizes or triggers ICx

- 10010 = IC3 module synchronizes or triggers ICx

- 10001 = IC2 module synchronizes or triggers ICx

- 10000 = IC1 module synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = PTGOx module synchronizes or triggers  $ICx^{(6)}$

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No Sync or Trigger source for ICx

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1

PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

| R-0, HSC                          | R-0, HSC  | U-0               | U-0          | U-0               | R/C-0, HS       | R-0, HSC                              | R-0, HSC |  |

|-----------------------------------|-----------|-------------------|--------------|-------------------|-----------------|---------------------------------------|----------|--|

| ACKSTAT                           | TRSTAT    | _                 | _            | —                 | BCL             | GCSTAT                                | ADD10    |  |

| bit 15                            |           |                   |              |                   |                 |                                       | bit 8    |  |

|                                   |           |                   |              |                   |                 |                                       |          |  |

| R/C-0, HS                         | R/C-0, HS | R-0, HSC          | R/C-0, HSC   | R/C-0, HSC        | R-0, HSC        | R-0, HSC                              | R-0, HSC |  |

| IWCOL                             | I2COV     | D_A               | Р            | S                 | R_W             | RBF                                   | TBF      |  |

| bit 7                             |           |                   |              |                   |                 |                                       | bit 0    |  |

|                                   |           |                   |              |                   |                 |                                       |          |  |

| Legend: C = C                     |           | C = Clearable bit |              | HS = Hardwa       | re Settable bit | HSC = Hardware Settable/Clearable bit |          |  |

| R = Readable bit W = Writable bit |           | e bit             | U = Unimplem | nented bit, read  | ead as '0'      |                                       |          |  |

| -n = Value at POR                 |           | '1' = Bit is se   | et           | '0' = Bit is clea | ared            | x = Bit is unknown                    |          |  |

## REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| bit 15       | <b>ACKSTAT:</b> Acknowledge Status bit (when operating as $I^2C^{TM}$ master, applicable to master transmit operation)                         |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10       | 1 = NACK received from slave                                                                                                                   |

|              | 0 = ACK received from slave                                                                                                                    |

|              | Hardware is set or clear at the end of slave Acknowledge.                                                                                      |

| bit 14       | TRSTAT: Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                               |

|              | 1 = Master transmit is in progress (8 bits + ACK)                                                                                              |

|              | 0 = Master transmit is not in progress                                                                                                         |

|              | Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.                                    |

| bit 13-11    | Unimplemented: Read as '0'                                                                                                                     |

| bit 10       | BCL: Master Bus Collision Detect bit                                                                                                           |

|              | 1 = A bus collision has been detected during a master operation                                                                                |

|              | 0 = No bus collision detected<br>Hardware is set at detection of a bus collision.                                                              |

| <b>h</b> # 0 |                                                                                                                                                |

| bit 9        | GCSTAT: General Call Status bit                                                                                                                |

|              | 1 = General call address was received<br>0 = General call address was not received                                                             |

|              | Hardware is set when address matches general call address. Hardware is clear at Stop detection.                                                |

| bit 8        | ADD10: 10-Bit Address Status bit                                                                                                               |

|              | 1 = 10-bit address was matched                                                                                                                 |

|              | 0 = 10-bit address was not matched                                                                                                             |

|              | Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop                                          |

|              | detection.                                                                                                                                     |

| bit 7        | IWCOL: I2Cx Write Collision Detect bit                                                                                                         |

|              | <ul> <li>1 = An attempt to write to the I2CxTRN register failed because the I<sup>2</sup>C module is busy</li> <li>0 = No collision</li> </ul> |

|              | Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).                                                      |

| bit 6        | <b>I2COV:</b> I2Cx Receive Overflow Flag bit                                                                                                   |

|              | 1 = A byte was received while the I2CxRCV register was still holding the previous byte                                                         |

|              | 0 = No overflow                                                                                                                                |

|              | Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                            |

| bit 5        | <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                        |

|              | 1 = Indicates that the last byte received was data                                                                                             |

|              | 0 = Indicates that the last byte received was a device address                                                                                 |

|              | Hardware is clear at a device address match. Hardware is set by reception of a slave byte.                                                     |

| bit 4        | P: Stop bit                                                                                                                                    |

|              | 1 = Indicates that a Stop bit has been detected last                                                                                           |

|              | 0 = Stop bit was not detected last<br>Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

|              |                                                                                                                                                |

|              |                                                                                                                                                |

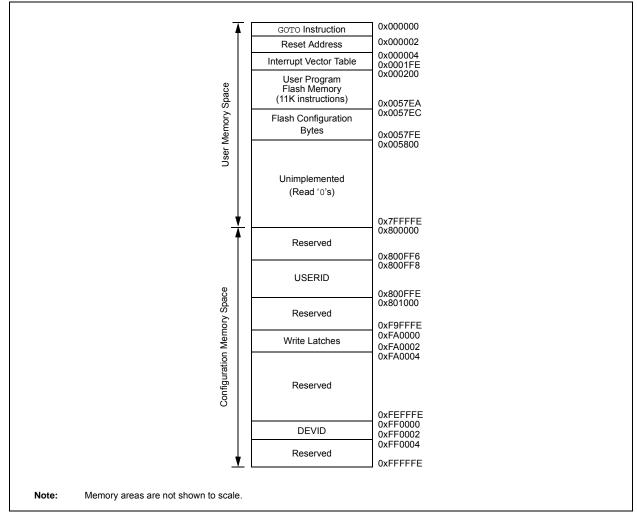

## 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70582) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

Note: <u>Hardware</u> flow control using UxRTS and UxCTS is not available on all pin count devices. See the "**Pin Diagrams**" section for availability.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 20-1: UARTx SIMPLIFIED BLOCK DIAGRAM

© 2011-2013 Microchip Technology Inc.

# 20.3 UARTx Control Registers

#### REGISTER 20-1: UXMODE: UARTX MODE REGISTER

| R/W-0               | U-0                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                    | R/W-0                              | U-0                                              | R/W-0            | R/W-0                     |  |  |  |  |

|---------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------|--------------------------------------------------|------------------|---------------------------|--|--|--|--|

| UARTEN <sup>(</sup> | <sup>1)</sup>                                                       | USIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IREN <sup>(2)</sup>                                      | RTSMD                              | _                                                | UEN1             | UEN0                      |  |  |  |  |

| bit 15              |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          | •                                  |                                                  |                  | bit 8                     |  |  |  |  |

|                     |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <b>D</b> AMA                                             | <b>D</b> 444 0                     | <b>D</b> 444 0                                   | <b>D</b> 444.0   | <b>D</b> 444 0            |  |  |  |  |

| R/W-0, H0           |                                                                     | R/W-0, HC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                    | R/W-0                              | R/W-0                                            | R/W-0            | R/W-0                     |  |  |  |  |

| WAKE                | LPBACK                                                              | ABAUD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | URXINV                                                   | BRGH                               | PDSEL1                                           | PDSEL0           | STSEL                     |  |  |  |  |

| bit 7               |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |                                    |                                                  |                  | bit                       |  |  |  |  |

| Legend:             |                                                                     | HC = Hardwar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | e Clearable b                                            | it                                 |                                                  |                  |                           |  |  |  |  |

| R = Reada           | ble bit                                                             | W = Writable b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | oit                                                      | U = Unimplem                       | ented bit, read                                  | as '0'           |                           |  |  |  |  |

| -n = Value          | at POR                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          | '0' = Bit is clea                  | ared                                             | x = Bit is unkn  | iown                      |  |  |  |  |

| bit 15              | 1 = UARTx is                                                        | ARTx Enable bit <sup>(</sup><br>s enabled; all UA<br>s disabled; all UA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ARTx pins are                                            |                                    |                                                  |                  |                           |  |  |  |  |

| bit 14              | Unimplemen                                                          | ted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ,                                                        |                                    |                                                  |                  |                           |  |  |  |  |

| bit 13              | USIDL: UAR                                                          | USIDL: UARTx Stop in Idle Mode bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                          |                                    |                                                  |                  |                           |  |  |  |  |

|                     |                                                                     | nues module opera                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                          |                                    | le mode                                          |                  |                           |  |  |  |  |

| bit 12              | 1 = IrDA enc                                                        | Encoder and De<br>oder and decod<br>oder and decod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | er are enable                                            | d                                  |                                                  |                  |                           |  |  |  |  |

| bit 11              | $1 = \overline{\text{UxRTS}} p$                                     | le Selection for<br>bin is in Simplex<br>bin is in Flow Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | mode                                                     | t                                  |                                                  |                  |                           |  |  |  |  |

| bit 10              | Unimplemen                                                          | ted: Read as '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ,                                                        |                                    |                                                  |                  |                           |  |  |  |  |

| bit 9-8             | 11 = UxTX, U<br>10 = UxTX, U<br>01 = UxTX, U                        | IARTx Pin Enab<br>JxRX and BCLK<br>JxRX, UxCTS ar<br>JxRX and UxRT<br>nd UxRX pins a<br>atches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | x p <u>ins are</u> ena<br>nd UxRTS pin<br>S pins are ena | s are enabled a<br>abled and used; | nd used <sup>(4)</sup><br>UxCT <u>S pin is</u> c | controlled by PC | ORT latches <sup>(4</sup> |  |  |  |  |

| bit 7               | WAKE: Wake                                                          | e-up on Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Detect During                                            | Sleep Mode Ei                      | nable bit                                        |                  |                           |  |  |  |  |

|                     | in hardwa                                                           | ontinues to sam<br>are on the follow<br>-up is enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |                                    | generated on t                                   | the falling edge | ; bit is cleare           |  |  |  |  |

| bit 6               | 1 = Enables                                                         | ARTx Loopback<br>Loopback mode<br>k mode is disab                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | :                                                        | bit                                |                                                  |                  |                           |  |  |  |  |

| 2:                  | Refer to the " <b>UAI</b><br>enabling the UAR<br>This feature is or | Tx module for realized and the second s | eceive or trans<br>the 16x BRG                           | mit operation.<br>mode (BRGH =     | -                                                | ce Manual" for i | nformation or             |  |  |  |  |

|                     | This feature is or                                                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                                        | -                                  |                                                  |                  |                           |  |  |  |  |

| A-                  | This fastura is ar                                                  | ny available on l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | al nin dovicos                                           |                                    |                                                  |                  |                           |  |  |  |  |

4: This feature is only available on 64-pin devices.

## 25.1 Op Amp Application Considerations

There are two configurations to take into consideration when designing with the op amp modules that available in the dsPIC33EPXXXGP50X. are dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X devices. Configuration A (see Figure 25-6) takes advantage of the internal connection to the ADC module to route the output of the op amp directly to the ADC for measurement. Configuration B (see Figure 25-7) requires that the designer externally route the output of the op amp (OAxOUT) to a separate analog input pin (ANy) on the device. Table 30-55 in Section 30.0 "Electrical Characteristics" describes the performance characteristics for the op amps, distinguishing between the two configuration types where applicable.

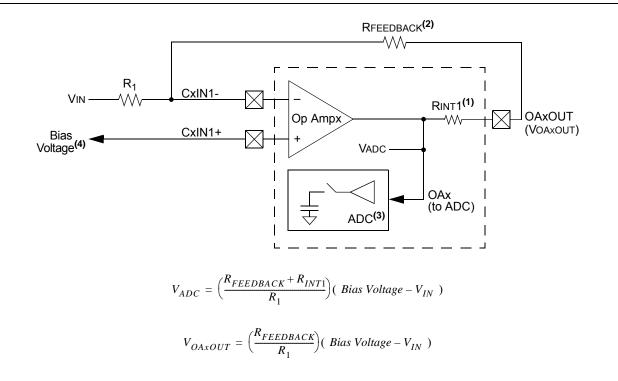

### 25.1.1 OP AMP CONFIGURATION A

Figure 25-6 shows a typical inverting amplifier circuit taking advantage of the internal connections from the op amp output to the input of the ADC. The advantage of this configuration is that the user does not need to consume another analog input (ANy) on the device, and allows the user to simultaneously sample all three op amps with the ADC module, if needed. However, the presence of the internal resistance, RINT1, adds an error in the feedback path. Since RINT1 is an internal resistance, in relation to the op amp output (VOAXOUT) and ADC internal connection (VADC), RINT1 must be included in the numerator term of the transfer function. See Table 30-53 in Section 30.0 "Electrical Characteristics" for the typical value of RINT1. Table 30-60 and Table 30-61 in Section 30.0 "Electrical Characteristics" describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration. Figure 25-6 also defines the equations that should be used when calculating the expected voltages at points, VADC and VOAXOUT.

#### FIGURE 25-6: OP AMP CONFIGURATION A

Note 1: See Table 30-53 for the Typical value.

- 2: See Table 30-53 for the Minimum value for the feedback resistor.

- 3: See Table 30-60 and Table 30-61 for the minimum sample time (TSAMP).

- 4: CVREF10 or CVREF20 are two options that are available for supplying bias voltage to the op amps.

| U-0          | U-0                      | U-0                           | U-0              | U-0              | U-0              | U-0            | U-0    |  |  |  |  |  |

|--------------|--------------------------|-------------------------------|------------------|------------------|------------------|----------------|--------|--|--|--|--|--|

|              | —                        | —                             | _                | —                |                  | —              | _      |  |  |  |  |  |

| bit 15       |                          |                               |                  |                  |                  |                | bit    |  |  |  |  |  |

|              |                          |                               |                  |                  |                  |                |        |  |  |  |  |  |

| U-0          | R/W-0                    | R/W-0                         | R/W-0            | R/W-0            | R/W-0            | R/W-0          | R/W-0  |  |  |  |  |  |

|              | CFSEL2                   | CFSEL1                        | CFSEL0           | CFLTREN          | CFDIV2           | CFDIV1         | CFDIV0 |  |  |  |  |  |

| bit 7        |                          |                               |                  |                  |                  |                | bit    |  |  |  |  |  |

| Legend:      |                          |                               |                  |                  |                  |                |        |  |  |  |  |  |

| R = Readab   | le bit                   | W = Writable                  | bit              | U = Unimpler     | mented bit, read | as '0'         |        |  |  |  |  |  |

| -n = Value a |                          | '1' = Bit is set              |                  | '0' = Bit is cle |                  | x = Bit is unk | nown   |  |  |  |  |  |

|              |                          |                               |                  |                  |                  |                | -      |  |  |  |  |  |

| bit 15-7     | Unimplemen               | ted: Read as                  | ʻ0'              |                  |                  |                |        |  |  |  |  |  |

| oit 6-4      | CFSEL<2:0>               | : Comparator                  | Filter Input Clo | ock Select bits  |                  |                |        |  |  |  |  |  |

|              | 111 = T5CLK              |                               | ·                |                  |                  |                |        |  |  |  |  |  |

|              |                          | $110 = T4CLK^{(2)}$           |                  |                  |                  |                |        |  |  |  |  |  |

|              | $101 = T3CLK^{(1)}$      |                               |                  |                  |                  |                |        |  |  |  |  |  |

|              | 100 = T2CLK              | $100 = T2CLK^{(2)}$           |                  |                  |                  |                |        |  |  |  |  |  |