Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | I²C, IrDA, LINbus, QEI, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 512KB (170K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 24K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 6x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-VQFN Exposed Pad                                                               |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc202t-i-mm |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

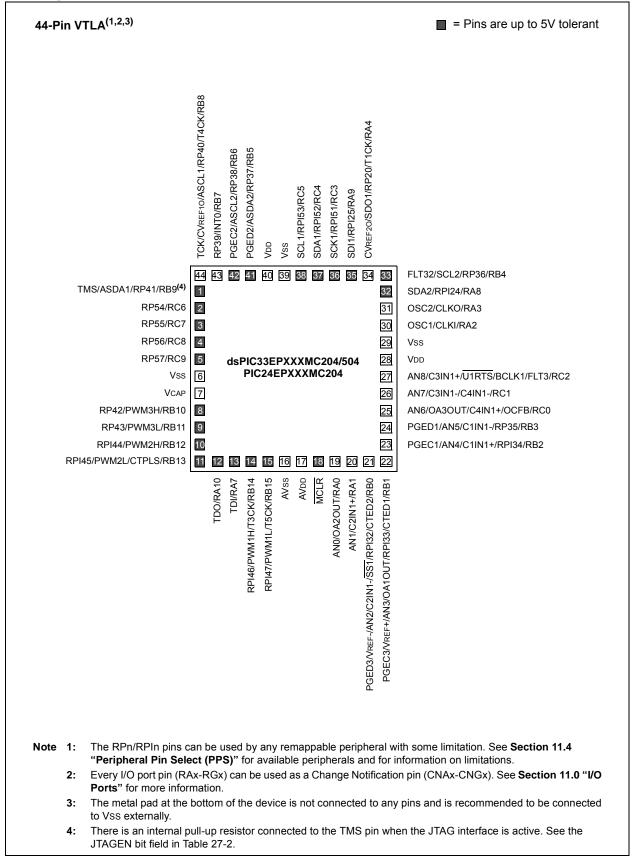

#### Pin Diagrams (Continued)

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

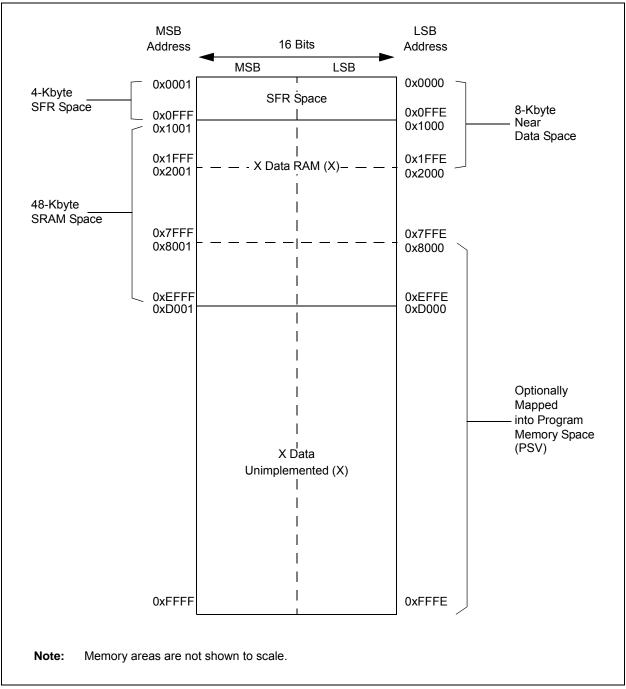

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

#### 4.6.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries check for addresses less than, or greater than, the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected Effective Address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the Effective Address. When an address offset (such as [W7 + W2]) is used, Modulo Addressing correction is performed but the contents of the register remain unchanged.

#### 4.7 Bit-Reversed Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Bit-Reversed Addressing mode is intended to simplify data reordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.7.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when all these conditions are met:

- BWMx bits (W register selection) in the MODCON register are any value other than '1111' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XBREV<14:0> is the Bit-Reversed Addressing modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume    |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|

|       | word-sized data (LSb of every EA is always |  |  |  |  |  |  |  |

|       | clear). The XBREVx value is scaled         |  |  |  |  |  |  |  |

|       | accordingly to generate compatible (byte)  |  |  |  |  |  |  |  |

|       | addresses.                                 |  |  |  |  |  |  |  |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing and word-sized data writes. It does not function for any other addressing mode or for byte-sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XBREVx) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note: Modulo Addressing and Bit-Reversed Addressing can be enabled simultaneously using the same W register, but Bit-Reversed Addressing operation will always take precedence for data writes when enabled.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the Bit-Reversed Pointer.

| -n = Value at POR                 |       | '1' = Bit is set |                                    | '0' = Bit is cle | 0' = Bit is cleared |       | nown  |

|-----------------------------------|-------|------------------|------------------------------------|------------------|---------------------|-------|-------|

| R = Readable bit W = Writable bit |       | bit              | U = Unimplemented bit, read as '0' |                  |                     |       |       |

| Legend:                           |       |                  |                                    |                  |                     |       |       |

|                                   |       |                  |                                    |                  |                     |       |       |

| bit 7                             |       |                  |                                    |                  |                     |       | bit C |

|                                   |       |                  | NVMAD                              | )R<23:16>        |                     |       |       |

| R/W-x                             | R/W-x | R/W-x            | R/W-x                              | R/W-x            | R/W-x               | R/W-x | R/W-x |

| bit 15                            |       |                  |                                    |                  |                     |       | bit 8 |

| _                                 | —     | —                | —                                  | —                | _                   | —     | —     |

| U-0                               | U-0   | U-0              | U-0                                | U-0              | U-0                 | U-0   | U-0   |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMADR<23:16>:** Nonvolatile Memory Write Address High bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

#### REGISTER 5-3: NVMADRL: NONVOLATILE MEMORY ADDRESS REGISTER LOW

| R/W-x                             | R/W-x | R/W-x            | R/W-x        | R/W-x                | R/W-x    | R/W-x              | R/W-x |

|-----------------------------------|-------|------------------|--------------|----------------------|----------|--------------------|-------|

|                                   |       |                  | NVMA         | DR<15:8>             |          |                    |       |

| bit 15                            |       |                  |              |                      |          |                    | bit 8 |

| R/W-x                             | R/W-x | R/W-x            | R/W-x        | R/W-x                | R/W-x    | R/W-x              | R/W-x |

|                                   |       |                  | NVMA         | DR<7:0>              |          |                    |       |

| bit 7                             |       |                  |              |                      |          |                    | bit 0 |

| Legend:                           |       |                  |              |                      |          |                    |       |

| R = Readable bit W = Writable bit |       | it               | U = Unimpler | nented bit, rea      | d as '0' |                    |       |

| -n = Value at POR                 |       | '1' = Bit is set |              | '0' = Bit is cleared |          | x = Bit is unknown |       |

bit 15-0 NVMADR<15:0>: Nonvolatile Memory Write Address Low bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

#### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY

| U-0                                 | U-0 | U-0              | U-0  | U-0                                    | U-0             | U-0      | U-0   |

|-------------------------------------|-----|------------------|------|----------------------------------------|-----------------|----------|-------|

| —                                   | —   | —                | —    | —                                      | —               | —        | —     |

| bit 15                              |     |                  |      |                                        |                 |          | bit 8 |

|                                     |     |                  |      |                                        |                 |          |       |

| W-0                                 | W-0 | W-0              | W-0  | W-0                                    | W-0             | W-0      | W-0   |

|                                     |     |                  | NVMK | EY<7:0>                                |                 |          |       |

| bit 7                               |     |                  |      |                                        |                 |          | bit 0 |

|                                     |     |                  |      |                                        |                 |          |       |

| Legend:                             |     |                  |      |                                        |                 |          |       |

| R = Readable bit W = Writable bit U |     |                  |      |                                        | mented bit, rea | d as '0' |       |

| -n = Value at P                     | OR  | '1' = Bit is set |      | '0' = Bit is cleared x = Bit is unknow |                 |          | nown  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register (write-only) bits

#### 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                 | 12. 2007.00                                                                                                                        |                    |                                                   |                                    |         |                 |        |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------|------------------------------------|---------|-----------------|--------|--|--|

| U-0             | U-0                                                                                                                                | U-0                | U-0                                               | U-0                                | U-0     | U-0             | U-0    |  |  |

| —               | —                                                                                                                                  | —                  | —                                                 | —                                  | —       | —               | —      |  |  |

| bit 15          |                                                                                                                                    |                    |                                                   |                                    |         |                 | bit 8  |  |  |

|                 |                                                                                                                                    |                    |                                                   |                                    |         |                 |        |  |  |

| U-0             | U-0                                                                                                                                | U-0                | U-0                                               | R-0                                | R-0     | R-0             | R-0    |  |  |

| —               |                                                                                                                                    | —                  | —                                                 | RQCOL3                             | RQCOL2  | RQCOL1          | RQCOL0 |  |  |

| bit 7           |                                                                                                                                    |                    |                                                   |                                    |         |                 | bit 0  |  |  |

|                 |                                                                                                                                    |                    |                                                   |                                    |         |                 |        |  |  |

| Legend:         |                                                                                                                                    |                    |                                                   |                                    |         |                 |        |  |  |

| R = Readable    | bit                                                                                                                                | W = Writable       | bit                                               | U = Unimplemented bit, read as '0' |         |                 |        |  |  |

| -n = Value at F | POR                                                                                                                                | '1' = Bit is set   |                                                   | '0' = Bit is cle                   | ared    | x = Bit is unkr | nown   |  |  |

|                 |                                                                                                                                    |                    |                                                   |                                    |         |                 |        |  |  |

| bit 15-4        | Unimplemen                                                                                                                         | ted: Read as '     | כ'                                                |                                    |         |                 |        |  |  |

| bit 3           | RQCOL3: DN                                                                                                                         | /IA Channel 3 T    | ransfer Requ                                      | est Collision F                    | ag bit  |                 |        |  |  |

|                 | <ul> <li>1 = User force and interrupt-based request collision is detected</li> <li>0 = No request collision is detected</li> </ul> |                    |                                                   |                                    |         |                 |        |  |  |

| <b>h</b> # 0    | •                                                                                                                                  |                    |                                                   | est Callisian Fl                   | aa hit  |                 |        |  |  |

| bit 2           |                                                                                                                                    | /A Channel 2 T     | •                                                 |                                    | 0       |                 |        |  |  |

|                 |                                                                                                                                    | •                  | and interrupt-based request collision is detected |                                    |         |                 |        |  |  |

| bit 1           | RQCOL1: DN                                                                                                                         | /IA Channel 1 T    | ransfer Requ                                      | est Collision F                    | ag bit  |                 |        |  |  |

|                 | 1 = User for                                                                                                                       | e and interrupt    | -based reque                                      | st collision is d                  | etected |                 |        |  |  |

|                 | 0 = No reque                                                                                                                       | est collision is d | etected                                           |                                    |         |                 |        |  |  |

| bit 0           | RQCOLO: DN                                                                                                                         | /IA Channel 0 T    | ransfer Requ                                      | est Collision F                    | lag bit |                 |        |  |  |

|                 | 1 = User force                                                                                                                     | e and interrupt    | -based reque                                      | st collision is d                  | etected |                 |        |  |  |

#### REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

## 9.3 Oscillator Control Registers

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0                               | R-0                                                                | R-0                                                                                                | R-0                                | U-0                                | R/W-y                              | R/W-y                | R/W-y                |  |  |  |

|-----------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|----------------------|----------------------|--|--|--|

| _                                 | COSC2                                                              | COSC1                                                                                              | COSC0                              | —                                  | NOSC2 <sup>(2)</sup>               | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |  |  |  |

| bit 15                            |                                                                    |                                                                                                    |                                    |                                    |                                    |                      | bit 8                |  |  |  |

| R/W-0                             | R/W-0                                                              | R-0                                                                                                | U-0                                | R/W-0                              | U-0                                | U-0                  | R/W-0                |  |  |  |

| CLKLOC                            | CK IOLOCK                                                          | LOCK                                                                                               |                                    | CF <sup>(3)</sup>                  |                                    |                      | OSWEN                |  |  |  |

| bit 7                             |                                                                    |                                                                                                    |                                    |                                    |                                    |                      | bit (                |  |  |  |

| Legend:                           |                                                                    | y = Value set                                                                                      | from Configur                      | ation bits on F                    | POR                                |                      |                      |  |  |  |

| R = Reada                         | able bit                                                           | W = Writable                                                                                       | -                                  |                                    | mented bit, read                   | l as '0'             |                      |  |  |  |

| -n = Value                        | at POR                                                             | '1' = Bit is se                                                                                    | t                                  | '0' = Bit is cle                   | eared                              | x = Bit is unkr      | nown                 |  |  |  |

| hit 1 <i>5</i>                    | Unimplemen                                                         | ted. Dood oo                                                                                       | 0'                                 |                                    |                                    |                      |                      |  |  |  |

| bit 15                            | -                                                                  | ted: Read as                                                                                       |                                    |                                    |                                    |                      |                      |  |  |  |

| bit 14-12                         |                                                                    | Current Oscill                                                                                     |                                    |                                    | ()                                 |                      |                      |  |  |  |

|                                   |                                                                    | C Oscillator (F<br>C Oscillator (F                                                                 |                                    |                                    |                                    |                      |                      |  |  |  |

|                                   |                                                                    |                                                                                                    |                                    |                                    |                                    |                      |                      |  |  |  |

|                                   |                                                                    | 101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved                                             |                                    |                                    |                                    |                      |                      |  |  |  |

|                                   |                                                                    | 011 = Primary Oscillator (XT, HS, EC) with PLL                                                     |                                    |                                    |                                    |                      |                      |  |  |  |

|                                   |                                                                    | 010 = Primary Oscillator (XT, HS, EC)                                                              |                                    |                                    |                                    |                      |                      |  |  |  |

|                                   |                                                                    | 001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |                                    |                                    |                                    |                      |                      |  |  |  |

| bit 11 Unimplemented: Read as '0' |                                                                    |                                                                                                    |                                    |                                    |                                    |                      |                      |  |  |  |

| bit 10-8                          | NOSC<2:0>:                                                         | NOSC<2:0>: New Oscillator Selection bits <sup>(2)</sup>                                            |                                    |                                    |                                    |                      |                      |  |  |  |

|                                   | 111 = Fast R                                                       | 111 = Fast RC Oscillator (FRC) with Divide-by-n                                                    |                                    |                                    |                                    |                      |                      |  |  |  |

|                                   |                                                                    | 110 = Fast RC Oscillator (FRC) with Divide-by-16                                                   |                                    |                                    |                                    |                      |                      |  |  |  |

|                                   |                                                                    | 101 = Low-Power RC Oscillator (LPRC)                                                               |                                    |                                    |                                    |                      |                      |  |  |  |

|                                   |                                                                    | 100 = Reserved                                                                                     |                                    |                                    |                                    |                      |                      |  |  |  |

|                                   |                                                                    | 011 = Primary Oscillator (XT, HS, EC) with PLL<br>010 = Primary Oscillator (XT, HS, EC)            |                                    |                                    |                                    |                      |                      |  |  |  |

|                                   |                                                                    | 001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)                                   |                                    |                                    |                                    |                      |                      |  |  |  |

|                                   |                                                                    | 000 = Fast RC Oscillator (FRC)                                                                     |                                    |                                    |                                    |                      |                      |  |  |  |

| bit 7                             |                                                                    | Clock Lock Ena                                                                                     |                                    |                                    |                                    |                      |                      |  |  |  |

|                                   |                                                                    |                                                                                                    |                                    | configurations                     | are locked; if (F                  | =CKSM0 = 0), t       | then clock and       |  |  |  |

|                                   |                                                                    | figurations may<br>d PLL selectio                                                                  |                                    | ked, configurat                    | ions may be mo                     | odified              |                      |  |  |  |

| bit 6                             |                                                                    | Lock Enable b                                                                                      |                                    | -                                  | -                                  |                      |                      |  |  |  |

|                                   | 1 = I/O lock is                                                    | 1 = I/O lock is active                                                                             |                                    |                                    |                                    |                      |                      |  |  |  |

|                                   | 0 = I/O lock is                                                    | s not active                                                                                       |                                    |                                    |                                    |                      |                      |  |  |  |

| bit 5                             | LOCK: PLL L                                                        | ock Status bit                                                                                     | (read-only)                        |                                    |                                    |                      |                      |  |  |  |

|                                   |                                                                    | s that PLL is in<br>s that PLL is ou                                                               |                                    |                                    | satisfied<br>progress or PLL       | is disabled          |                      |  |  |  |

| Note 1:                           | Writes to this regis                                               |                                                                                                    |                                    |                                    |                                    |                      | ʻdsPIC33/            |  |  |  |

| 2:                                | Direct clock switch<br>This applies to cloo<br>mode as a transitio | es between ar<br>ck switches in                                                                    | y primary osci<br>either directior | llator mode wi<br>n. In these inst | th PLL and FRC<br>ances, the appli | PLL mode are         |                      |  |  |  |

| 0                                 | This bit should only                                               |                                                                                                    |                                    |                                    |                                    |                      |                      |  |  |  |

**3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

# **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 4 Unimplemented: Read as '0'

- bit 3 **CF:** Clock Fail Detect bit<sup>(3)</sup>

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **"Oscillator"** (DS70580) in the *"dsPIC33/ PIC24 Family Reference Manual"* (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

NOTES:

#### 11.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx and TRISx registers for data control, port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs other than VDD by using external pull-up resistors. The maximum open-drain voltage allowed on any pin is the same as the maximum VIH specification for that particular pin.

See the **"Pin Diagrams"** section for the available 5V tolerant pins and Table 30-11 for the maximum VIH specification for each pin.

#### 11.2 Configuring Analog and Digital Port Pins

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs or outputs must have their corresponding ANSELx and TRISx bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

Pins with analog functions affected by the ANSELx registers are listed with a buffer type of analog in the Pinout I/O Descriptions (see Table 1-1).

If the TRISx bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or comparator module.

When the PORTx register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 11.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP, as shown in Example 11-1.

#### **11.3** Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature can detect input Change-of-States even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a Change-of-State.

Three control registers are associated with the Change Notification (CN) functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each I/O pin also has a weak pull-up and a weak pull-down connected to it. The pull-ups and pulldowns act as a current source or sink source connected to the pin and eliminate the need for external resistors when push button, or keypad devices are connected. The pull-ups and pull-downs are enabled separately, using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on Change Noti-      |

|-------|----------------------------------------------|

|       | fication pins should always be disabled      |

|       | when the port pin is configured as a digital |

|       | output.                                      |

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8> |

|------|------------|-------------------------|

|      |            | ; as inputs             |

| MOV  | W0, TRISB  | ; and PORTB<7:0>        |

|      |            | ; as outputs            |

| NOP  |            | ; Delay 1 cycle         |

| BTSS | PORTB, #13 | ; Next Instruction      |

|      |            |                         |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|        |     | PP20P<5:0> |       |       |         |       |       |

|--------|-----|------------|-------|-------|---------|-------|-------|

| U-0    | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

| bit 15 |     |            |       |       |         |       | bit 8 |

|        |     |            |       | RP35  | iR<5:0> |       |       |

| U-0    | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

#### REGISTER 11-18: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP20  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

|       |     |       |       |       |        |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP35R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP35 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP20R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-19: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP37  | ′R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP36  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP37R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP37 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP36R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-3 for peripheral function numbers) |

NOTES:

### dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 21-17: CxRXFnEID: ECANx ACCEPTANCE FILTER n EXTENDED IDENTIFIER REGISTER (n = 0-15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-0 EID<15:0>: Extended Identifier bits

1 = Message address bit, EIDx, must be '1' to match filter

0 = Message address bit, EIDx, must be '0' to match filter

#### REGISTER 21-18: CxFMSKSEL1: ECANx FILTER 7-0 MASK SELECTION REGISTER 1

| R/W-0         | R/W-0       | R/W-0                                                        | R/W-0            | R/W-0                             | R/W-0            | R/W-0           | R/W-0  |

|---------------|-------------|--------------------------------------------------------------|------------------|-----------------------------------|------------------|-----------------|--------|

| F7MSK<1:0>    |             | F6MS                                                         | K<1:0>           | F5MSK<1:0>                        |                  | F4MSK<1:0>      |        |

| bit 15        |             | ·                                                            |                  |                                   |                  |                 | bit    |

| R/W-0         | R/W-0       | R/W-0                                                        | R/W-0            | R/W-0                             | R/W-0            | R/W-0           | R/W-0  |

| F3MS          | SK<1:0>     | F2MS                                                         | K<1:0>           | F1MS                              | K<1:0>           | F0MS            | K<1:0> |

| bit 7         |             |                                                              |                  |                                   |                  |                 | bit (  |

| Legend:       |             |                                                              |                  |                                   |                  |                 |        |

| R = Readable  | e bit       | W = Writable                                                 | bit              | U = Unimplen                      | nented bit, read | d as '0'        |        |

| -n = Value at | POR         | '1' = Bit is set                                             |                  | •                                 |                  | x = Bit is unkr | nown   |

|               | 01 = Accept | red<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg | gisters contain  | mask                              |                  |                 |        |

| bit 13-12     | F6MSK<1:0   | >: Mask Source                                               | for Filter 6 bit | s (same values                    | s as bits<15:14  | >)              |        |

| bit 11-10     | F5MSK<1:0   | >: Mask Source                                               | for Filter 5 bit | s (same values                    | s as bits<15:14  | >)              |        |

| bit 9-8       | F4MSK<1:0   | >: Mask Source                                               | for Filter 4 bit | s (same values                    | s as bits<15:14  | >)              |        |

| bit 7-6       | F3MSK<1:0   | >: Mask Source                                               | for Filter 3 bit | s (same values                    | s as bits<15:14  | >)              |        |

| bit 5-4       | F2MSK<1:0   | >: Mask Source                                               | for Filter 2 bit | s (same values                    | s as bits<15:14  | >)              |        |

| bit 3-2       | F1MSK<1:0   | )>: Mask Source for Filter 1 b                               |                  | bits (same values as bits<15:14>) |                  |                 |        |

|               |             |                                                              |                  |                                   |                  | . )             |        |

| U-0          | U-0                                                                                                | U-0                                                                                                                                               | U-0                                                                                                       | U-0                                                                                                          | U-0                               | U-0            | R/W-0   |

|--------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------|---------|

| —            | _                                                                                                  | —                                                                                                                                                 |                                                                                                           | —                                                                                                            | _                                 | —              | ADDMAEN |

| bit 15       |                                                                                                    |                                                                                                                                                   |                                                                                                           |                                                                                                              |                                   |                | bit 8   |

| U-0          | U-0                                                                                                | U-0                                                                                                                                               | U-0                                                                                                       | U-0                                                                                                          | R/W-0                             | R/W-0          | R/W-0   |

| 0-0          | 0-0                                                                                                | 0-0                                                                                                                                               | 0-0                                                                                                       | 0-0                                                                                                          |                                   |                | -       |

|              | —                                                                                                  | —                                                                                                                                                 | _                                                                                                         | —                                                                                                            | DMABL2                            | DMABL1         | DMABL0  |

| bit 7        |                                                                                                    |                                                                                                                                                   |                                                                                                           |                                                                                                              |                                   |                | bit 0   |

| Legend:      |                                                                                                    |                                                                                                                                                   |                                                                                                           |                                                                                                              |                                   |                |         |

| R = Readab   | le bit                                                                                             | W = Writable b                                                                                                                                    | bit                                                                                                       | U = Unimpler                                                                                                 | mented bit, read                  | 1 as '0'       |         |

| -n = Value a | t POR                                                                                              | '1' = Bit is set                                                                                                                                  |                                                                                                           | '0' = Bit is cle                                                                                             |                                   | x = Bit is unk | nown    |

|              |                                                                                                    |                                                                                                                                                   |                                                                                                           |                                                                                                              |                                   |                |         |

| bit 15-9     | Unimplemen                                                                                         | ted: Read as '0                                                                                                                                   | 3                                                                                                         |                                                                                                              |                                   |                |         |

| bit 8        | ADDMAEN: A                                                                                         | ADC1 DMA Ena                                                                                                                                      | ıble bit                                                                                                  |                                                                                                              |                                   |                |         |

|              |                                                                                                    |                                                                                                                                                   |                                                                                                           | 0                                                                                                            | ster for transfer<br>ADC1BUFF reg | 0              |         |

| bit 7-3      | Unimplemen                                                                                         | ted: Read as '0                                                                                                                                   | ,                                                                                                         |                                                                                                              |                                   |                |         |

| bit 2-0      | DMABL<2:0>                                                                                         | Selects Numb                                                                                                                                      | per of DMA B                                                                                              | uffer Locations                                                                                              | per Analog Inpu                   | ut bits        |         |

|              | 110 = Allocat<br>101 = Allocat<br>100 = Allocat<br>011 = Allocat<br>010 = Allocat<br>001 = Allocat | es 128 words of<br>es 64 words of<br>es 32 words of<br>es 16 words of<br>es 8 words of b<br>es 4 words of b<br>es 2 words of b<br>es 1 word of bu | buffer to each<br>buffer to each<br>buffer to each<br>uffer to each<br>uffer to each a<br>uffer to each a | analog input<br>analog input<br>analog input<br>analog input<br>analog input<br>analog input<br>analog input |                                   |                |         |

#### REGISTER 23-4: AD1CON4: ADC1 CONTROL REGISTER 4

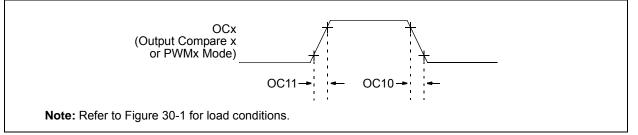

#### FIGURE 30-7: OUTPUT COMPARE x MODULE (OCx) TIMING CHARACTERISTICS

#### TABLE 30-27: OUTPUT COMPARE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |   |   |    |                    |  |

|--------------------|--------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|----|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min. Typ. Max. Units Conditions                                                                                                                                                                                                                                                         |   |   |    | Conditions         |  |

| OC10               | TccF   | OCx Output Fall Time          | _                                                                                                                                                                                                                                                                                       |   | _ | ns | See Parameter DO32 |  |

| OC11               | TccR   | OCx Output Rise Time          | _                                                                                                                                                                                                                                                                                       | _ | — | ns | See Parameter DO31 |  |

Note 1: These parameters are characterized but not tested in manufacturing.

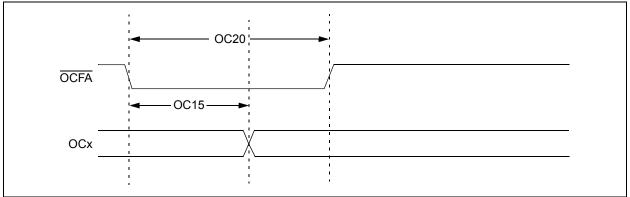

#### FIGURE 30-8: OCx/PWMx MODULE TIMING CHARACTERISTICS

#### TABLE 30-28: OCx/PWMx MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                   | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |          |       |            |

|--------------------|--------|-----------------------------------|-------------------------------------------------------|------|----------|-------|------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>     | Min.                                                  | Тур. | Max.     | Units | Conditions |

| OC15               | TFD    | Fault Input to PWMx I/O<br>Change | —                                                     | _    | Tcy + 20 | ns    |            |

| OC20               | TFLT   | Fault Input Pulse Width           | TCY + 20                                              |      | —        | ns    |            |

**Note 1:** These parameters are characterized but not tested in manufacturing.

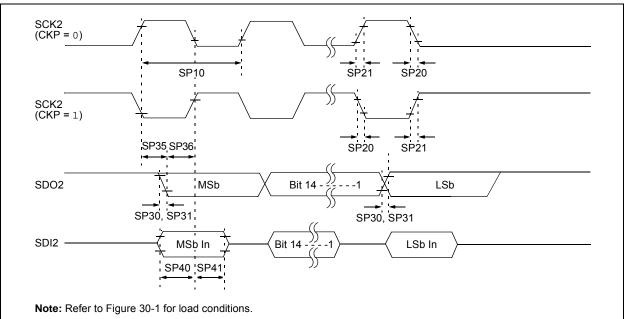

#### FIGURE 30-17: SPI2 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-36:SPI2 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                             |

|--------------------|-----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |

| SP10               | FscP                  | Maximum SCK2 Frequency                        |                                                                                                                                                                                                                                                                                         | —                   | 9    | MHz   | -40°C to +125°C<br>(Note 3) |

| SP20               | TscF                  | SCK2 Output Fall Time                         | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP21               | TscR                  | SCK2 Output Rise Time                         | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                    | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                    | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after SCK2 Edge        | _                                                                                                                                                                                                                                                                                       | 6                   | 20   | ns    |                             |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge  | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                             |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data<br>Input to SCK2 Edge | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                             |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge     | 30                                                                                                                                                                                                                                                                                      | —                   |      | ns    |                             |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 111 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

| AC CHARA             | CTERISTICS                               |                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |  |

| 15 MHz               | Table 30-42                              | _                                           | _                                                     | 0,1 | 0,1 | 0,1 |  |

| 10 MHz               | _                                        | Table 30-43                                 | —                                                     | 1   | 0,1 | 1   |  |

| 10 MHz               | —                                        | Table 30-44                                 | —                                                     | 0   | 0,1 | 1   |  |

| 15 MHz               | —                                        | —                                           | Table 30-45                                           | 1   | 0   | 0   |  |

| 11 MHz               | —                                        | —                                           | Table 30-46                                           | 1   | 1   | 0   |  |

| 15 MHz               | _                                        | —                                           | Table 30-47                                           | 0   | 1   | 0   |  |

| 11 MHz               | _                                        | —                                           | Table 30-48                                           | 0   | 0   | 0   |  |

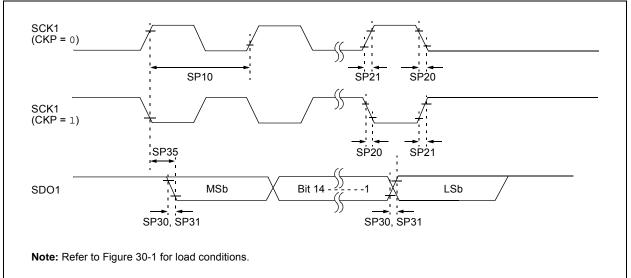

#### TABLE 30-41: SPI1 MAXIMUM DATA/CLOCK RATE SUMMARY

#### FIGURE 30-22: SPI1 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

NOTES:

#### **Revision C (December 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

In addition, where applicable, new sections were added to each peripheral chapter that provide information and links to related resources, as well as helpful tips. For examples, see Section 20.1 "UART Helpful Tips" and Section 3.6 "CPU Resources". All occurrences of TLA were updated to VTLA throughout the document, with the exception of the pin diagrams (updated diagrams were not available at time of publication).

A new chapter, Section 31.0 "DC and AC Device Characteristics Graphs", was added.

All other major changes are referenced by their respective section in Table A-2.

| Section Name                                                                                                                                                            | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal<br>Controllers (up to<br>256-Kbyte Flash and<br>32-Kbyte SRAM) with High-<br>Speed PWM, Op amps, and<br>Advanced Analog" | The content on the first page of this section was extensively reworked to provide the reader with the key features and functionality of this device family in an "at-a-glance" format.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Section 1.0 "Device<br>Overview"                                                                                                                                        | Updated the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X, and<br>PIC24EPXXXGP/MC20X Block Diagram (see Figure 1-1), which now contains a CPU<br>block and a reference to the CPU diagram.<br>Updated the description and Note references in the Pinout I/O Descriptions for these                                                                                                                                                                                                                                                                                                                                                              |