Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

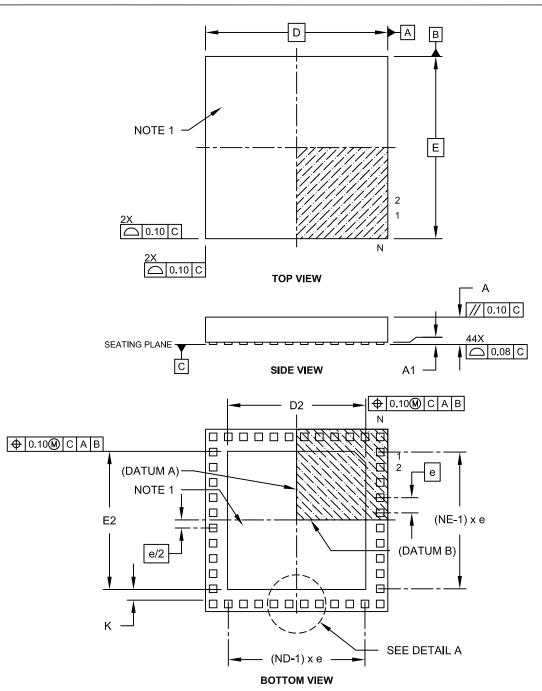

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc204-h-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

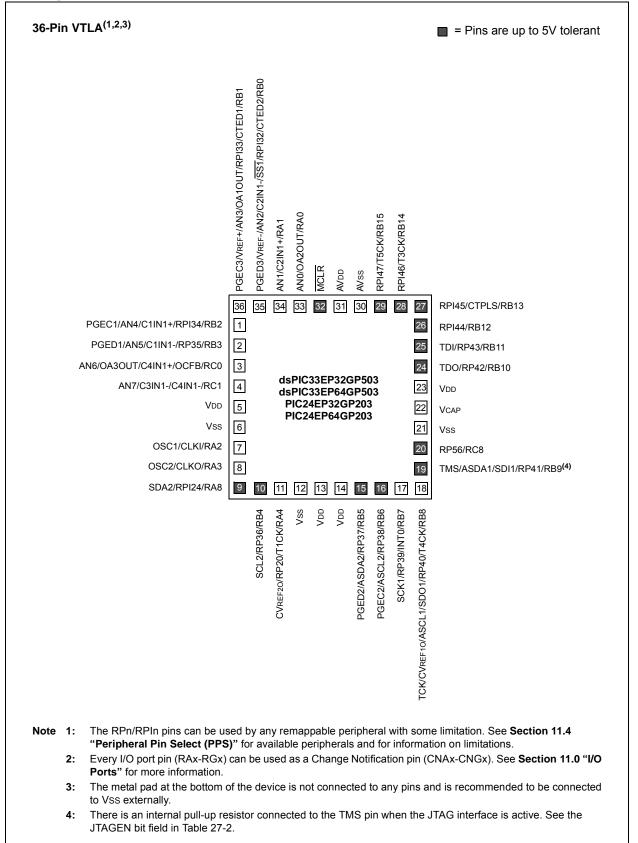

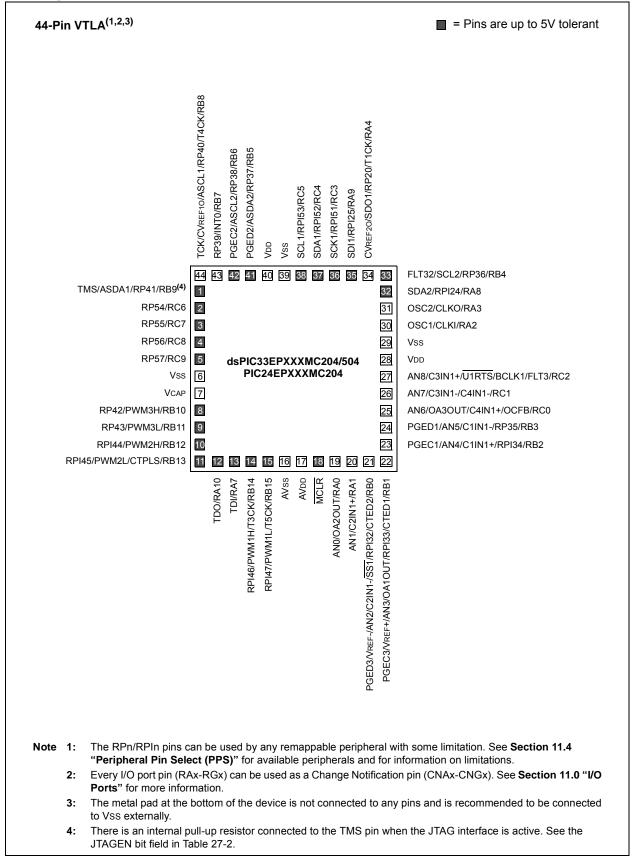

# **Pin Diagrams (Continued)**

# Pin Diagrams (Continued)

| Pin Name <sup>(4)</sup>                        | Pin<br>Type         | Buffer<br>Type          | PPS              | Description                                                                                                                                                                        |

|------------------------------------------------|---------------------|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN15                                       | I                   | Analog                  | No               | Analog input channels.                                                                                                                                                             |

| CLKI                                           | I                   | ST/<br>CMOS             | No               | External clock source input. Always associated with OSC1 pin function                                                                                                              |

| CLKO                                           | 0                   | —                       | No               | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with OSC2 pin function. |

| OSC1                                           | I                   | ST/                     | No               | Oscillator crystal input. ST buffer when configured in RC mode; CMOS                                                                                                               |

| OSC2                                           | I/O                 | CMOS<br>—               | No               | otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                          |

| REFCLKO                                        | 0                   |                         | Yes              | Reference clock output.                                                                                                                                                            |

| IC1-IC4                                        | Ι                   | ST                      | Yes              | Capture Inputs 1 through 4.                                                                                                                                                        |

| OCFA<br>OCFB<br>OC1-OC4                        | <br> <br> <br>0     | ST<br>ST                | Yes<br>No<br>Yes | Compare Fault A input (for Compare channels).<br>Compare Fault B input (for Compare channels).<br>Compare Outputs 1 through 4.                                                     |

| INT0                                           | I                   | ST                      | No               | External Interrupt 0.                                                                                                                                                              |

| INT1<br>INT2                                   |                     | ST<br>ST                | Yes<br>Yes       | External Interrupt 1.<br>External Interrupt 2.                                                                                                                                     |

| RA0-RA4, RA7-RA12                              | I/O                 | ST                      | No               | PORTA is a bidirectional I/O port.                                                                                                                                                 |

| RB0-RB15                                       | I/O                 | ST                      | No               | PORTB is a bidirectional I/O port.                                                                                                                                                 |

| RC0-RC13, RC15                                 | I/O                 | ST                      | No               | PORTC is a bidirectional I/O port.                                                                                                                                                 |

| RD5, RD6, RD8                                  | I/O                 | ST                      | No               | PORTD is a bidirectional I/O port.                                                                                                                                                 |

| RE12-RE15                                      | I/O                 | ST                      | No               | PORTE is a bidirectional I/O port.                                                                                                                                                 |

| RF0, RF1                                       | I/O                 | ST                      | No               | PORTF is a bidirectional I/O port.                                                                                                                                                 |

| RG6-RG9                                        | I/O                 | ST                      | No               | PORTG is a bidirectional I/O port.                                                                                                                                                 |

| T1CK                                           | Ι                   | ST                      | No               | Timer1 external clock input.                                                                                                                                                       |

| T2CK<br>T3CK                                   |                     | ST<br>ST                | Yes              | Timer2 external clock input.                                                                                                                                                       |

| T4CK                                           |                     | ST                      | No<br>No         | Timer3 external clock input.<br>Timer4 external clock input.                                                                                                                       |

| T5CK                                           | i                   | ST                      | No               | Timer5 external clock input.                                                                                                                                                       |

| CTPLS                                          | 0                   | ST                      | No               | CTMU pulse output.                                                                                                                                                                 |

| CTED1                                          | Ι                   | ST                      | No               | CTMU External Edge Input 1.                                                                                                                                                        |

| CTED2                                          | Ι                   | ST                      | No               | CTMU External Edge Input 2.                                                                                                                                                        |

| U1CTS                                          | Ι                   | ST                      | No               | UART1 Clear-To-Send.                                                                                                                                                               |

| U1RTS                                          | 0                   |                         | No               | UART1 Ready-To-Send.                                                                                                                                                               |

| U1RX                                           |                     | ST                      | Yes              | UART1 receive.<br>UART1 transmit.                                                                                                                                                  |

| U1TX<br>BCLK1                                  | 0                   | ST                      | Yes<br>No        | UART1 Iransmit.<br>UART1 IrDA <sup>®</sup> baud clock output.                                                                                                                      |

| Legend: CMOS = CM<br>ST = Schmi<br>PPS = Perip | MOS co<br>itt Trigg | ompatible<br>er input v | input<br>with CN | or output Analog = Analog input P = Power                                                                                                                                          |

# TABLE 1-1:PINOUT I/O DESCRIPTIONS

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

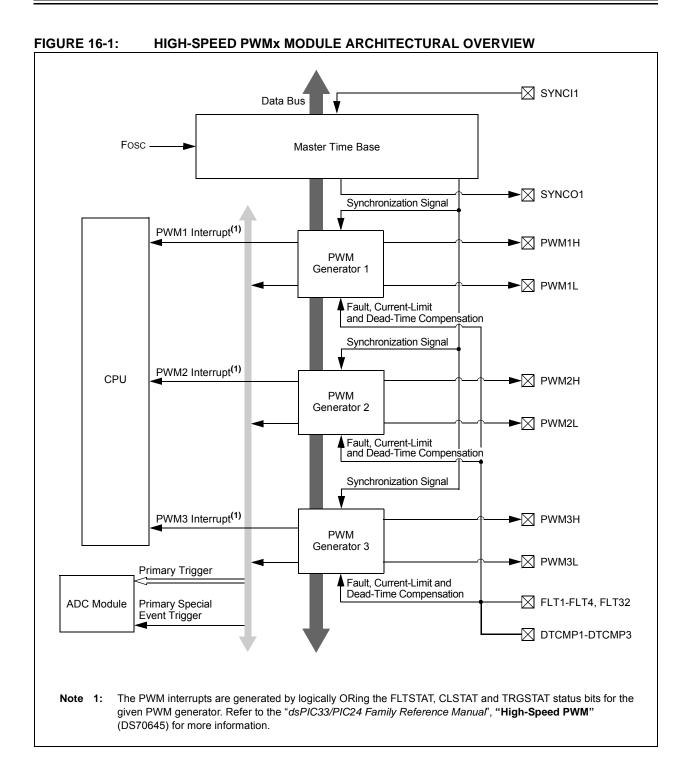

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

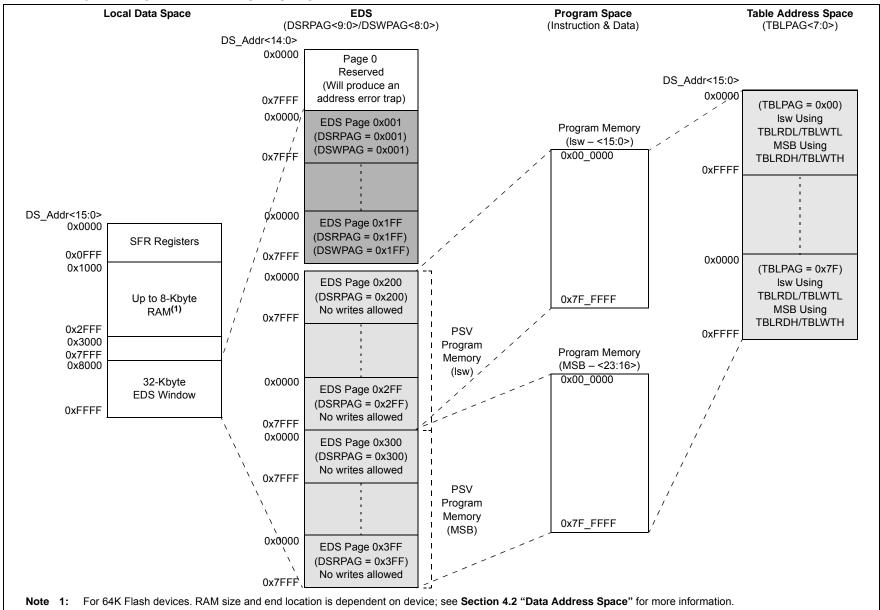

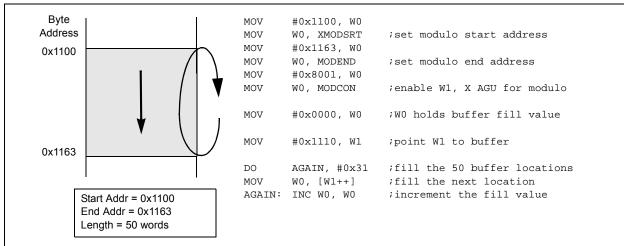

## EXAMPLE 4-3: PAGED DATA MEMORY SPACE

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# 4.6 Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

# 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Y space Modulo Addressing EA calcula- |

|-------|---------------------------------------|

|       | tions assume word-sized data (LSb of  |

|       | every EA is always clear).            |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

## 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

# FIGURE 4-20: MODULO ADDRESSING OPERATION EXAMPLE

# 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory and to program two instruction words at a time. See the General Purpose and Motor Control Family tables (Table 1 and Table 2, respectively) for the page sizes of each device.

For more information on erasing and programming Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

# 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time) in Table 30-14 in **Section 30.0 "Electrical Characteristics"**.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

## 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to **Flash Programming**" (DS70609) in the "*dsPIC33/PIC24 Family Reference Manual*" for details and codes examples on programming using RTSP.

# 5.4 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |  |  |  |

|-------|--------------------------------------------------------------------------------------|--|--|--|

|       | this URL in your browser:                                                            |  |  |  |

|       | http://www.microchip.com/wwwproducts/                                                |  |  |  |

|       | Devices.aspx?dDocName=en555464                                                       |  |  |  |

## 5.4.1 KEY RESOURCES

- "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# 5.5 Control Registers

Four SFRs are used to erase and write the program Flash memory: NVMCON, NVMKEY, NVMADRH and NVMADRL.

The NVMCON register (Register 5-1) enables and initiates Flash memory erase and write operations.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRH and NVMADRL. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations or the selected page for erase operations.

The NVMADRH register is used to hold the upper 8 bits of the EA, while the NVMADRL register is used to hold the lower 16 bits of the EA.

| R/W-0                | R/W-0                   | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|-------------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                      | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                         |                      |       |       |       |       | bit 8 |

|                      |                         |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA    | Ν     | OV    | Z     | С     |

| bit 7                |                         |                      |       |       |       |       | bit 0 |

|                      |                         |                      |       |       |       |       |       |

# REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

# 9.3 Oscillator Control Registers

# REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup>

| U-0            | R-0                                                                | R-0                                                                                                                                  | R-0                                | U-0                                | R/W-y                              | R/W-y                | R/W-y                |  |  |  |

|----------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|----------------------|----------------------|--|--|--|

| _              | COSC2                                                              | COSC1                                                                                                                                | COSC0                              | —                                  | NOSC2 <sup>(2)</sup>               | NOSC1 <sup>(2)</sup> | NOSCO <sup>(2)</sup> |  |  |  |

| bit 15         |                                                                    |                                                                                                                                      |                                    |                                    |                                    |                      | bit 8                |  |  |  |

| R/W-0          | R/W-0                                                              | R-0                                                                                                                                  | U-0                                | R/W-0                              | U-0                                | U-0                  | R/W-0                |  |  |  |

| CLKLOC         | CK IOLOCK                                                          | LOCK                                                                                                                                 |                                    | CF <sup>(3)</sup>                  |                                    |                      | OSWEN                |  |  |  |

| bit 7          |                                                                    |                                                                                                                                      |                                    |                                    |                                    |                      | bit (                |  |  |  |

| Legend:        |                                                                    | y = Value set                                                                                                                        | from Configur                      | ation bits on F                    | POR                                |                      |                      |  |  |  |

| R = Reada      | able bit                                                           | W = Writable                                                                                                                         | -                                  |                                    | mented bit, read                   | l as '0'             |                      |  |  |  |

| -n = Value     | at POR                                                             | '1' = Bit is se                                                                                                                      | t                                  | '0' = Bit is cle                   | eared                              | x = Bit is unkr      | nown                 |  |  |  |

| hit 1 <i>5</i> | Unimplemen                                                         | ted. Dood oo                                                                                                                         | 0'                                 |                                    |                                    |                      |                      |  |  |  |

| bit 15         | -                                                                  | ted: Read as                                                                                                                         |                                    |                                    |                                    |                      |                      |  |  |  |

| bit 14-12      |                                                                    | Current Oscill                                                                                                                       |                                    |                                    | /)                                 |                      |                      |  |  |  |

|                |                                                                    | C Oscillator (F<br>C Oscillator (F                                                                                                   |                                    |                                    |                                    |                      |                      |  |  |  |

|                |                                                                    |                                                                                                                                      |                                    |                                    |                                    |                      |                      |  |  |  |

|                |                                                                    | 101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved                                                                               |                                    |                                    |                                    |                      |                      |  |  |  |

|                |                                                                    | 011 = Primary Oscillator (XT, HS, EC) with PLL                                                                                       |                                    |                                    |                                    |                      |                      |  |  |  |

|                |                                                                    | 010 = Primary Oscillator (XT, HS, EC)                                                                                                |                                    |                                    |                                    |                      |                      |  |  |  |

|                |                                                                    | 001 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)<br>000 = Fast RC Oscillator (FRC)                                   |                                    |                                    |                                    |                      |                      |  |  |  |

| bit 11         |                                                                    | Unimplemented: Read as '0'                                                                                                           |                                    |                                    |                                    |                      |                      |  |  |  |

| bit 10-8       | NOSC<2:0>:                                                         | NOSC<2:0>: New Oscillator Selection bits <sup>(2)</sup>                                                                              |                                    |                                    |                                    |                      |                      |  |  |  |

|                | 111 = Fast R                                                       | 111 = Fast RC Oscillator (FRC) with Divide-by-n                                                                                      |                                    |                                    |                                    |                      |                      |  |  |  |

|                |                                                                    | C Oscillator (F                                                                                                                      |                                    | le-by-16                           |                                    |                      |                      |  |  |  |

|                |                                                                    | 101 = Low-Power RC Oscillator (LPRC)                                                                                                 |                                    |                                    |                                    |                      |                      |  |  |  |

|                |                                                                    | 100 = Reserved                                                                                                                       |                                    |                                    |                                    |                      |                      |  |  |  |

|                |                                                                    | 011 = Primary Oscillator (XT, HS, EC) with PLL<br>010 = Primary Oscillator (XT, HS, EC)                                              |                                    |                                    |                                    |                      |                      |  |  |  |

|                |                                                                    | 010 = Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL)                                                                     |                                    |                                    |                                    |                      |                      |  |  |  |

|                |                                                                    | 000 = Fast RC Oscillator (FRC)                                                                                                       |                                    |                                    |                                    |                      |                      |  |  |  |

| bit 7          |                                                                    | Clock Lock Ena                                                                                                                       |                                    |                                    |                                    |                      |                      |  |  |  |

|                |                                                                    |                                                                                                                                      |                                    | configurations                     | are locked; if (F                  | =CKSM0 = 0), t       | then clock and       |  |  |  |

|                |                                                                    | figurations may<br>d PLL selectio                                                                                                    |                                    | ked, configurat                    | ions may be mo                     | odified              |                      |  |  |  |

| bit 6          |                                                                    | <ul> <li>0 = Clock and PLL selections are not locked, configurations may be modified</li> <li>IOLOCK: I/O Lock Enable bit</li> </ul> |                                    |                                    |                                    |                      |                      |  |  |  |

|                | 1 = I/O lock is                                                    | 1 = I/O lock is active                                                                                                               |                                    |                                    |                                    |                      |                      |  |  |  |

|                | 0 = I/O lock is                                                    | s not active                                                                                                                         |                                    |                                    |                                    |                      |                      |  |  |  |

| bit 5          | LOCK: PLL L                                                        | ock Status bit                                                                                                                       | (read-only)                        |                                    |                                    |                      |                      |  |  |  |

|                |                                                                    | s that PLL is in<br>s that PLL is ou                                                                                                 |                                    |                                    | satisfied<br>progress or PLL       | is disabled          |                      |  |  |  |

| Note 1:        | Writes to this regis                                               |                                                                                                                                      |                                    |                                    |                                    |                      | ʻdsPIC33/            |  |  |  |

| 2:             | Direct clock switch<br>This applies to cloo<br>mode as a transitio | es between ar<br>ck switches in                                                                                                      | y primary osci<br>either directior | llator mode wi<br>n. In these inst | th PLL and FRC<br>ances, the appli | PLL mode are         |                      |  |  |  |

| 0              | This bit should only                                               |                                                                                                                                      |                                    |                                    |                                    |                      |                      |  |  |  |

**3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

#### 11.7 **Peripheral Pin Select Registers**

## REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      |       |       |       | INT1R<6:0> |       |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

| —      | —     | —     | —     | —          | _     | _     | —     |

| bit 7  |       | •     |       | •          |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

| Legend: |

|---------|

|---------|

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15 | Unimplemented: Read as '0' |

|--------|----------------------------|

|--------|----------------------------|

bit 14-8 INT1R<6:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 0000001 = Input tied to CMP1 0000000 = Input tied to Vss bit 7-0 Unimplemented: Read as '0'

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

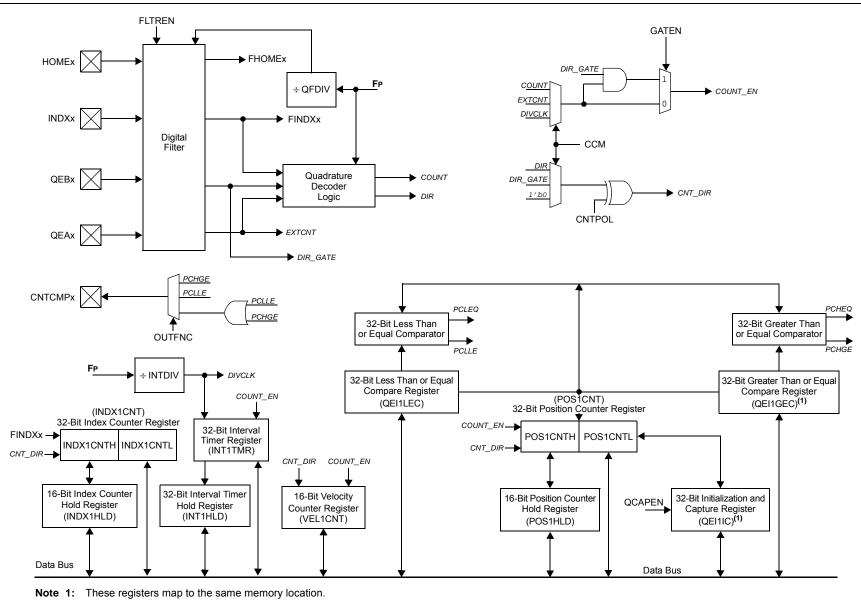

## FIGURE 17-1: QEI BLOCK DIAGRAM

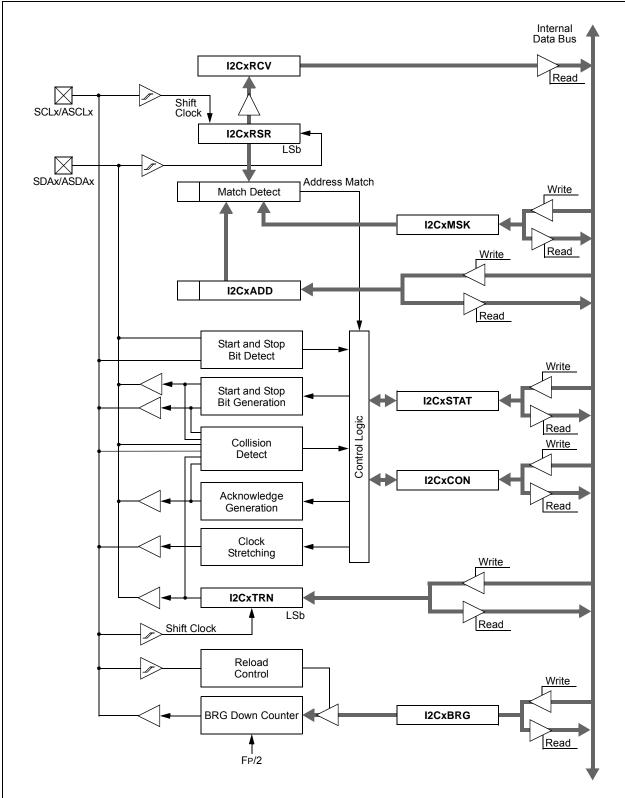

FIGURE 19-1: I2Cx BLOCK DIAGRAM (X = 1 OR 2)

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                          | U-0                                                                                            | U-0                                                                                      | U-0      | U-0          | U-0              | U-0             | U-0   |  |  |  |

|------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------|--------------|------------------|-----------------|-------|--|--|--|

| _                            | —                                                                                              | —                                                                                        |          | —            | —                | —               | _     |  |  |  |

| bit 15                       |                                                                                                |                                                                                          |          |              |                  |                 | bit   |  |  |  |

|                              |                                                                                                |                                                                                          |          |              |                  |                 |       |  |  |  |

| R/W-0                        | R/W-0                                                                                          | R/W-0                                                                                    | U-0      | R/W-0        | R/W-0            | R/W-0           | R/W-0 |  |  |  |

| IVRIE                        | WAKIE                                                                                          | ERRIE                                                                                    | —        | FIFOIE       | RBOVIE           | RBIE            | TBIE  |  |  |  |

| bit 7                        |                                                                                                |                                                                                          |          |              |                  |                 | bit   |  |  |  |

|                              |                                                                                                |                                                                                          |          |              |                  |                 |       |  |  |  |

| <b>Legend:</b><br>R = Readab | la hit                                                                                         | W = Writable b                                                                           | .it      |              | montod bit rook  | l oo 'O'        |       |  |  |  |

| n = Value a                  |                                                                                                | '1' = Bit is set                                                                         | אנ       | 0 = Onimpler | mented bit, read | x = Bit is unkr |       |  |  |  |

|                              | IL POR                                                                                         | I = DILIS SEL                                                                            |          |              | areu             |                 | IOWI  |  |  |  |

| bit 15-8                     | Unimplemen                                                                                     | ted: Read as '0                                                                          | ,        |              |                  |                 |       |  |  |  |

| bit 7                        | -                                                                                              |                                                                                          |          | bit          |                  |                 |       |  |  |  |

|                              |                                                                                                | IVRIE: Invalid Message Interrupt Enable bit<br>1 = Interrupt request is enabled          |          |              |                  |                 |       |  |  |  |

|                              |                                                                                                | request is not er                                                                        |          |              |                  |                 |       |  |  |  |

| bit 6                        | WAKIE: Bus                                                                                     | WAKIE: Bus Wake-up Activity Interrupt Enable bit                                         |          |              |                  |                 |       |  |  |  |

|                              |                                                                                                | equest is enabl                                                                          |          |              |                  |                 |       |  |  |  |

|                              |                                                                                                | request is not er                                                                        |          |              |                  |                 |       |  |  |  |

| bit 5                        |                                                                                                | Interrupt Enabl                                                                          |          |              |                  |                 |       |  |  |  |

|                              | <ol> <li>I = Interrupt request is enabled</li> <li>Interrupt request is not enabled</li> </ol> |                                                                                          |          |              |                  |                 |       |  |  |  |

| bit 4                        |                                                                                                | -                                                                                        |          |              |                  |                 |       |  |  |  |

| bit 3                        | -                                                                                              | Unimplemented: Read as '0'                                                               |          |              |                  |                 |       |  |  |  |

| DIL J                        |                                                                                                | <b>FIFOIE:</b> FIFO Almost Full Interrupt Enable bit<br>1 = Interrupt request is enabled |          |              |                  |                 |       |  |  |  |

|                              | 0 = Interrupt request is not enabled                                                           |                                                                                          |          |              |                  |                 |       |  |  |  |

| bit 2                        | <b>RBOVIE:</b> RX                                                                              | <b>RBOVIE:</b> RX Buffer Overflow Interrupt Enable bit                                   |          |              |                  |                 |       |  |  |  |

|                              | 1 = Interrupt request is enabled                                                               |                                                                                          |          |              |                  |                 |       |  |  |  |

|                              | 0 = Interrupt i                                                                                | request is not er                                                                        | nabled   |              |                  |                 |       |  |  |  |

| bit 1                        |                                                                                                | ffer Interrupt En                                                                        |          |              |                  |                 |       |  |  |  |

|                              |                                                                                                | equest is enabl                                                                          |          |              |                  |                 |       |  |  |  |

|                              |                                                                                                | request is not er                                                                        | nabled   |              |                  |                 |       |  |  |  |

|                              | •                                                                                              | •                                                                                        |          |              |                  |                 |       |  |  |  |

| bit 0                        | TBIE: TX Buf                                                                                   | fer Interrupt Ena<br>request is enabl                                                    | able bit |              |                  |                 |       |  |  |  |

## REGISTER 21-7: CXINTE: ECANX INTERRUPT ENABLE REGISTER

# REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

| bit 7-5 | SSRC<2:0>: Sample Trigger Source Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If SSRCG = 1:<br>111 = Reserved<br>110 = PTGO15 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>101 = PTGO14 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>100 = PTGO13 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>011 = PTGO12 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion <sup>(2)</sup> |

|         | If SSRCG = 0:<br>111 = Internal counter ends sampling and starts conversion (auto-convert)<br>110 = CTMU ends sampling and starts conversion<br>101 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>101 - Reserved</li> <li>100 = Timer5 compare ends sampling and starts conversion</li> <li>011 = PWM primary Special Event Trigger ends sampling and starts conversion</li> <li>010 = Timer3 compare ends sampling and starts conversion</li> <li>001 = Active transition on the INT0 pin ends sampling and starts conversion</li> <li>000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)</li> </ul>                                                                                                                                                                                                                                                                        |

| bit 4   | SSRCG: Sample Trigger Source Group bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | See SSRC<2:0> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 3   | <ul> <li>SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS&lt;1:0&gt; = 01 or 1x)</li> <li><u>In 12-bit mode (AD21B = 1), SIMSAM is Unimplemented and is Read as '0':</u></li> <li>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01)</li> <li>0 = Samples multiple channels individually in sequence</li> </ul>                                                                                                                                                                                                                                                                                              |

| bit 2   | ASAM: ADC1 Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Sampling begins immediately after the last conversion; SAMP bit is auto-set</li> <li>0 = Sampling begins when the SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 1   | SAMP: ADC1 Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = ADC Sample-and-Hold amplifiers are sampling</li> <li>0 = ADC Sample-and-Hold amplifiers are holding</li> <li>If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1. If SSRC&lt;2:0&gt; = 000, software can write '0' to end sampling and start conversion. If SSRC&lt;2:0&gt; ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>                                                                                                                                                                                                                                                                                         |

| bit 0   | DONE: ADC1 Conversion Status bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = ADC conversion cycle has completed</li> <li>0 = ADC conversion has not started or is in progress</li> <li>Automatically set by hardware when the ADC conversion is complete. Software can write '0' to clear the DONE status bit (software is not allowed to write '1'). Clearing this bit does NOT affect any operation in progress. Automatically cleared by hardware at the start of a new conversion.</li> </ul>                                                                                                                                                                                                                                                                                       |

| Note 1: | See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

- 2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- **3:** Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the Program Counter is changed as a result of the instruction, or a PSV or Table Read is performed, or an SFR register is read. In these cases, the execution takes multiple instruction cycles with the additional instruction cycle(s) executed as a NOP. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note: For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157). For more information on instructions that take more than one instruction cycle to execute, refer to **"CPU"** (DS70359) in the *"dsPIC33/PIC24 Family Reference Manual"*, particularly the **"Instruction Flow Types"** section.

| Field               | Description                                                                          |

|---------------------|--------------------------------------------------------------------------------------|

| #text               | Means literal defined by "text"                                                      |

| (text)              | Means "content of text"                                                              |

| [text]              | Means "the location addressed by text"                                               |

| {}                  | Optional field or operation                                                          |

| $a \in \{b, c, d\}$ | a is selected from the set of values b, c, d                                         |

| <n:m></n:m>         | Register bit field                                                                   |

| .b                  | Byte mode selection                                                                  |

| .d                  | Double-Word mode selection                                                           |

| .S                  | Shadow register select                                                               |

| .w                  | Word mode selection (default)                                                        |

| Acc                 | One of two accumulators {A, B}                                                       |

| AWB                 | Accumulator write back destination address register ∈ {W13, [W13]+ = 2}              |

| bit4                | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$        |

| C, DC, N, OV, Z     | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |

| Expr                | Absolute address, label or expression (resolved by the linker)                       |

| f                   | File register address ∈ {0x00000x1FFF}                                               |

| lit1                | 1-bit unsigned literal $\in \{0,1\}$                                                 |

| lit4                | 4-bit unsigned literal ∈ {015}                                                       |

| lit5                | 5-bit unsigned literal ∈ {031}                                                       |

| lit8                | 8-bit unsigned literal ∈ {0255}                                                      |

| lit10               | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode               |

| lit14               | 14-bit unsigned literal ∈ {016384}                                                   |

| lit16               | 16-bit unsigned literal ∈ {065535}                                                   |

| lit23               | 23-bit unsigned literal ∈ {08388608}; LSb must be '0'                                |

| None                | Field does not require an entry, can be blank                                        |

| OA, OB, SA, SB      | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate          |

| PC                  | Program Counter                                                                      |

| Slit10              | 10-bit signed literal ∈ {-512511}                                                    |

| Slit16              | 16-bit signed literal ∈ {-3276832767}                                                |

| Slit6               | 6-bit signed literal ∈ {-1616}                                                       |

| Wb                  | Base W register ∈ {W0W15}                                                            |

| Wd                  | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                    |

| Wdo                 | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

## TABLE 28-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Field | Description                                                                                                                                                                                                                                                          |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm,Wn | Dividend, Divisor working register pair (direct addressing)                                                                                                                                                                                                          |

| Wm*Wm | Multiplicand and Multiplier working register pair for Square instructions $\in$ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                                    |

| Wm*Wn | Multiplicand and Multiplier working register pair for DSP instructions ∈<br>{W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                                        |

| Wn    | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                                                                |

| Wnd   | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                                                                    |

| Wns   | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                                                         |

| WREG  | W0 (working register used in file register instructions)                                                                                                                                                                                                             |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                                         |

| Wso   | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                                      |

| Wx    | X Data Space Prefetch Address register for DSP instructions<br>∈ {[W8] + = 6, [W8] + = 4, [W8] + = 2, [W8], [W8] - = 6, [W8] - = 4, [W8] - = 2,<br>[W9] + = 6, [W9] + = 4, [W9] + = 2, [W9], [W9] - = 6, [W9] - = 4, [W9] - = 2,<br>[W9 + W12], none}                |

| Wxd   | X Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |

| Wy    | Y Data Space Prefetch Address register for DSP instructions<br>∈ {[W10] + = 6, [W10] + = 4, [W10] + = 2, [W10], [W10] - = 6, [W10] - = 4, [W10] - = 2,<br>[W11] + = 6, [W11] + = 4, [W11] + = 2, [W11], [W11] - = 6, [W11] - = 4, [W11] - = 2,<br>[W11 + W12], none} |

| Wyd   | Y Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                             |

| TABLE 28-1: | SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED) | ) |

|-------------|-------------------------------------------------|---|

|             | ······································          | , |

| Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)<br>Operating temperature-40°C $\leq$ TA $\leq$ +85°C for Industr<br>-40°C $\leq$ TA $\leq$ +125°C for Exten |                               |               | °C for Industrial |                       |                 |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------|-------------------|-----------------------|-----------------|--|

| Parameter<br>No.                                                                                                                                                                     | Тур.                          | Max.          | Units Conditions  |                       | tions           |  |

| Power-Down Cu                                                                                                                                                                        | urrent (IPD) <sup>(1)</sup> - | dsPIC33EP32GI | P50X, dsPIC33EF   | P32MC20X/50X and PIC2 | 4EP32GP/MC20X   |  |

| DC60d                                                                                                                                                                                | 30                            | 100           | μA                | -40°C                 |                 |  |

| DC60a                                                                                                                                                                                | 35                            | 100           | μA                | +25°C                 | 3.3V            |  |

| DC60b                                                                                                                                                                                | 150                           | 200           | μA                | +85°C                 | 3.3V            |  |

| DC60c                                                                                                                                                                                | 250                           | 500           | μA                | +125°C                |                 |  |

| Power-Down Cu                                                                                                                                                                        | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP64GI | P50X, dsPIC33EF   | P64MC20X/50X and PIC2 | 4EP64GP/MC20X   |  |

| DC60d                                                                                                                                                                                | 25                            | 100           | μA                | -40°C                 |                 |  |

| DC60a                                                                                                                                                                                | 30                            | 100           | μA                | +25°C                 | 3.3V            |  |

| DC60b                                                                                                                                                                                | 150                           | 350           | μΑ                | +85°C                 |                 |  |

| DC60c                                                                                                                                                                                | 350                           | 800           | μΑ                | +125°C                |                 |  |

| Power-Down Cu                                                                                                                                                                        | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP128G | P50X, dsPIC33E    | P128MC20X/50X and PIC | 24EP128GP/MC20X |  |

| DC60d                                                                                                                                                                                | 30                            | 100           | μΑ                | -40°C                 |                 |  |

| DC60a                                                                                                                                                                                | 35                            | 100           | μΑ                | +25°C                 | 3.3V            |  |

| DC60b                                                                                                                                                                                | 150                           | 350           | μΑ                | +85°C                 | 5.50            |  |

| DC60c                                                                                                                                                                                | 550                           | 1000          | μΑ                | +125°C                |                 |  |

| Power-Down Cu                                                                                                                                                                        | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP256G | P50X, dsPIC33E    | P256MC20X/50X and PIC | 24EP256GP/MC20X |  |

| DC60d                                                                                                                                                                                | 35                            | 100           | μΑ                | -40°C                 |                 |  |

| DC60a                                                                                                                                                                                | 40                            | 100           | μΑ                | +25°C                 | 3.3V            |  |

| DC60b                                                                                                                                                                                | 250                           | 450           | μΑ                | +85°C                 |                 |  |

| DC60c                                                                                                                                                                                | 1000                          | 1200          | μΑ                | +125°C                |                 |  |

| Power-Down Cu                                                                                                                                                                        | urrent (IPD) <sup>(1)</sup> – | dsPIC33EP512G | P50X, dsPIC33E    | P512MC20X/50X and PIC | 24EP512GP/MC20X |  |

| DC60d                                                                                                                                                                                | 40                            | 100           | μΑ                | -40°C                 |                 |  |