Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

|                            |                                                                                  |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc204-h-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                                                                    | 25  |

|-------|----------------------------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers and Microcontrollers         | 29  |

| 3.0   | CPU                                                                                                | 35  |

| 4.0   | Memory Organization                                                                                | 45  |

| 5.0   | Flash Program Memory                                                                               | 119 |

| 6.0   | Resets                                                                                             | 123 |

| 7.0   | Interrupt Controller                                                                               | 127 |

| 8.0   | Direct Memory Access (DMA)                                                                         | 139 |

| 9.0   | Oscillator Configuration                                                                           | 153 |

| 10.0  | Power-Saving Features                                                                              | 163 |

| 11.0  | I/O Ports                                                                                          | 173 |

| 12.0  | Timer1                                                                                             | 203 |

| 13.0  | Timer2/3 and Timer4/5                                                                              | 207 |

| 14.0  | Input Capture                                                                                      | 213 |

|       | Output Compare                                                                                     |     |

| 16.0  | High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)                     | 225 |

| 17.0  | Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only) | 249 |

|       | Serial Peripheral Interface (SPI)                                                                  |     |

| 19.0  | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                                      | 273 |

| 20.0  | Universal Asynchronous Receiver Transmitter (UART)                                                 | 281 |

| 21.0  | Enhanced CAN (ECAN™) Module (dsPIC33EPXXXGP/MC50X Devices Only)                                    | 287 |

| 22.0  | Charge Time Measurement Unit (CTMU)                                                                | 315 |

| 23.0  | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                                                    | 321 |

| 24.0  | Peripheral Trigger Generator (PTG) Module                                                          | 337 |

|       | Op Amp/Comparator Module                                                                           |     |

| 26.0  | Programmable Cyclic Redundancy Check (CRC) Generator                                               | 373 |

| 27.0  | Special Features                                                                                   | 379 |

| 28.0  | Instruction Set Summary                                                                            | 387 |

| 29.0  | Development Support                                                                                | 397 |

| 30.0  | Electrical Characteristics                                                                         | 401 |

| 31.0  | High-Temperature Electrical Characteristics                                                        | 467 |

| 32.0  | DC and AC Device Characteristics Graphs                                                            | 475 |

| 33.0  | Packaging Information                                                                              | 479 |

|       | endix A: Revision History                                                                          |     |

| Index | X                                                                                                  | 517 |

| The I | Microchip Web Site                                                                                 | 525 |

| Cust  | omer Change Notification Service                                                                   | 525 |

| Cust  | omer Support                                                                                       | 525 |

| Prod  | uct Identification System                                                                          | 527 |

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS AND MICROCONTROLLERS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

#### 2.1 Basic Connection Requirements

Getting started with the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used) (see Section 2.2 "Decoupling Capacitors")

- VCAP

(see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

VREF+/VREF- pins are used when external voltage reference for the ADC module is implemented

**Note:** The AVDD and AVSS pins must be connected, independent of the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended to use ceramic capacitors.

- Placement on the printed circuit board: The

decoupling capacitors should be placed as close

to the pins as possible. It is recommended to

place the capacitors on the same side of the

board as the device. If space is constricted, the

capacitor can be placed on another layer on the

PCB using a via; however, ensure that the trace

length from the pin to the capacitor is within

one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, above tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01 μF to 0.001 μF. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1 μF in parallel with 0.001 μF.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

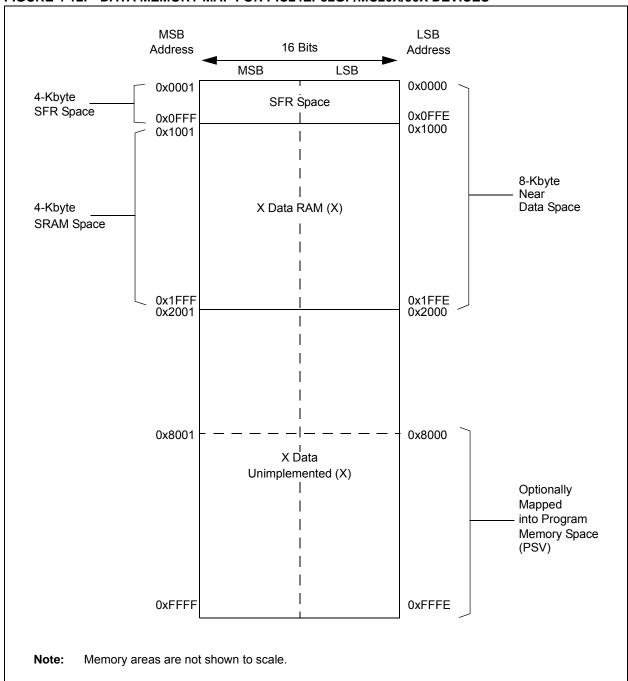

FIGURE 4-12: DATA MEMORY MAP FOR PIC24EP32GP/MC20X/50X DEVICES

TABLE 4-4: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8 | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|-------|-------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      | ,      | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >     | _     | _       | -           | 1       | _       | _      | _           | -      | 4400          |

| IPC36        | 0888  | _      | F      | PTG0IP<2:0 | >      | -      | PT     | GWDTIP<    | 2:0>  | -     | PT      | GSTEPIP<2   | :0>     | _       | -      | _           | ı      | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | -      | F      | PTG3IP<2:0 | 0>    | -     | l       | PTG2IP<2:0> | >       | _       | I      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | -      | -      | 1      | -          | _     | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     | 1      | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | -      | -      | 1      | -          | _     | _     | _       | _           | ı       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | _      | _          | -      | -      | 1      | -          | _     | _     | _       | DAE         | DOOVR   | _       | _      | _           | 1      | 0000          |

| INTCON4      | 08C6  | _      | _      | _          | _      | _      | ı      | _          | _     | _     | _       | _           | ı       | _       | _      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | _      | _      | _          | -      |        | ILR<   | 3:0>       |       |       |         |             | VECN    | UM<7:0> |        |             |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-53: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|---------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | 1      | _      | 1      | _      | TRISA10 | TRISA9 | TRISA8 | TRISA7 | -     | -     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 079F          |

| PORTA        | 0E02  | 1      | -      | _      | _      | _      | RA10    | RA9    | RA8    | RA7    | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | 1      | -      | _      | _      | _      | LATA10  | LATA9  | LATA8  | LATA7  | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | 1      | -      | _      | _      | _      | ODCA10  | ODCA9  | ODCA8  | ODCA7  | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | 1      | -      | _      | _      | _      | CNIEA10 | CNIEA9 | CNIEA8 | CNIEA7 | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | 1      | -      | _      | _      | _      | CNPUA10 | CNPUA9 | CNPUA8 | CNPUA7 | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | 1      | -      | _      | _      | _      | CNPDA10 | CNPDA9 | CNPDA8 | CNPDA7 | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | -      | 1      | _      | ı      | 1      | _       | _      | _      | _      | ı     | -     | ANSA4  | -      | _      | ANSA1  | ANSA0  | 0013          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-54: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | _       | _      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-55: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      | _      | _      | -      | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 03FF          |

| PORTC        | 0E22  | -      | _      |        | _      |        | 1      | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx          |

| LATC         | 0E24  | -      | _      |        | _      |        | 1      | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  | _      | _      | ı      |        | ı      | -      | ODCC9  | ODCC8  | ODCC7  | ODCC6  | ODCC5  | ODCC4  | ODCC3  | ODCC2  | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | -      | _      |        | _      |        | 1      | CNIEC9 | CNIEC8 | CNIEC7 | CNIEC6 | CNIEC5 | CNIEC4 | CNIEC3 | CNIEC2 | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  | -      | _      | -      | -      | -      | _      | CNPUC9 | CNPUC8 | CNPUC7 | CNPUC6 | CNPUC5 | CNPUC4 | CNPUC3 | CNPUC2 | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  | -      | _      | -      | _      | _      | _      | CNPDC9 | CNPDC8 | CNPDC7 | CNPDC6 | CNPDC5 | CNPDC4 | CNPDC3 | CNPDC2 | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | ANSC2  | ANSC1  | ANSC0  | 0007          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

#### 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2 where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- · Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

#### 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory and to program two instruction words at a time. See the General Purpose and Motor Control Family tables (Table 1 and Table 2, respectively) for the page sizes of each device.

For more information on erasing and programming Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

## 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time) in Table 30-14 in **Section 30.0 "Electrical Characteristics"**.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

# 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x000000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS

Refer to **Flash Programming**" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual" for details and codes examples on programming using RTSP.

#### 5.4 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/Devices.aspx?dDocName=en555464

#### 5.4.1 KEY RESOURCES

- "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

#### 5.5 Control Registers

Four SFRs are used to erase and write the program Flash memory: NVMCON, NVMKEY, NVMADRH and NVMADRL.

The NVMCON register (Register 5-1) enables and initiates Flash memory erase and write operations.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRH and NVMADRL. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations or the selected page for erase operations.

The NVMADRH register is used to hold the upper 8 bits of the EA, while the NVMADRL register is used to hold the lower 16 bits of the EA.

#### REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   |     | _   |     | _   |     | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R-1 | R-1   | R-1    | R-1   |

|-------|-----|-----|-----|-----|-------|--------|-------|

| _     | _   | _   | _   |     | LSTCH | 1<3:0> |       |

| bit 7 |     |     |     |     |       |        | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-4 Unimplemented: Read as '0'

bit 3-0 LSTCH<3:0>: Last DMAC Channel Active Status bits

1111 = No DMA transfer has occurred since system Reset

1110 = Reserved

•

•

•

0100 = Reserved

0011 = Last data transfer was handled by Channel 3

0010 = Last data transfer was handled by Channel 2

0001 = Last data transfer was handled by Channel 1

0000 = Last data transfer was handled by Channel 0

## 9.1 CPU Clocking System

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices provides six system clock options:

- · Fast RC (FRC) Oscillator

- FRC Oscillator with Phase Locked Loop (PLL)

- · FRC Oscillator with Postscaler

- · Primary (XT, HS or EC) Oscillator

- · Primary Oscillator with PLL

- · Low-Power RC (LPRC) Oscillator

Instruction execution speed or device operating frequency, Fcy, is given by Equation 9-1.

# EQUATION 9-1: DEVICE OPERATING FREQUENCY

$$FCY = Fosc/2$$

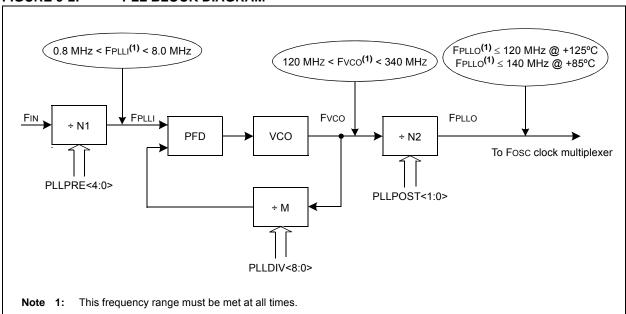

Figure 9-2 is a block diagram of the PLL module.

Equation 9-2 provides the relationship between input frequency (FIN) and output frequency (FPLLO). In clock modes S1 and S3, when the PLL output is selected, FOSC = FPLLO.

Equation 9-3 provides the relationship between input frequency (FIN) and VCO frequency (FVCO).

#### FIGURE 9-2: PLL BLOCK DIAGRAM

#### **EQUATION 9-2:** FPLLO CALCULATION

$$FPLLO = FIN \times \left(\frac{M}{N1 \times N2}\right) = FIN \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2) \times 2(PLLPOST + 1)}\right)$$

Where:

N1 = PLLPRE + 2

$N2 = 2 \times (PLLPOST + 1)$

M = PLLDIV + 2

#### **EQUATION 9-3:** Fvco CALCULATION

$$Fvco = Fin \times \left(\frac{M}{N1}\right) = Fin \times \left(\frac{(PLLDIV + 2)}{(PLLPRE + 2)}\right)$$

# REGISTER 11-9: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| _      |       |       |       | HOME1R<6:0 | )>    |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|------------|-------|-------|-------|

| _     |       |       |       | INDX1R<6:0 | >     |       |       |

| bit 7 |       |       |       |            |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 **HOME1R<6:0>:** Assign QEI1 HOME1 (HOME1) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

bit 7 **Unimplemented:** Read as '0'

bit 6-0 IND1XR<6:0>: Assign QEI1 INDEX1 (INDX1) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

#### 21.4 ECAN Control Registers

#### REGISTER 21-1: CxCTRL1: ECANx CONTROL REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-1  | R/W-0  | R/W-0  |

|--------|-----|-------|-------|--------|--------|--------|--------|

| _      | _   | CSIDL | ABAT  | CANCKS | REQOP2 | REQOP1 | REQOP0 |

| bit 15 |     |       |       |        |        |        | bit 8  |

| R-1     | R-0     | R-0     | U-0 | R/W-0  | U-0 | U-0 | R/W-0 |  |  |

|---------|---------|---------|-----|--------|-----|-----|-------|--|--|

| OPMODE2 | OPMODE1 | OPMODE0 | _   | CANCAP | _   | _   | WIN   |  |  |

| bit 7   |         |         |     |        |     |     |       |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13 CSIDL: ECANx Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 ABAT: Abort All Pending Transmissions bit

1 = Signals all transmit buffers to abort transmission

0 = Module will clear this bit when all transmissions are aborted

bit 11 CANCKS: ECANx Module Clock (FCAN) Source Select bit

1 = FCAN is equal to 2 \* FP

0 = FCAN is equal to FP

bit 10-8 **REQOP<2:0>:** Request Operation Mode bits

111 = Set Listen All Messages mode

110 = Reserved

101 = Reserved

100 = Set Configuration mode

011 = Set Listen Only mode

010 = Set Loopback mode

001 = Set Disable mode

000 = Set Normal Operation mode

bit 7-5 **OPMODE<2:0>**: Operation Mode bits

111 = Module is in Listen All Messages mode

110 = Reserved

101 = Reserved

100 = Module is in Configuration mode

011 = Module is in Listen Only mode

010 = Module is in Loopback mode

001 = Module is in Disable mode

000 = Module is in Normal Operation mode

bit 4 Unimplemented: Read as '0'

bit 3 CANCAP: CAN Message Receive Timer Capture Event Enable bit

1 = Enables input capture based on CAN message receive

0 = Disables CAN capture

bit 2-1 **Unimplemented:** Read as '0'

bit 0 WIN: SFR Map Window Select bit

1 = Uses filter window

0 = Uses buffer window

# REGISTER 21-17: CxRXFnEID: ECANx ACCEPTANCE FILTER n EXTENDED IDENTIFIER REGISTER (n = 0-15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **EID<15:0>:** Extended Identifier bits

1 = Message address bit, EIDx, must be '1' to match filter

0 = Message address bit, EIDx, must be '0' to match filter

#### REGISTER 21-18: CxFMSKSEL1: ECANx FILTER 7-0 MASK SELECTION REGISTER 1

| R/W-0      | R/W-0 | R/W-0      | R/W-0 | R/W-0      | R/W-0 | R/W-0      | R/W-0 |

|------------|-------|------------|-------|------------|-------|------------|-------|

| F7MSK<1:0> |       | F6MSK<1:0> |       | F5MSK<1:0> |       | F4MSK<1:0> |       |

| bit 15     |       |            |       | •          |       | •          | bit 8 |

| R/W-0      | R/W-0 | R/W-0      | R/W-0 | R/W-0      | R/W-0 | R/W-0      | R/W-0 |

|------------|-------|------------|-------|------------|-------|------------|-------|

| F3MSK<1:0> |       | F2MSK<1:0> |       | F1MSK<1:0> |       | F0MSK<1:0> |       |

| bit 7      |       |            |       |            |       |            | bit 0 |

Legend:

bit 3-2

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 F7MSK<1:0>: Mask Source for Filter 7 bits

11 = Reserved

10 = Acceptance Mask 2 registers contain mask

01 = Acceptance Mask 1 registers contain mask

00 = Acceptance Mask 0 registers contain mask

bit 13-12 **F6MSK<1:0>:** Mask Source for Filter 6 bits (same values as bits<15:14>)

bit 11-10 **F5MSK<1:0>:** Mask Source for Filter 5 bits (same values as bits<15:14>)

bit 9-8 **F4MSK<1:0>:** Mask Source for Filter 4 bits (same values as bits<15:14>)

bit 7-6 **F3MSK<1:0>:** Mask Source for Filter 3 bits (same values as bits<15:14>)

bit 5-4 **F2MSK<1:0>:** Mask Source for Filter 2 bits (same values as bits<15:14>)

**F1MSK<1:0>:** Mask Source for Filter 1 bits (same values as bits<15:14>)

bit 1-0 **F0MSK<1:0>:** Mask Source for Filter 0 bits (same values as bits<15:14>)

# REGISTER 23-2: AD1CON2: ADC1 CONTROL REGISTER 2 (CONTINUED)

bit 1 BUFM: Buffer Fill Mode Select bit

- 1 = Starts the buffer filling the first half of the buffer on the first interrupt and the second half of the buffer on next interrupt

- 0 = Always starts filling the buffer from the start address.

- bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses channel input selects for Sample MUXA on first sample and Sample MUXB on next sample

- 0 = Always uses channel input selects for Sample MUXA

TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

| bit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                                                                                      |

|---------|------------------------|-------------|---------------------------------------------------------------------------------------------------------|

|         | PTGCTRL(1)             | 0000        | Reserved.                                                                                               |

|         |                        | 0001        | Reserved.                                                                                               |

|         |                        | 0010        | Disable Step Delay Timer (PTGSD).                                                                       |

|         |                        | 0011        | Reserved.                                                                                               |

|         |                        | 0100        | Reserved.                                                                                               |

|         |                        | 0101        | Reserved.                                                                                               |

|         |                        | 0110        | Enable Step Delay Timer (PTGSD).                                                                        |

|         |                        | 0111        | Reserved.                                                                                               |

|         |                        | 1000        | Start and wait for the PTG Timer0 to match the Timer0 Limit Register.                                   |

|         |                        | 1001        | Start and wait for the PTG Timer1 to match the Timer1 Limit Register.                                   |

|         |                        | 1010        | Reserved.                                                                                               |

|         |                        | 1011        | Wait for the software trigger bit transition from low-to-high before continuing (PTGSWT = $0$ to $1$ ). |

|         |                        | 1100        | Copy contents of the Counter 0 register to the AD1CHS0 register.                                        |

|         |                        | 1101        | Copy contents of the Counter 1 register to the AD1CHS0 register.                                        |

|         |                        | 1110        | Copy contents of the Literal 0 register to the AD1CHS0 register.                                        |

|         |                        | 1111        | Generate triggers indicated in the Broadcast Trigger Enable register (PTGBTE).                          |

|         | PTGADD(1)              | 0000        | Add contents of the PTGADJ register to the Counter 0 Limit register (PTGC0LIM).                         |

|         |                        | 0001        | Add contents of the PTGADJ register to the Counter 1 Limit register (PTGC1LIM).                         |

|         |                        | 0010        | Add contents of the PTGADJ register to the Timer0 Limit register (PTGT0LIM).                            |

|         |                        | 0011        | Add contents of the PTGADJ register to the Timer1 Limit register (PTGT1LIM).                            |

|         |                        | 0100        | prop:prop:prop:prop:prop:prop:prop:prop                                                                 |

|         |                        | 0101        | Add contents of the PTGADJ register to the Literal 0 register (PTGL0).                                  |

|         |                        | 0110        | Reserved.                                                                                               |

|         |                        | 0111        | Reserved.                                                                                               |

|         | PTGCOPY <sup>(1)</sup> | 1000        | Copy contents of the PTGHOLD register to the Counter 0 Limit register (PTGC0LIM).                       |

|         |                        | 1001        | Copy contents of the PTGHOLD register to the Counter 1 Limit register (PTGC1LIM).                       |

|         |                        | 1010        | Copy contents of the PTGHOLD register to the Timer0 Limit register (PTGT0LIM).                          |

|         |                        | 1011        | Copy contents of the PTGHOLD register to the Timer1 Limit register (PTGT1LIM).                          |

|         |                        | 1100        | Copy contents of the PTGHOLD register to the Step Delay Limit register (PTGSDLIM).                      |

|         |                        | 1101        | Copy contents of the PTGHOLD register to the Literal 0 register (PTGL0).                                |

|         |                        | 1110        | Reserved.                                                                                               |

|         |                        | 1111        | Reserved.                                                                                               |

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

<sup>2:</sup> Refer to Table 24-2 for the trigger output descriptions.

**<sup>3:</sup>** This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

TABLE 27-1: CONFIGURATION BYTE REGISTER MAP

| File<br>Name | Address | Device<br>Memory<br>Size<br>(Kbytes) | Bits 23-8    | Bit 7                   | Bit 6                  | Bit 5   | Bit 4                   | Bit 3                   | Bit 2        | Bit 1     | Bit 0   |

|--------------|---------|--------------------------------------|--------------|-------------------------|------------------------|---------|-------------------------|-------------------------|--------------|-----------|---------|

| Reserved     | 0057EC  | 32                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 00AFEC  | 64                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 0157EC  | 128                                  | _            | _                       | _                      | _       | _                       | _                       | _            | _         | -       |

|              | 02AFEC  | 256                                  |              |                         |                        |         |                         |                         |              |           |         |

|              | 0557EC  | 512                                  |              |                         |                        |         |                         |                         |              |           |         |

| Reserved     | 0057EE  | 32                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 00AFEE  | 64                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 0157EE  | 128                                  | _            | _                       | _                      | _       | _                       | _                       | _            | _         | _       |

|              | 02AFEE  | 256                                  |              |                         |                        |         |                         |                         |              |           |         |

|              | 0557EE  | 512                                  |              |                         |                        |         |                         |                         |              |           |         |

| FICD         | 0057F0  | 32                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 00AFF0  | 64                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 0157F0  | 128                                  | i _          | Reserved <sup>(3)</sup> | _                      | JTAGEN  | Reserved <sup>(2)</sup> | Reserved <sup>(3)</sup> | _            | ICS<      | :1:0>   |

|              | 02AFF0  | 256                                  |              |                         |                        |         |                         | reserved                |              |           |         |

|              | 0557F0  | 512                                  |              |                         |                        |         |                         |                         |              |           |         |

| FPOR         | 0057F2  | 32                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 00AFF2  | 64                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 0157F2  | 128                                  | _            | WDTV                    | VIN<1:0>               | ALTI2C2 | ALTI2C1                 | Reserved <sup>(3)</sup> | ) _   _      |           | _       |

|              | 02AFF2  | 256                                  |              |                         |                        |         |                         |                         |              |           |         |

|              | 0557F2  | 512                                  |              |                         |                        |         |                         |                         |              |           |         |

| FWDT         | 0057F4  | 32                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 00AFF4  | 64                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 0157F4  | 128                                  | _            | FWDTEN                  | WINDIS                 | PLLKEN  | WDTPRE                  |                         | WDTPOST<3:0> |           |         |

|              | 02AFF4  | 256                                  |              |                         |                        |         |                         |                         |              |           |         |

|              | 0557F4  | 512                                  |              |                         |                        |         |                         |                         |              |           |         |

| FOSC         | 0057F6  | 32                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 00AFF6  | 64                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 0157F6  | 128                                  | _            | FCKS                    | SM<1:0>                | IOL1WAY | _                       | _                       | OSCIOFNC     | POSCM     | ID<1:0> |

|              | 02AFF6  | 256                                  |              |                         |                        | .02     |                         |                         | 000.01.110   |           |         |

|              | 0557F6  | 512                                  |              |                         |                        |         |                         |                         |              |           |         |

| FOSCSEL      | 0057F8  | 32                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 00AFF8  | 64                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 0157F8  | 128                                  | _            | IESO                    | PWMLOCK <sup>(1)</sup> | _       | _                       | _                       | F            | NOSC<2:0> |         |

|              | 02AFF8  | 256                                  |              |                         |                        |         |                         |                         |              |           |         |

|              | 0557F8  | 512                                  |              |                         |                        |         |                         |                         |              |           |         |

| FGS          | 0057FA  | 32                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 00AFFA  | 64                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 0157FA  | 128                                  | _            | _                       | _                      | _       | _                       | _                       | _            | GCP       | GWRP    |

|              | 02AFFA  | 256                                  |              |                         |                        |         |                         |                         |              |           |         |

|              | 0557FA  | 512                                  |              |                         |                        |         |                         |                         |              |           |         |

| Reserved     | 0057FC  | 32                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 00AFFC  | 64                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 0157FC  | 128                                  | _            | _                       | _                      | _       | _                       | _                       | _            | _         | _       |

|              | 02AFFC  | 256                                  |              |                         |                        |         |                         |                         |              |           |         |

|              | 0557FC  | 512                                  |              |                         |                        |         |                         |                         |              |           |         |

| Reserved     | 057FFE  | 32                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 00AFFE  | 64                                   |              |                         |                        |         |                         |                         |              |           |         |

|              | 0157FE  | 128                                  | _            | _                       | _                      | _       | _                       | _                       |              |           | _       |

|              | 02AFFE  | 256                                  |              |                         |                        |         |                         |                         |              |           | _       |

|              | 0557FE  | 512                                  |              |                         |                        |         |                         |                         |              |           |         |

| l amandi     |         |                                      | read as '1'. |                         |                        |         |                         |                         |              |           |         |

**Legend:** — = unimplemented, read as '1'.

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

<sup>2:</sup> This bit is reserved and must be programmed as '0'.

<sup>3:</sup> These bits are reserved and must be programmed as '1'.

TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| .,,,               | _L Z0-Z.             |         | COCTION SET OVERVIEW                      | (CONTINUED)                                   |               |                               |                          |  |  |  |

|--------------------|----------------------|---------|-------------------------------------------|-----------------------------------------------|---------------|-------------------------------|--------------------------|--|--|--|

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax                           | Description                                   | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |  |  |  |

| 9                  | BTG                  | BTG     | f,#bit4                                   | Bit Toggle f                                  | 1             | 1                             | None                     |  |  |  |

|                    |                      | BTG     | Ws,#bit4                                  | Bit Toggle Ws                                 | 1             | 1                             | None                     |  |  |  |

| 10                 | BTSC                 | BTSC    | f,#bit4                                   | Bit Test f, Skip if Clear                     | 1             | 1<br>(2 or 3)                 | None                     |  |  |  |

|                    |                      | BTSC    | Ws,#bit4                                  | Bit Test Ws, Skip if Clear                    | 1             | 1<br>(2 or 3)                 | None                     |  |  |  |

| 11                 | BTSS                 | BTSS    | f,#bit4                                   | Bit Test f, Skip if Set                       | 1             | 1<br>(2 or 3)                 | None                     |  |  |  |

|                    |                      | BTSS    | Ws,#bit4                                  | Bit Test Ws, Skip if Set                      | 1             | 1<br>(2 or 3)                 | None                     |  |  |  |

| 12                 | BTST                 | BTST    | f,#bit4                                   | Bit Test f                                    | 1             | 1                             | Z                        |  |  |  |

|                    |                      | BTST.C  | Ws,#bit4                                  | Bit Test Ws to C                              | 1             | 1                             | С                        |  |  |  |

|                    |                      | BTST.Z  | Ws,#bit4                                  | Bit Test Ws to Z                              | 1             | 1                             | Z                        |  |  |  |

|                    |                      | BTST.C  | Ws,Wb                                     | Bit Test Ws <wb> to C</wb>                    | 1             | 1                             | С                        |  |  |  |

|                    |                      | BTST.Z  | Ws,Wb                                     | Bit Test Ws <wb> to Z</wb>                    | 1             | 1                             | Z                        |  |  |  |

| 13                 | BTSTS                | BTSTS   | f,#bit4                                   | Bit Test then Set f                           | 1             | 1                             | Z                        |  |  |  |

|                    |                      | BTSTS.C | Ws,#bit4                                  | Bit Test Ws to C, then Set                    | 1             | 1                             | С                        |  |  |  |

|                    |                      | BTSTS.Z | Ws,#bit4                                  | Bit Test Ws to Z, then Set                    | 1             | 1                             | Z                        |  |  |  |

| 14                 | CALL                 | CALL    | lit23                                     | Call subroutine                               | 2             | 4                             | SFA                      |  |  |  |

|                    |                      | CALL    | Wn                                        | Call indirect subroutine                      | 1             | 4                             | SFA                      |  |  |  |

|                    |                      | CALL.L  | Wn                                        | Call indirect subroutine (long address)       | 1             | 4                             | SFA                      |  |  |  |

| 15                 | CLR                  | CLR     | f                                         | f = 0x0000                                    | 1             | 1                             | None                     |  |  |  |

|                    |                      | CLR     | WREG                                      | WREG = 0x0000                                 | 1             | 1                             | None                     |  |  |  |

|                    |                      | CLR     | Ws                                        | Ws = 0x0000                                   | 1             | 1                             | None                     |  |  |  |

|                    |                      | CLR     | Acc, Wx, Wxd, Wy, Wyd, AWB <sup>(1)</sup> | Clear Accumulator                             | 1             | 1                             | OA,OB,SA,SB              |  |  |  |

| 16                 | CLRWDT               | CLRWDT  |                                           | Clear Watchdog Timer                          | 1             | 1                             | WDTO,Sleep               |  |  |  |

| 17                 | COM                  | COM     | f                                         | f = Ī                                         | 1             | 1                             | N,Z                      |  |  |  |

|                    |                      | COM     | f,WREG                                    | WREG = f                                      | 1             | 1                             | N,Z                      |  |  |  |

|                    |                      | COM     | Ws, Wd                                    | Wd = Ws                                       | 1             | 1                             | N,Z                      |  |  |  |

| 18                 | CP                   | CP      | f                                         | Compare f with WREG                           | 1             | 1                             | C,DC,N,OV,Z              |  |  |  |

|                    |                      | CP      | Wb,#lit8                                  | Compare Wb with lit8                          | 1             | 1                             | C,DC,N,OV,Z              |  |  |  |

|                    |                      | CP      | Wb,Ws                                     | Compare Wb with Ws (Wb – Ws)                  | 1             | 1                             | C,DC,N,OV,Z              |  |  |  |

| 19                 | CP0                  | CP0     | f                                         | Compare f with 0x0000                         | 1             | 1                             | C,DC,N,OV,Z              |  |  |  |

|                    |                      | CP0     | Ws                                        | Compare Ws with 0x0000                        | 1             | 1                             | C,DC,N,OV,Z              |  |  |  |

| 20                 | CPB                  | CPB     | f                                         | Compare f with WREG, with Borrow              | 1             | 1                             | C,DC,N,OV,Z              |  |  |  |

|                    |                      | CPB     | Wb,#lit8                                  | Compare Wb with lit8, with Borrow             | 1             | 1                             | C,DC,N,OV,Z              |  |  |  |

|                    |                      | CPB     | Wb,Ws                                     | Compare Wb with Ws, with Borrow (Wb – Ws – C) | 1             | 1                             | C,DC,N,OV,Z              |  |  |  |

| 21                 | CPSEQ                | CPSEQ   | Wb,Wn                                     | Compare Wb with Wn, skip if =                 | 1             | 1<br>(2 or 3)                 | None                     |  |  |  |

|                    | CPBEQ                | CPBEQ   | Wb,Wn,Expr                                | Compare Wb with Wn, branch if =               | 1             | 1 (5)                         | None                     |  |  |  |

| 22                 | CPSGT                | CPSGT   | Wb,Wn                                     | Compare Wb with Wn, skip if >                 | 1             | 1<br>(2 or 3)                 | None                     |  |  |  |

|                    | CPBGT                | CPBGT   | Wb,Wn,Expr                                | Compare Wb with Wn, branch if >               | 1             | 1 (5)                         | None                     |  |  |  |

| 23                 | CPSLT                | CPSLT   | Wb,Wn                                     | Compare Wb with Wn, skip if <                 | 1             | 1<br>(2 or 3)                 | None                     |  |  |  |

|                    | CPBLT                | CPBLT   | Wb,Wn,Expr                                | Compare Wb with Wn, branch if <               | 1             | 1 (5)                         | None                     |  |  |  |

| 24                 | CPSNE                | CPSNE   | Wb,Wn                                     | Compare Wb with Wn, skip if ≠                 | 1             | 1<br>(2 or 3)                 | None                     |  |  |  |

|                    | CPBNE                | CPBNE   | Wb,Wn,Expr                                | Compare Wb with Wn, branch if ≠               | 1             | 1 (5)                         | None                     |  |  |  |

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

<sup>2:</sup> Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

# 30.2 AC Characteristics and Timing Parameters

This section defines dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X AC characteristics and timing parameters.

TABLE 30-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V                  |  |  |  |  |  |

|--------------------|--------------------------------------------------------------|--|--|--|--|--|

|                    | (unless otherwise stated)                                    |  |  |  |  |  |

| AC CHARACTERISTICS | Operating temperature -40°C ≤ Ta ≤ +85°C for Industrial      |  |  |  |  |  |

| AC CHARACTERISTICS | -40°C ≤ Ta ≤ +125°C for Extended                             |  |  |  |  |  |

|                    | Operating voltage VDD range as described in Section 30.1 "DC |  |  |  |  |  |

|                    | Characteristics".                                            |  |  |  |  |  |

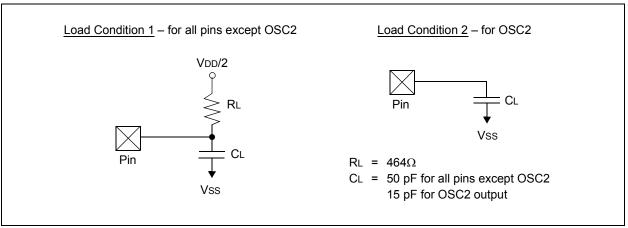

#### FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                    |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | _    | 15   | pF    | In XT and HS modes, when external clock is used to drive OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | _    | _    | 50   | pF    | EC mode                                                       |

| DO58         | Св     | SCLx, SDAx            | _    | _    | 400  | pF    | In I <sup>2</sup> C™ mode                                     |

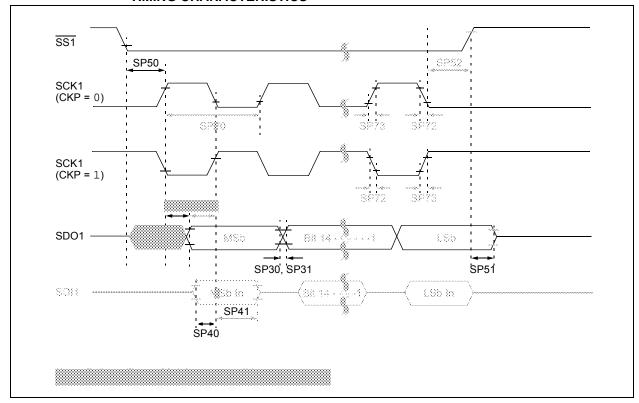

FIGURE 30-29: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

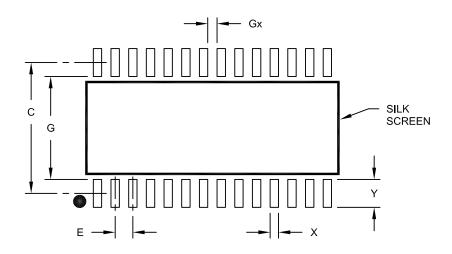

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |      |          |      |

|--------------------------|-------------|------|----------|------|

| Dimension                | MIN         | NOM  | MAX      |      |

| Contact Pitch            | Е           |      | 1.27 BSC |      |

| Contact Pad Spacing      | С           |      | 9.40     |      |

| Contact Pad Width (X28)  | Х           |      |          | 0.60 |

| Contact Pad Length (X28) | Υ           |      |          | 2.00 |

| Distance Between Pads    | Gx          | 0.67 |          |      |

| Distance Between Pads    | G           | 7.40 |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A

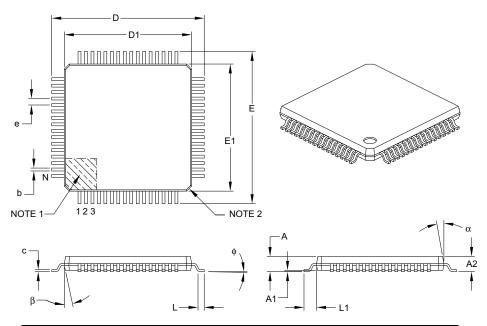

## 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |           |      |  |

|--------------------------|------------------|-------------|-----------|------|--|

|                          | Dimension Limits | MIN         | NOM       | MAX  |  |

| Number of Leads          | N                |             | 64        |      |  |

| Lead Pitch               | е                |             | 0.50 BSC  |      |  |

| Overall Height           | Α                | _           | -         | 1.20 |  |

| Molded Package Thickness | A2               | 0.95        | 1.00      | 1.05 |  |

| Standoff                 | A1               | 0.05        | _         | 0.15 |  |

| Foot Length              | L                | 0.45        | 0.60      | 0.75 |  |

| Footprint                | L1               | 1.00 REF    |           |      |  |

| Foot Angle               | ф                | 0°          | 3.5°      | 7°   |  |

| Overall Width            | E                |             | 12.00 BSC |      |  |

| Overall Length           | D                |             | 12.00 BSC |      |  |

| Molded Package Width     | E1               |             | 10.00 BSC |      |  |

| Molded Package Length    | D1               |             | 10.00 BSC |      |  |

| Lead Thickness           | С                | 0.09        | _         | 0.20 |  |

| Lead Width               | b                | 0.17        | 0.22      | 0.27 |  |

| Mold Draft Angle Top     | α                | 11°         | 12°       | 13°  |  |

| Mold Draft Angle Bottom  | β                | 11°         | 12°       | 13°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B