Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Betano                     |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 35                                                                                |

| Program Memory Size        | 512KB (170K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 24K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 9x10b/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 44-TQFP                                                                           |

| Supplier Device Package    | 44-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc204t-e-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

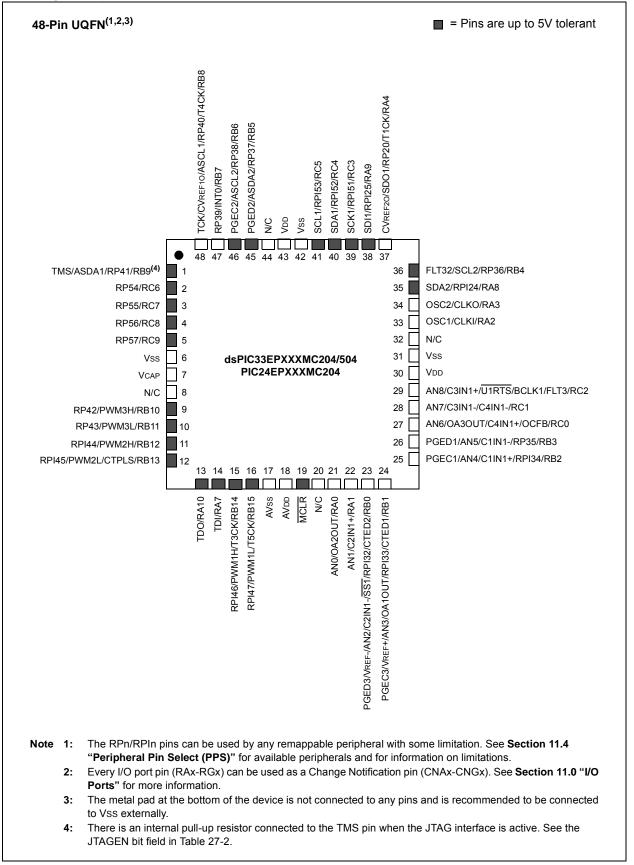

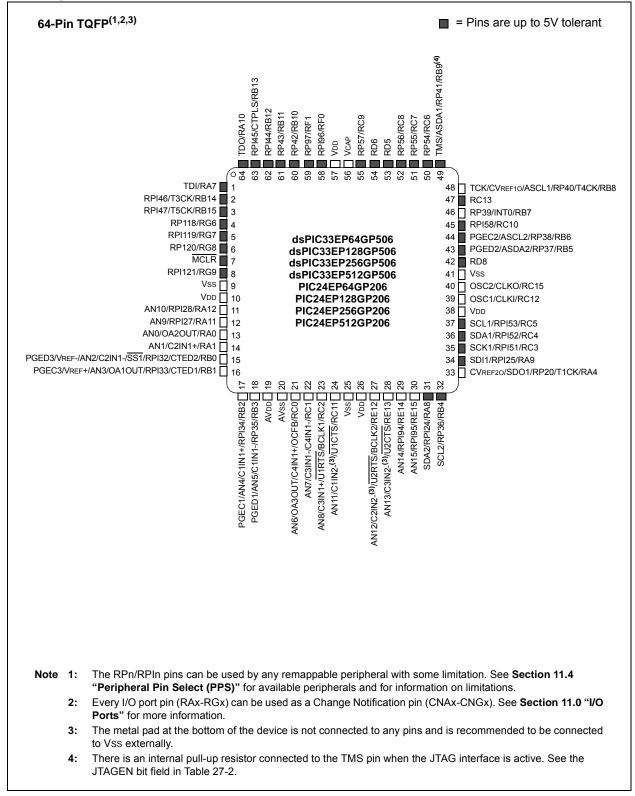

# Pin Diagrams (Continued)

## **Pin Diagrams (Continued)**

#### TABLE 4-53: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|---------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      | _      | TRISA10 | TRISA9 | TRISA8 | TRISA7 | -     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 079F          |

| PORTA        | 0E02  |        | _      | _      | -      | _      | RA10    | RA9    | RA8    | RA7    | -     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | LATA10  | LATA9  | LATA8  | LATA7  | -     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | —      | —      | _      |        | ODCA10  | ODCA9  | ODCA8  | ODCA7  | —     | —     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | —      | —      | _      |        | CNIEA10 | CNIEA9 | CNIEA8 | CNIEA7 | —     | —     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | —      | —      | _      |        | CNPUA10 | CNPUA9 | CNPUA8 | CNPUA7 | —     | —     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | —      | —      | _      |        | CNPDA10 | CNPDA9 | CNPDA8 | CNPDA7 | —     | —     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | _      | _      | —       | _      | —      | _      | _     | —     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-54: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | -       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-55: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC204 AND dsPIC33EPXXXGP/MC204/504 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      |        | —      | _      | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 03FF          |

| PORTC        | 0E22  | _      | _      | -      | _      | _      | —      | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx          |

| LATC         | 0E24  | —      | —      | _      | _      |        | —      | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  | —      | —      | _      | _      |        | —      | ODCC9  | ODCC8  | ODCC7  | ODCC6  | ODCC5  | ODCC4  | ODCC3  | ODCC2  | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | —      | —      | _      | _      |        | —      | CNIEC9 | CNIEC8 | CNIEC7 | CNIEC6 | CNIEC5 | CNIEC4 | CNIEC3 | CNIEC2 | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  | —      | —      | _      | _      |        | —      | CNPUC9 | CNPUC8 | CNPUC7 | CNPUC6 | CNPUC5 | CNPUC4 | CNPUC3 | CNPUC2 | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  | —      | —      | _      | _      |        | —      | CNPDC9 | CNPDC8 | CNPDC7 | CNPDC6 | CNPDC5 | CNPDC4 | CNPDC3 | CNPDC2 | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | —      | —      | _      | _      |        | —      | _      |        |        |        | —      |        | _      | ANSC2  | ANSC1  | ANSC0  | 0007          |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0         | R/W-0                                  | U-0                                    | U-0           | R/W-0                 | U-0               | R/W-0            | R/W-0         |

|---------------|----------------------------------------|----------------------------------------|---------------|-----------------------|-------------------|------------------|---------------|

| TRAPF         | R IOPUWR                               | —                                      | _             | VREGSF                | —                 | CM               | VREGS         |

| bit 15        |                                        |                                        |               |                       |                   |                  | bit 8         |

|               |                                        | DANIO                                  | DAMO          | DAMA                  | DAMO              |                  |               |

| R/W-0         |                                        | R/W-0                                  | R/W-0         | R/W-0                 | R/W-0             | R/W-1            | R/W-1         |

| EXTR<br>bit 7 | SWR                                    | SWDTEN <sup>(2)</sup>                  | WDTO          | SLEEP                 | IDLE              | BOR              | POR           |

|               |                                        |                                        |               |                       |                   |                  | bit (         |

| Legend:       |                                        |                                        |               |                       |                   |                  |               |

| R = Reada     | able bit                               | W = Writable I                         | oit           | U = Unimpler          | mented bit, read  | d as '0'         |               |

| -n = Value    | at POR                                 | '1' = Bit is set                       |               | '0' = Bit is cle      | ared              | x = Bit is unkı  | nown          |

|               |                                        |                                        |               |                       |                   |                  |               |

| bit 15        | •                                      | Reset Flag bit                         |               |                       |                   |                  |               |

|               |                                        | onflict Reset ha<br>onflict Reset ha   |               | d                     |                   |                  |               |

| bit 14        | •                                      | gal Opcode or                          |               |                       | et Flag bit       |                  |               |

|               |                                        | I opcode detec                         |               |                       | •                 | lized W registe  | er used as ar |

|               |                                        | Pointer caused                         |               |                       |                   |                  |               |

|               | -                                      | l opcode or Uni                        |               | egister Reset h       | as not occurred   | d                |               |

| bit 13-12     | -                                      | ted: Read as '                         |               |                       | . 1.9             |                  |               |

| bit 11        |                                        | ash Voltage Reg<br>Itage regulator i   |               |                       | p bit             |                  |               |

|               |                                        | ltage regulator (                      |               | •                     | ing Sleep         |                  |               |

| bit 10        |                                        | ted: Read as '                         | -             | ,,                    | 5                 |                  |               |

| bit 9         | CM: Configur                           | ation Mismatch                         | Flag bit      |                       |                   |                  |               |

|               | 1 = A Configu                          | uration Mismatc<br>uration Mismatc     | h Reset has   |                       |                   |                  |               |

| bit 8         | VREGS: Volta                           | age Regulator S                        | Standby Durir | ng Sleep bit          |                   |                  |               |

|               | •                                      | egulator is active<br>egulator goes in | •             | •                     | еер               |                  |               |

| bit 7         | EXTR: Extern                           | nal Reset (MCL                         | R) Pin bit    |                       |                   |                  |               |

|               |                                        | Clear (pin) Res<br>Clear (pin) Res     |               |                       |                   |                  |               |

| bit 6         | SWR: Softwa                            | re RESET (Instr                        | uction) Flag  | bit                   |                   |                  |               |

|               |                                        | instruction has instruction has        |               |                       |                   |                  |               |

| bit 5         | SWDTEN: So                             | oftware Enable/                        | Disable of W  | DT bit <sup>(2)</sup> |                   |                  |               |

|               | 1 = WDT is e<br>0 = WDT is di          |                                        |               |                       |                   |                  |               |

| bit 4         | WDTO: Watc                             | hdog Timer Tim                         | e-out Flag bi | it                    |                   |                  |               |

|               |                                        | e-out has occur<br>e-out has not oc    |               |                       |                   |                  |               |

| Note 1:       | All of the Reset sta cause a device Re |                                        | set or cleare | d in software. S      | Setting one of th | ese bits in soft | ware does not |

| 2:            | If the FWDTEN Co<br>SWDTEN bit settir  | onfiguration bit i                     | s '1' (unprog | rammed), the V        | VDT is always e   | enabled, regard  | lless of the  |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

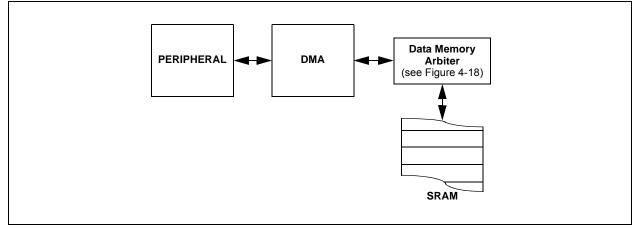

# 8.0 DIRECT MEMORY ACCESS (DMA)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The DMA Controller transfers data between Peripheral Data registers and Data Space SRAM

In addition, DMA can access the entire data memory space. The Data Memory Bus Arbiter is utilized when either the CPU or DMA attempts to access SRAM, resulting in potential DMA or CPU stalls.

The DMA Controller supports 4 independent channels. Each channel can be configured for transfers to or from selected peripherals. Some of the peripherals supported by the DMA Controller include:

- ECAN<sup>™</sup>

- Analog-to-Digital Converter (ADC)

- Serial Peripheral Interface (SPI)

- UART

- Input Capture

- Output Compare

Refer to Table 8-1 for a complete list of supported peripherals.

# FIGURE 8-1: DMA CONTROLLER MODULE

# **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 4 Unimplemented: Read as '0'

- bit 3 **CF:** Clock Fail Detect bit<sup>(3)</sup>

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **"Oscillator"** (DS70580) in the *"dsPIC33/ PIC24 Family Reference Manual"* (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

## REGISTER 11-17: RPINR39: PERIPHERAL PIN SELECT INPUT REGISTER 39 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|------------------|----------------------------------------------------------|-------|-------------------|-----------------|-----------------|-------|

|              |                  |                                                          |       | DTCMP3R<6:0       | )>              |                 |       |

| bit 15       |                  |                                                          |       |                   |                 |                 | bit 8 |

| U-0          | R/W-0            | R/W-0                                                    | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| 0-0          | R/W-0            | R/W-0                                                    | -     | DTCMP2R<6:0       |                 | R/W-0           | R/W-U |

| bit 7        |                  |                                                          |       |                   | 17              |                 | bit 0 |

| bit i        |                  |                                                          |       |                   |                 |                 | bit 0 |

| Legend:      |                  |                                                          |       |                   |                 |                 |       |

| R = Readab   | ole bit          | W = Writable                                             | bit   | U = Unimplem      | nented bit, rea | ad as '0'       |       |

| -n = Value a | at POR           | '1' = Bit is set                                         |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              |                  |                                                          |       |                   |                 |                 |       |

|              |                  | nput tied to CMI                                         |       |                   |                 |                 |       |

| bit 7        | 1 = 0000000 = Ir | nput tied to CMI<br>nput tied to Vss<br>nted: Read as '( |       |                   |                 |                 |       |

# 17.0 QUADRATURE ENCODER INTERFACE (QEI) MODULE (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Quadrature Encoder Interface (QEI)" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter describes the Quadrature Encoder Interface (QEI) module and associated operational modes. The QEI module provides the interface to incremental encoders for obtaining mechanical position data.

The operational features of the QEI module include:

- 32-Bit Position Counter

- 32-Bit Index Pulse Counter

- 32-Bit Interval Timer

- 16-Bit Velocity Counter

- 32-Bit Position Initialization/Capture/Compare High register

- 32-Bit Position Compare Low register

- x4 Quadrature Count mode

- External Up/Down Count mode

- External Gated Count mode

- External Gated Timer mode

- Internal Timer mode

Figure 17-1 illustrates the QEI block diagram.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 17-17: INT1TMRH: INTERVAL 1 TIMER HIGH WORD REGISTER

| R/W-0           | R/W-0                                                                | R/W-0            | R/W-0 | R/W-0             | R/W-0 | R/W-0           | R/W-0 |  |  |  |  |

|-----------------|----------------------------------------------------------------------|------------------|-------|-------------------|-------|-----------------|-------|--|--|--|--|

|                 |                                                                      |                  | INTTM | R<31:24>          |       |                 |       |  |  |  |  |

| bit 15          |                                                                      |                  |       |                   |       |                 | bit 8 |  |  |  |  |

|                 |                                                                      |                  |       |                   |       |                 |       |  |  |  |  |

| R/W-0           | R/W-0                                                                | R/W-0            | R/W-0 | R/W-0             | R/W-0 | R/W-0           | R/W-0 |  |  |  |  |

|                 |                                                                      |                  | INTTM | R<23:16>          |       |                 |       |  |  |  |  |

| bit 7           |                                                                      |                  |       |                   |       |                 | bit 0 |  |  |  |  |

|                 |                                                                      |                  |       |                   |       |                 |       |  |  |  |  |

| Legend:         |                                                                      |                  |       |                   |       |                 |       |  |  |  |  |

| R = Readable    | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |       |                   |       |                 |       |  |  |  |  |

| -n = Value at P | OR                                                                   | '1' = Bit is set |       | '0' = Bit is clea | ared  | x = Bit is unkr | nown  |  |  |  |  |

bit 15-0 INTTMR<31:16>: High Word Used to Form 32-Bit Interval Timer Register (INT1TMR) bits

## REGISTER 17-18: INT1TMRL: INTERVAL 1 TIMER LOW WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | INTTM | IR<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INTT  | /IR<7:0>         |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable I  | bit   | W = Writable b   | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 INTTMR<15:0>: Low Word Used to Form 32-Bit Interval Timer Register (INT1TMR) bits

#### REGISTER 18-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

- 1 = Transmit not yet started, SPIxTXB is full

- 0 = Transmit started, SPIxTXB is empty

#### Standard Buffer mode:

Automatically set in hardware when core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.

## Enhanced Buffer mode:

Automatically set in hardware when the CPU writes to the SPIxBUF location, loading the last available buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write operation.

#### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive is complete, SPIxRXB is full

0 = Receive is incomplete, SPIxRXB is empty

#### Standard Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when the core reads the SPIxBUF location, reading SPIxRXB.

#### Enhanced Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to the buffer, filling the last unread buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from SPIxSR.

## REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Receiver is active                                                                                                                                                                                                           |

| bit 3 | <b>PERR:</b> Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character (character at the top of the receive FIFO) 0 = Parity error has not been detected                                                                                                  |

| bit 2 | <pre>FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character (character at the top of the receive FIFO) 0 = Framing error has not been detected</pre>                                                                                           |

| bit 1 | <ul> <li>OERR: Receive Buffer Overrun Error Status bit (clear/read-only)</li> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | <ul> <li>URXDA: UARTx Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                |

**Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0         | R/W-0                        | R/W-0                                                                                                                      | R/W-0                                          | R/W-0                                   | R/W-0          | R/W-0  | R/W-0  |  |  |

|---------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------|----------------|--------|--------|--|--|

|               | F15B                         | P<3:0>                                                                                                                     |                                                |                                         | F14BI          | P<3:0> |        |  |  |

| bit 15        |                              |                                                                                                                            |                                                |                                         |                |        | bit 8  |  |  |

| R/W-0         | R/W-0                        | R/W-0                                                                                                                      | R/W-0                                          | R/W-0                                   | R/W-0          | R/W-0  | R/W-0  |  |  |

| 1010 0        |                              | P<3:0>                                                                                                                     | 10110                                          |                                         |                | P<3:0> | 1010 0 |  |  |

| bit 7         |                              |                                                                                                                            |                                                |                                         |                |        | bit 0  |  |  |

| Legend:       |                              |                                                                                                                            |                                                |                                         |                |        |        |  |  |

| R = Readabl   | e bit                        | W = Writable                                                                                                               | bit                                            | U = Unimplemented bit, read as '0'      |                |        |        |  |  |

| -n = Value at | t POR                        | '1' = Bit is set                                                                                                           |                                                | '0' = Bit is cleared x = Bit is unknown |                |        |        |  |  |

| bit 15-12     | 1111 = Filte<br>1110 = Filte | RX Buffer Ma<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | differ<br>4                             |                |        |        |  |  |

| bit 11-8      | F14BP<3:0;                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 4 bits (same val                        | ues as bits<15 | :12>)  |        |  |  |

| bit 7-4       | F13BP<3:0;                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 3 bits (same val                        | ues as bits<15 | :12>)  |        |  |  |

| bit 3-0       | F12BP<3:0:                   | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 2 bits (same val                        | ues as bits<15 | :12>)  |        |  |  |

# REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

# 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0           | U-0                               | U-0               | R/W-x         | R/W-x                                   | R/W-x            | R/W-x    | R/W-x |  |  |

|---------------|-----------------------------------|-------------------|---------------|-----------------------------------------|------------------|----------|-------|--|--|

|               | —                                 | _                 | SID10         | SID9                                    | SID8             | SID7     | SID6  |  |  |

| bit 15        |                                   |                   |               |                                         |                  |          | bit 8 |  |  |

| R/W-x         | R/W-x                             | R/W-x             | R/W-x         | R/W-x                                   | R/W-x            | R/W-x    | R/W-x |  |  |

| SID5          | SID4                              | SID3              | SID2          | SID1                                    | SID0             | SRR      | IDE   |  |  |

| bit 7         |                                   |                   |               |                                         |                  |          | bit 0 |  |  |

| Legend:       |                                   |                   |               |                                         |                  |          |       |  |  |

| R = Readabl   | e bit                             | W = Writable      | bit           | U = Unimpler                            | mented bit, read | l as '0' |       |  |  |

| -n = Value at | n = Value at POR '1' = Bit is set |                   |               | '0' = Bit is cleared x = Bit is unknown |                  |          |       |  |  |

|               |                                   |                   |               |                                         |                  |          |       |  |  |

| bit 15-13     | Unimplemen                        | ted: Read as '    | כי            |                                         |                  |          |       |  |  |

| bit 12-2      | <b>SID&lt;10:0&gt;:</b> S         | Standard Identifi | ier bits      |                                         |                  |          |       |  |  |

| bit 1         | SRR: Substitu                     | ute Remote Re     | quest bit     |                                         |                  |          |       |  |  |

|               | When IDE =                        | 0:                |               |                                         |                  |          |       |  |  |

|               | 1 = Message                       | will request rer  | note transmis | ssion                                   |                  |          |       |  |  |

|               | 0 = Normal m                      | nessage           |               |                                         |                  |          |       |  |  |

|               | When IDE = 1                      | <u>1:</u>         |               |                                         |                  |          |       |  |  |

|               | The SRR bit r                     | must be set to '  | 1'.           |                                         |                  |          |       |  |  |

| bit 0         | IDE: Extende                      | d Identifier bit  |               |                                         |                  |          |       |  |  |

|               | 1 = Message                       | will transmit Ex  | tended Ident  | ifier                                   |                  |          |       |  |  |

|               | 0 = Message                       | will transmit St  | andard Identi | fier                                    |                  |          |       |  |  |

|               |                                   |                   |               |                                         |                  |          |       |  |  |

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0             | U-0   | U-0              | U-0   | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |  |

|-----------------|-------|------------------|-------|-----------------------------------------|-------|-------|-------|--|--|

| —               | —     | —                |       | EID17                                   | EID16 | EID15 | EID14 |  |  |

| bit 15          |       |                  |       |                                         |       |       | bit 8 |  |  |

|                 |       |                  |       |                                         |       |       |       |  |  |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |  |

| EID13           | EID12 | EID11            | EID10 | EID9                                    | EID8  | EID7  | EID6  |  |  |

| bit 7           |       |                  |       |                                         |       |       | bit 0 |  |  |

|                 |       |                  |       |                                         |       |       |       |  |  |

| Legend:         |       |                  |       |                                         |       |       |       |  |  |

| R = Readable    | bit   | W = Writable I   | bit   | U = Unimplemented bit, read as '0'      |       |       |       |  |  |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |  |

| L               |       |                  |       |                                         |       |       |       |  |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

# 22.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual", which is available on the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Charge Time Measurement Unit is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. Its key features include:

- Four Edge Input Trigger Sources

- Polarity Control for Each Edge Source

- Control of Edge Sequence

- Control of Response to Edges

- · Precise Time Measurement Resolution of 1 ns

- Accurate Current Source Suitable for Capacitive Measurement

- On-Chip Temperature Measurement using a Built-in Diode

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock.

The CTMU module is ideal for interfacing with capacitive-based sensors. The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 and CTMUCON2 enable the module and control edge source selection, edge source polarity selection and edge sequencing. The CTMUICON register controls the selection and trim of the current source.

| Base<br>Instr<br># | Assembly<br>Mnemonic |         |                             |                                                 |   | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |  |

|--------------------|----------------------|---------|-----------------------------|-------------------------------------------------|---|-------------------------------|--------------------------|--|

| 52                 | MUL                  | MUL.SS  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = signed(Wb) *<br>signed(Ws)     | 1 | 1                             | None                     |  |

|                    |                      | MUL.SS  | Wb,Ws,Acc <sup>(1)</sup>    | Accumulator = signed(Wb) * signed(Ws)           | 1 | 1                             | None                     |  |

|                    |                      | MUL.SU  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(Ws)   | 1 | 1                             | None                     |  |

|                    |                      | MUL.SU  | Wb,Ws,Acc <sup>(1)</sup>    | Accumulator = signed(Wb) *<br>unsigned(Ws)      | 1 | 1                             | None                     |  |

|                    |                      | MUL.SU  | Wb,#lit5,Acc <sup>(1)</sup> | Accumulator = signed(Wb) *<br>unsigned(lit5)    | 1 | 1                             | None                     |  |

|                    |                      | MUL.US  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)      | 1 | 1                             | None                     |  |

|                    |                      | MUL.US  | Wb,Ws,Acc <sup>(1)</sup>    | Accumulator = unsigned(Wb) *<br>signed(Ws)      | 1 | 1                             | None                     |  |

|                    |                      | MUL.UU  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws) | 1 | 1                             | None                     |  |

|                    |                      | MUL.UU  | Wb,#lit5,Acc <sup>(1)</sup> | Accumulator = unsigned(Wb) *<br>unsigned(lit5)  | 1 | 1                             | None                     |  |

|                    |                      | MUL.UU  | Wb,Ws,Acc <sup>(1)</sup>    | Accumulator = unsigned(Wb) *<br>unsigned(Ws)    | 1 | 1                             | None                     |  |

|                    |                      | MULW.SS | Wb,Ws,Wnd                   | Wnd = signed(Wb) * signed(Ws)                   | 1 | 1                             | None                     |  |

|                    |                      | MULW.SU | Wb,Ws,Wnd                   | Wnd = signed(Wb) * unsigned(Ws)                 | 1 | 1                             | None                     |  |

|                    |                      | MULW.US | Wb,Ws,Wnd                   | Wnd = unsigned(Wb) * signed(Ws)                 | 1 | 1                             | None                     |  |

|                    |                      | MULW.UU | Wb,Ws,Wnd                   | Wnd = unsigned(Wb) * unsigned(Ws)               | 1 | 1                             | None                     |  |

|                    |                      | MUL.SU  | Wb,#lit5,Wnd                | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(lit5) | 1 | 1                             | None                     |  |

|                    |                      | MUL.SU  | Wb,#lit5,Wnd                | Wnd = signed(Wb) * unsigned(lit5)               | 1 | 1                             | None                     |  |

|                    |                      | MUL.UU  | Wb,#lit5,Wnd                | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(lit5)  | 1 | 1                             | None                     |  |

|                    |                      | MUL.UU  | Wb,#lit5,Wnd                | Wnd = unsigned(Wb) * unsigned(lit5)             | 1 | 1                             | None                     |  |

|                    |                      | MUL     | f                           | W3:W2 = f * WREG                                | 1 | 1                             | None                     |  |

### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| DC CHARACTER  | ISTICS |      | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |        |       |  |  |  |

|---------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--|--|--|

| Parameter No. | Тур.   | Max. | Units                                                                                                                                                                                                | tions  |       |  |  |  |

| DC61d         | 8      |      | μΑ                                                                                                                                                                                                   | -40°C  | 2.21/ |  |  |  |

| DC61a         | 10     | —    | μA                                                                                                                                                                                                   | +25°C  |       |  |  |  |

| DC61b         | 12     | —    | μA                                                                                                                                                                                                   | +85°C  | 3.3V  |  |  |  |

| DC61c         | 13     | —    | μA                                                                                                                                                                                                   | +125°C |       |  |  |  |

# TABLE 30-9: DC CHARACTERISTICS: WATCHDOG TIMER DELTA CURRENT ( $\Delta$ Iwdt)<sup>(1)</sup>

**Note 1:** The  $\triangle$ IwDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

#### TABLE 30-10: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTER                        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |       |            |    |        |      |                 |  |  |

|-------------------------------------|-------------------------------------------------------|-------|------------|----|--------|------|-----------------|--|--|

| Parameter No.                       | Doze<br>Ratio                                         | Units | Conditions |    |        |      |                 |  |  |

| Doze Current (IDOZE) <sup>(1)</sup> |                                                       |       |            |    |        |      |                 |  |  |

| DC73a <sup>(2)</sup>                | 35                                                    |       | 1:2        | mA | -40°C  | 3.3V | Fosc = 140 MHz  |  |  |

| DC73g                               | 20                                                    | 30    | 1:128      | mA | -40 C  |      |                 |  |  |

| DC70a <sup>(2)</sup>                | 35                                                    | _     | 1:2        | mA | +25°C  | 3.3V | Fosc = 140 MHz  |  |  |

| DC70g                               | 20                                                    | 30    | 1:128      | mA | +25 C  |      |                 |  |  |

| DC71a <sup>(2)</sup>                | 35                                                    | —     | 1:2        | mA | 195%   | 3.3V | Fosc = 140 MHz  |  |  |

| DC71g                               | 20                                                    | 30    | 1:128      | mA | +85°C  |      |                 |  |  |

| DC72a <sup>(2)</sup>                | 28                                                    | —     | 1:2        | mA | +125°C | 3.3V | Fosc = 120 MHz  |  |  |

| DC72g                               | 15                                                    | 30    | 1:128      | mA | +125 C |      | FUSC - 120 MITZ |  |  |

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) statement

- · JTAG is disabled

- 2: Parameter is characterized but not tested in manufacturing.

| DC CHARACTERISTICS |                       |                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                                                                                                                                               |  |  |

|--------------------|-----------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol Characteristic |                                         | Min.                                                                                                                                                                                                                                                                                  | Тур. | Max. | Units | Conditions                                                                                                                                    |  |  |

|                    | liL                   | Input Leakage Current <sup>(1,2)</sup>  |                                                                                                                                                                                                                                                                                       |      |      |       |                                                                                                                                               |  |  |

| DI50               |                       | I/O Pins 5V Tolerant <sup>(3)</sup>     | -1                                                                                                                                                                                                                                                                                    | —    | +1   | μA    | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in at high-impedance} \end{split}$                         |  |  |

| DI51               |                       | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                                                                                                                                                                                                                                                    | _    | +1   | μA    | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ Pin \text{ at high-impedance}, \\ -40^\circC \leq TA \leq +85^\circC \end{array}$ |  |  |

| DI51a              |                       | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                                                                                                                                                                                                                                                    | _    | +1   | μA    | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +85^{\circ}C$                                                 |  |  |

| DI51b              |                       | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                                                                                                                                                                                                                                                    | _    | +1   | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance,<br>-40°C ≤ TA ≤ +125°C                                                                      |  |  |

| DI51c              |                       | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                                                                                                                                                                                                                                                    | _    | +1   | μA    | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +125^{\circ}C$                                                |  |  |

| DI55               |                       | MCLR                                    | -5                                                                                                                                                                                                                                                                                    | —    | +5   | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                      |  |  |

| DI56               |                       | OSC1                                    | -5                                                                                                                                                                                                                                                                                    | —    | +5   | μΑ    | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ XT \text{ and } HS \text{ modes} \end{array}$                                     |  |  |

## TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- **5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

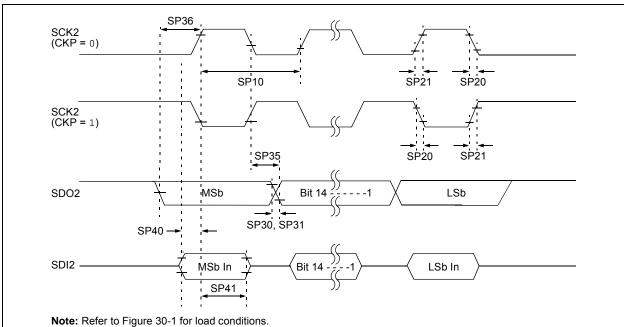

## FIGURE 30-16: SPI2 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

# TABLE 30-35:SPI2 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1)TIMING REQUIREMENTS

| АС СНА | RACTERIST             | $\label{eq:standard operating Conditions: 3.0V to 3.6V \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \\  \end{aligned}$ |                               |   |    |       |                             |

|--------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---|----|-------|-----------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                 | Min. Typ. <sup>(2)</sup> Max. |   |    | Units | Conditions                  |

| SP10   | FscP                  | Maximum SCK2 Frequency                                                                                                                                                                                                                                                        | _                             | — | 9  | MHz   | (Note 3)                    |

| SP20   | TscF                  | SCK2 Output Fall Time                                                                                                                                                                                                                                                         | —                             | — |    | ns    | See Parameter DO32 (Note 4) |

| SP21   | TscR                  | SCK2 Output Rise Time                                                                                                                                                                                                                                                         | —                             | — | —  | ns    | See Parameter DO31 (Note 4) |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                                                                                                                                                                                                                                                    | —                             | — | —  | ns    | See Parameter DO32 (Note 4) |

| SP31   | TdoR                  | SDO2 Data Output Rise Time                                                                                                                                                                                                                                                    | —                             | — | _  | ns    | See Parameter DO31 (Note 4) |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after SCK2 Edge                                                                                                                                                                                                                                        | —                             | 6 | 20 | ns    |                             |

| SP36   | TdoV2sc,<br>TdoV2scL  | SDO2 Data Output Setup to<br>First SCK2 Edge                                                                                                                                                                                                                                  | 30                            |   | —  | ns    |                             |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data<br>Input to SCK2 Edge                                                                                                                                                                                                                                 | 30                            | — |    | ns    |                             |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge                                                                                                                                                                                                                                     | 30                            |   | _  | ns    |                             |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 111 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPI2 pins.

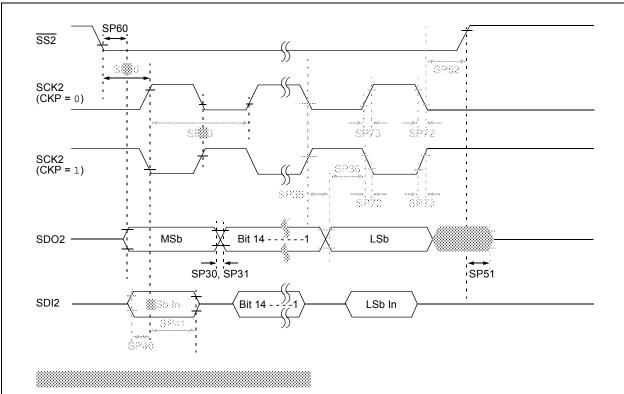

## FIGURE 30-18: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

NOTES: