Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc206-e-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

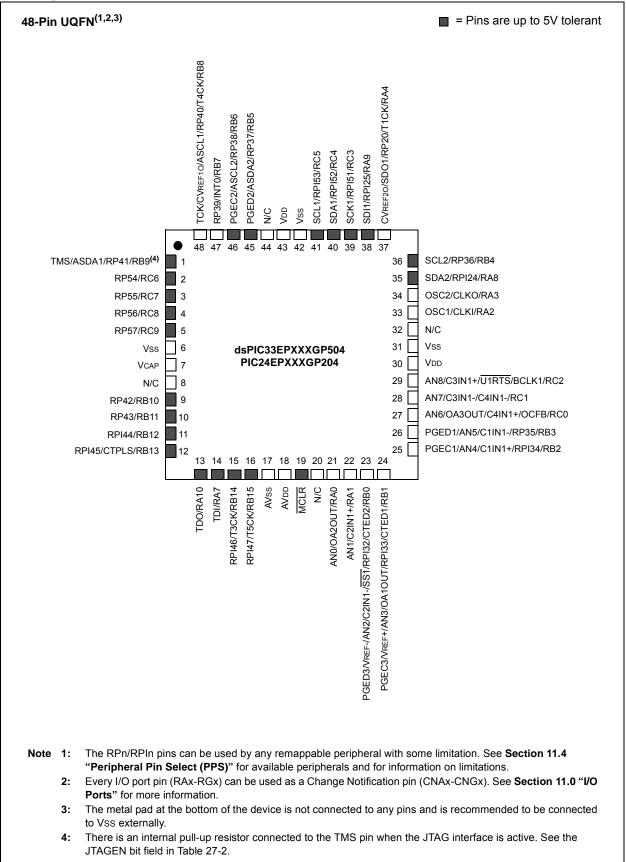

## Pin Diagrams (Continued)

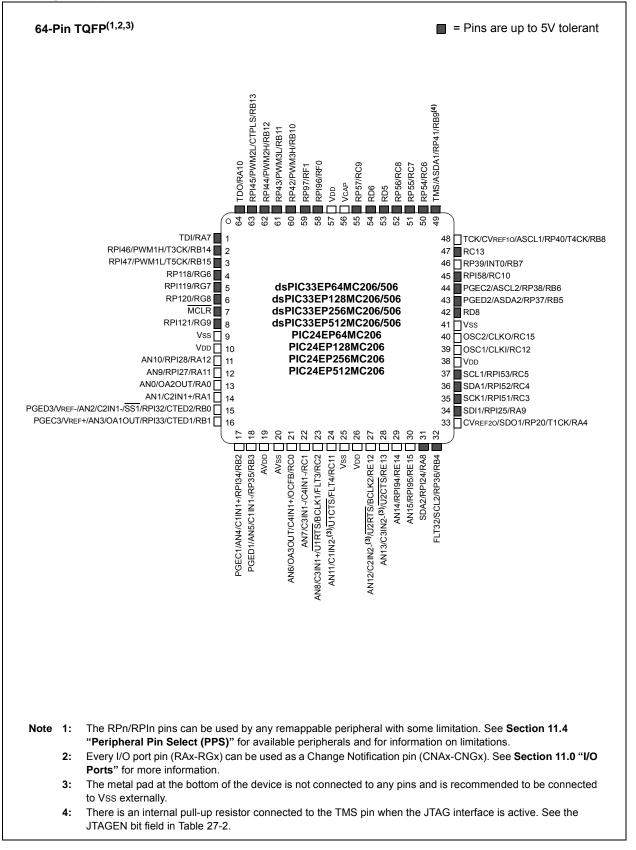

## Pin Diagrams (Continued)

## TABLE 4-59: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | —      | _      | _      | _      | -      | _     | _     | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | _      | _     | _     | _     | _     | _     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-60: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | _       | _      | ANSB8  | _      |        | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 4.4.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating of the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack               |

|-------|---------------------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the hardware. |

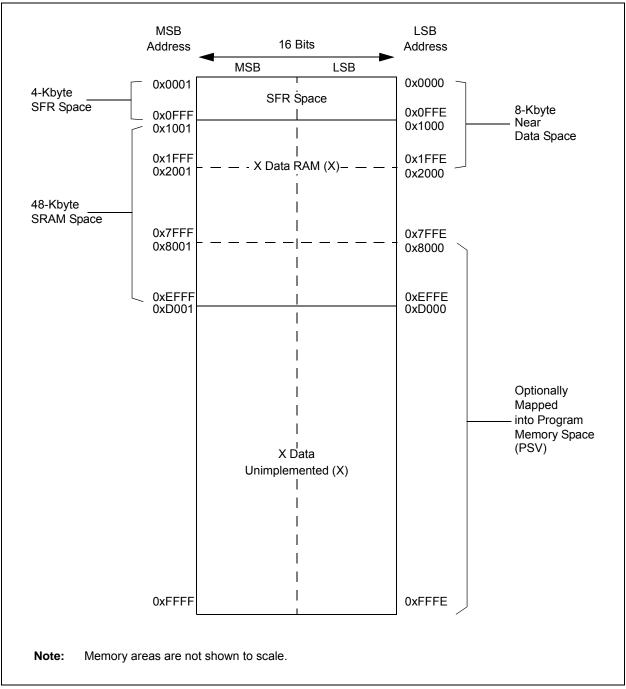

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

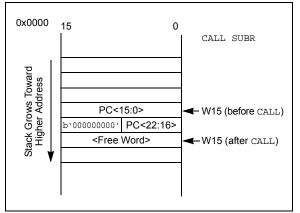

The Software Stack Pointer always points to the first available free word and fills the software stack working from lower toward higher addresses. Figure 4-19 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-19. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain system Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a C development environment

FIGURE 4-19: CALL STACK FRAME

## 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Interrupts" (DS70600) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X CPU.

The interrupt controller has the following features:

- Up to eight processor exceptions and software traps

- Eight user-selectable priority levels

- Interrupt Vector Table (IVT) with a unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Interrupt Vector Table (IVT), shown in Figure 7-1, resides in program memory starting at location, 000004h. The IVT contains seven non-maskable trap vectors and up to 246 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit-wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority. This priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with Vector 0 takes priority over interrupts at any other vector address.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices clear their registers in response to a Reset, which forces the PC to zero. The device then begins program execution at location, 0x000000. A GOTO instruction at the Reset address can redirect program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

|                                                     | Vector  | IRQ        |                   | Inte     | errupt Bit L | ocation      |

|-----------------------------------------------------|---------|------------|-------------------|----------|--------------|--------------|

| Interrupt Source                                    | #       | #          | IVT Address       | Flag     | Enable       | Priority     |

| QEI1 – QEI1 Position Counter Compare <sup>(2)</sup> | 66      | 58         | 0x000088          | IFS3<10> | IEC3<10>     | IPC14<10:8>  |

| Reserved                                            | 67-72   | 59-64      | 0x00008A-0x000094 | _        | _            | _            |

| U1E – UART1 Error Interrupt                         | 73      | 65         | 0x000096          | IFS4<1>  | IEC4<1>      | IPC16<6:4>   |

| U2E – UART2 Error Interrupt                         | 74      | 66         | 0x000098          | IFS4<2>  | IEC4<2>      | IPC16<10:8>  |

| CRC – CRC Generator Interrupt                       | 75      | 67         | 0x00009A          | IFS4<3>  | IEC4<3>      | IPC16<14:12> |

| Reserved                                            | 76-77   | 68-69      | 0x00009C-0x00009E | —        | _            | —            |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>          | 78      | 70         | 0x000A0           | IFS4<6>  | IEC4<6>      | IPC17<10:8>  |

| Reserved                                            | 79-84   | 71-76      | 0x0000A2-0x0000AC | —        | _            | —            |

| CTMU – CTMU Interrupt                               | 85      | 77         | 0x0000AE          | IFS4<13> | IEC4<13>     | IPC19<6:4>   |

| Reserved                                            | 86-101  | 78-93      | 0x0000B0-0x0000CE | —        | _            | —            |

| PWM1 – PWM Generator 1 <sup>(2)</sup>               | 102     | 94         | 0x0000D0          | IFS5<14> | IEC5<14>     | IPC23<10:8>  |

| PWM2 – PWM Generator 2 <sup>(2)</sup>               | 103     | 95         | 0x0000D2          | IFS5<15> | IEC5<15>     | IPC23<14:12> |

| PWM3 – PWM Generator 3 <sup>(2)</sup>               | 104     | 96         | 0x0000D4          | IFS6<0>  | IEC6<0>      | IPC24<2:0>   |

| Reserved                                            | 105-149 | 97-141     | 0x0001D6-0x00012E | —        | _            | —            |

| ICD – ICD Application                               | 150     | 142        | 0x000142          | IFS8<14> | IEC8<14>     | IPC35<10:8>  |

| JTAG – JTAG Programming                             | 151     | 143        | 0x000130          | IFS8<15> | IEC8<15>     | IPC35<14:12> |

| Reserved                                            | 152     | 144        | 0x000134          | —        | _            | _            |

| PTGSTEP – PTG Step                                  | 153     | 145        | 0x000136          | IFS9<1>  | IEC9<1>      | IPC36<6:4>   |

| PTGWDT – PTG Watchdog Time-out                      | 154     | 146        | 0x000138          | IFS9<2>  | IEC9<2>      | IPC36<10:8>  |

| PTG0 – PTG Interrupt 0                              | 155     | 147        | 0x00013A          | IFS9<3>  | IEC9<3>      | IPC36<14:12> |

| PTG1 – PTG Interrupt 1                              | 156     | 148        | 0x00013C          | IFS9<4>  | IEC9<4>      | IPC37<2:0>   |

| PTG2 – PTG Interrupt 2                              | 157     | 149        | 0x00013E          | IFS9<5>  | IEC9<5>      | IPC37<6:4>   |

| PTG3 – PTG Interrupt 3                              | 158     | 150        | 0x000140          | IFS9<6>  | IEC9<6>      | IPC37<10:8>  |

| Reserved                                            | 159-245 | 151-245    | 0x000142-0x0001FE | —        | —            | _            |

|                                                     | Lowe    | est Natura | I Order Priority  |          |              |              |

## TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

NOTES:

## REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| bit 6         | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with the SCLREL bit.<br>1 = Enables software or receives clock stretching<br>0 = Disables software or receives clock stretching |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5         | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                                     |

|               | Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                                                                                       |

| bit 4         | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master, applicable during master receive)                                                                                                                   |

|               | <ul> <li>1 = Initiates Acknowledge sequence on SDAx and SCLx pins and transmits ACKDT data bit. Hardware is clear at the end of the master Acknowledge sequence.</li> <li>0 = Acknowledge sequence is not in progress</li> </ul>              |

| bit 3         | <b>RCEN:</b> Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                                   |

|               | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware is clear at the end of the eighth bit of the master receive data byte.</li> <li>0 = Receive sequence is not in progress</li> </ul>                                             |

| bit 2         | <b>PEN:</b> Stop Condition Enable bit (when operating as $I^2C$ master)                                                                                                                                                                       |

| 511 2         | 1 = Initiates Stop condition on SDAx and SCLx pins. Hardware is clear at the end of the master Stop sequence.                                                                                                                                 |

| <b>h</b> :+ 4 | 0 = Stop condition is not in progress                                                                                                                                                                                                         |

| bit 1         | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                                                                  |

|               | <ul> <li>1 = Initiates Repeated Start condition on SDAx and SCLx pins. Hardware is clear at the end of the<br/>master Repeated Start sequence.</li> <li>0 = Repeated Start condition is not in progress</li> </ul>                            |

| bit 0         | <b>SEN:</b> Start Condition Enable bit (when operating as $l^2C$ master)                                                                                                                                                                      |

|               | <ul> <li>1 = Initiates Start condition on SDAx and SCLx pins. Hardware is clear at the end of the master Start sequence.</li> <li>0 = Start condition is not in progress</li> </ul>                                                           |

**Note 1:** When performing master operations, ensure that the IPMIEN bit is set to '0'.

## REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Receiver is active                                                                                                                                                                                                           |

| bit 3 | <b>PERR:</b> Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character (character at the top of the receive FIFO) 0 = Parity error has not been detected                                                                                                  |

| bit 2 | <pre>FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character (character at the top of the receive FIFO) 0 = Framing error has not been detected</pre>                                                                                           |

| bit 1 | <ul> <li>OERR: Receive Buffer Overrun Error Status bit (clear/read-only)</li> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | <ul> <li>URXDA: UARTx Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                |

**Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 21-26: | CxTRmnCON: ECANx TX/RX BUFFER mn CONTROL REGISTER |

|-----------------|---------------------------------------------------|

|                 | (m = 0,2,4,6; n = 1,3,5,7)                        |

|               | <b>`</b>                                                                                                                                                |                                    |                       |                  |                  |                 |                 |  |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|------------------|------------------|-----------------|-----------------|--|--|--|--|--|--|

| R/W-0         | R-0                                                                                                                                                     | R-0                                | R-0                   | R/W-0            | R/W-0            | R/W-0           | R/W-0           |  |  |  |  |  |  |

| TXENn         | TXABTn                                                                                                                                                  | TXLARBn                            | TXERRn                | TXREQn           | RTRENn           | TXnPRI1         | TXnPRI0         |  |  |  |  |  |  |

| bit 15        |                                                                                                                                                         |                                    |                       |                  |                  |                 | bit 8           |  |  |  |  |  |  |

| R/W-0         | R-0                                                                                                                                                     | R-0                                | R-0                   | R/W-0            | R/W-0            | R/W-0           | R/W-0           |  |  |  |  |  |  |

| TXENm         | TXABTm <sup>(1)</sup>                                                                                                                                   | TXLARBm <sup>(1)</sup>             | TXERRm <sup>(1)</sup> | TXREQm           | RTRENm           | TXmPRI1         | TXmPRI0         |  |  |  |  |  |  |

| bit 7         |                                                                                                                                                         | 1                                  | 1                     |                  |                  |                 | bit (           |  |  |  |  |  |  |

| Legend:       |                                                                                                                                                         |                                    |                       |                  |                  |                 |                 |  |  |  |  |  |  |

| R = Readable  | e bit                                                                                                                                                   | W = Writable                       | bit                   | U = Unimpler     | mented bit, read | d as '0'        |                 |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                                                                     | '1' = Bit is set                   |                       | '0' = Bit is cle | ared             | x = Bit is unkr | nown            |  |  |  |  |  |  |

| bit 15-8      | See Dofinition                                                                                                                                          | n for bits<7:0>,                   | Controls Ruffs        | ar n             |                  |                 |                 |  |  |  |  |  |  |

| bit 7         |                                                                                                                                                         | ,                                  |                       |                  |                  |                 |                 |  |  |  |  |  |  |

|               |                                                                                                                                                         | TXENm: TX/RX Buffer Selection bit  |                       |                  |                  |                 |                 |  |  |  |  |  |  |

|               | 1 = Buffer TRBn is a transmit buffer<br>0 = Buffer TRBn is a receive buffer                                                                             |                                    |                       |                  |                  |                 |                 |  |  |  |  |  |  |

| bit 6         | TXABTm: Message Aborted bit <sup>(1)</sup>                                                                                                              |                                    |                       |                  |                  |                 |                 |  |  |  |  |  |  |

|               | 1 = Message was aborted                                                                                                                                 |                                    |                       |                  |                  |                 |                 |  |  |  |  |  |  |

|               | •                                                                                                                                                       | completed trar                     | nsmission succ        | essfully         |                  |                 |                 |  |  |  |  |  |  |

| bit 5         | TXLARBm: Message Lost Arbitration bit <sup>(1)</sup>                                                                                                    |                                    |                       |                  |                  |                 |                 |  |  |  |  |  |  |

|               | 1 = Message lost arbitration while being sent                                                                                                           |                                    |                       |                  |                  |                 |                 |  |  |  |  |  |  |

|               | 0 = Message                                                                                                                                             | did not lose ar                    | bitration while       | being sent       |                  |                 |                 |  |  |  |  |  |  |

| bit 4         | TXERRm: Error Detected During Transmission bit <sup>(1)</sup>                                                                                           |                                    |                       |                  |                  |                 |                 |  |  |  |  |  |  |

|               | 1 = A bus error occurred while the message was being sent                                                                                               |                                    |                       |                  |                  |                 |                 |  |  |  |  |  |  |

|               | 0 = A bus error did not occur while the message was being sent                                                                                          |                                    |                       |                  |                  |                 |                 |  |  |  |  |  |  |

| bit 3         |                                                                                                                                                         | TXREQm: Message Send Request bit   |                       |                  |                  |                 |                 |  |  |  |  |  |  |

|               | sent                                                                                                                                                    |                                    | -                     |                  | -                | n the message   | is successfully |  |  |  |  |  |  |

|               |                                                                                                                                                         | the bit to '0' wh                  | •                     | 0                | abort            |                 |                 |  |  |  |  |  |  |

| bit 2         |                                                                                                                                                         | n: Auto-Remote Transmit Enable bit |                       |                  |                  |                 |                 |  |  |  |  |  |  |

|               | <ul> <li>1 = When a remote transmit is received, TXREQ will be set</li> <li>0 = When a remote transmit is received, TXREQ will be unaffected</li> </ul> |                                    |                       |                  |                  |                 |                 |  |  |  |  |  |  |

| bit 1-0       | TXmPRI<1:0                                                                                                                                              | >: Message Tra                     | ansmission Pri        | ority bits       |                  |                 |                 |  |  |  |  |  |  |

|               |                                                                                                                                                         | message prior                      |                       |                  |                  |                 |                 |  |  |  |  |  |  |

|               |                                                                                                                                                         | ermediate mes                      |                       |                  |                  |                 |                 |  |  |  |  |  |  |

|               |                                                                                                                                                         | ermediate mess<br>message priori   |                       |                  |                  |                 |                 |  |  |  |  |  |  |

|               | 00 – Lowesi                                                                                                                                             | messaye priori                     | ıy                    |                  |                  |                 |                 |  |  |  |  |  |  |

| Note 1: Th    | nis bit is cleared                                                                                                                                      | when TXREQ i                       | s set.                |                  |                  |                 |                 |  |  |  |  |  |  |

|               |                                                                                                                                                         |                                    |                       |                  |                  |                 |                 |  |  |  |  |  |  |

Note: The buffers, SID, EID, DLC, Data Field, and Receive Status registers are located in DMA RAM.

## BUFFER 21-5: ECAN™ MESSAGE BUFFER WORD 4

| R/W-x                                    | R/W-x | R/W-x        | R/W-x | R/W-x                              | R/W-x | R/W-x                                   | R/W-x |  |  |  |

|------------------------------------------|-------|--------------|-------|------------------------------------|-------|-----------------------------------------|-------|--|--|--|

|                                          |       |              | Ву    | /te 3                              |       |                                         |       |  |  |  |

| bit 15                                   |       |              |       |                                    |       |                                         | bit 8 |  |  |  |

|                                          |       |              |       |                                    |       |                                         |       |  |  |  |

| R/W-x                                    | R/W-x | R/W-x        | R/W-x | R/W-x                              | R/W-x | R/W-x                                   | R/W-x |  |  |  |

|                                          |       |              | Ву    | /te 2                              |       |                                         |       |  |  |  |

| bit 7                                    |       |              |       |                                    |       |                                         | bit 0 |  |  |  |

| Legend:                                  |       |              |       |                                    |       |                                         |       |  |  |  |

| R = Readable                             | bit   | W = Writable | bit   | U = Unimplemented bit, read as '0' |       |                                         |       |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = |       |              |       |                                    | ared  | '0' = Bit is cleared x = Bit is unknown |       |  |  |  |

bit 15-8 Byte 3<15:8>: ECAN Message Byte 3 bits

bit 7-0 Byte 2<7:0>: ECAN Message Byte 2 bits

#### BUFFER 21-6: ECAN™ MESSAGE BUFFER WORD 5

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                                  | R/W-x | R/W-x | R/W-x |  |  |  |

|-----------------------------------|-------|------------------|-------|----------------------------------------|-------|-------|-------|--|--|--|

|                                   |       |                  | В     | yte 5                                  |       |       |       |  |  |  |

| bit 15                            |       |                  |       |                                        |       |       | bit 8 |  |  |  |

| R/W-x                             | R/W-x | R/W-x            | R/W-x | R/W-x                                  | R/W-x | R/W-x | R/W-x |  |  |  |

|                                   |       |                  |       | yte 4                                  |       |       |       |  |  |  |

| bit 7                             |       |                  |       | -                                      |       |       | bit 0 |  |  |  |

|                                   |       |                  |       |                                        |       |       |       |  |  |  |

| Legend:                           |       |                  |       |                                        |       |       |       |  |  |  |

| R = Readable bit W = Writable bit |       |                  |       | U = Unimplemented bit, read as '0'     |       |       |       |  |  |  |

| -n = Value at P                   | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknow |       |       | nown  |  |  |  |

bit 15-8 Byte 5<15:8>: ECAN Message Byte 5 bits

bit 7-0 Byte 4<7:0>: ECAN Message Byte 4 bits

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER

| 11.0   | 11.0 | 11.0 | 11.0 | 11.0 |          |          |         |

|--------|------|------|------|------|----------|----------|---------|

| U-0    | U-0  | U-0  | U-0  | U-0  | R/W-0    | R/W-0    | R/W-0   |

| —      | _    |      |      |      | CH123NB1 | CH123NB0 | CH123SB |

| bit 15 |      |      |      |      |          |          | bit 8   |

|        |      |      |      |      |          |          |         |

| U-0    | U-0  | U-0  | U-0  | U-0  | R/W-0    | R/W-0    | R/W-0   |

| 0-0   | 0-0 | 0-0 | 0-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

|-------|-----|-----|-----|-----|----------|----------|---------|

| —     | —   | —   | _   |     | CH123NA1 | CH123NA0 | CH123SA |

| bit 7 |     |     |     |     |          |          | bit 0   |

## Legend:

| Legenu.           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-11 Unimplemented: Read as '0'

bit 10-9

CH123NB<1:0>: Channel 1, 2, 3 Negative Input Select for Sample MUXB bits

In 12-bit mode (AD21B = 1), CH123NB is Unimplemented and is Read as '0':

| Value           | ADC Channel |       |       |  |  |

|-----------------|-------------|-------|-------|--|--|

| value           | CH1         | CH2   | CH3   |  |  |

| 11              | AN9         | AN10  | AN11  |  |  |

| 10 <b>(1,2)</b> | OA3/AN6     | AN7   | AN8   |  |  |

| 0x              | Vrefl       | Vrefl | VREFL |  |  |

bit 8 **CH123SB:** Channel 1, 2, 3 Positive Input Select for Sample MUXB bit In 12-bit mode (AD21B = 1), CH123SB is Unimplemented and is Read as '0':

| Value          | ADC Channel |         |         |  |  |

|----------------|-------------|---------|---------|--|--|

| value          |             |         | CH3     |  |  |

| 1 <b>(2)</b>   | OA1/AN3     | OA2/AN0 | OA3/AN6 |  |  |

| 0 <b>(1,2)</b> | OA2/AN0     | AN1     | AN2     |  |  |

bit 7-3 Unimplemented: Read as '0'

bit 2-1 **CH123NA<1:0>:** Channel 1, 2, 3 Negative Input Select for Sample MUXA bits In 12-bit mode (AD21B = 1), CH123NA is Unimplemented and is Read as '<u>0</u>':

| Value           | ADC Channel |       |       |  |  |

|-----------------|-------------|-------|-------|--|--|

| value           | CH1         | CH2   | CH3   |  |  |

| 11              | AN9         | AN10  | AN11  |  |  |

| 10 <b>(1,2)</b> | OA3/AN6     | AN7   | AN8   |  |  |

| 0x              | VREFL       | VREFL | Vrefl |  |  |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER      | 25-3: CM40                                              | CON: COMPA                             | RATOR 4 CO        | ONTROL RE        | GISTER             |                                            |                     |  |  |

|---------------|---------------------------------------------------------|----------------------------------------|-------------------|------------------|--------------------|--------------------------------------------|---------------------|--|--|

| R/W-0         | R/W-0                                                   | R/W-0                                  | U-0               | U-0              | U-0                | R/W-0                                      | R/W-0               |  |  |

| CON           | COE                                                     | CPOL                                   | —                 | —                | _                  | CEVT                                       | COUT                |  |  |

| bit 15        |                                                         |                                        |                   |                  |                    |                                            | bit 8               |  |  |

| R/W-0         | DAALO                                                   | U-0                                    |                   | U-0              | U-0                |                                            | R/W-0               |  |  |

|               | R/W-0                                                   | 0-0                                    | R/W-0             | 0-0              | 0-0                | R/W-0                                      |                     |  |  |

| EVPOL1        | EVPOL0                                                  | —                                      | CREF              | —                | _                  | CCH1 <sup>(1)</sup>                        | CCH0 <sup>(1)</sup> |  |  |

| bit 7         |                                                         |                                        |                   |                  |                    |                                            | bit (               |  |  |

| Legend:       |                                                         |                                        |                   |                  |                    |                                            |                     |  |  |

| R = Readable  | e bit                                                   | W = Writable                           | bit               | U = Unimple      | mented bit, rea    | d as '0'                                   |                     |  |  |

| -n = Value at |                                                         | '1' = Bit is se                        |                   | '0' = Bit is cle |                    | x = Bit is unkr                            | iown                |  |  |

|               |                                                         |                                        | •                 |                  |                    |                                            |                     |  |  |

| bit 15        | CON: Comp                                               | arator Enable b                        | bit               |                  |                    |                                            |                     |  |  |

|               |                                                         | ator is enabled                        |                   |                  |                    |                                            |                     |  |  |

|               |                                                         | ator is disabled                       |                   |                  |                    |                                            |                     |  |  |

| bit 14        | COE: Comp                                               | arator Output E                        | nable bit         |                  |                    |                                            |                     |  |  |

|               |                                                         | ator output is pr<br>ator output is in |                   | xOUT pin         |                    |                                            |                     |  |  |

| bit 13        | CPOL: Com                                               | parator Output                         | Polarity Select   | bit              |                    |                                            |                     |  |  |

|               |                                                         | ator output is in                      |                   |                  |                    |                                            |                     |  |  |

|               | 0 = Compara                                             | ator output is no                      | ot inverted       |                  |                    |                                            |                     |  |  |

| bit 12-10     | Unimpleme                                               | nted: Read as                          | '0'               |                  |                    |                                            |                     |  |  |

| bit 9         | CEVT: Com                                               | parator Event b                        | it                |                  |                    |                                            |                     |  |  |

|               | interrup                                                | ts until the bit is                    | cleared           | POL<1:0> set     | tings occurred;    | disables future                            | triggers and        |  |  |

|               | •                                                       | ator event did i                       |                   |                  |                    |                                            |                     |  |  |

| bit 8         |                                                         | parator Output                         |                   |                  |                    |                                            |                     |  |  |

|               | $\frac{\text{VVnen CPOL}}{1 = \text{VIN} + > \text{V}}$ | When CPOL = 0 (non-inverted polarity): |                   |                  |                    |                                            |                     |  |  |

|               | 0 = VIN + < V                                           |                                        |                   |                  |                    |                                            |                     |  |  |

|               | When CPOL                                               | = 1 (inverted p                        | olarity):         |                  |                    |                                            |                     |  |  |

|               | 1 = VIN+ < V                                            |                                        |                   |                  |                    |                                            |                     |  |  |

|               | 0 = VIN + > V                                           | 'IN-                                   |                   |                  |                    |                                            |                     |  |  |

| bit 7-6       |                                                         | >: Trigger/Ever                        |                   | -                |                    |                                            |                     |  |  |

|               | 10 = Trigger                                            |                                        | generated only    |                  |                    | or output (while (<br>ne polarity selected |                     |  |  |

|               |                                                         | L = 1 (inverted)<br>-high transition   |                   | ator output.     |                    |                                            |                     |  |  |

|               |                                                         | L = 0 (non-inve<br>-low transition     |                   | ator output.     |                    |                                            |                     |  |  |

|               |                                                         | /event/interrupt<br>(while CEVT =      |                   | v on low-to-higl | n transition of th | e polarity selecte                         | ed comparato        |  |  |

|               |                                                         | L = 1 (inverted                        |                   | ator output.     |                    |                                            |                     |  |  |

|               |                                                         | L = 0 (non-inve<br>-high transition    |                   | ator output.     |                    |                                            |                     |  |  |

|               | 00 = Trigger                                            | /event/interrupt                       | generation is     | disabled         |                    |                                            |                     |  |  |

| Note 1: In    | puts that are se                                        | lected and not a                       | available will be | e tied to Vss. S | See the "Pin Dia   | agrams" sectior                            | n for available     |  |  |

Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

## 27.6 JTAG Interface

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement a JTAG interface, which supports boundary scan device testing. Detailed information on this interface is provided in future revisions of the document.

| Note: | Refer to "Programming and Diagnostics"       |

|-------|----------------------------------------------|

|       | (DS70608) in the "dsPIC33/PIC24 Family       |

|       | Reference Manual" for further information    |

|       | on usage, configuration and operation of the |

|       | JTAG interface.                              |

## 27.7 In-Circuit Serial Programming

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices can be serially programmed while in the end application circuit. This is done with two lines for clock and data, and three other lines for power, ground and the programming sequence. Serial programming allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. Serial programming also allows the most recent firmware or a custom firmware to be programmed. Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for details about In-Circuit Serial Programming (ICSP).

Any of the three pairs of programming clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

## 27.8 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 3 or REAL ICE<sup>™</sup> is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. Debugging functionality is controlled through the PGECx (Emulation/Debug Clock) and PGEDx (Emulation/Debug Data) pin functions.

Any of the three pairs of debugging clock/data pins can be used:

- PGEC1 and PGED1

- PGEC2 and PGED2

- PGEC3 and PGED3

To use the in-circuit debugger function of the device, the design must implement ICSP connections to  $\overline{MCLR}$ , VDD, Vss and the PGECx/PGEDx pin pair. In addition, when the feature is enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins (PGECx and PGEDx).

## 27.9 Code Protection and CodeGuard™ Security

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X, and PIC24EPXXXGP/MC20X devices offer basic implementation of CodeGuard Security that supports only General Segment (GS) security. This feature helps protect individual Intellectual Property.

Note: Refer to "CodeGuard<sup>™</sup> Security" (DS70634) in the "dsPIC33/PIC24 Family Reference Manual" for further information on usage, configuration and operation of CodeGuard Security.

| AC CHARAG            | CTERISTICS                               |                                             | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |     |     |     |

|----------------------|------------------------------------------|---------------------------------------------|----------------------------------------------------------|-----|-----|-----|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)               | CKE | СКР | SMP |

| 15 MHz               | Table 30-33                              | _                                           | _                                                        | 0,1 | 0,1 | 0,1 |

| 9 MHz                | _                                        | Table 30-34                                 | —                                                        | 1   | 0,1 | 1   |

| 9 MHz                | —                                        | Table 30-35                                 | —                                                        | 0   | 0,1 | 1   |

| 15 MHz               | —                                        | —                                           | Table 30-36                                              | 1   | 0   | 0   |

| 11 MHz               | —                                        | —                                           | Table 30-37                                              | 1   | 1   | 0   |

| 15 MHz               | _                                        | —                                           | Table 30-38                                              | 0   | 1   | 0   |

| 11 MHz               | _                                        | —                                           | Table 30-39                                              | 0   | 0   | 0   |

#### TABLE 30-33: SPI2 MAXIMUM DATA/CLOCK RATE SUMMARY

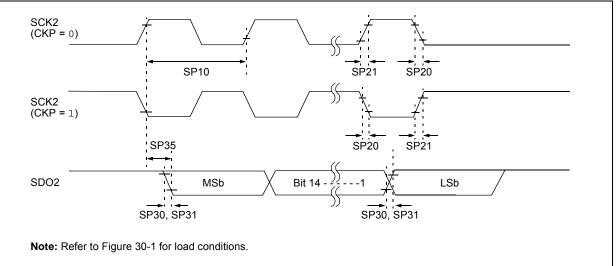

## FIGURE 30-14: SPI2 MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY, CKE = 0) TIMING CHARACTERISTICS

# 32.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

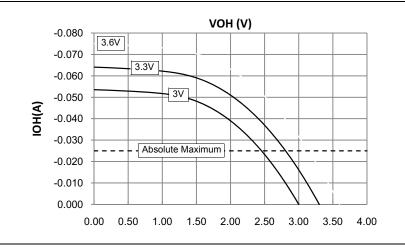

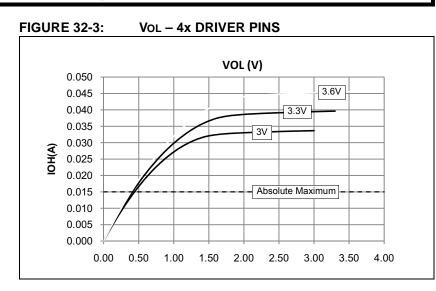

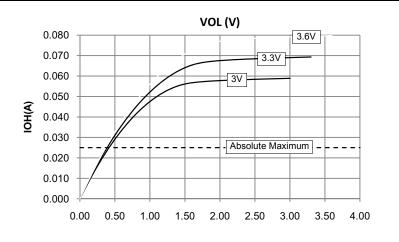

**Note:** The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

**FIGURE 32-1: VOH – 4x DRIVER PINS** VOH (V) -0.050 -0.045 3.6V -0.040 3.3V -0.035 3V -0.030 IOH(A) -0.025 -0.020 Absolute Maximum -0.015 -0.010 -0.005 0.000 0.50 1.00 2.00 2.50 3.00 3.50 0.00 1.50 4.00

## FIGURE 32-2: VOH – 8x DRIVER PINS

## FIGURE 32-4: Vol – 8x DRIVER PINS

## **Revision D (December 2011)**

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-3.

## TABLE A-3: MAJOR SECTION UPDATES

| Section Name                                                                                                                                                            | Update Description                                                                                                                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "16-bit Microcontrollers<br>and Digital Signal<br>Controllers (up to<br>512-Kbyte Flash and<br>48-Kbyte SRAM) with High-<br>Speed PWM, Op amps, and<br>Advanced Analog" | Removed the Analog Comparators column and updated the Op amps/Comparators column in Table 1 and Table 2.                                                                                                                                                                                                |

| Section 21.0 "Enhanced<br>CAN (ECAN™) Module<br>(dsPIC33EPXXXGP/MC50X<br>Devices Only)"                                                                                 | Updated the CANCKS bit value definitions in CiCTRL1: ECAN Control Register 1 (see Register 21-1).                                                                                                                                                                                                       |

| Section 30.0 "Electrical<br>Characteristics"                                                                                                                            | Updated the VBOR specifications and/or its related note in the following electrical<br>characteristics tables:<br>• Table 30-1<br>• Table 30-4<br>• Table 30-12<br>• Table 30-14<br>• Table 30-15<br>• Table 30-16<br>• Table 30-56<br>• Table 30-57<br>• Table 30-58<br>• Table 30-59<br>• Table 30-60 |

| TyCON (Timer3 and Timer5 Control)    | 211    |

|--------------------------------------|--------|

| UxMODE (UARTx Mode)                  |        |

| UxSTA (UARTx Status and Control)     |        |

| VEL1CNT (Velocity Counter 1)         |        |

| Resets                               | 123    |

| Brown-out Reset (BOR)                |        |

| Configuration Mismatch Reset (CM)    | 123    |

| Illegal Condition Reset (IOPUWR)     | 123    |

| Illegal Opcode                       | 123    |

| Security                             |        |

| Uninitialized W Register             | 123    |

| Master Clear (MCLR) Pin Reset        | 123    |

| Power-on Reset (POR)                 |        |

| RESET Instruction (SWR)              |        |

| Resources                            |        |

| Trap Conflict Reset (TRAPR)          | 123    |

| Watchdog Timer Time-out Reset (WDTO) | 123    |

| Resources Required for Digital PFC   | 32, 34 |

| Revision History                     | 507    |

## S

| Serial Peripheral Interface (SPI)<br>Software Stack Pointer (SSP) |     |

|-------------------------------------------------------------------|-----|

| Special Features of the CPU                                       |     |

| SPI                                                               |     |

| Control Registers                                                 | 268 |

| Helpful Tips                                                      | 267 |

| Resources                                                         | 267 |

## т

| Temperature and Voltage Specifications |

|----------------------------------------|

| AC                                     |

| Thermal Operating Conditions           |

| Thermal Packaging Characteristics      |

| Timer1                                 |

| Control Register                       |

| Resources                              |

| Timer2/3 and Timer4/5                  |

| Control Registers                      |

| Resources                              |

| Timing Diagrams                        |

| 10-Bit ADC Conversion (CHPS<1:0> = 01, |

| SIMSAM = 0, ASAM = 0, SSRC<2:0> = 000, |

| SSRCG = 0)                             |

| 10-Bit ADC Conversion (CHPS<1:0> = 01, |

| SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, |

| SSRCG = 0, SAMC<4:0> = 00010)          |

| 12-Bit ADC Conversion (ASAM = 0,       |

| SSRC<2:0> = 000, SSRCG = 0)            |

| BOR and Master Clear Reset             |

| ECANx I/O                              |

| External Clock414                      |

| High-Speed PWMx Fault422               |

| High-Speed PWMx Module                 |

| I/O Characteristics                    |

| I2Cx Bus Data (Master Mode)450         |

| I2Cx Bus Data (Slave Mode)             |

| I2Cx Bus Start/Stop Bits (Master Mode) |

| I2Cx Bus Start/Stop Bits (Slave Mode)  |

|                                        |

| Input Capture x (ICx)                         | . 420 |

|-----------------------------------------------|-------|

| OCx/PWMx                                      |       |

| Output Compare x (OCx)                        | . 421 |

| QEA/QEB Input                                 | . 424 |

| QEI Module Index Pulse                        | . 425 |

| SPI1 Master Mode (Full-Duplex, CKE = 0,       |       |

| CKP = x, SMP = 1)                             | . 441 |

| SPI1 Master Mode (Full-Duplex, CKE = 1,       |       |

| CKP = x, SMP = 1)                             | . 440 |

| SPI1 Master Mode (Half-Duplex, Transmit Only, |       |

| CKE = 0)                                      | . 438 |

| SPI1 Master Mode (Half-Duplex, Transmit Only, |       |

| CKE = 1)                                      | . 439 |

| SPI1 Slave Mode (Full-Duplex, CKE = 0,        |       |

| CKP = 0, SMP = 0)                             | . 448 |

| SPI1 Slave Mode (Full-Duplex, CKE = 0,        |       |

| CKP = 1, SMP = 0)                             | . 446 |

| SPI1 Slave Mode (Full-Duplex, CKE = 1,        |       |

| CKP = 0, SMP = 0)                             | . 442 |

| SPI1 Slave Mode (Full-Duplex, CKE = 1,        |       |

| CKP = 1, SMP = 0)                             | . 444 |

| SPI2 Master Mode (Full-Duplex, CKE = 0,       |       |

| CKP = x, SMP = 1)                             | . 429 |

| SPI2 Master Mode (Full-Duplex, CKE = 1,       |       |

| CKP = x, SMP = 1)                             | . 428 |

| SPI2 Master Mode (Half-Duplex, Transmit Only, |       |

| CKE = 0)                                      | . 426 |

| SPI2 Master Mode (Half-Duplex, Transmit Only, |       |

| CKE = 1)                                      | . 427 |

| SPI2 Slave Mode (Full-Duplex, CKE = 0,        |       |

| CKP = 0, SMP = 0)                             | . 436 |

| SPI2 Slave Mode (Full-Duplex, CKE = 0,        |       |

| CKP = 1, SMP = 0)                             | . 434 |

| SPI2 Slave Mode (Full-Duplex, CKE = 1,        |       |

| CKP = 0, SMP = 0)                             | . 430 |

| SPI2 Slave Mode (Full-Duplex, CKE = 1,        |       |

| CKP = 1, SMP = 0)                             |       |

| Timer1-Timer5 External Clock                  |       |

| TimerQ (QEI Module) External Clock            |       |

| UARTx I/O                                     | . 454 |

|                                               |       |

## U

| Universal Asynchronous Receiver |       |

|---------------------------------|-------|

| Transmitter (UART)              | . 281 |

| Control Registers               | . 283 |

| Helpful Tips                    | . 282 |

| Resources                       | . 282 |

| User ID Words                   | . 384 |

| V                               |       |

| Voltage Regulator (On-Chip)     | . 384 |

# w

| Watchdog Timer (WDT)       | 379, 385 |

|----------------------------|----------|

| Programming Considerations | 385      |

| WWW Address                | 524      |

| WWW, On-Line Support       | 23       |

NOTES: