Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Betans                     |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                          |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 60 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 512KB (170K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 24K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc206t-e-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

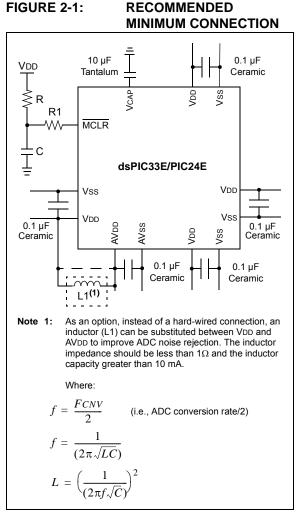

#### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

## 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 1 Ohm) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD and must have a capacitor greater than 4.7  $\mu$ F (10  $\mu$ F is recommended), 16V connected to ground. The type can be ceramic or tantalum. See **Section 30.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP pin. It is recommended that the trace length not exceeds one-quarter inch (6 mm). See **Section 27.3 "On-Chip Voltage Regulator"** for details.

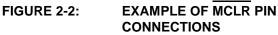

## 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor, C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components as shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

| TABLE        | 4-2:  | CPU C                 | CORE RE | EGISTER | R MAP F | FOR PIC | 24EPX) | XGP/M | C20X D   | EVICES | ONLY  |       |           |          |       |       |       |               |

|--------------|-------|-----------------------|---------|---------|---------|---------|--------|-------|----------|--------|-------|-------|-----------|----------|-------|-------|-------|---------------|

| File<br>Name | Addr. | Bit 15                | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8    | Bit 7  | Bit 6 | Bit 5 | Bit 4     | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| W0           | 0000  |                       |         |         |         |         |        |       | W0 (WR   | EG)    |       |       |           |          |       |       |       | xxxx          |

| W1           | 0002  |                       | W1 xxx  |         |         |         |        |       |          |        |       | xxxx  |           |          |       |       |       |               |

| W2           | 0004  |                       | W2 xxx  |         |         |         |        |       |          |        | xxxx  |       |           |          |       |       |       |               |

| W3           | 0006  |                       |         |         |         |         |        |       | W3       |        |       |       |           |          |       |       |       | xxxx          |

| W4           | 0008  |                       |         |         |         |         |        |       | W4       |        |       |       |           |          |       |       |       | xxxx          |

| W5           | 000A  |                       | W5 xxxx |         |         |         |        |       |          | xxxx   |       |       |           |          |       |       |       |               |

| W6           | 000C  |                       |         |         |         |         |        |       | W6       |        |       |       |           |          |       |       |       | xxxx          |

| W7           | 000E  |                       |         |         |         |         |        |       | W7       |        |       |       |           |          |       |       |       | xxxx          |

| W8           | 0010  |                       |         |         |         |         |        |       | W8       |        |       |       |           |          |       |       |       | xxxx          |

| W9           | 0012  |                       |         |         |         |         |        |       | W9       |        |       |       |           |          |       |       |       | xxxx          |

| W10          | 0014  |                       |         |         |         |         |        |       | W10      |        |       |       |           |          |       |       |       | xxxx          |

| W11          | 0016  |                       | W11 xxx |         |         |         |        |       |          | xxxx   |       |       |           |          |       |       |       |               |

| W12          | 0018  |                       |         |         |         |         |        |       | W12      |        |       |       |           |          |       |       |       | xxxx          |

| W13          | 001A  |                       |         |         |         |         |        |       | W13      |        |       |       |           |          |       |       |       | xxxx          |

| W14          | 001C  |                       |         |         |         |         |        |       | W14      |        |       |       |           |          |       |       |       | xxxx          |

| W15          | 001E  |                       |         |         |         |         |        |       | W15      |        |       |       |           |          |       |       |       | xxxx          |

| SPLIM        | 0020  |                       |         |         |         |         |        |       | SPLIM<1  | 5:0>   |       |       |           |          |       |       |       | 0000          |

| PCL          | 002E  |                       |         |         |         |         |        | P     | CL<15:1> |        |       |       |           |          |       |       | —     | 0000          |

| PCH          | 0030  | —                     | -       | _       | _       | —       | —      | —     | —        | _      |       |       |           | PCH<6:0> |       |       |       | 0000          |

| DSRPAG       | 0032  | —                     | -       | _       | _       | —       | —      |       |          |        |       | DSRPA | G<9:0>    |          |       |       |       | 0001          |

| DSWPAG       | 0034  | _                     |         |         |         | _       |        | _     |          |        |       | DS    | SWPAG<8:0 | >        |       |       |       | 0001          |

| RCOUNT       | 0036  | RCOUNT<15:0> 0        |         |         |         |         |        |       | 0000     |        |       |       |           |          |       |       |       |               |

| SR           | 0042  | _                     |         |         |         | —       |        | —     | DC       | IPL2   | IPL1  | IPL0  | RA        | N        | OV    | Z     | С     | 0000          |

| CORCON       | 0044  | VAR                   | _       | -       | _       | —       |        | —     | _        | -      | _     | —     | -         | IPL3     | SFA   | —     | _     | 0020          |

| DISICNT      | 0052  | — — DISICNT<13:0> 000 |         |         |         |         |        |       | 0000     |        |       |       |           |          |       |       |       |               |

| TBLPAG       | 0054  | TBLPAG<7:0>           |         |         |         |         |        |       | 0000     |        |       |       |           |          |       |       |       |               |

| MSTRPR       | 0058  | MSTRPR<15:0> 0000     |         |         |         |         |        |       | 0000     |        |       |       |           |          |       |       |       |               |

#### **D** I -4.0 - -

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-45: DMAC REGISTER MAP

| File Name | Addr. | Bit 15              | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7         | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|---------------------|--------|--------|--------|--------|--------|-------|--------|---------------|-------|-------|--------|--------|--------|--------|--------|---------------|

| DMA0CON   | 0B00  | CHEN                | SIZE   | DIR    | HALF   | NULLW  |        | _     | _      | _             | _     | AMOD  | E<1:0> | _      | _      | MODE   | <1:0>  | 0000          |

| DMA0REQ   | 0B02  | FORCE               | _      | _      |        | _      | _      | _     | _      |               |       | •     | IRQSE  | _<7:0> | •      |        |        | 00FF          |

| DMA0STAL  | 0B04  | STA<15:0>           |        |        |        |        |        |       |        |               | 0000  |       |        |        |        |        |        |               |

| DMA0STAH  | 0B06  | _                   | _      | _      | _      | _      | _      | _     | _      |               |       |       | STA<2  | 3:16>  |        |        |        | 0000          |

| DMA0STBL  | 0B08  |                     |        |        |        |        |        |       | STB<1  | 5:0>          |       |       |        |        |        |        |        | 0000          |

| DMA0STBH  | 0B0A  | _                   | —      | —      | _      | _      | —      | —     | —      |               |       |       | STB<2  | 3:16>  |        |        |        | 0000          |

| DMA0PAD   | 0B0C  |                     |        |        |        |        |        |       | PAD<1  | 5:0>          |       |       |        |        |        |        |        | 0000          |

| DMA0CNT   | 0B0E  | _                   | _      |        |        |        |        |       |        | CNT<1         | 3:0>  |       |        |        |        |        |        | 0000          |

| DMA1CON   | 0B10  | CHEN                | SIZE   | DIR    | HALF   | NULLW  | —      | —     | —      | _             | —     | AMOD  | E<1:0> | —      | _      | MODE   | <1:0>  | 0000          |

| DMA1REQ   | 0B12  | FORCE               | _      | _      |        | _      | _      | _     | _      |               |       |       | IRQSE  | _<7:0> | •      |        |        | 00FF          |

| DMA1STAL  | 0B14  |                     |        |        |        |        |        |       | STA<15 | 5:0>          |       |       |        |        |        |        |        | 0000          |

| DMA1STAH  | 0B16  | _                   | —      | —      | _      | _      | —      | —     | —      |               |       |       | STA<2  | 3:16>  |        |        |        | 0000          |

| DMA1STBL  | 0B18  |                     |        |        |        |        |        |       | STB<1  | 5:0>          |       |       |        |        |        |        |        | 0000          |

| DMA1STBH  | 0B1A  | _                   | _      | _      | _      |        | _      | _     | _      |               |       |       | STB<2  | 3:16>  |        |        |        | 0000          |

| DMA1PAD   | 0B1C  |                     |        |        |        |        |        |       | PAD<1  |               |       |       |        | 0000   |        |        |        |               |

| DMA1CNT   | 0B1E  | _                   | —      |        |        |        |        |       |        | CNT<13:0>     |       |       |        |        | 0000   |        |        |               |

| DMA2CON   | 0B20  | CHEN                | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _             | _     | AMOD  | E<1:0> |        | —      | MODE   | <1:0>  | 0000          |

| DMA2REQ   | 0B22  | FORCE               | _      | _      |        | _      | _      | _     | _      | - IRQSEL<7:0> |       |       |        |        |        | 00FF   |        |               |

| DMA2STAL  | 0B24  |                     |        |        |        |        |        |       | STA<18 | 5:0>          |       |       |        |        |        |        |        | 0000          |

| DMA2STAH  | 0B26  | _                   | _      | _      | _      | _      | _      | _     | _      |               |       |       | STA<2  | 3:16>  |        |        |        | 0000          |

| DMA2STBL  | 0B28  |                     |        |        |        |        |        |       | STB<1  | 5:0>          |       |       |        |        |        |        |        | 0000          |

| DMA2STBH  | 0B2A  | _                   | _      | _      | _      | _      | _      | _     | _      |               |       |       | STB<2  | 3:16>  |        |        |        | 0000          |

| DMA2PAD   | 0B2C  |                     |        |        |        |        |        |       | PAD<1  | 5:0>          |       |       |        |        |        |        |        | 0000          |

| DMA2CNT   | 0B2E  | _                   | _      |        |        |        |        |       |        | CNT<1         | 3:0>  |       |        |        |        |        |        | 0000          |

| DMA3CON   | 0B30  | CHEN                | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _             | _     | AMOD  | E<1:0> | -      | —      | MODE   | <1:0>  | 0000          |

| DMA3REQ   | 0B32  | FORCE               | _      | _      | _      | _      | _      | _     | _      |               |       |       | IRQSE  | L<7:0> |        |        |        | 00FF          |

| DMA3STAL  | 0B34  |                     |        |        |        |        |        |       | STA<18 | 5:0>          |       |       |        |        |        |        |        | 0000          |

| DMA3STAH  | 0B36  | _                   | _      | _      | _      | _      | _      | _     | _      |               |       |       | STA<2  | 3:16>  |        |        |        | 0000          |

| DMA3STBL  | 0B38  |                     |        |        |        |        |        |       | STB<1  | 5:0>          |       |       |        |        |        |        |        | 0000          |

| DMA3STBH  | 0B3A  | _                   | _      | _      | _      | _      | _      | _     | _      |               |       |       | STB<2  | 3:16>  |        |        |        | 0000          |

| DMA3PAD   | 0B3C  |                     |        |        |        |        |        |       | PAD<1  | 5:0>          |       |       |        |        |        |        |        | 0000          |

| DMA3CNT   | 0B3E  | _                   | _      |        |        |        |        |       |        | CNT<1         | 3:0>  |       |        |        |        |        |        | 0000          |

| DMAPWC    | 0BF0  | _                   | —      | —      | —      | —      | —      |       | _      | —             | —     |       | —      | PWCOL3 | PWCOL2 | PWCOL1 | PWCOL0 | 0000          |

| DMARQC    | 0BF2  | _                   | —      | _      | _      | _      | _      | _     | _      | _             | _     | _     | _      | RQCOL3 | RQCOL2 | RQCOL1 | RQCOL0 | 0000          |

| DMAPPS    | 0BF4  | _                   | —      | _      | _      | _      | _      | _     | _      | _             | _     | _     | _      | PPST3  | PPST2  | PPST1  | PPST0  | 0000          |

| DMALCA    | 0BF6  | _                   | _      | _      | _      | _      | _      | _     | _      | _             | _     | _     | _      |        | LSTCH  | 1<3:0> |        | 000F          |

| DSADRL    | 0BF8  | 0BF8 DSADR<15:0> 0  |        |        |        |        |        |       | 0000   |               |       |       |        |        |        |        |        |               |

| DSADRH    | 0BFA  | BFA DSADR<23:16> 00 |        |        |        |        |        |       | 0000   |               |       |       |        |        |        |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

| -n = Value at F | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | mented bit, rea | id as '0'       |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

|                 |       |                  |       |                  |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit C |

|                 |       |                  | NVMAD | )R<23:16>        |                 |                 |       |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

| _               | —     | —                | —     | —                | _               | —               | —     |

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0             | U-0             | U-0   |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMADR<23:16>:** Nonvolatile Memory Write Address High bits Selects the upper 8 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

#### REGISTER 5-3: NVMADRL: NONVOLATILE MEMORY ADDRESS REGISTER LOW

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | NVMA  | DR<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

| R/W-x           | R/W-x | R/W-x            | R/W-x | R/W-x            | R/W-x           | R/W-x           | R/W-x |

|                 |       |                  | NVMA  | DR<7:0>          |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 NVMADR<15:0>: Nonvolatile Memory Write Address Low bits

Selects the lower 16 bits of the location to program or erase in program Flash memory. This register may be read or written by the user application.

#### REGISTER 5-4: NVMKEY: NONVOLATILE MEMORY KEY

| U-0             | U-0 | U-0              | U-0  | U-0              | U-0             | U-0             | U-0   |

|-----------------|-----|------------------|------|------------------|-----------------|-----------------|-------|

| —               | —   | —                | —    | —                | —               | —               | —     |

| bit 15          |     |                  |      |                  |                 |                 | bit 8 |

|                 |     |                  |      |                  |                 |                 |       |

| W-0             | W-0 | W-0              | W-0  | W-0              | W-0             | W-0             | W-0   |

|                 |     |                  | NVMK | EY<7:0>          |                 |                 |       |

| bit 7           |     |                  |      |                  |                 |                 | bit 0 |

|                 |     |                  |      |                  |                 |                 |       |

| Legend:         |     |                  |      |                  |                 |                 |       |

| R = Readable I  | bit | W = Writable     | bit  | U = Unimple      | mented bit, rea | d as '0'        |       |

| -n = Value at P | OR  | '1' = Bit is set |      | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 **NVMKEY<7:0>:** Key Register (write-only) bits

| R/W-0           | R/W-0                           | R/W-1                             | R/W-1                | R/W-0                  | R/W-0              | R/W-0           | R/W-0     |

|-----------------|---------------------------------|-----------------------------------|----------------------|------------------------|--------------------|-----------------|-----------|

| ROI             | DOZE2 <sup>(1)</sup>            | DOZE1 <sup>(1)</sup>              | DOZE0 <sup>(1)</sup> | DOZEN <sup>(2,3)</sup> | FRCDIV2            | FRCDIV1         | FRCDIV0   |

| bit 15          |                                 |                                   | •                    |                        |                    |                 | bit 8     |

|                 |                                 |                                   |                      |                        |                    |                 |           |

| R/W-0           | R/W-1                           | U-0                               | R/W-0                | R/W-0                  | R/W-0              | R/W-0           | R/W-0     |

| PLLPOST1        | PLLPOST0                        | —                                 | PLLPRE4              | PLLPRE3                | PLLPRE2            | PLLPRE1         | PLLPRE0   |

| bit 7           |                                 |                                   |                      |                        |                    |                 | bit (     |

|                 |                                 |                                   |                      |                        |                    |                 |           |

| Legend:         |                                 |                                   |                      |                        |                    |                 |           |

| R = Readable    |                                 | W = Writable                      |                      | -                      | nented bit, read   |                 |           |

| -n = Value at F | POR                             | '1' = Bit is set                  |                      | '0' = Bit is cle       | ared               | x = Bit is unkr | nown      |

| h:+ 45          |                                 | on Interview h                    |                      |                        |                    |                 |           |

| bit 15          |                                 | on Interrupt bis will clear the l |                      |                        |                    |                 |           |

|                 |                                 | s have no effect                  |                      | EN bit                 |                    |                 |           |

| bit 14-12       | •                               | Processor Clo                     |                      |                        |                    |                 |           |

|                 | 111 = Fcy div                   |                                   |                      |                        |                    |                 |           |

|                 | 110 = Fcy div                   | vided by 64                       |                      |                        |                    |                 |           |

|                 | 101 = Fcy div                   |                                   |                      |                        |                    |                 |           |

|                 | 100 = FCY div                   | vided by 16<br>vided by 8 (defa   | oult)                |                        |                    |                 |           |

|                 | 011 = FCY div<br>010 = FCY div  |                                   | auit)                |                        |                    |                 |           |

|                 | 001 = FCY div                   |                                   |                      |                        |                    |                 |           |

|                 | 000 = Fcy div                   | •                                 |                      |                        |                    |                 |           |

| bit 11          |                                 | e Mode Enable                     |                      |                        |                    |                 |           |

|                 |                                 |                                   |                      |                        | pheral clocks a    | nd the process  | or clocks |

|                 |                                 | -                                 | -                    | ratio is forced to     |                    |                 |           |

| bit 10-8        |                                 |                                   | RC Oscillator        | r Postscaler bit       | S                  |                 |           |

|                 | 111 = FRC di<br>110 = FRC di    |                                   |                      |                        |                    |                 |           |

|                 | 101 <b>= FRC di</b>             |                                   |                      |                        |                    |                 |           |

|                 | 100 <b>= FRC d</b> i            | vided by 16                       |                      |                        |                    |                 |           |

|                 | 011 = FRC di                    |                                   |                      |                        |                    |                 |           |

|                 | 010 = FRC di<br>001 = FRC di    | 2                                 |                      |                        |                    |                 |           |

|                 |                                 | vided by 2<br>vided by 1 (de      | fault)               |                        |                    |                 |           |

| bit 7-6         |                                 |                                   | -                    | r Select bits (al      | so denoted as      | 'N2', PLL posts | caler)    |

|                 | 11 = Output d                   |                                   |                      |                        |                    |                 | ,         |

|                 | 10 = Reserve                    |                                   |                      |                        |                    |                 |           |

|                 |                                 | livided by 4 (de                  | efault)              |                        |                    |                 |           |

| bit 5           | 00 = Output d                   | ted: Read as '                    | o'                   |                        |                    |                 |           |

|                 | •                               |                                   |                      |                        |                    |                 |           |

|                 | e DOZE<2:0> b<br>ZE<2:0> are ig |                                   | written to whe       | en the DOZEN           | bit is clear. If D | OZEN = 1, any   | writes to |

| <b>2:</b> This  | s bit is cleared                | when the ROI I                    | oit is set and a     | an interrupt occ       | urs.               |                 |           |

|                 | DOJENUS                         |                                   |                      |                        | ~ ~                |                 | <i>.</i>  |

#### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER

The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| R/W-0         | R/W-0        | R/W-0                                                 | R/W-0   | R/W-0             | R/W-0                 | R/W-0                | U-0   |

|---------------|--------------|-------------------------------------------------------|---------|-------------------|-----------------------|----------------------|-------|

| T5MD          | T4MD         | T3MD                                                  | T2MD    | T1MD              | QEI1MD <sup>(1)</sup> | PWMMD <sup>(1)</sup> | _     |

| bit 15        |              |                                                       |         |                   |                       |                      | bit   |

|               |              |                                                       |         |                   |                       |                      |       |

| R/W-0         | R/W-0        | R/W-0                                                 | R/W-0   | R/W-0             | U-0                   | R/W-0                | R/W-0 |

| I2C1MD        | U2MD         | U1MD                                                  | SPI2MD  | SPI1MD            | —                     | C1MD <sup>(2)</sup>  | AD1MD |

| bit 7         |              |                                                       |         |                   |                       |                      | bit   |

| Legend:       |              |                                                       |         |                   |                       |                      |       |

| R = Readabl   | e bit        | W = Writable                                          | bit     | U = Unimplen      | nented bit, read      | d as '0'             |       |

| -n = Value at | POR          | '1' = Bit is set                                      |         | '0' = Bit is clea | ared                  | x = Bit is unkno     | own   |

| bit 15        | 1 = Timer5 m | 5 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 14        | 1 = Timer4 m | 4 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 13        | 1 = Timer3 m | 3 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 12        | 1 = Timer2 m | 2 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 11        | 1 = Timer1 m | 1 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 10        | 1 = QEI1 mod | 11 Module Disa<br>Iule is disablec<br>Iule is enabled |         |                   |                       |                      |       |

| bit 9         | 1 = PWM mod  | /M Module Dis<br>dule is disabled<br>dule is enabled  | 1       |                   |                       |                      |       |

| bit 8         | Unimplemen   | ted: Read as '                                        | כי      |                   |                       |                      |       |

| bit 7         | 1 = I2C1 mod | 1 Module Disal<br>ule is disabled<br>ule is enabled   | ble bit |                   |                       |                      |       |

| bit 6         | 1 = UART2 m  | 2 Module Disa<br>odule is disabl<br>odule is enable   | ed      |                   |                       |                      |       |

| bit 5         | 1 = UART1 m  | 1 Module Disa<br>odule is disabl<br>odule is enable   | ed      |                   |                       |                      |       |

| bit 4         | 1 = SPI2 mod | 2 Module Disa<br>lule is disabled<br>lule is enabled  | ole bit |                   |                       |                      |       |

## REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This bit is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

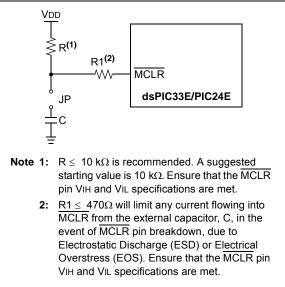

## 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70598) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Many of the device pins are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

## 11.1 Parallel I/O (PIO) Ports

Generally, a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Latch register (LATx) read the latch. Writes to the Latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device is disabled. This means the corresponding LATx and TRISx registers and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

#### 11.7 **Peripheral Pin Select Registers**

#### REGISTER 11-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      |       |       |       | INT1R<6:0> |       |       |       |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

| —      | —     | —     | —     | —          | _     | _     | —     |

| bit 7  |       | •     |       | •          |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

| Legend: |

|---------|

|---------|

| Legena:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15 | Unimplemented: Read as '0' |

|--------|----------------------------|

|--------|----------------------------|

bit 14-8 INT1R<6:0>: Assign External Interrupt 1 (INT1) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 0000001 = Input tied to CMP1 0000000 = Input tied to Vss bit 7-0 Unimplemented: Read as '0'

#### REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER (CONTINUED)

- bit 2 INDEX: Status of INDXx Input Pin After Polarity Control

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 1 QEB: Status of QEBx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1' 0 = Pin is at logic '0'

- bit 0 **QEA:** Status of QEAx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

## REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

| bit 2 | <b>HOMIEN:</b> Home Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IDXIRQ:</b> Status Flag for Index Event Status bit<br>1 = Index event has occurred<br>0 = No Index event has occurred |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

#### REGISTER 18-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

- 1 = Transmit not yet started, SPIxTXB is full

- 0 = Transmit started, SPIxTXB is empty

#### Standard Buffer mode:

Automatically set in hardware when core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.

#### Enhanced Buffer mode:

Automatically set in hardware when the CPU writes to the SPIxBUF location, loading the last available buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write operation.

#### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive is complete, SPIxRXB is full

0 = Receive is incomplete, SPIxRXB is empty

#### Standard Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when the core reads the SPIxBUF location, reading SPIxRXB.

#### Enhanced Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to the buffer, filling the last unread buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from SPIxSR.

| R/W-0       R/W-0       R/W-0       U-0       U-0       U-0       U-0         DMABS2       DMABS1       DMABS0       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       … |                          |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|--|--|--|--|--|--|

| bit 15<br>U-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0<br>FSA4 FSA3 FSA2 FSA1<br>bit 7<br>Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknov<br>bit 15-13 DMABS<2:0>: DMA Buffer Size bits<br>111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U-0                      |  |  |  |  |  |  |  |  |

| U-0       U-0       U-0       R/W-0       R/W-0       R/W-0       R/W-0         —       —       —       FSA4       FSA3       FSA2       FSA1         bit 7         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-13       DMABS<2:0>: DMA Buffer Size bits       111 = Reserved       110 = 32 buffers in RAM       101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | —                        |  |  |  |  |  |  |  |  |

| FSA4     FSA3     FSA2     FSA1       bit 7       Legend:       R = Readable bit     W = Writable bit     U = Unimplemented bit, read as '0'       -n = Value at POR     '1' = Bit is set     '0' = Bit is cleared     x = Bit is unknown       bit 15-13     DMABS<2:0>: DMA Buffer Size bits       111 = Reserved       110 = 32 buffers in RAM       101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | bit 8                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |  |  |  |  |  |  |  |  |

| bit 7  Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow bit 15-13 DMABS<2:0>: DMA Buffer Size bits 111 = Reserved 110 = 32 buffers in RAM 101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                    |  |  |  |  |  |  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-13       DMABS<2:0>: DMA Buffer Size bits         111 = Reserved       110 = 32 buffers in RAM         101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | FSA0                     |  |  |  |  |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknow         bit 15-13       DMABS<2:0>: DMA Buffer Size bits       111 = Reserved         110 = 32 buffers in RAM       101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | bit C                    |  |  |  |  |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknow         bit 15-13       DMABS<2:0>: DMA Buffer Size bits       111 = Reserved         110 = 32 buffers in RAM       101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |  |  |  |  |  |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknow<br>bit 15-13 DMABS<2:0>: DMA Buffer Size bits<br>111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |  |  |  |  |  |  |  |  |

| bit 15-13 DMABS<2:0>: DMA Buffer Size bits<br>111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |  |  |  |  |  |  |  |  |

| 111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | wn                       |  |  |  |  |  |  |  |  |

| 111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |  |  |  |  |  |  |  |  |

| 111 = Reserved<br>110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |  |  |  |  |  |  |  |  |

| 110 = 32 buffers in RAM<br>101 = 24 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |  |  |  |  |  |  |  |  |

| 100 - 16 huffers in DAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |  |  |  |  |  |  |  |  |

| 100 = 16 builds in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 100 = 16 buffers in RAM  |  |  |  |  |  |  |  |  |

| 011 = 12 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |  |  |  |  |  |  |  |  |

| 010 = 8 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |  |  |  |  |  |  |  |  |

| 001 = 6 buffers in RAM<br>000 = 4 buffers in RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |  |  |  |  |  |  |  |  |

| bit 12-5 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |  |  |  |  |  |  |  |  |

| bit 4-0 <b>FSA&lt;4:0&gt;:</b> FIFO Area Starts with Buffer bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11111 = Read Buffer RB31 |  |  |  |  |  |  |  |  |

| 11110 = Read Buffer RB30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |  |  |  |  |  |  |  |  |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |  |  |  |  |  |  |  |  |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |  |  |  |  |  |  |  |  |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                          |  |  |  |  |  |  |  |  |

| 00001 = TX/RX Buffer TRB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |  |  |  |  |  |  |  |  |

| 00000 = TX/RX Buffer TRB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |  |  |  |  |  |  |  |  |

### REGISTER 21-4: CxFCTRL: ECANx FIFO CONTROL REGISTER

## 23.4 ADC Control Registers

#### REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1

| R/W-0         | U-0                        | R/W-0                               | R/W-0               | U-0               | R/W-0            | R/W-0                               | R/W-0               |  |  |

|---------------|----------------------------|-------------------------------------|---------------------|-------------------|------------------|-------------------------------------|---------------------|--|--|

| ADON          | —                          | ADSIDL                              | ADDMABM             |                   | AD12B            | FORM1                               | FORM0               |  |  |

| bit 15        | •                          |                                     |                     |                   |                  |                                     | bit 8               |  |  |

| R/W-0         | R/W-0                      | R/W-0                               | R/W-0               | R/W-0             | R/W-0            | R/W-0, HC, HS                       | R/C-0. HC. HS       |  |  |

| SSRC2         | SSRC1                      | SSRC0                               | SSRCG               | SIMSAM            | ASAM             | SAMP                                | DONE <sup>(3)</sup> |  |  |