Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 70 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 512KB (170K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 24K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 16x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc206t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

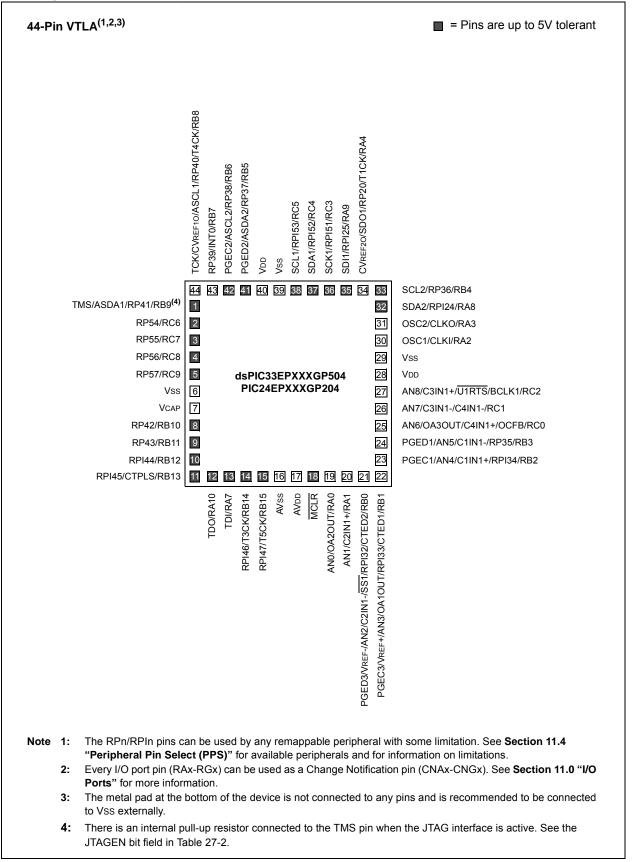

### **Pin Diagrams (Continued)**

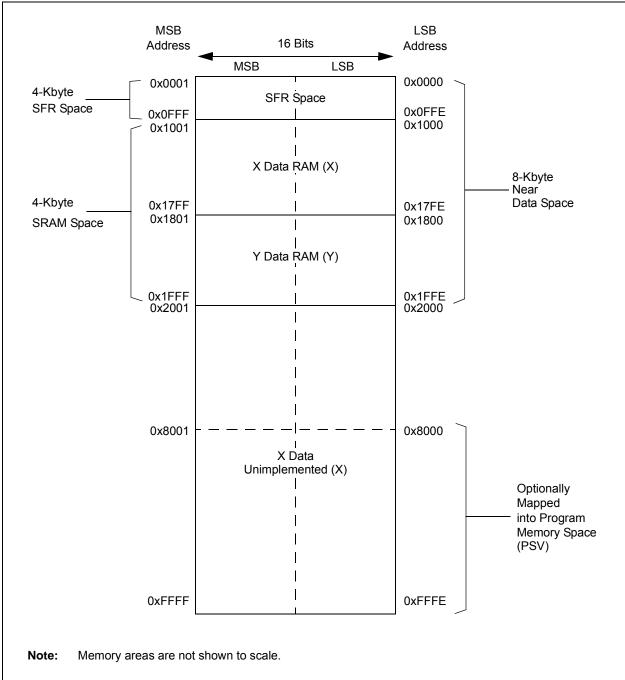

# FIGURE 4-7: DATA MEMORY MAP FOR dsPIC33EP32MC20X/50X AND dsPIC33EP32GP50X DEVICES

| IABLE 4   | -14:  | PVVIVI G | ENERA  | ATOR 2 REGISTER MAP FOR dSPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY |                                                             |        |        |          |            |           |          |         |         |          |          |         |         |               |

|-----------|-------|----------|--------|--------------------------------------------------------------------------------|-------------------------------------------------------------|--------|--------|----------|------------|-----------|----------|---------|---------|----------|----------|---------|---------|---------------|

| File Name | Addr. | Bit 15   | Bit 14 | Bit 13                                                                         | Bit 12                                                      | Bit 11 | Bit 10 | Bit 9    | Bit 8      | Bit 7     | Bit 6    | Bit 5   | Bit 4   | Bit 3    | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

| PWMCON2   | 0C40  | FLTSTAT  | CLSTAT | TRGSTAT                                                                        | FLTIEN                                                      | CLIEN  | TRGIEN | ITB      | MDCS       | DTC       | <1:0>    | DTCP    | _       | MTBS     | CAM      | XPRES   | IUE     | 0000          |

| IOCON2    | 0C42  | PENH     | PENL   | POLH                                                                           | POLL                                                        | PMOD   | 0<1:0> | OVRENH   | OVRENL     | OVRDA     | \T<1:0>  | FLTD    | \T<1:0> | CLDA     | AT<1:0>  | SWAP    | OSYNC   | C000          |

| FCLCON2   | 0C44  | _        |        | (                                                                              | CLSRC<4:0                                                   | )>     |        | CLPOL    | CLMOD      |           | FLT      | SRC<4:0 | >       |          | FLTPOL   | FLTMO   | D<1:0>  | 00F8          |

| PDC2      | 0C46  |          |        |                                                                                | PDC2<15:0> 000                                              |        |        |          |            |           |          |         | 0000    |          |          |         |         |               |

| PHASE2    | 0C48  |          |        |                                                                                |                                                             |        |        | Р        | HASE2<15:0 | >         |          |         |         |          |          |         |         | 0000          |

| DTR2      | 0C4A  | _        | _      |                                                                                |                                                             |        |        |          | [          | DTR2<13:0 | >        |         |         |          |          |         |         | 0000          |

| ALTDTR2   | 0C4C  | _        | _      |                                                                                |                                                             |        |        |          | AL         | TDTR2<13  | :0>      |         |         |          |          |         |         | 0000          |

| TRIG2     | 0C52  |          |        |                                                                                |                                                             |        |        | TI       | RGCMP<15:0 | )>        |          |         |         |          |          |         |         | 0000          |

| TRGCON2   | 0C54  |          | TRGDI  | V<3:0>                                                                         |                                                             | _      | —      | _        | _          | _         | -        |         |         | TRO      | GSTRT<5: | 0>      |         | 0000          |

| LEBCON2   | 0C5A  | PHR      | PHF    | PLR                                                                            | PLF FLTLEBEN CLLEBEN — — — BCH BCL BPHH BPHL BPLL BPLL 0000 |        |        |          |            |           |          |         | 0000    |          |          |         |         |               |

| LEBDLY2   | 0C5C  | _        | _      | _                                                                              | _                                                           |        |        |          |            |           | LEB<11:0 | )>      |         |          |          |         |         | 0000          |

| AUXCON2   | 0C5E  | _        | _      | —                                                                              | —                                                           |        | BLANK  | SEL<3:0> |            | _         | —        |         | CHOPS   | SEL<3:0> |          | CHOPHEN | CHOPLEN | 0000          |

I- DIGGOEDV/VMOGOV/EGV AND DIGGOEDV/VMOGOV DEVICED ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-15: PWM GENERATOR 3 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12                                                        | Bit 11                                              | Bit 10 | Bit 9  | Bit 8       | Bit 7     | Bit 6    | Bit 5   | Bit 4   | Bit 3 | Bit 2    | Bit 1 | Bit 0  | All<br>Resets |

|-----------|-------|---------|--------|---------|---------------------------------------------------------------|-----------------------------------------------------|--------|--------|-------------|-----------|----------|---------|---------|-------|----------|-------|--------|---------------|

| PWMCON3   | 0C60  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN                                                        | CLIEN                                               | TRGIEN | ITB    | MDCS        | DTC<      | <1:0>    | DTCP    | —       | MTBS  | CAM      | XPRES | IUE    | 0000          |

| IOCON3    | 0C62  | PENH    | PENL   | POLH    | POLL                                                          | PMOD                                                | )<1:0> | OVRENH | OVRENL      | OVRDA     | T<1:0>   | FLTD    | AT<1:0> | CLD   | AT<1:0>  | SWAP  | OSYNC  | C000          |

| FCLCON3   | 0C64  |         |        | (       | CLSRC<4:0                                                     | )>                                                  |        | CLPOL  | CLMOD       |           | FLT      | SRC<4:0 | >       |       | FLTPOL   | FLTMO | D<1:0> | 00F8          |

| PDC3      | 0C66  |         |        |         |                                                               |                                                     |        |        | PDC3<15:0>  | •         |          |         |         |       |          |       |        | 0000          |

| PHASE3    | 0C68  |         |        |         |                                                               |                                                     |        | F      | PHASE3<15:0 | )>        |          |         |         |       |          |       |        | 0000          |

| DTR3      | 0C6A  |         | —      |         |                                                               |                                                     |        |        | [           | DTR3<13:0 | >        |         |         |       |          |       |        | 0000          |

| ALTDTR3   | 0C6C  |         | —      |         |                                                               |                                                     |        |        | AL          | TDTR3<13  | :0>      |         |         |       |          |       |        | 0000          |

| TRIG3     | 0C72  |         |        |         |                                                               |                                                     |        | Т      | RGCMP<15:   | 0>        |          |         |         |       |          |       |        | 0000          |

| TRGCON3   | 0C74  |         | TRGDI  | V<3:0>  |                                                               | _                                                   | _      | _      | _           | _         | _        |         |         | TR    | GSTRT<5: | 0>    |        | 0000          |

| LEBCON3   | 0C7A  | PHR     | PHF    | PLR     | R PLF FLTLEBEN CLLEBEN — — — BCH BCL BPHH BPHL BPLH BPLL 0000 |                                                     |        |        |             |           |          |         | 0000    |       |          |       |        |               |

| LEBDLY3   | 0C7C  |         | —      | _       | _                                                             |                                                     |        |        |             |           | LEB<11:0 | )>      |         |       |          |       |        | 0000          |

| AUXCON3   | 0C7E  |         | —      | —       | —                                                             | BLANKSEL<3:0> — — CHOPSEL<3:0> CHOPHEN CHOPLEN 0000 |        |        |             |           |          |         | 0000    |       |          |       |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

.

----

.

### TABLE 4-42: OP AMP/COMPARATOR REGISTER MAP

| File Name                | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8 | Bit 7 | Bit 6  | Bit 5    | Bit 4 | Bit 3   | Bit 2  | Bit 1     | Bit 0 | All<br>Resets |

|--------------------------|-------|--------|--------|--------|--------|--------|---------|---------|-------|-------|--------|----------|-------|---------|--------|-----------|-------|---------------|

| CMSTAT                   | 0A80  | PSIDL  | _      | -      | —      | C4EVT  | C3EVT   | C2EVT   | C1EVT | _     | -      | —        | —     | C4OUT   | C3OUT  | C2OUT     | C10UT | 0000          |

| CVRCON                   | 0A82  |        | CVR2OE | _      | _      | _      | VREFSEL | _       | _     | CVREN | CVR10E | CVRR     | CVRSS |         | CVR<   | 3:0>      |       | 0000          |

| CM1CON                   | 0A84  | CON    | COE    | CPOL   | _      | _      | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | _       | _      | CCH       | <1:0> | 0000          |

| CM1MSKSRC                | 0A86  |        | _      | _      | _      |        | SELSR   | CC<3:0> |       |       | SELSRC | B<3:0>   |       |         | SELSRC | A<3:0>    |       | 0000          |

| CM1MSKCON                | 0A88  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM1FLTR                  | 0A8A  |        | _      | _      | _      | _      | _       | _       | _     | _     | C      | FSEL<2:0 | >     | CFLTREN | (      | CFDIV<2:0 | >     | 0000          |

| CM2CON                   | 0A8C  | CON    | COE    | CPOL   | _      | _      | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | _       | _      | CCH       | <1:0> | 0000          |

| CM2MSKSRC                | 0A8E  |        | _      | _      | _      |        | SELSR   | CC<3:0> |       |       | SELSRC | B<3:0>   |       |         | SELSRC | A<3:0>    |       | 0000          |

| CM2MSKCON                | 0A90  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM2FLTR                  | 0A92  | _      | _      | _      | _      | _      | _       | _       | _     |       | C      | FSEL<2:0 | >     | CFLTREN | (      | CFDIV<2:0 | >     | 0000          |

| CM3CON <sup>(1)</sup>    | 0A94  | CON    | COE    | CPOL   | _      | _      | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | _       | _      | CCH       | <1:0> | 0000          |

| CM3MSKSRC(1)             | 0A96  | _      | _      | _      | _      |        | SELSR   | CC<3:0> |       |       | SELSRC | B<3:0>   |       |         | SELSRC | A<3:0>    |       | 0000          |

| CM3MSKCON <sup>(1)</sup> | 0A98  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM3FLTR <sup>(1)</sup>   | 0A9A  | _      | _      | _      | _      | _      | _       | _       | _     |       | C      | FSEL<2:0 | >     | CFLTREN | (      | CFDIV<2:0 | >     | 0000          |

| CM4CON                   | 0A9C  | CON    | COE    | CPOL   | _      | _      | _       | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF  | _       | _      | CCH       | <1:0> | 0000          |

| CM4MSKSRC                | 0A9E  | _      | _      |        | _      |        | SELSR   | CC<3:0> | -     |       | SELSRC | B<3:0>   | •     |         | SELSRC | A<3:0>    |       | 0000          |

| CM4MSKCON                | 0AA0  | HLMS   | _      | OCEN   | OCNEN  | OBEN   | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM4FLTR                  | 0AA2  | _      | _      |        | _      | _      | _       | _       | _     | —     | C      | FSEL<2:0 | >     | CFLTREN | (      | CFDIV<2:0 | >     | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These registers are unavailable on dsPIC33EPXXXGP502/MC502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

#### TABLE 4-43: CTMU REGISTER MAP

| File N | lame | Addr. | Bit 15  | Bit 14  | Bit 13   | Bit 12 | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------|------|-------|---------|---------|----------|--------|----------|----------|----------|----------|---------|---------|-------|-------|---------|-------|-------|-------|---------------|

| CTMUC  | CON1 | 033A  | CTMUEN  | —       | CTMUSIDL | TGEN   | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | _       | _       | _     | _     | _       | _     | _     | _     | 0000          |

| CTMUC  | CON2 | 033C  | EDG1MOD | EDG1POL |          | EDG1   | SEL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |       | EDG2S | EL<3:0> |       | _     | -     | 0000          |

| CTMU   | ICON | 033E  |         |         | ITRIM<5  | 5:0>   |          |          | IRNG     | <1:0>    |         | _       | _     | _     | _       | _     | -     | _     | 0000          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-44: JTAG INTERFACE REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11       | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------------|--------|-------|-------|-------|--------|---------|-------|-------|-------|-------|-------|---------------|

| JDATAH    | 0FF0 | _      | —      | _      | _      |              |        |       |       |       | JDATAH | <27:16> |       |       |       |       |       | xxxx          |

| JDATAL    | 0FF2 |        |        |        |        | JDATAL<15:0> |        |       |       |       |        |         | 0000  |       |       |       |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 97

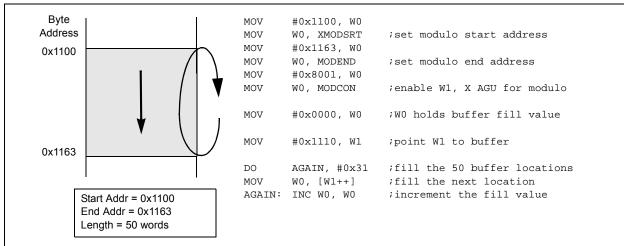

# 4.6 Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

# 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Y space Modulo Addressing EA calcula- |

|-------|---------------------------------------|

|       | tions assume word-sized data (LSb of  |

|       | every EA is always clear).            |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

# FIGURE 4-20: MODULO ADDRESSING OPERATION EXAMPLE

# **REGISTER 8-7:** DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | PAD   | <15:8>            |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | PAE   | )<7:0>            |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

#### bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

### REGISTER 8-8: DMAXCNT: DMA CHANNEL X TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0             | U-0   | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

| —               |       |                  |       | CNT<              | 13:8> <b>(2)</b> |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | CNT<  | <7:0> <b>(2)</b>  |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable b  | oit   | W = Writable b   | bit   | U = Unimplen      | nented bit, rea  | id as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                 | 12. 2007.00    |                                       |              |                   |                  |                 |        |

|-----------------|----------------|---------------------------------------|--------------|-------------------|------------------|-----------------|--------|

| U-0             | U-0            | U-0                                   | U-0          | U-0               | U-0              | U-0             | U-0    |

| —               | —              | —                                     | —            | —                 | —                | —               | —      |

| bit 15          |                |                                       |              |                   |                  |                 | bit 8  |

|                 |                |                                       |              |                   |                  |                 |        |

| U-0             | U-0            | U-0                                   | U-0          | R-0               | R-0              | R-0             | R-0    |

| —               |                | —                                     | —            | RQCOL3            | RQCOL2           | RQCOL1          | RQCOL0 |

| bit 7           |                |                                       |              |                   |                  |                 | bit 0  |

|                 |                |                                       |              |                   |                  |                 |        |

| Legend:         |                |                                       |              |                   |                  |                 |        |

| R = Readable    | bit            | W = Writable                          | bit          | U = Unimpler      | mented bit, read | l as '0'        |        |

| -n = Value at F | POR            | '1' = Bit is set                      |              | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |

|                 |                |                                       |              |                   |                  |                 |        |

| bit 15-4        | Unimplemen     | ted: Read as '                        | כ'           |                   |                  |                 |        |

| bit 3           | RQCOL3: DN     | /IA Channel 3 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |

|                 |                | e and interrupt<br>est collision is d |              | st collision is d | etected          |                 |        |

| <b>h</b> # 0    | •              |                                       |              | est Callisian Fl  | aa hit           |                 |        |

| bit 2           |                | /IA Channel 2 T<br>ce and interrupt   | •            |                   | 0                |                 |        |

|                 |                | e and interrupt<br>est collision is d |              |                   | elecieu          |                 |        |

| bit 1           | RQCOL1: DN     | /IA Channel 1 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |

|                 | 1 = User for   | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

|                 | 0 = No reque   | est collision is d                    | etected      |                   |                  |                 |        |

| bit 0           | RQCOLO: DN     | /IA Channel 0 T                       | ransfer Requ | est Collision F   | lag bit          |                 |        |

|                 | 1 = User force | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

# REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

# REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- $\label{eq:constraint} \textbf{2:} \quad \text{This bit is cleared when the ROI bit is set and an interrupt occurs.}$

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# REGISTER 11-26: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP118 | 3R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

|        |     |       |       |       |         |       |       |

| U-0    | U-0 | U-0   | U-0   | U-0   | U-0     | U-0   | U-0   |

| —      | —   |       | —     | _     | _       | —     | _     |

| bit 7  |     |       |       |       |         |       | bit 0 |

|        |     |       |       |       |         |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP118R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP118 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 11-27: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------------|-------|-------|-------|-------|-------|

| —     | —   | RP120R<5:0> |       |       |       |       |       |

| bit 7 |     |             |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **RP120R<5:0>:** Peripheral Output Function is Assigned to RP120 Output Pin bits (see Table 11-3 for peripheral function numbers)

# 16.3 PWMx Control Registers

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | HS/HC-0 | R/W-0 | R/W-0               | R/W-0                  | R/W-0                  |

|--------|-----|--------|---------|-------|---------------------|------------------------|------------------------|

| PTEN   | —   | PTSIDL | SESTAT  | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15 |     |        |         |       |                     |                        | bit 8                  |

| R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-----------------------|-------------------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|------------------------|

| SYNCEN <sup>(1)</sup> | SYNCSRC2 <sup>(1)</sup> | SYNCSRC1 <sup>(1)</sup> | SYNCSRC0 <sup>(1)</sup> | SEVTPS3 <sup>(1)</sup> | SEVTPS2 <sup>(1)</sup> | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |

| bit 7                 | •                       |                         |                         |                        |                        |                        | bit 0                  |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit |                    |

|-------------------|-----------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re  | ad as '0'          |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15  | PTEN: PWMx Module Enable bit                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = PWMx module is enabled</li> <li>0 = PWMx module is disabled</li> </ul>                                                                     |

| bit 14  | Unimplemented: Read as '0'                                                                                                                              |

| bit 13  | PTSIDL: PWMx Time Base Stop in Idle Mode bit                                                                                                            |

|         | <ul> <li>1 = PWMx time base halts in CPU Idle mode</li> <li>0 = PWMx time base runs in CPU Idle mode</li> </ul>                                         |

| bit 12  | SESTAT: Special Event Interrupt Status bit                                                                                                              |

|         | <ul> <li>1 = Special event interrupt is pending</li> <li>0 = Special event interrupt is not pending</li> </ul>                                          |

| bit 11  | SEIEN: Special Event Interrupt Enable bit                                                                                                               |

|         | 1 = Special event interrupt is enabled                                                                                                                  |

|         | 0 = Special event interrupt is disabled                                                                                                                 |

| bit 10  | EIPU: Enable Immediate Period Updates bit <sup>(1)</sup>                                                                                                |

|         | <ul> <li>1 = Active Period register is updated immediately</li> <li>0 = Active Period register updates occur on PWMx cycle boundaries</li> </ul>        |

| bit 9   | SYNCPOL: Synchronize Input and Output Polarity bit <sup>(1)</sup>                                                                                       |

|         | 1 = SYNCI1/SYNCO1 polarity is inverted (active-low)                                                                                                     |

|         | 0 = SYNCI1/SYNCO1 is active-high                                                                                                                        |

| bit 8   | SYNCOEN: Primary Time Base Sync Enable bit <sup>(1)</sup>                                                                                               |

|         | 1 = SYNCO1 output is enabled                                                                                                                            |

| L:1 7   | 0 = SYNCO1 output is disabled                                                                                                                           |

| bit 7   | SYNCEN: External Time Base Synchronization Enable bit <sup>(1)</sup>                                                                                    |

|         | <ul> <li>1 = External synchronization of primary time base is enabled</li> <li>0 = External synchronization of primary time base is disabled</li> </ul> |

|         |                                                                                                                                                         |

| Note 1: | These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user                                                   |

|         | application must program the period register with a value that is slightly larger than the expected period of                                           |

the external synchronization input signal.

2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

# REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER (CONTINUED)

| bit 2 | <b>HOMIEN:</b> Home Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled            |

|-------|--------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IDXIRQ:</b> Status Flag for Index Event Status bit<br>1 = Index event has occurred<br>0 = No Index event has occurred |

| bit 0 | <b>IDXIEN:</b> Index Input Event Interrupt Enable bit<br>1 = Interrupt is enabled<br>0 = Interrupt is disabled           |

Note 1: This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family offers two SPI modules on a single device. These modules, which are designated as SPI1 and SPI2, are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of the SPI2 module, but results in a lower maximum speed for SPI2. See **Section 30.0** "**Electrical Characteristics**" for more information.

The SPIx serial interface consists of four pins, as follows:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER (CONTINUED)

- PTGITM<1:0>: PTG Input Trigger Command Operating Mode bits<sup>(1)</sup>

- 11 = Single level detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 10 = Single level detect with Step delay executed on exit of command

- 01 = Continuous edge detect with Step delay not executed on exit of command (regardless of the PTGCTRL command)

- 00 = Continuous edge detect with Step delay executed on exit of command

- Note 1: These bits apply to the PTGWHI and PTGWLO commands only.

bit 1-0

- **2:** This bit is only used with the PTGCTRL step command software trigger option.

- **3:** Use of the PTG Single-Step mode is reserved for debugging tools only.

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup> (CONTINUED)

| bit 4 | OC1CS: Clock Source for OC1 bit                                                                                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Generates clock pulse when the broadcast command is executed</li> <li>0 = Does not generate clock pulse when the broadcast command is executed</li> </ul>                         |

| bit 3 | OC4TSS: Trigger/Synchronization Source for OC4 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 2 | OC3TSS: Trigger/Synchronization Source for OC3 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 1 | OC2TSS: Trigger/Synchronization Source for OC2 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 0 | OC1TSS: Trigger/Synchronization Source for OC1 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

|       |                                                                                                                                                                                                |

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: This register is only used with the PTGCTRL OPTION = 1111 Step command.

# REGISTER 24-8: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGC1L | IM<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

|        |       |       |        |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGC1L | IM<7:0>  |       |       |       |

| bit 7  |       |       |        |          |       |       | bit C |

| Legena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGC1LIM<15:0>:** PTG Counter 1 Limit Register bits May be used to specify the loop count for the PTGJMPC1 Step command or as a limit register for the General Purpose Counter 1.

# REGISTER 24-9: PTGHOLD: PTG HOLD REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|--------|---------------|-------|-------|-------|-------|-------|-------|--|

|        | PTGHOLD<15:8> |       |       |       |       |       |       |  |

| bit 15 |               |       |       |       |       |       | bit 8 |  |

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------------|-------|-------|-------|-------|-------|-------|-------|

| PTGHOLD<7:0> |       |       |       |       |       |       |       |

| bit 7 bit    |       |       |       |       |       | bit 0 |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGHOLD<15:0>:** PTG General Purpose Hold Register bits Holds user-supplied data to be copied to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGCOPY command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| TABLE 30-23: TIME | 1 EXTERNAL CLOCK TIMING REQUI | REMENTS <sup>(1)</sup> |

|-------------------|-------------------------------|------------------------|

|-------------------|-------------------------------|------------------------|

| AC CHARACTERISTICS |           |                                                                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                                        |      |               |       |                                                                             |

|--------------------|-----------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------|---------------|-------|-----------------------------------------------------------------------------|

| Param<br>No.       | Symbol    | Characteristic <sup>(2)</sup>                                                                      |                                                                                                                                                                                                                                                                                         | Min.                                   | Тур. | Max.          | Units | Conditions                                                                  |

| TA10               | ТтхН      | T1CK High<br>Time                                                                                  | Synchronous<br>mode                                                                                                                                                                                                                                                                     | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |

|                    |           |                                                                                                    | Asynchronous                                                                                                                                                                                                                                                                            | 35                                     | _    | —             | ns    |                                                                             |

| TA11               | ΤτχL      | T1CK Low<br>Time                                                                                   | Synchronous<br>mode                                                                                                                                                                                                                                                                     | Greater of:<br>20 or<br>(Tcy + 20)/N   |      | _             | ns    | Must also meet<br>Parameter TA15,<br>N = prescaler value<br>(1, 8, 64, 256) |

|                    |           |                                                                                                    | Asynchronous                                                                                                                                                                                                                                                                            | 10                                     | _    | _             | ns    |                                                                             |

| TA15               | ΤτχΡ      | T1CK Input<br>Period                                                                               | Synchronous mode                                                                                                                                                                                                                                                                        | Greater of:<br>40 or<br>(2 Tcy + 40)/N | _    | _             | ns    | N = prescale value<br>(1, 8, 64, 256)                                       |

| OS60               | Ft1       | T1CK Oscillator Input<br>Frequency Range (oscillator<br>enabled by setting bit, TCS<br>(T1CON<1>)) |                                                                                                                                                                                                                                                                                         | DC                                     |      | 50            | kHz   |                                                                             |

| TA20               | TCKEXTMRL | Delay from External T1CK<br>Clock Edge to Timer<br>Increment                                       |                                                                                                                                                                                                                                                                                         | 0.75 Tcy + 40                          | —    | 1.75 Tcy + 40 | ns    |                                                                             |

**Note 1:** Timer1 is a Type A.

2: These parameters are characterized, but are not tested in manufacturing.

### FIGURE 30-29: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

# 33.0 PACKAGING INFORMATION

# 33.1 Package Marking Information

# 28-Lead SPDIP

#### 28-Lead SOIC (.300")

28-Lead SSOP

Example dsPIC33EP64GP 502-I/SP@3 1310017

# Example

### Example

28-Lead QFN-S (6x6x0.9 mm)

Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | be carried                               | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>of or customer-specific information.                                                                                                                                                                                              |

# **Revision F (November 2012)**

Removed "Preliminary" from data sheet footer.

# **Revision G (March 2013)**

This revision includes the following global changes:

- changes "FLTx" pin function to "FLTx" on all occurrences

- adds Section 31.0 "High-Temperature Electrical Characteristics" for high-temperature (+150°C) data

This revision also includes minor typographical and formatting changes throughout the text.

Other major changes are referenced by their respective section in Table A-5.

| Section Name                                                         | Update Description                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cover Section                                                        | <ul> <li>Changes internal oscillator specification to 1.0%</li> <li>Changes I/O sink/source values to 12 mA or 6 mA</li> <li>Corrects 44-pin VTLA pin diagram (pin 32 now shows as 5V tolerant)</li> </ul>                                                                                                                                                                           |

| Section 4.0 "Memory<br>Organization"                                 | <ul> <li>Deletes references to Configuration Shadow registers</li> <li>Corrects the spelling of the JTAGIP and PTGWDTIP bits throughout</li> <li>Corrects the Reset value of all IOCON registers as C000h</li> <li>Adds footnote to Table 4-42 to indicate the absence of Comparator 3 in 28-pin devices</li> </ul>                                                                  |

| Section 6.0 "Resets"                                                 | <ul> <li>Removes references to cold and warm Resets, and clarifies the initial configuration of<br/>the device clock source on all Resets</li> </ul>                                                                                                                                                                                                                                 |

| Section 7.0 "Interrupt<br>Controller"                                | Corrects the definition of GIE as "Global Interrupt Enable" (not "General")                                                                                                                                                                                                                                                                                                          |

| Section 9.0 "Oscillator<br>Configuration"                            | <ul> <li>Clarifies the behavior of the CF bit when cleared in software</li> <li>Removes POR behavior footnotes from all control registers</li> <li>Corrects the tuning range of the TUN&lt;5:0&gt; bits in Register 9-4 to an overall range ±1.5%</li> </ul>                                                                                                                         |

| Section 13.0 "Timer2/3 and Timer4/5"                                 | <ul> <li>Clarifies the presence of the ADC Trigger in 16-bit Timer3 and Timer5, as well as the<br/>32-bit timers</li> </ul>                                                                                                                                                                                                                                                          |

| Section 15.0 "Output<br>Compare"                                     | <ul> <li>Corrects the first trigger source for SYNCSEL&lt;4:0&gt; (OCxCON2&lt;4:0&gt;) as OCxRS<br/>match</li> </ul>                                                                                                                                                                                                                                                                 |

| Section 16.0 "High-Speed<br>PWM Module"                              | <ul> <li>Clarifies the source of the PWM interrupts in Figure 16-1</li> <li>Corrects the Reset states of IOCONx&lt;15:14&gt; in Register 16-13 as '11'</li> </ul>                                                                                                                                                                                                                    |

| Section 17.0 "Quadrature<br>Encoder Interface (QEI)<br>Module"       | <ul> <li>Clarifies the operation of the IMV&lt;1:0&gt; bits (QEICON&lt;9:8&gt;) with updated text and additional notes</li> <li>Corrects the first prescaler value for QFVDIV&lt;2:0&gt; (QEI10C&lt;13:11&gt;), now 1:128</li> </ul>                                                                                                                                                 |

| Section 23.0 "10-Bit/12-Bit<br>Analog-to-Digital Converter<br>(ADC)" | <ul> <li>Adds note to Figure 23-1 that Op Amp 3 is not available in 28-pin devices</li> <li>Changes "sample clock" to "sample trigger" in AD1CON1 (Register 23-1)</li> <li>Clarifies footnotes on op amp usage in Registers 23-5 and 23-6</li> </ul>                                                                                                                                 |

| Section 25.0 "Op Amp/<br>Comparator Module"                          | <ul> <li>Adds Note text to indicate that Comparator 3 is unavailable in 28-pin devices</li> <li>Splits Figure 25-1 into two figures for clearer presentation (Figure 25-1 for Op amp/<br/>Comparators 1 through 3, Figure 25-2 for Comparator 4). Subsequent figures are<br/>renumbered accordingly.</li> <li>Corrects reference description in xxxxx (now (AVDD+AVSS)/2)</li> </ul> |

| Section 27.0 "Special<br>Features"                                   | <ul> <li>Changes CMSTAT&lt;15&gt; in Register 25-1 to "PSIDL"</li> <li>Corrects the addresses of all Configuration bytes for 512 Kbyte devices</li> </ul>                                                                                                                                                                                                                            |

### TABLE A-5: MAJOR SECTION UPDATES

# Revision H (August 2013)

This revision includes minor typographical and formatting changes throughout the text.

Other major changes are referenced by their respective section in Table A-6.

| Section Name                                                         | Update Description                                                                                                                                      |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cover Section                                                        | <ul> <li>Adds Peripheral Pin Select (PPS) to allow Digital Function Remapping and Change<br/>Notification Interrupts to Input/Output section</li> </ul> |

|                                                                      | Adds heading information to 64-Pin TQFP                                                                                                                 |

| Section 4.0 "Memory                                                  | Corrects Reset values for ANSELE, TRISF, TRISC, ANSELC and TRISA                                                                                        |

| Organization"                                                        | <ul> <li>Corrects address range from 0x2FFF to 0x7FFF</li> </ul>                                                                                        |

|                                                                      | Corrects DSRPAG and DSWPAG (now 3 hex digits)                                                                                                           |

|                                                                      | Changes Call Stack Frame from <15:1> to PC<15:0>                                                                                                        |

|                                                                      | Word length in Figure 4-20 is changed to 50 words for clarity                                                                                           |

| Section 5.0 "Flash Program                                           | Corrects descriptions of NVM registers                                                                                                                  |

| Memory"                                                              |                                                                                                                                                         |

| Section 9.0 "Oscillator                                              | Removes resistor from Figure 9-1                                                                                                                        |

| Configuration"                                                       | Adds Fast RC Oscillator with Divide-by-16 (FRCDIV16) row to Table 9-1                                                                                   |

|                                                                      | Removes incorrect information from ROI bit in Register 9-2                                                                                              |

| Section 14.0 "Input Capture"                                         | Changes 31 user-selectable Trigger/Sync interrupts to 19 user-selectable Trigger/<br>Sync interrupts                                                    |

|                                                                      | Corrects ICTSEL<12:10> bits (now ICTSEL<2:0>)                                                                                                           |

| Section 17.0 "Quadrature<br>Encoder Interface (QEI)                  | Corrects QCAPEN bit description                                                                                                                         |

| Module                                                               |                                                                                                                                                         |

| (dsPIC33EPXXXMC20X/50X                                               |                                                                                                                                                         |

| and PIC24EPXXXMC20X<br>Devices Only)"                                |                                                                                                                                                         |

| Section 19.0 "Inter-                                                 | Adds note to clarify that 100kbit/sec operation of I <sup>2</sup> C is not possible at high processor                                                   |

| Integrated Circuit™ (I <sup>2</sup> C™)"                             | speeds                                                                                                                                                  |

| Section 22.0 "Charge Time<br>Measurement Unit (CTMU)"                | Clarifies Figure 22-1 to accurately reflect peripheral behavior                                                                                         |

| Section 23.0 "10-Bit/12-Bit<br>Analog-to-Digital Converter<br>(ADC)" | Correct Figure 23-1 (changes CH123x to CH123Sx)                                                                                                         |

| Section 24.0 "Peripheral<br>Trigger Generator (PTG)<br>Module"       | <ul> <li>Adds footnote to Register 24-1 (In order to operate with CVRSS=1, at least one of the<br/>comparator modules must be enabled.</li> </ul>       |

| Section 25.0 "Op Amp/<br>Comparator Module"                          | Adds note to Figure 25-3 (In order to operate with CVRSS=1, at least one of the comparator modules must be enabled)                                     |

|                                                                      | <ul> <li>Adds footnote to Register 25-2 (COE is not available when OPMODE<br/>(CMxCON&lt;10&gt;) = 1)</li> </ul>                                        |

| Section 27.0 "Special<br>Features"                                   | Corrects the bit description for FNOSC<2:0>                                                                                                             |

| Section 30.0 "Electrical                                             | Corrects 512K part power-down currents based on test data                                                                                               |

| Characteristics"                                                     | Corrects WDT timing limits based on LPRC oscillator tolerance                                                                                           |

| Section 31.0 "High-<br>Temperature Electrical<br>Characteristics"    | Adds Table 31-5 (DC Characteristics: Idle Current (IIDLE)                                                                                               |

| Unarautenstics                                                       |                                                                                                                                                         |