#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                               |

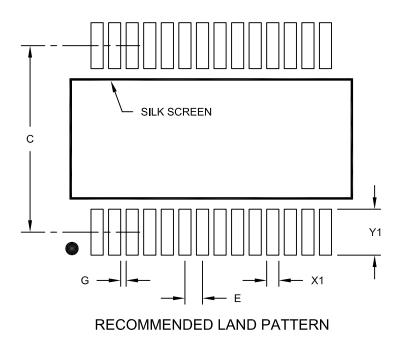

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc502-h-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

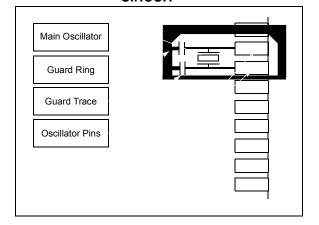

## 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

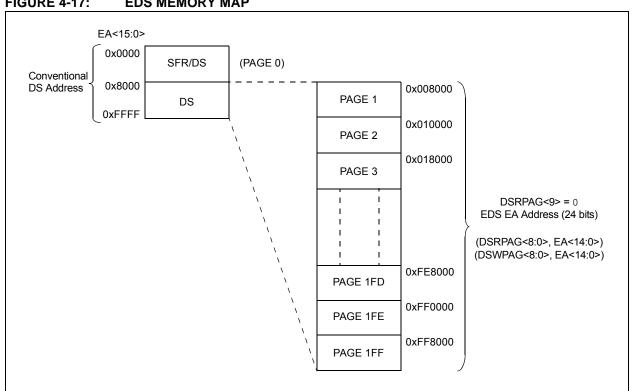

#### 4.4.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-17.

For more information on the PSV page access using Data Space Page registers, refer to the "**Program Space Visibility from Data Space**" section in "**Program Memory**" (DS70613) of the "*dsPIC33/ PIC24 Family Reference Manual*".

#### FIGURE 4-17: EDS MEMORY MAP

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0         | R/W-0                                     | U-0                                                                                                            | U-0           | R/W-0                 | U-0               | R/W-0            | R/W-0         |  |  |  |  |

|---------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------|-----------------------|-------------------|------------------|---------------|--|--|--|--|

| TRAPF         | R IOPUWR                                  | —                                                                                                              | _             | VREGSF                | —                 | CM               | VREGS         |  |  |  |  |

| bit 15        |                                           |                                                                                                                |               |                       |                   |                  | bit 8         |  |  |  |  |

|               |                                           | DANIO                                                                                                          | DAA/ O        | DAMA                  | DAMO              |                  |               |  |  |  |  |

| R/W-0         |                                           | R/W-0                                                                                                          | R/W-0         | R/W-0                 | R/W-0             | R/W-1            | R/W-1         |  |  |  |  |

| EXTR<br>bit 7 | SWR                                       | SWDTEN <sup>(2)</sup>                                                                                          | WDTO          | SLEEP                 | IDLE              | BOR              | POR           |  |  |  |  |

|               |                                           |                                                                                                                |               |                       |                   |                  | bit (         |  |  |  |  |

| Legend:       |                                           |                                                                                                                |               |                       |                   |                  |               |  |  |  |  |

| R = Reada     | able bit                                  | W = Writable I                                                                                                 | oit           | U = Unimpler          | mented bit, read  | d as '0'         |               |  |  |  |  |

| -n = Value    | at POR                                    | '1' = Bit is set                                                                                               |               | '0' = Bit is cle      | ared              | x = Bit is unkı  | nown          |  |  |  |  |

|               |                                           |                                                                                                                |               |                       |                   |                  |               |  |  |  |  |

| bit 15        | •                                         | Reset Flag bit                                                                                                 |               |                       |                   |                  |               |  |  |  |  |

|               |                                           | onflict Reset ha<br>onflict Reset ha                                                                           |               | d                     |                   |                  |               |  |  |  |  |

| bit 14        | •                                         | gal Opcode or                                                                                                  |               |                       | et Flag bit       |                  |               |  |  |  |  |

|               |                                           | I opcode detec                                                                                                 |               |                       | •                 | lized W registe  | er used as ar |  |  |  |  |

|               |                                           | Pointer caused                                                                                                 |               |                       |                   |                  |               |  |  |  |  |

|               | -                                         | l opcode or Uni                                                                                                |               | egister Reset h       | as not occurred   | d                |               |  |  |  |  |

| bit 13-12     | -                                         | ted: Read as '                                                                                                 |               |                       | . 1.9             |                  |               |  |  |  |  |

| bit 11        |                                           | VREGSF: Flash Voltage Regulator Standby During Sleep bit<br>1 = Flash voltage regulator is active during Sleep |               |                       |                   |                  |               |  |  |  |  |

|               |                                           | ltage regulator (                                                                                              |               | •                     | ing Sleep         |                  |               |  |  |  |  |

| bit 10        |                                           | ted: Read as '                                                                                                 | -             | ,,                    | 5                 |                  |               |  |  |  |  |

| bit 9         | CM: Configur                              | ation Mismatch                                                                                                 | Flag bit      |                       |                   |                  |               |  |  |  |  |

|               | 1 = A Configu                             | uration Mismatc<br>uration Mismatc                                                                             | h Reset has   |                       |                   |                  |               |  |  |  |  |

| bit 8         | VREGS: Volta                              | VREGS: Voltage Regulator Standby During Sleep bit                                                              |               |                       |                   |                  |               |  |  |  |  |

|               | •                                         | egulator is active<br>egulator goes in                                                                         | •             | •                     | еер               |                  |               |  |  |  |  |

| bit 7         | EXTR: Extern                              | EXTR: External Reset (MCLR) Pin bit                                                                            |               |                       |                   |                  |               |  |  |  |  |

|               |                                           | Clear (pin) Res<br>Clear (pin) Res                                                                             |               |                       |                   |                  |               |  |  |  |  |

| bit 6         | SWR: Softwa                               | SWR: Software RESET (Instruction) Flag bit                                                                     |               |                       |                   |                  |               |  |  |  |  |

|               |                                           | instruction has instruction has                                                                                |               |                       |                   |                  |               |  |  |  |  |

| bit 5         | SWDTEN: So                                | oftware Enable/                                                                                                | Disable of W  | DT bit <sup>(2)</sup> |                   |                  |               |  |  |  |  |

|               | 1 = WDT is e<br>0 = WDT is di             |                                                                                                                |               |                       |                   |                  |               |  |  |  |  |

| bit 4         | WDTO: Watc                                | hdog Timer Tim                                                                                                 | e-out Flag bi | it                    |                   |                  |               |  |  |  |  |

|               |                                           | e-out has occur<br>e-out has not oc                                                                            |               |                       |                   |                  |               |  |  |  |  |

| Note 1:       | All of the Reset sta<br>cause a device Re |                                                                                                                | set or cleare | d in software. S      | Setting one of th | ese bits in soft | ware does not |  |  |  |  |

| 2:            | If the FWDTEN Co<br>SWDTEN bit settir     | onfiguration bit i                                                                                             | s '1' (unprog | rammed), the V        | VDT is always e   | enabled, regard  | lless of the  |  |  |  |  |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| U-0             | U-0                                                                                                                                                                                                                                                                                                                                                                                 | U-0              | U-0     | R-0               | R-0              | R-0             | R-0     |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------|-------------------|------------------|-----------------|---------|--|--|--|--|

|                 | —                                                                                                                                                                                                                                                                                                                                                                                   |                  |         | ILR3              | ILR2             | ILR1            | ILR0    |  |  |  |  |

| bit 15          |                                                                                                                                                                                                                                                                                                                                                                                     |                  |         |                   |                  |                 | bit 8   |  |  |  |  |

| R-0             | R-0                                                                                                                                                                                                                                                                                                                                                                                 | R-0              | R-0     | R-0               | R-0              | R-0             | R-0     |  |  |  |  |

| VECNUM7         | VECNUM6                                                                                                                                                                                                                                                                                                                                                                             | VECNUM5          | VECNUM4 | VECNUM3           | VECNUM2          | VECNUM1         | VECNUM0 |  |  |  |  |

| bit 7           |                                                                                                                                                                                                                                                                                                                                                                                     |                  |         |                   |                  |                 | bit C   |  |  |  |  |

| Legend:         |                                                                                                                                                                                                                                                                                                                                                                                     |                  |         |                   |                  |                 |         |  |  |  |  |

| R = Readable    | bit                                                                                                                                                                                                                                                                                                                                                                                 | W = Writable     | bit     | U = Unimplen      | nented bit, read | as '0'          |         |  |  |  |  |

| -n = Value at I | POR                                                                                                                                                                                                                                                                                                                                                                                 | '1' = Bit is set |         | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |  |  |  |  |

| bit 15-12       | Unimplemen                                                                                                                                                                                                                                                                                                                                                                          | ted: Read as '   | 0'      |                   |                  |                 |         |  |  |  |  |

| bit 11-8        | ILR<3:0>: New CPU Interrupt Priority Level bits                                                                                                                                                                                                                                                                                                                                     |                  |         |                   |                  |                 |         |  |  |  |  |

|                 | 1111 = CPU Interrupt Priority Level is 15                                                                                                                                                                                                                                                                                                                                           |                  |         |                   |                  |                 |         |  |  |  |  |

|                 | •                                                                                                                                                                                                                                                                                                                                                                                   |                  |         |                   |                  |                 |         |  |  |  |  |

|                 | •                                                                                                                                                                                                                                                                                                                                                                                   |                  |         |                   |                  |                 |         |  |  |  |  |

|                 | 0001 = CPU Interrupt Priority Level is 1<br>0000 = CPU Interrupt Priority Level is 0                                                                                                                                                                                                                                                                                                |                  |         |                   |                  |                 |         |  |  |  |  |

| bit 7-0         | VECNUM<7:0>: Vector Number of Pending Interrupt bits                                                                                                                                                                                                                                                                                                                                |                  |         |                   |                  |                 |         |  |  |  |  |

|                 | 11111111 = 255, Reserved; do not use                                                                                                                                                                                                                                                                                                                                                |                  |         |                   |                  |                 |         |  |  |  |  |

|                 | •                                                                                                                                                                                                                                                                                                                                                                                   |                  |         |                   |                  |                 |         |  |  |  |  |

|                 | •                                                                                                                                                                                                                                                                                                                                                                                   |                  |         |                   |                  |                 |         |  |  |  |  |

|                 | •<br>00001001 = 9, IC1 – Input Capture 1<br>00001000 = 8, INT0 – External Interrupt 0<br>00000111 = 7, Reserved; do not use<br>00000110 = 6, Generic soft error trap<br>00000101 = 5, DMAC error trap<br>00000100 = 4, Math error trap<br>00000011 = 3, Stack error trap<br>00000011 = 2, Generic hard trap<br>00000010 = 1, Address error trap<br>00000001 = 1, Address error trap |                  |         |                   |                  |                 |         |  |  |  |  |

## REGISTER 7-7: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

| R/W-0                 | R/W-0                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                            | R/W-0                          | R/W-0            | U-0             | U-0             | U-0   |  |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------|-----------------|-----------------|-------|--|--|--|--|

| CHEN                  | SIZE                                                                                                                                       | DIR                                                                                                                                                                                                                                                                              | HALF                           | NULLW            |                 |                 |       |  |  |  |  |

| bit 15                |                                                                                                                                            |                                                                                                                                                                                                                                                                                  |                                |                  |                 |                 | bit   |  |  |  |  |

| U-0                   | U-0                                                                                                                                        | R/W-0                                                                                                                                                                                                                                                                            | R/W-0                          | U-0              | U-0             | R/W-0           | R/W-0 |  |  |  |  |

|                       | 0-0                                                                                                                                        | AMODE1                                                                                                                                                                                                                                                                           | AMODE0                         | 0-0              | 0-0             | MODE1           | MODE0 |  |  |  |  |

| bit 7                 |                                                                                                                                            | AWODET                                                                                                                                                                                                                                                                           | 7 WIODE0                       |                  |                 | MODET           | bit   |  |  |  |  |

| Lovende               |                                                                                                                                            |                                                                                                                                                                                                                                                                                  |                                |                  |                 |                 |       |  |  |  |  |

| Legend:<br>R = Readab | lo hit                                                                                                                                     | M - Mritabla                                                                                                                                                                                                                                                                     | hit.                           |                  | monted bit rec  | ud aa '0'       |       |  |  |  |  |

|                       |                                                                                                                                            | W = Writable                                                                                                                                                                                                                                                                     |                                | -                | mented bit, rea |                 |       |  |  |  |  |

| -n = Value a          | IT POR                                                                                                                                     | '1' = Bit is set                                                                                                                                                                                                                                                                 |                                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |  |  |  |

| bit 15                | CHEN: DMA                                                                                                                                  | Channel Enabl                                                                                                                                                                                                                                                                    | e bit                          |                  |                 |                 |       |  |  |  |  |

|                       | 1 = Channel                                                                                                                                |                                                                                                                                                                                                                                                                                  |                                |                  |                 |                 |       |  |  |  |  |

| bit 14                | <ul> <li>0 = Channel is disabled</li> <li>SIZE: DMA Data Transfer Size bit</li> </ul>                                                      |                                                                                                                                                                                                                                                                                  |                                |                  |                 |                 |       |  |  |  |  |

|                       | 1 = Byte                                                                                                                                   |                                                                                                                                                                                                                                                                                  |                                |                  |                 |                 |       |  |  |  |  |

|                       | 0 = Word                                                                                                                                   |                                                                                                                                                                                                                                                                                  |                                |                  |                 |                 |       |  |  |  |  |

| bit 13                | DIR: DMA Transfer Direction bit (source/destination bus select)                                                                            |                                                                                                                                                                                                                                                                                  |                                |                  |                 |                 |       |  |  |  |  |

|                       |                                                                                                                                            | om RAM addre<br>om peripheral a                                                                                                                                                                                                                                                  |                                |                  |                 |                 |       |  |  |  |  |

| bit 12                | <ul> <li>0 = Reads from peripheral address, writes to RAM address</li> <li>HALF: DMA Block Transfer Interrupt Select bit</li> </ul>        |                                                                                                                                                                                                                                                                                  |                                |                  |                 |                 |       |  |  |  |  |

|                       | 1 = Initiates i                                                                                                                            | nterrupt when                                                                                                                                                                                                                                                                    | half of the data               | a has been mo    |                 |                 |       |  |  |  |  |

| bit 11                | <ul> <li>0 = Initiates interrupt when all of the data has been moved</li> <li>NULLW: Null Data Peripheral Write Mode Select bit</li> </ul> |                                                                                                                                                                                                                                                                                  |                                |                  |                 |                 |       |  |  |  |  |

|                       |                                                                                                                                            | write to periph                                                                                                                                                                                                                                                                  |                                |                  | e (DIR bit must | also be clear)  |       |  |  |  |  |

| bit 10-6              | Unimplemen                                                                                                                                 | ted: Read as '                                                                                                                                                                                                                                                                   | 0'                             |                  |                 |                 |       |  |  |  |  |

| bit 5-4               | AMODE<1:0                                                                                                                                  | -: DMA Chann                                                                                                                                                                                                                                                                     | el Addressing                  | Mode Select b    | oits            |                 |       |  |  |  |  |

|                       | 11 = Reserve<br>10 = Periphe<br>01 = Register                                                                                              |                                                                                                                                                                                                                                                                                  | ressing mode<br>ut Post-Increm | nent mode        |                 |                 |       |  |  |  |  |

| bit 3-2               | Unimplemen                                                                                                                                 | ted: Read as '                                                                                                                                                                                                                                                                   | 0'                             |                  |                 |                 |       |  |  |  |  |

| bit 1-0               | -                                                                                                                                          |                                                                                                                                                                                                                                                                                  |                                | de Select bits   |                 |                 |       |  |  |  |  |

|                       | 11 = One-Sho<br>10 = Continuo<br>01 = One-Sho                                                                                              | MODE<1:0>: DMA Channel Operating Mode Select bits 11 = One-Shot, Ping-Pong modes are enabled (one block transfer from/to each DMA buffer) 10 = Continuous, Ping-Pong modes are enabled 01 = One-Shot, Ping-Pong modes are disabled 00 = Continuous, Ping-Pong modes are disabled |                                |                  |                 |                 |       |  |  |  |  |

## REGISTER 8-1: DMAXCON: DMA CHANNEL X CONTROL REGISTER

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|--------------|----------------------------------------------------------|---------------|-------------------|-----------------|-----------------|-------|

| —            |              |                                                          |               | IC4R<6:0>         |                 |                 |       |

| bit 15       |              |                                                          |               |                   |                 |                 | bit 8 |

|              |              |                                                          |               |                   |                 |                 |       |

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |              |                                                          |               | IC3R<6:0>         |                 |                 |       |

| bit 7        |              |                                                          |               |                   |                 |                 | bit C |

|              |              |                                                          |               |                   |                 |                 |       |

| Legend:      |              |                                                          |               |                   |                 |                 |       |

| R = Readab   | ole bit      | W = Writable I                                           | bit           | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value a | at POR       | '1' = Bit is set                                         |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 0000001 =    | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss | ⊃1            |                   |                 |                 |       |

| bit 7        | Unimpleme    | nted: Read as 'o                                         | )'            |                   |                 |                 |       |

| bit 6-0      | (see Table 1 | Assign Input Ca<br>1-2 for input pin<br>nput tied to RPI | selection nun |                   | onding RPn Pi   | n bits          |       |

## REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

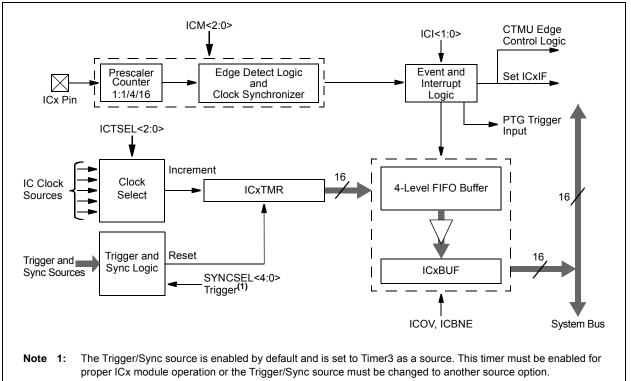

# 14.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70352) in the "dsPIC33/dsPIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices support four input capture channels.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 19 user-selectable Trigger/Sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to six clock sources available for each module, driving a separate internal 16-bit counter

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

|                                                                                                          | lled low externally in order to clear and disable the fault<br>egister requires unlock sequence                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0x0000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |

| -                                                                                                        | d polarity using the IOCON1 register<br>gister requires unlock sequence                                                                                                                                                                                                                           |

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0xF000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |

## REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup> bit 4-2 111 = Secondary prescale 1:1 110 = Secondary prescale 2:1 000 = Secondary prescale 8:1 bit 1-0 PPRE<1:0>: Primary Prescale bits (Master mode)<sup>(3)</sup> 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both primary and secondary prescalers to the value of 1:1.

# 19.1 I<sup>2</sup>C Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this UDL increases |

|-------|---------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                                               |

|       | http://www.microchip.com/wwwproducts/                                                                   |

|       | Devices.aspx?dDocName=en555464                                                                          |

## 19.1.1 KEY RESOURCES

- "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that a Start (or Repeated Start) bit has been detected last                                |

|       | 0 = Start bit was not detected last                                                                      |

|       | Hardware is set or clear when a Start, Repeated Start or Stop is detected.                               |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                        |

|       | 1 = Read – Indicates data transfer is output from the slave                                              |

|       | 0 = Write – Indicates data transfer is input to the slave                                                |

|       | Hardware is set or clear after reception of an I <sup>2</sup> C device address byte.                     |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                      |

|       | 1 = Receive is complete, I2CxRCV is full                                                                 |

|       | 0 = Receive is not complete, I2CxRCV is empty                                                            |

|       | Hardware is set when I2CxRCV is written with a received byte. Hardware is clear when software reads      |

|       | I2CxRCV.                                                                                                 |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                     |

|       | 1 = Transmit in progress, I2CxTRN is full                                                                |

|       | 0 = Transmit is complete, I2CxTRN is empty                                                               |

|       | Hardware is set when software writes to I2CxTRN. Hardware is clear at completion of a data transmission. |

| R/W-0         | R/W-0                                                                                                                            | R/W-0                                                                                                              | R/W-0        | R/W-0             | R/W-0           | R/W-0           | R/W-0    |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------|-------------------|-----------------|-----------------|----------|--|--|--|--|

| EDG1MOD       | EDG1POL                                                                                                                          | EDG1SEL3                                                                                                           | EDG1SEL2     | EDG1SEL1          | EDG1SEL0        | EDG2STAT        | EDG1STAT |  |  |  |  |

| bit 15        |                                                                                                                                  | 1                                                                                                                  |              | 11                |                 |                 | bit 8    |  |  |  |  |

|               |                                                                                                                                  |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                            | R/W-0                                                                                                              | R/W-0        | R/W-0             | R/W-0           | U-0             | U-0      |  |  |  |  |

| EDG2MOD       | EDG2POL                                                                                                                          | EDG2SEL3                                                                                                           | EDG2SEL2     | EDG2SEL1          | EDG2SEL0        | —               | _        |  |  |  |  |

| bit 7         |                                                                                                                                  |                                                                                                                    |              | 1 1               |                 | 1               | bit (    |  |  |  |  |

|               |                                                                                                                                  |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

| Legend:       |                                                                                                                                  |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

| R = Readabl   | le bit                                                                                                                           | W = Writable                                                                                                       | oit          | U = Unimplem      | ented bit, read | l as '0'        |          |  |  |  |  |

| -n = Value at | POR                                                                                                                              | '1' = Bit is set                                                                                                   |              | '0' = Bit is clea | red             | x = Bit is unkr | nown     |  |  |  |  |

|               |                                                                                                                                  |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

| bit 15        | EDG1MOD: E                                                                                                                       | Edge 1 Edge Sa                                                                                                     | ampling Mode | Selection bit     |                 |                 |          |  |  |  |  |

|               | 1 = Edge 1 is                                                                                                                    | s edge-sensitive                                                                                                   | 9            |                   |                 |                 |          |  |  |  |  |

|               | •                                                                                                                                | s level-sensitive                                                                                                  |              |                   |                 |                 |          |  |  |  |  |

| bit 14        |                                                                                                                                  | dge 1 Polarity                                                                                                     |              |                   |                 |                 |          |  |  |  |  |

|               |                                                                                                                                  | 1 = Edge 1 is programmed for a positive edge response                                                              |              |                   |                 |                 |          |  |  |  |  |

| L:1 40 40     | •                                                                                                                                | 0 = Edge 1 is programmed for a negative edge response                                                              |              |                   |                 |                 |          |  |  |  |  |

| bit 13-10     | EDG1SEL<3:0>: Edge 1 Source Select bits                                                                                          |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

|               | 1xxx = Reserved<br>01xx = Reserved                                                                                               |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

|               | 0011 = CTED1 pin                                                                                                                 |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

|               | 0010 = CTED2 pin                                                                                                                 |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

|               | 0001 = OC1 module<br>0000 = Timer1 module                                                                                        |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

| hit O         |                                                                                                                                  |                                                                                                                    | :+           |                   |                 |                 |          |  |  |  |  |

| bit 9         |                                                                                                                                  | <b>DG2STAT:</b> Edge 2 Status bit<br>indicates the status of Edge 2 and can be written to control the edge source. |              |                   |                 |                 |          |  |  |  |  |

|               | 1 = Edge 2 has occurred                                                                                                          |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

|               | 0 = Edge 2 has not occurred                                                                                                      |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

| bit 8         | EDG1STAT: E                                                                                                                      | EDG1STAT: Edge 1 Status bit                                                                                        |              |                   |                 |                 |          |  |  |  |  |

|               | Indicates the status of Edge 1 and can be written to control the edge source.                                                    |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

|               | 1 = Edge 1 has occurred<br>0 = Edge 1 has not occurred                                                                           |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

|               | -                                                                                                                                |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

| bit 7         | EDG2MOD: Edge 2 Edge Sampling Mode Selection bit                                                                                 |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

|               | <ul> <li>1 = Edge 2 is edge-sensitive</li> <li>0 = Edge 2 is level-sensitive</li> </ul>                                          |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

| bit 6         | •                                                                                                                                | dge 2 Polarity                                                                                                     |              |                   |                 |                 |          |  |  |  |  |

| Sit 0         |                                                                                                                                  | •                                                                                                                  |              | dae response      |                 |                 |          |  |  |  |  |

|               | <ol> <li>Edge 2 is programmed for a positive edge response</li> <li>Edge 2 is programmed for a negative edge response</li> </ol> |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

| bit 5-2       | EDG2SEL<3                                                                                                                        | EDG2SEL<3:0>: Edge 2 Source Select bits                                                                            |              |                   |                 |                 |          |  |  |  |  |

|               | 1111 <b>= Rese</b>                                                                                                               | rved                                                                                                               |              |                   |                 |                 |          |  |  |  |  |

|               | 01xx = Rese                                                                                                                      |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

|               | 0100 = CMP <sup>2</sup><br>0011 = CTEE                                                                                           |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

|               |                                                                                                                                  |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

|               | 0010 = CTED1 pin                                                                                                                 |                                                                                                                    |              |                   |                 |                 |          |  |  |  |  |

|               | 0001 = OC1                                                                                                                       | module                                                                                                             |              |                   |                 |                 |          |  |  |  |  |

|               |                                                                                                                                  | module                                                                                                             |              |                   |                 |                 |          |  |  |  |  |

## REGISTER 22-2: CTMUCON2: CTMU CONTROL REGISTER 2

# 24.0 PERIPHERAL TRIGGER GENERATOR (PTG) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Peripheral Trigger Generator (PTG)" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 24.1 Module Introduction

The Peripheral Trigger Generator (PTG) provides a means to schedule complex high-speed peripheral operations that would be difficult to achieve using software. The PTG module uses 8-bit commands, called "Steps", that the user writes to the PTG Queue registers (PTGQUE0-PTGQUE7), which perform operations, such as wait for input signal, generate output trigger and wait for timer.

The PTG module has the following major features:

- Multiple clock sources

- Two 16-bit general purpose timers

- Two 16-bit general limit counters

- Configurable for rising or falling edge triggering

- Generates processor interrupts to include:

- Four configurable processor interrupts

- Interrupt on a Step event in Single-Step modeInterrupt on a PTG Watchdog Timer time-out

- Able to receive trigger signals from these peripherals:

- ADC

- PWM

- Output Compare

- Input Capture

- Op Amp/Comparator

- INT2

- Able to trigger or synchronize to these peripherals:

- Watchdog Timer

- Output Compare

- Input Capture

- ADC

- PWM

- Op Amp/Comparator

| REGISTER 25-5: | CMxMSKCON: COMPARATOR x MASK GATING |

|----------------|-------------------------------------|

|                | CONTROL REGISTER                    |

| R/W-0                                                                                                                |                                                                                                                |                                                                                        |                                                                          |                  |                   |                   |              |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------|-------------------|-------------------|--------------|--|--|--|--|

|                                                                                                                      | U-0                                                                                                            | R/W-0                                                                                  | R/W-0                                                                    | R/W-0            | R/W-0             | R/W-0             | R/W-0        |  |  |  |  |

| HLMS                                                                                                                 | —                                                                                                              | OCEN                                                                                   | OCNEN                                                                    | OBEN             | OBNEN             | OAEN              | OANEN        |  |  |  |  |

| bit 15                                                                                                               |                                                                                                                |                                                                                        |                                                                          |                  |                   |                   | bit          |  |  |  |  |

| R/W-0                                                                                                                | R/W-0                                                                                                          | R/W-0                                                                                  | R/W-0                                                                    | R/W-0            | R/W-0             | R/W-0             | R/W-0        |  |  |  |  |

| NAGS                                                                                                                 | PAGS                                                                                                           | ACEN                                                                                   | ACNEN                                                                    | ABEN             | ABNEN             | AAEN              | AANEN        |  |  |  |  |

| bit 7                                                                                                                |                                                                                                                |                                                                                        |                                                                          | 1                |                   |                   | bit          |  |  |  |  |

| Legend:                                                                                                              |                                                                                                                |                                                                                        |                                                                          |                  |                   |                   |              |  |  |  |  |

| R = Readable I                                                                                                       | bit                                                                                                            | W = Writable                                                                           | bit                                                                      | U = Unimple      | mented bit, read  | l as '0'          |              |  |  |  |  |