Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc504-e-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

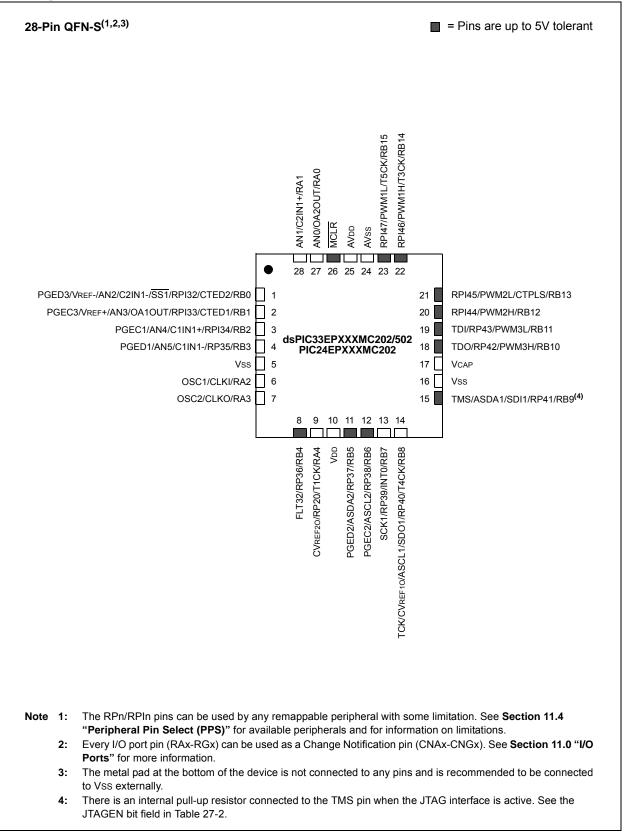

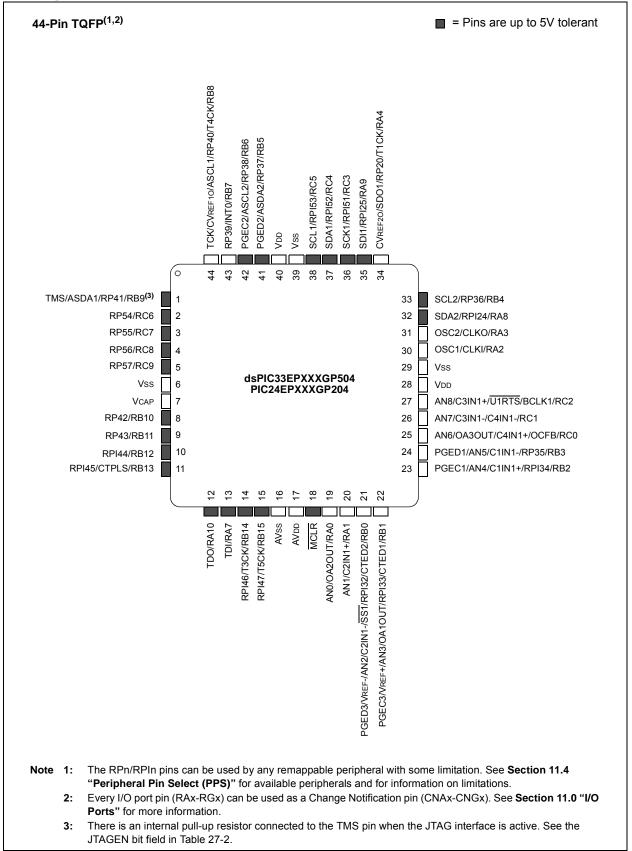

#### Pin Diagrams (Continued)

#### **Pin Diagrams (Continued)**

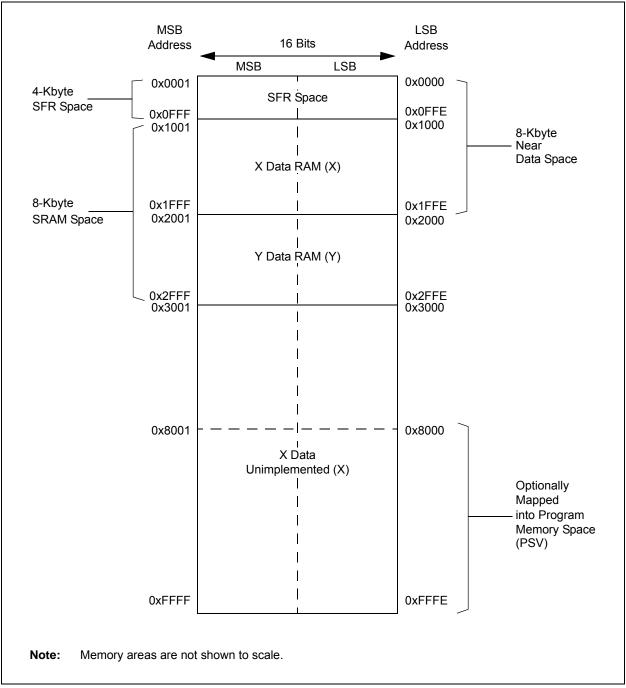

# FIGURE 4-8: DATA MEMORY MAP FOR dsPIC33EP64MC20X/50X AND dsPIC33EP64GP50X DEVICES

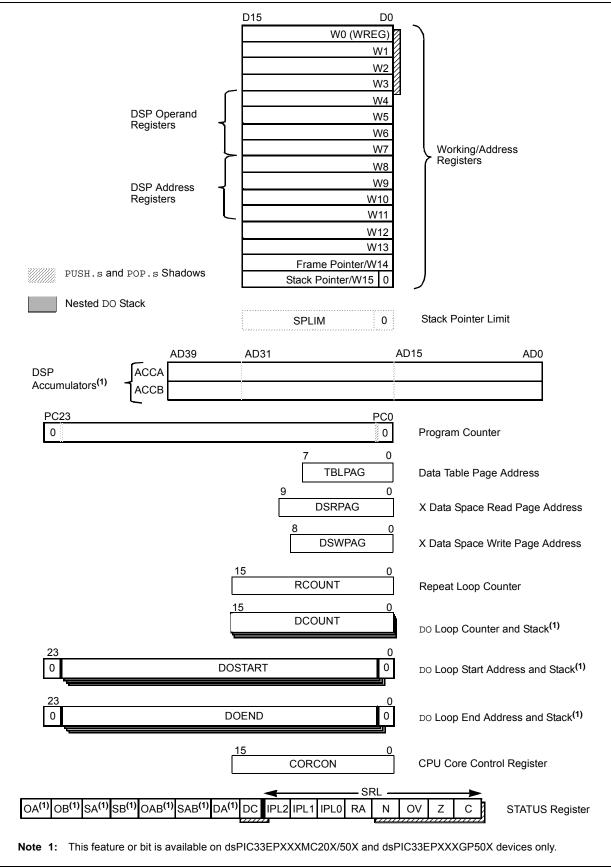

| TABLE        | 4-2:  | CPU C  | CORE RE | EGISTER | R MAP F | FOR PIC | 24EPX) | XGP/M | C20X D   | EVICES   | ONLY   |       |           |          |       |       |       |               |

|--------------|-------|--------|---------|---------|---------|---------|--------|-------|----------|----------|--------|-------|-----------|----------|-------|-------|-------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8    | Bit 7    | Bit 6  | Bit 5 | Bit 4     | Bit 3    | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| W0           | 0000  |        |         |         |         |         |        |       | W0 (WR   | EG)      |        |       |           |          |       |       |       | xxxx          |

| W1           | 0002  |        |         |         |         |         |        |       | W1       |          |        |       |           |          |       |       |       | xxxx          |

| W2           | 0004  |        |         |         |         |         |        |       | W2       |          |        |       |           |          |       |       |       | xxxx          |

| W3           | 0006  |        |         |         |         |         |        |       | W3       |          |        |       |           |          |       |       |       | xxxx          |

| W4           | 0008  |        |         |         |         |         |        |       | W4       |          |        |       |           |          |       |       |       | xxxx          |

| W5           | 000A  |        |         |         |         |         |        |       | W5       |          |        |       |           |          |       |       |       | xxxx          |

| W6           | 000C  |        |         |         |         |         |        |       | W6       |          |        |       |           |          |       |       |       | xxxx          |

| W7           | 000E  |        |         |         |         |         |        |       | W7       |          |        |       |           |          |       |       |       | xxxx          |

| W8           | 0010  |        |         |         |         |         |        |       | W8       |          |        |       |           |          |       |       |       | xxxx          |

| W9           | 0012  |        |         |         |         |         |        |       | W9       |          |        |       |           |          |       |       |       | xxxx          |

| W10          | 0014  |        |         |         |         |         |        |       | W10      |          |        |       |           |          |       |       |       | xxxx          |

| W11          | 0016  |        |         |         |         |         |        |       | W11      |          |        |       |           |          |       |       |       | xxxx          |

| W12          | 0018  |        |         |         |         |         |        |       | W12      |          |        |       |           |          |       |       |       | xxxx          |

| W13          | 001A  |        |         |         |         |         |        |       | W13      |          |        |       |           |          |       |       |       | xxxx          |

| W14          | 001C  |        |         |         |         |         |        |       | W14      |          |        |       |           |          |       |       |       | xxxx          |

| W15          | 001E  |        |         |         |         |         |        |       | W15      |          |        |       |           |          |       |       |       | xxxx          |

| SPLIM        | 0020  |        |         |         |         |         |        |       | SPLIM<1  | 5:0>     |        |       |           |          |       |       |       | 0000          |

| PCL          | 002E  |        |         |         |         |         |        | P     | CL<15:1> |          |        |       |           |          |       |       | —     | 0000          |

| PCH          | 0030  | —      | -       | _       | _       | —       | —      | —     | —        | _        |        |       |           | PCH<6:0> |       |       |       | 0000          |

| DSRPAG       | 0032  | —      | -       | _       | _       | —       | —      |       |          |          |        | DSRPA | G<9:0>    |          |       |       |       | 0001          |

| DSWPAG       | 0034  | _      |         |         |         | _       |        | _     |          |          |        | DS    | SWPAG<8:0 | >        |       |       |       | 0001          |

| RCOUNT       | 0036  |        |         |         |         |         |        |       | RCOUNT<  | 15:0>    |        |       |           |          |       |       |       | 0000          |

| SR           | 0042  | _      |         |         |         | —       |        | _     | DC       | IPL2     | IPL1   | IPL0  | RA        | N        | OV    | Z     | С     | 0000          |

| CORCON       | 0044  | VAR    | _       | -       | -       | —       |        | —     | _        | -        | _      | —     | -         | IPL3     | SFA   | —     | _     | 0020          |

| DISICNT      | 0052  | _      | _       |         |         |         |        |       |          | DISICNT< | :13:0> |       |           |          |       |       |       | 0000          |

| TBLPAG       | 0054  | _      | _       | -       | -       | —       |        | —     | _        |          |        |       | TBLPA     | G<7:0>   |       |       |       | 0000          |

| MSTRPR       | 0058  |        |         |         |         |         |        |       | MSTRPR<  | 15:0>    |        |       |           |          |       |       |       | 0000          |

#### **D** I -4.0 - -

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

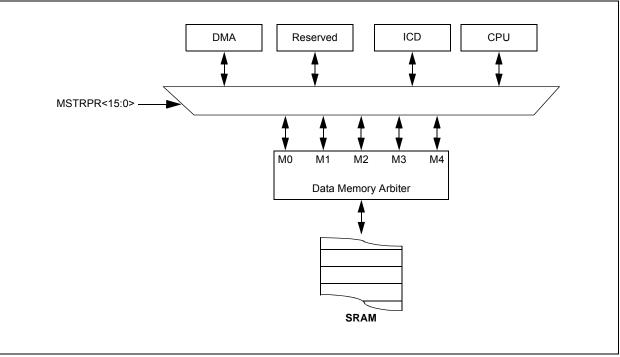

# 4.4.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below

### FIGURE 4-18: ARBITER ARCHITECTURE

that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-62.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

| TABLE 4-62: | DATA MEMORY BUS  |

|-------------|------------------|

|             | ARBITER PRIORITY |

| Drierity     | MSTRPR<15:0 | > Bit Setting <sup>(1)</sup> |

|--------------|-------------|------------------------------|

| Priority     | 0x0000      | 0x0020                       |

| M0 (highest) | CPU         | DMA                          |

| M1           | Reserved    | CPU                          |

| M2           | Reserved    | Reserved                     |

| M3           | DMA         | Reserved                     |

| M4 (lowest)  | ICD         | ICD                          |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

#### 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

#### 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

#### TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0         | R/W-0                                     | U-0                                    | U-0           | R/W-0                 | U-0               | R/W-0            | R/W-0         |

|---------------|-------------------------------------------|----------------------------------------|---------------|-----------------------|-------------------|------------------|---------------|

| TRAPF         | R IOPUWR                                  | —                                      | _             | VREGSF                | —                 | CM               | VREGS         |

| bit 15        |                                           |                                        |               |                       |                   |                  | bit 8         |

| <b>D</b> 4440 |                                           | DANIO                                  | DAMO          | DAMA                  | DAMO              |                  |               |

| R/W-0         |                                           | R/W-0                                  | R/W-0         | R/W-0                 | R/W-0             | R/W-1            | R/W-1         |

| EXTR<br>bit 7 | SWR                                       | SWDTEN <sup>(2)</sup>                  | WDTO          | SLEEP                 | IDLE              | BOR              | POR           |

|               |                                           |                                        |               |                       |                   |                  | bit (         |

| Legend:       |                                           |                                        |               |                       |                   |                  |               |

| R = Reada     | able bit                                  | W = Writable I                         | oit           | U = Unimpler          | mented bit, read  | d as '0'         |               |

| -n = Value    | at POR                                    | '1' = Bit is set                       |               | '0' = Bit is cle      | ared              | x = Bit is unkı  | nown          |

|               |                                           |                                        |               |                       |                   |                  |               |

| bit 15        | •                                         | Reset Flag bit                         |               |                       |                   |                  |               |

|               |                                           | onflict Reset ha<br>onflict Reset ha   |               | d                     |                   |                  |               |

| bit 14        | •                                         | gal Opcode or                          |               |                       | et Flag bit       |                  |               |

|               |                                           | I opcode detec                         |               |                       | •                 | lized W registe  | er used as ar |

|               |                                           | Pointer caused                         |               |                       |                   |                  |               |

|               | -                                         | l opcode or Uni                        |               | egister Reset h       | as not occurred   | d                |               |

| bit 13-12     | -                                         | ted: Read as '                         |               |                       | . 1.9             |                  |               |

| bit 11        |                                           | ash Voltage Reg<br>Itage regulator i   |               |                       | p bit             |                  |               |

|               |                                           | ltage regulator (                      |               | •                     | ing Sleep         |                  |               |

| bit 10        |                                           | ted: Read as '                         | -             | ,,                    | 5                 |                  |               |

| bit 9         | CM: Configur                              | ation Mismatch                         | Flag bit      |                       |                   |                  |               |

|               | 1 = A Configu                             | uration Mismatc<br>uration Mismatc     | h Reset has   |                       |                   |                  |               |

| bit 8         | VREGS: Volta                              | age Regulator S                        | Standby Durir | ng Sleep bit          |                   |                  |               |

|               | •                                         | egulator is active<br>egulator goes in | •             | •                     | еер               |                  |               |

| bit 7         | EXTR: Extern                              | nal Reset (MCL                         | R) Pin bit    |                       |                   |                  |               |

|               |                                           | Clear (pin) Res<br>Clear (pin) Res     |               |                       |                   |                  |               |

| bit 6         | SWR: Softwa                               | re RESET (Instr                        | uction) Flag  | bit                   |                   |                  |               |

|               |                                           | instruction has instruction has        |               |                       |                   |                  |               |

| bit 5         | SWDTEN: So                                | oftware Enable/                        | Disable of W  | DT bit <sup>(2)</sup> |                   |                  |               |

|               | 1 = WDT is e<br>0 = WDT is di             |                                        |               |                       |                   |                  |               |

| bit 4         | WDTO: Watc                                | hdog Timer Tim                         | e-out Flag bi | it                    |                   |                  |               |

|               |                                           | e-out has occur<br>e-out has not oc    |               |                       |                   |                  |               |

| Note 1:       | All of the Reset sta<br>cause a device Re |                                        | set or cleare | d in software. S      | Setting one of th | ese bits in soft | ware does not |

| 2:            | If the FWDTEN Co<br>SWDTEN bit settir     | onfiguration bit i                     | s '1' (unprog | rammed), the V        | VDT is always e   | enabled, regard  | lless of the  |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 8-3: DMAXSTAH: DMA CHANNEL X START ADDRESS REGISTER A (HIGH)

| U-0            | U-0   | U-0            | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-------|----------------|-------|--------------|------------------|--------|-------|

| —              | _     | —              | —     | —            | —                | —      | —     |

| bit 15         |       |                |       |              |                  |        | bit 8 |

|                |       |                |       |              |                  |        |       |

| R/W-0          | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

|                |       |                | STA<  | 23:16>       |                  |        |       |

| bit 7          |       |                |       |              |                  |        | bit 0 |

|                |       |                |       |              |                  |        |       |

| Legend:        |       |                |       |              |                  |        |       |

| R = Readable b | oit   | W = Writable b | it    | U = Unimpler | mented bit, read | as '0' |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 STA<23:16>: Primary Start Address bits (source or destination)

#### REGISTER 8-4: DMAXSTAL: DMA CHANNEL x START ADDRESS REGISTER A (LOW)

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0              | R/W-0 |  |

|-----------------|-------|------------------|-------|------------------|-----------------|--------------------|-------|--|

|                 |       |                  | STA   | <15:8>           |                 |                    |       |  |

| bit 15          |       |                  |       |                  |                 |                    | bit 8 |  |

|                 |       |                  |       |                  |                 |                    |       |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0              | R/W-0 |  |

|                 |       |                  | STA   | A<7:0>           |                 |                    |       |  |

| bit 7           |       |                  |       |                  |                 |                    | bit 0 |  |

|                 |       |                  |       |                  |                 |                    |       |  |

| Legend:         |       |                  |       |                  |                 |                    |       |  |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimpler     | mented bit, rea | ad as '0'          |       |  |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unknown |       |  |

bit 15-0 STA<15:0>: Primary Start Address bits (source or destination)

#### 10.3 Doze Mode

The preferred strategies for reducing power consumption are changing clock speed and invoking one of the powersaving modes. In some circumstances, this cannot be practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed can introduce communication errors, while using a power-saving mode can stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate.

Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

Programs can use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU Idles, waiting for something to invoke an interrupt routine. An automatic return to full-speed CPU operation on interrupts can be enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the ECAN<sup>™</sup> module has been configured for 500 kbps, based on this device operating speed. If the device is placed in Doze mode with a clock frequency ratio of 1:4, the ECAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

#### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid.

A peripheral module is enabled only if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

| Note: | If a PMD bit is set, the corresponding        |

|-------|-----------------------------------------------|

|       | module is disabled after a delay of one       |

|       | instruction cycle. Similarly, if a PMD bit is |

|       | cleared, the corresponding module is          |

|       | enabled after a delay of one instruction      |

|       | cycle (assuming the module control regis-     |

|       | ters are already configured to enable         |

|       | module operation).                            |

### 10.5 Power-Saving Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

#### 10.5.1 KEY RESOURCES

- "Watchdog Timer and Power-Saving Modes" (DS70615) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0                     | U-0                 | U-0                                                                                                                               | U-0   | U-0              | U-0              | U-0                | U-0   |  |  |

|-------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|------------------|------------------|--------------------|-------|--|--|

| —                       | —                   | —                                                                                                                                 | _     | —                | —                | —                  | _     |  |  |

| bit 15                  |                     |                                                                                                                                   |       |                  |                  |                    | bit 8 |  |  |

|                         |                     |                                                                                                                                   |       |                  |                  |                    |       |  |  |

| U-0                     | R/W-0               | R/W-0                                                                                                                             | R/W-0 | R/W-0            | R/W-0            | R/W-0              | R/W-0 |  |  |

| —                       |                     | INT2R<6:0>                                                                                                                        |       |                  |                  |                    |       |  |  |

| bit 7                   | t.                  |                                                                                                                                   |       |                  |                  |                    |       |  |  |

|                         |                     |                                                                                                                                   |       |                  |                  |                    |       |  |  |

| Legend:                 |                     |                                                                                                                                   |       |                  |                  |                    |       |  |  |

| R = Readal              | ole bit             | W = Writable                                                                                                                      | bit   | U = Unimpler     | mented bit, read | as '0'             |       |  |  |

| -n = Value at POR '1' = |                     | '1' = Bit is set                                                                                                                  |       | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |  |

|                         |                     |                                                                                                                                   |       |                  |                  |                    |       |  |  |

| bit 15-7                | Unimplemen          | ted: Read as 'd                                                                                                                   | )'    |                  |                  |                    |       |  |  |

| bit 6-0                 |                     | INT2R<6:0>: Assign External Interrupt 2 (INT2) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) |       |                  |                  |                    |       |  |  |

|                         | 1111001 <b>= lr</b> | put tied to RPI                                                                                                                   | 121   |                  |                  |                    |       |  |  |

|                         |                     |                                                                                                                                   |       |                  |                  |                    |       |  |  |

|                         |                     |                                                                                                                                   |       |                  |                  |                    |       |  |  |

|                         | 0000001 – Ir        | put tied to CMI                                                                                                                   | ⊃1    |                  |                  |                    |       |  |  |

|                         |                     | put tied to Civil                                                                                                                 |       |                  |                  |                    |       |  |  |

|                         |                     |                                                                                                                                   |       |                  |                  |                    |       |  |  |

|                         |                     |                                                                                                                                   |       |                  |                  |                    |       |  |  |

#### REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

#### REGISTER 11-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0<br>— T2CKR<6:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                     |                  |       |                  |                  |                    |       |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|------------------|-------|------------------|------------------|--------------------|-------|--|--|

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0          | U-0                 | U-0              | U-0   | U-0              | U-0              | U-0                | U-0   |  |  |

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _            | -                   | —                | _     | —                | —                | —                  | —     |  |  |

| —       T2CKR<6:0>         bit 7       t         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 15       |                     |                  |       |                  |                  |                    | bit 8 |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                  |                  |                    |       |  |  |

| bit 7       Image: Constraint of the system of | U-0          | R/W-0               | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0              | R/W-0 |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . <td< td=""><td>—</td><td></td><td colspan="8">T2CKR&lt;6:0&gt;</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —            |                     | T2CKR<6:0>       |       |                  |                  |                    |       |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 7        |                     | bit              |       |                  |                  |                    |       |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |                     |                  |       |                  |                  |                    |       |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Legend:      |                     |                  |       |                  |                  |                    |       |  |  |

| bit 15-7 Unimplemented: Read as '0'<br>bit 6-0 T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121<br>0000001 = Input tied to CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R = Readab   | ole bit             | W = Writable I   | bit   | U = Unimpler     | mented bit, read | as '0'             |       |  |  |

| bit 6-0 <b>T2CKR&lt;6:0&gt;:</b> Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -n = Value a | at POR              | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |  |

| bit 6-0 <b>T2CKR&lt;6:0&gt;:</b> Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                     |                  |       |                  |                  |                    |       |  |  |

| (see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121<br>0000001 = Input tied to CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 15-7     | Unimplemen          | ted: Read as 'd  | )'    |                  |                  |                    |       |  |  |

| 1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 6-0      |                     |                  |       |                  |                  |                    |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                  |                  |                    |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                  |                  |                    |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                  |                  |                    |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 0000001 = Ir        | nout tied to CM  | ⊃1    |                  |                  |                    |       |  |  |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                     |                  |       |                  |                  |                    |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 0000000 <b>- II</b> | iput tied to vss |       |                  |                  |                    |       |  |  |

#### REGISTER 11-8: RPINR14: PERIPHERAL PIN SELECT INPUT REGISTER 14 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0                | R/W-0           | R/W-0              | R/W-0 |