Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8x8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc504-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                                                                                    | 25  |

|-------|----------------------------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers and Microcontrollers         | 29  |

| 3.0   | CPU                                                                                                | 35  |

| 4.0   | Memory Organization                                                                                | 45  |

| 5.0   | Flash Program Memory                                                                               | 119 |

| 6.0   | Resets                                                                                             | 123 |

| 7.0   | Interrupt Controller                                                                               | 127 |

| 8.0   | Direct Memory Access (DMA)                                                                         | 139 |

| 9.0   | Oscillator Configuration                                                                           | 153 |

| 10.0  | Power-Saving Features                                                                              | 163 |

| 11.0  | I/O Ports                                                                                          | 173 |

| 12.0  | Timer1                                                                                             | 203 |

| 13.0  | Timer2/3 and Timer4/5                                                                              | 207 |

| 14.0  | Input Capture                                                                                      | 213 |

|       | Output Compare                                                                                     |     |

| 16.0  | High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)                     | 225 |

| 17.0  | Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only) | 249 |

|       | Serial Peripheral Interface (SPI)                                                                  |     |

| 19.0  | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                                      | 273 |

| 20.0  | Universal Asynchronous Receiver Transmitter (UART)                                                 | 281 |

| 21.0  | Enhanced CAN (ECAN™) Module (dsPIC33EPXXXGP/MC50X Devices Only)                                    | 287 |

| 22.0  | Charge Time Measurement Unit (CTMU)                                                                | 315 |

| 23.0  | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                                                    | 321 |

| 24.0  | Peripheral Trigger Generator (PTG) Module                                                          | 337 |

|       | Op Amp/Comparator Module                                                                           |     |

| 26.0  | Programmable Cyclic Redundancy Check (CRC) Generator                                               | 373 |

| 27.0  | Special Features                                                                                   | 379 |

| 28.0  | Instruction Set Summary                                                                            | 387 |

| 29.0  | Development Support                                                                                | 397 |

| 30.0  | Electrical Characteristics                                                                         | 401 |

| 31.0  | High-Temperature Electrical Characteristics                                                        | 467 |

| 32.0  | DC and AC Device Characteristics Graphs                                                            | 475 |

| 33.0  | Packaging Information                                                                              | 479 |

|       | endix A: Revision History                                                                          |     |

| Index | X                                                                                                  | 517 |

| The I | Microchip Web Site                                                                                 | 525 |

| Cust  | omer Change Notification Service                                                                   | 525 |

| Cust  | omer Support                                                                                       | 525 |

| Prod  | uct Identification System                                                                          | 527 |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

| Pin Name <sup>(4)</sup>                   | Pin<br>Type | Buffer<br>Type | PPS | Description                                                    |

|-------------------------------------------|-------------|----------------|-----|----------------------------------------------------------------|

| U2CTS                                     | - 1         | ST             | No  | UART2 Clear-To-Send.                                           |

| U2RTS                                     | 0           | _              | No  | UART2 Ready-To-Send.                                           |

| U2RX                                      | - 1         | ST             | Yes | UART2 receive.                                                 |

| U2TX                                      | 0           | _              | Yes | UART2 transmit.                                                |

| BCLK2                                     | 0           | ST             | No  | UART2 IrDA <sup>®</sup> baud clock output.                     |

| SCK1                                      | I/O         | ST             | No  | Synchronous serial clock input/output for SPI1.                |

| SDI1                                      | I           | ST             | No  | SPI1 data in.                                                  |

| SDO1                                      | 0           | _              | No  | SPI1 data out.                                                 |

| SS1                                       | I/O         | ST             | No  | SPI1 slave synchronization or frame pulse I/O.                 |

| SCK2                                      | I/O         | ST             | Yes | Synchronous serial clock input/output for SPI2.                |

| SDI2                                      | I           | ST             | Yes | SPI2 data in.                                                  |

| SDO2                                      | 0           | _              | Yes | SPI2 data out.                                                 |

| SS2                                       | I/O         | ST             | Yes | SPI2 slave synchronization or frame pulse I/O.                 |

| SCL1                                      | I/O         | ST             | No  | Synchronous serial clock input/output for I2C1.                |

| SDA1                                      | I/O         | ST             | No  | Synchronous serial data input/output for I2C1.                 |

| ASCL1                                     | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C1.      |

| ASDA1                                     | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C1.       |

| SCL2                                      | I/O         | ST             | No  | Synchronous serial clock input/output for I2C2.                |

| SDA2                                      | I/O         | ST             | No  | Synchronous serial data input/output for I2C2.                 |

| ASCL2                                     | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C2.      |

| ASDA2                                     | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C2.       |

| TMS <sup>(5)</sup>                        | - 1         | ST             | No  | JTAG Test mode select pin.                                     |

| TCK                                       | I           | ST             | No  | JTAG test clock input pin.                                     |

| TDI                                       | I           | ST             | No  | JTAG test data input pin.                                      |

| TDO                                       | 0           | _              | No  | JTAG test data output pin.                                     |

| C1RX <sup>(2)</sup>                       | - 1         | ST             | Yes | ECAN1 bus receive pin.                                         |

| C1TX <sup>(2)</sup>                       | 0           | _              | Yes | ECAN1 bus transmit pin.                                        |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup> | - 1         | ST             | Yes | PWM Fault Inputs 1 and 2.                                      |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup> | - 1         | ST             | No  | PWM Fault Inputs 3 and 4.                                      |

| FLT32 <sup>(1,3)</sup>                    | - 1         | ST             | No  | PWM Fault Input 32 (Class B Fault).                            |

| DTCMP1-DTCMP3 <sup>(1)</sup>              | - 1         | ST             | Yes | PWM Dead-Time Compensation Inputs 1 through 3.                 |

| PWM1L-PWM3L <sup>(1)</sup>                | 0           | _              | No  | PWM Low Outputs 1 through 3.                                   |

| PWM1H-PWM3H <sup>(1)</sup>                | 0           | _              | No  | PWM High Outputs 1 through 3.                                  |

| SYNCI1 <sup>(1)</sup>                     | - 1         | ST             | Yes | PWM Synchronization Input 1.                                   |

| SYNCO1 <sup>(1)</sup>                     | 0           | _              | Yes | PWM Synchronization Output 1.                                  |

| INDX1 <sup>(1)</sup>                      | I           | ST             | Yes | Quadrature Encoder Index1 pulse input.                         |

| HOME1 <sup>(1)</sup>                      | - 1         | ST             | Yes | Quadrature Encoder Home1 pulse input.                          |

| QEA1 <sup>(1)</sup>                       | - 1         | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer |

| (4)                                       |             |                |     | external clock/gate input in Timer mode.                       |

| QEB1 <sup>(1)</sup>                       | I           | ST             | Yes | Quadrature Encoder Phase B input in QEI1 mode. Auxiliary timer |

| ONTO 45 (1)                               |             |                | .,  | external clock/gate input in Timer mode.                       |

| CNTCMP1 <sup>(1)</sup>                    | 0           | _              | Yes | Quadrature Encoder Compare Output 1.                           |

Legend:CMOS = CMOS compatible input or output<br/>ST = Schmitt Trigger input with CMOS levels<br/>PPS = Peripheral Pin SelectAnalog = Analog input<br/>O = Output<br/>TTL = TTL input bufferP = Power<br/>I = Input

- Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

- 3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

- 4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

- 5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

### REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0  | U-0 | U-0 | R/W-0  | U-0 | R/W-0 | R/W-0 |

|--------|--------|-----|-----|--------|-----|-------|-------|

| TRAPR  | IOPUWR | _   | _   | VREGSF | _   | CM    | VREGS |

| bit 15 |        |     |     |        |     |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0                 | R/W-0 | R/W-0 | R/W-0 | R/W-1 | R/W-1 |

|-------|-------|-----------------------|-------|-------|-------|-------|-------|

| EXTR  | SWR   | SWDTEN <sup>(2)</sup> | WDTO  | SLEEP | IDLE  | BOR   | POR   |

| bit 7 |       |                       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 TRAPR: Trap Reset Flag bit

1 = A Trap Conflict Reset has occurred0 = A Trap Conflict Reset has not occurred

bit 14 IOPUWR: Illegal Opcode or Uninitialized W Access Reset Flag bit

1 = An illegal opcode detection, an illegal address mode or Uninitialized W register used as an Address Pointer caused a Reset

0 = An illegal opcode or Uninitialized W register Reset has not occurred

bit 13-12 Unimplemented: Read as '0'

bit 11 VREGSF: Flash Voltage Regulator Standby During Sleep bit

1 = Flash voltage regulator is active during Sleep

0 = Flash voltage regulator goes into Standby mode during Sleep

bit 10 **Unimplemented:** Read as '0'

bit 9 **CM:** Configuration Mismatch Flag bit

1 = A Configuration Mismatch Reset has occurred.0 = A Configuration Mismatch Reset has not occurred

bit 8 VREGS: Voltage Regulator Standby During Sleep bit

1 = Voltage regulator is active during Sleep

0 = Voltage regulator goes into Standby mode during Sleep

bit 7 **EXTR:** External Reset (MCLR) Pin bit

1 = A Master Clear (pin) Reset has occurred 0 = A Master Clear (pin) Reset has not occurred

bit 6 SWR: Software RESET (Instruction) Flag bit

1 = A RESET instruction has been executed 0 = A RESET instruction has not been executed

bit 5 **SWDTEN:** Software Enable/Disable of WDT bit<sup>(2)</sup>

1 = WDT is enabled 0 = WDT is disabled

WDTO: Watchdog Timer Time-out Flag bit

1 = WDT time-out has occurred

0 = WDT time-out has not occurred

**Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

bit 4

#### **REGISTER 10-3:** PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0 | U-0 | U-0 |  |  |

|--------|-----|-----|-----|-----|-------|-----|-----|--|--|

| _      | _   |     | _   | _   | CMPMD | 1   | _   |  |  |

| bit 15 |     |     |     |     |       |     |     |  |  |

| R/W-0       | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | U-0 |  |  |

|-------------|-----|-----|-----|-----|-----|--------|-----|--|--|

| CRCMD       | _   | _   | _   | _   | _   | I2C2MD | _   |  |  |

| bit 7 bit 0 |     |     |     |     |     |        |     |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 Unimplemented: Read as '0'

bit 10 **CMPMD:** Comparator Module Disable bit

1 = Comparator module is disabled

0 = Comparator module is enabled

bit 9-8 Unimplemented: Read as '0' bit 7

CRCMD: CRC Module Disable bit

1 = CRC module is disabled 0 = CRC module is enabled

Unimplemented: Read as '0'

bit 6-2 bit 1 I2C2MD: I2C2 Module Disable bit

1 = I2C2 module is disabled

0 = I2C2 module is enabled

bit 0 Unimplemented: Read as '0'

#### **REGISTER 10-4:** PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | U-0 | U-0   |

|-------|-----|-----|-----|--------|--------|-----|-------|

| _     | _   | _   | _   | REFOMD | CTMUMD | _   | _     |

| bit 7 |     |     |     |        |        |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-4 Unimplemented: Read as '0'

bit 3 **REFOMD:** Reference Clock Module Disable bit

> 1 = Reference clock module is disabled 0 = Reference clock module is enabled

bit 2 CTMUMD: CTMU Module Disable bit

1 = CTMU module is disabled

0 = CTMU module is enabled

bit 1-0 Unimplemented: Read as '0'

### REGISTER 17-10: INDX1HLD: INDEX COUNTER 1 HOLD REGISTER

| R/W-0        | R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|--------------|---------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|              | INDXHLD<15:8> |       |       |       |       |       |       |  |  |  |  |

| bit 15 bit 8 |               |       |       |       |       |       |       |  |  |  |  |

| R/W-0       | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|

|             | INDXHLD<7:0> |       |       |       |       |       |       |  |  |  |

| bit 7 bit 0 |              |       |       |       |       |       |       |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 INDXHLD<15:0>: Hold Register for Reading and Writing INDX1CNTH bits

### REGISTER 17-11: QEI1ICH: QEI1 INITIALIZATION/CAPTURE HIGH WORD REGISTER

| R/W-0  | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|--------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|        | QEIIC<31:24> |       |       |       |       |       |       |  |  |  |  |

| bit 15 |              |       |       |       |       |       |       |  |  |  |  |

| R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|--------|---------|-------|-------|-------|

|       |       |       | QEIIC< | :23:16> |       |       |       |

| bit 7 |       |       |        |         |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 QEIIC<31:16>: High Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

### REGISTER 17-12: QEI1ICL: QEI1 INITIALIZATION/CAPTURE LOW WORD REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|--------|-------|-------|-------|

|        |       |       | QEIIC- | <15:8> |       |       |       |

| bit 15 |       |       |        |        |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | QEIIC | <7:0> |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 QEIIC<15:0>: Low Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

### REGISTER 17-15: QEI1GECH: QEI1 GREATER THAN OR EQUAL COMPARE HIGH WORD REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|----------|-------|-------|-------|

|        |       |       | QEIGE | C<31:24> |       |       |       |

| bit 15 |       |       |       |          |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|----------|-------|-------|-------|

|       |       |       | QEIGE | C<23:16> |       |       |       |

| bit 7 |       |       |       |          |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 QEIGEC<31:16>: High Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

### REGISTER 17-16: QEI1GECL: QEI1 GREATER THAN OR EQUAL COMPARE LOW WORD REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|---------|-------|-------|-------|

|        |       |       | QEIGE | C<15:8> |       |       |       |

| bit 15 |       |       |       |         |       |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------|-------|-------|-------|

|       |       |       | QEIGE | C<7:0> |       |       |       |

| bit 7 |       |       |       |        |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 QEIGEC<15:0>: Low Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

# 21.0 ENHANCED CAN (ECAN™) MODULE (dsPIC33EPXXXGP/ MC50X DEVICES ONLY)

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

### 21.1 Overview

The Enhanced Controller Area Network (ECAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The dsPIC33EPXXXGP/MC50X devices contain one ECAN module.

The ECAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH CAN specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader can refer to the BOSCH CAN specification for further details.

The ECAN module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- · 0-8 bytes data length

- · Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote transmission requests

- Up to eight transmit buffers with application specified prioritization and abort capability (each buffer can contain up to 8 bytes of data)

- Up to 32 receive buffers (each buffer can contain up to 8 bytes of data)

- Up to 16 full (Standard/Extended Identifier) acceptance filters

- · Three full acceptance filter masks

- DeviceNet<sup>™</sup> addressing support

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- · Programmable clock source

- Programmable link to Input Capture (IC2) module for time-stamping and network synchronization

- · Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

### REGISTER 21-2: CxCTRL2: ECANx CONTROL REGISTER 2

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R-0    | R-0    | R-0    | R-0    | R-0    |

|-------|-----|-----|--------|--------|--------|--------|--------|

| _     | _   | _   | DNCNT4 | DNCNT3 | DNCNT2 | DNCNT1 | DNCNT0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-5 **Unimplemented:** Read as '0'

bit 4-0 **DNCNT<4:0>:** DeviceNet™ Filter Bit Number bits

10010-11111 = Invalid selection

10001 = Compares up to Data Byte 3, bit 6 with EID<17>

•

•

•

00001 = Compares up to Data Byte 1, bit 7 with EID<0>

00000 = Does not compare data bytes

## 25.1 Op Amp Application Considerations

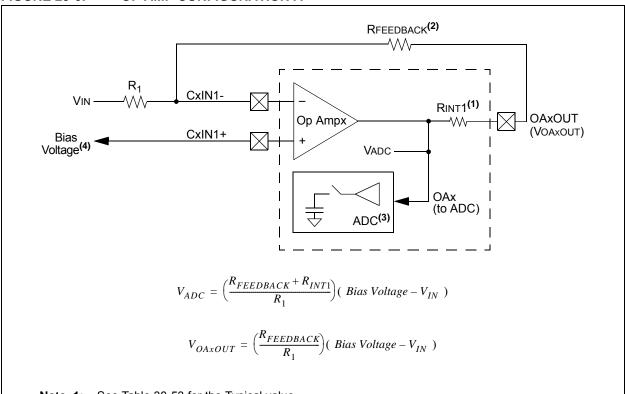

There are two configurations to take into consideration when designing with the op amp modules that available in the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X devices. Configuration A (see Figure 25-6) takes advantage of the internal connection to the ADC module to route the output of the op amp directly to the ADC for measurement. Configuration B (see Figure 25-7) requires that the designer externally route the output of the op amp (OAxOUT) to a separate analog input pin (ANy) on the device. Table 30-55 in Section 30.0 "Electrical Characteristics" describes the performance characteristics for the op amps, distinguishing between the two configuration types where applicable.

### 25.1.1 OP AMP CONFIGURATION A

Figure 25-6 shows a typical inverting amplifier circuit taking advantage of the internal connections from the op amp output to the input of the ADC. The advantage of this configuration is that the user does not need to consume another analog input (ANy) on the device, and allows the user to simultaneously sample all three op amps with the ADC module, if needed. However, the presence of the internal resistance, RINT1, adds an error in the feedback path. Since RINT1 is an internal resistance, in relation to the op amp output (VOAXOUT) and ADC internal connection (VADC), RINT1 must be included in the numerator term of the transfer function. See Table 30-53 in Section 30.0 "Electrical Characteristics" for the typical value of RINT1. Table 30-60 and Table 30-61 in Section 30.0 "Electrical Characteristics" describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration. Figure 25-6 also defines the equations that should be used when calculating the expected voltages at points, VADC and VOAXOUT.

FIGURE 25-6: OP AMP CONFIGURATION A

- **Note 1:** See Table 30-53 for the Typical value.

- 2: See Table 30-53 for the Minimum value for the feedback resistor.

- 3: See Table 30-60 and Table 30-61 for the minimum sample time (TSAMP).

- 4: CVREF10 or CVREF20 are two options that are available for supplying bias voltage to the op amps.

### REGISTER 25-2: CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3) (CONTINUED)

bit 7-6 **EVPOL<1:0>:** Trigger/Event/Interrupt Polarity Select bits

- 11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)

- 10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

Low-to-high transition of the comparator output.

If CPOL = 0 (non-inverted polarity):

High-to-low transition of the comparator output.

01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity-selected comparator output (while CEVT = 0)

If CPOL = 1 (inverted polarity):

High-to-low transition of the comparator output.

If CPOL = 0 (non-inverted polarity):

Low-to-high transition of the comparator output

00 = Trigger/event/interrupt generation is disabled

bit 5 **Unimplemented:** Read as '0'

bit 4 CREF: Comparator Reference Select bit (VIN+ input)<sup>(1)</sup>

1 = VIN+ input connects to internal CVREFIN voltage(2)

0 = VIN+ input connects to CxIN1+ pin

bit 3-2 Unimplemented: Read as '0'

bit 1-0 CCH<1:0>: Op Amp/Comparator Channel Select bits<sup>(1)</sup>

11 = Unimplemented

10 = Unimplemented

01 = Inverting input of the comparator connects to the CxIN2- pin<sup>(2)</sup>

00 = Inverting input of the op amp/comparator connects to the CxIN1- pin

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

| SPIC33EPXXX | SP50X, dsPIC3 | 3EPXXXMC2 | 0X/50X AND | PIC24EPX | XXGP/MC2 | 20X |

|-------------|---------------|-----------|------------|----------|----------|-----|

| OTES:       |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

|             |               |           |            |          |          |     |

TABLE 27-1: CONFIGURATION BYTE REGISTER MAP

| File<br>Name | Address | Device<br>Memory<br>Size<br>(Kbytes) | Bits 23-8    | Bit 7                   | Bit 6                  | Bit 5   | Bit 4                   | Bit 3                   | Bit 2    | Bit 1     | Bit 0   |

|--------------|---------|--------------------------------------|--------------|-------------------------|------------------------|---------|-------------------------|-------------------------|----------|-----------|---------|

| Reserved     | 0057EC  | 32                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 00AFEC  | 64                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 0157EC  | 128                                  | _            | _                       | _                      | _       | _                       | _                       | _        | _         | -       |

|              | 02AFEC  | 256                                  |              |                         |                        |         |                         |                         |          |           |         |

|              | 0557EC  | 512                                  |              |                         |                        |         |                         |                         |          |           |         |

| Reserved     | 0057EE  | 32                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 00AFEE  | 64                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 0157EE  | 128                                  | _            | _                       | _                      | _       | _                       | _                       | _        | _         | _       |

|              | 02AFEE  | 256                                  |              |                         |                        |         |                         |                         |          |           |         |

|              | 0557EE  | 512                                  |              |                         |                        |         |                         |                         |          |           |         |

| FICD         | 0057F0  | 32                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 00AFF0  | 64                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 0157F0  | 128                                  | i _          | Reserved <sup>(3)</sup> | _                      | JTAGEN  | Reserved <sup>(2)</sup> | Reserved <sup>(3)</sup> | _        | ICS<      | :1:0>   |

|              | 02AFF0  | 256                                  |              |                         |                        |         |                         |                         |          |           |         |

|              | 0557F0  | 512                                  |              |                         |                        |         |                         |                         |          |           |         |

| FPOR         | 0057F2  | 32                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 00AFF2  | 64                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 0157F2  | 128                                  | _            | WDTV                    | VIN<1:0>               | ALTI2C2 | ALTI2C1                 | Reserved <sup>(3)</sup> | _        | _         | _       |

|              | 02AFF2  | 256                                  |              |                         |                        |         |                         |                         |          |           |         |

|              | 0557F2  | 512                                  |              |                         |                        |         |                         |                         |          |           |         |

| FWDT         | 0057F4  | 32                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 00AFF4  | 64                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 0157F4  | 128                                  | _            | FWDTEN                  | WINDIS                 | PLLKEN  | WDTPRE                  |                         | WDTPOS   | T<3:0>    |         |

|              | 02AFF4  | 256                                  |              |                         |                        |         |                         |                         |          |           |         |

|              | 0557F4  | 512                                  |              |                         |                        |         |                         |                         |          |           |         |

| FOSC         | 0057F6  | 32                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 00AFF6  | 64                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 0157F6  | 128                                  | _            | FCKS                    | SM<1:0>                | IOL1WAY | _                       | _                       | OSCIOFNC | POSCM     | ID<1:0> |

|              | 02AFF6  | 256                                  |              |                         |                        |         |                         |                         |          | 1 0001112 |         |

|              | 0557F6  | 512                                  |              |                         |                        |         |                         |                         |          |           |         |

| FOSCSEL      | 0057F8  | 32                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 00AFF8  | 64                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 0157F8  | 128                                  | _            | IESO                    | PWMLOCK <sup>(1)</sup> | _       | _                       | _                       | F        | NOSC<2:0> |         |

|              | 02AFF8  | 256                                  |              |                         |                        |         |                         |                         |          |           |         |

|              | 0557F8  | 512                                  |              |                         |                        |         |                         |                         |          |           |         |

| FGS          | 0057FA  | 32                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 00AFFA  | 64                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 0157FA  | 128                                  | _            | _                       | _                      | _       | _                       | _                       | _        | GCP       | GWRP    |

|              | 02AFFA  | 256                                  |              |                         |                        |         |                         |                         |          |           |         |

|              | 0557FA  | 512                                  |              |                         |                        |         |                         |                         |          |           |         |

| Reserved     | 0057FC  | 32                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 00AFFC  | 64                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 0157FC  | 128                                  | _            | _                       | _                      | _       | _                       | _                       | _        | _         | _       |

|              | 02AFFC  | 256                                  |              |                         |                        |         |                         |                         |          |           |         |

|              | 0557FC  | 512                                  |              |                         |                        |         |                         |                         |          |           |         |

| Reserved     | 057FFE  | 32                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 00AFFE  | 64                                   |              |                         |                        |         |                         |                         |          |           |         |

|              | 0157FE  | 128                                  | _            | _                       | _                      | _       | _                       | _                       | _        | _         | _       |

|              | 02AFFE  | 256                                  |              |                         |                        |         |                         |                         |          |           |         |

|              | 0557FE  | 512                                  |              |                         |                        |         |                         |                         |          |           |         |

| l amandi     |         |                                      | read as '1'. |                         |                        |         |                         |                         |          |           |         |

**Legend:** — = unimplemented, read as '1'.

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

<sup>2:</sup> This bit is reserved and must be programmed as '0'.

<sup>3:</sup> These bits are reserved and must be programmed as '1'.

TABLE 27-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

| Bit Field             | Description                                                                                                                                                                           |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WDTPRE                | Watchdog Timer Prescaler bit 1 = 1:128 0 = 1:32                                                                                                                                       |

| WDTPOST<3:0>          | Watchdog Timer Postscaler bits  1111 = 1:32,768  1110 = 1:16,384  •  0001 = 1:2  0000 = 1:1                                                                                           |

| WDTWIN<1:0>           | Watchdog Window Select bits  11 = WDT window is 25% of WDT period  10 = WDT window is 37.5% of WDT period  01 = WDT window is 50% of WDT period  00 = WDT window is 75% of WDT period |

| ALTI2C1               | Alternate I2C1 pin 1 = I2C1 is mapped to the SDA1/SCL1 pins 0 = I2C1 is mapped to the ASDA1/ASCL1 pins                                                                                |

| ALTI2C2               | Alternate I2C2 pin 1 = I2C2 is mapped to the SDA2/SCL2 pins 0 = I2C2 is mapped to the ASDA2/ASCL2 pins                                                                                |

| JTAGEN <sup>(2)</sup> | JTAG Enable bit 1 = JTAG is enabled 0 = JTAG is disabled                                                                                                                              |

| ICS<1:0>              | ICD Communication Channel Select bits  11 = Communicate on PGEC1 and PGED1  10 = Communicate on PGEC2 and PGED2  01 = Communicate on PGEC3 and PGED3  00 = Reserved, do not use       |

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

<sup>2:</sup> When JTAGEN = 1, an internal pull-up resistor is enabled on the TMS pin. Erased devices default to JTAGEN = 1. Applications requiring I/O pins in a high-impedance state (tri-state) in Reset should use pins other than TMS for this purpose.

Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the Program Counter is changed as a result of the instruction, or a PSV or Table Read is performed, or an SFR register is read. In these cases, the execution takes multiple instruction cycles with the additional instruction cycle(s) executed as a NOP. Certain instructions that involve skipping over the subsequent instruction require either

two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note:

For more details on the instruction set, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

For more information on instructions that take more than one instruction cycle to execute, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual", particularly the "Instruction Flow Types" section.

TABLE 28-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Field           | Description                                                                       |  |  |

|-----------------|-----------------------------------------------------------------------------------|--|--|

| #text           | Means literal defined by "text"                                                   |  |  |

| (text)          | Means "content of text"                                                           |  |  |

| [text]          | Means "the location addressed by text"                                            |  |  |

| {}              | Optional field or operation                                                       |  |  |

| a ∈ {b, c, d}   | a is selected from the set of values b, c, d                                      |  |  |

| <n:m></n:m>     | Register bit field                                                                |  |  |

| .b              | Byte mode selection                                                               |  |  |

| .d              | Double-Word mode selection                                                        |  |  |

| .S              | Shadow register select                                                            |  |  |

| .w              | Word mode selection (default)                                                     |  |  |

| Acc             | One of two accumulators {A, B}                                                    |  |  |

| AWB             | Accumulator write back destination address register ∈ {W13, [W13]+ = 2}           |  |  |

| bit4            | 4-bit bit selection field (used in word addressed instructions) ∈ {015}           |  |  |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero              |  |  |

| Expr            | Absolute address, label or expression (resolved by the linker)                    |  |  |

| f               | File register address ∈ {0x00000x1FFF}                                            |  |  |

| lit1            | 1-bit unsigned literal ∈ {0,1}                                                    |  |  |

| lit4            | 4-bit unsigned literal ∈ {015}                                                    |  |  |

| lit5            | 5-bit unsigned literal ∈ {031}                                                    |  |  |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                   |  |  |

| lit10           | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode            |  |  |

| lit14           | 14-bit unsigned literal ∈ {016384}                                                |  |  |

| lit16           | 16-bit unsigned literal ∈ {065535}                                                |  |  |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSb must be '0'                             |  |  |

| None            | Field does not require an entry, can be blank                                     |  |  |

| OA, OB, SA, SB  | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate       |  |  |

| PC              | Program Counter                                                                   |  |  |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                 |  |  |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                             |  |  |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                    |  |  |

| Wb              | Base W register ∈ {W0W15}                                                         |  |  |

| Wd              | $Destination\ W\ register \in \{\ Wd,\ [Wd],\ [Wd++],\ [Wd],\ [++Wd],\ [Wd]\ \}$  |  |  |

| Wdo             | Destination W register ∈ { Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |  |  |

# 30.2 AC Characteristics and Timing Parameters

This section defines dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X AC characteristics and timing parameters.

TABLE 30-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V                  |  |  |  |  |  |

|--------------------|--------------------------------------------------------------|--|--|--|--|--|

|                    | (unless otherwise stated)                                    |  |  |  |  |  |

| AC CHARACTERISTICS | Operating temperature -40°C ≤ TA ≤ +85°C for Industrial      |  |  |  |  |  |

| AC CHARACTERISTICS | -40°C ≤ TA ≤ +125°C for Extended                             |  |  |  |  |  |

|                    | Operating voltage VDD range as described in Section 30.1 "DC |  |  |  |  |  |

|                    | Characteristics".                                            |  |  |  |  |  |

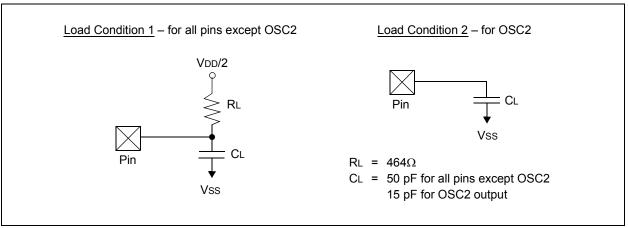

### FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                    |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | _    | 15   | pF    | In XT and HS modes, when external clock is used to drive OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | _    | _    | 50   | pF    | EC mode                                                       |

| DO58         | Св     | SCLx, SDAx            | _    | _    | 400  | pF    | In I <sup>2</sup> C™ mode                                     |

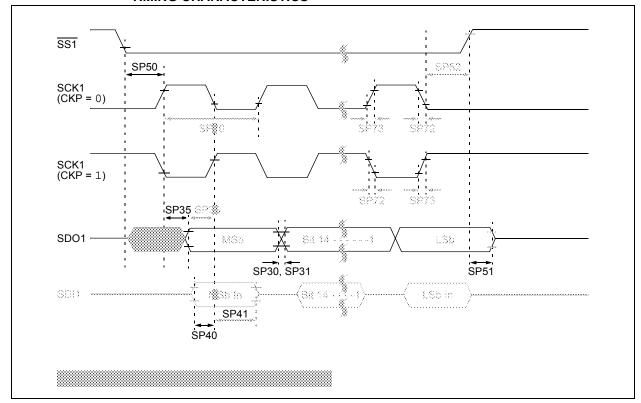

FIGURE 30-28: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

**TABLE 30-57: ADC MODULE SPECIFICATIONS**

|                    |               | ADC MODULE SPECI                                                                                                                                                                                                                                                |                                    |         |                                   |                          |                                                                                               |  |

|--------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------|-----------------------------------|--------------------------|-----------------------------------------------------------------------------------------------|--|

| AC CHARACTERISTICS |               | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) <sup>(1)</sup> Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                                    |         |                                   |                          |                                                                                               |  |

| Param<br>No.       | Symbol        | Characteristic                                                                                                                                                                                                                                                  | Min.                               | Тур.    | Max.                              | Units                    | Conditions                                                                                    |  |

|                    | Device Supply |                                                                                                                                                                                                                                                                 |                                    |         |                                   |                          |                                                                                               |  |

| AD01               | AVDD          | Module VDD Supply                                                                                                                                                                                                                                               | Greater of:<br>VDD – 0.3<br>or 3.0 |         | Lesser of:<br>VDD + 0.3<br>or 3.6 | >                        |                                                                                               |  |

| AD02               | AVss          | Module Vss Supply                                                                                                                                                                                                                                               | Vss - 0.3                          | _       | Vss + 0.3                         | V                        |                                                                                               |  |

|                    |               |                                                                                                                                                                                                                                                                 | Refere                             | ence In | puts                              |                          |                                                                                               |  |

| AD05               | VREFH         | Reference Voltage High                                                                                                                                                                                                                                          | AVss + 2.5                         | ĺ       | AVDD                              | >                        | VREFH = VREF+<br>VREFL = VREF- (Note 1)                                                       |  |

| AD05a              |               |                                                                                                                                                                                                                                                                 | 3.0                                |         | 3.6                               | ٧                        | VREFH = AVDD<br>VREFL = AVSS = 0                                                              |  |

| AD06               | VREFL         | Reference Voltage Low                                                                                                                                                                                                                                           | AVss                               | _       | AVDD - 2.5                        | V                        | (Note 1)                                                                                      |  |

| AD06a              |               |                                                                                                                                                                                                                                                                 | 0                                  | _       | 0                                 | V                        | VREFH = AVDD<br>VREFL = AVSS = 0                                                              |  |

| AD07               | VREF          | Absolute Reference<br>Voltage                                                                                                                                                                                                                                   | 2.5                                | _       | 3.6                               | V                        | VREF = VREFH - VREFL                                                                          |  |

| AD08               | IREF          | Current Drain                                                                                                                                                                                                                                                   | _                                  |         | 10<br>600                         | μ <b>Α</b><br>μ <b>Α</b> | ADC off<br>ADC on                                                                             |  |

| AD09               | IAD           | Operating Current <sup>(2)</sup>                                                                                                                                                                                                                                | _                                  | 5       | _                                 | mA                       | ADC operating in 10-bit mode (Note 1)                                                         |  |

|                    |               |                                                                                                                                                                                                                                                                 | _                                  | 2       | _                                 | mA                       | ADC operating in 12-bit mode (Note 1)                                                         |  |

|                    | Analog Input  |                                                                                                                                                                                                                                                                 |                                    |         |                                   |                          |                                                                                               |  |

| AD12               | VINH          | Input Voltage Range<br>VINH                                                                                                                                                                                                                                     | VINL                               | _       | VREFH                             | V                        | This voltage reflects Sample-and-<br>Hold Channels 0, 1, 2 and 3<br>(CH0-CH3), positive input |  |

| AD13               | VINL          | Input Voltage Range<br>VINL                                                                                                                                                                                                                                     | VREFL                              | _       | AVss + 1V                         | V                        | This voltage reflects Sample-and-<br>Hold Channels 0, 1, 2 and 3<br>(CH0-CH3), negative input |  |

| AD17               | RIN           | Recommended<br>Impedance of Analog<br>Voltage Source                                                                                                                                                                                                            | _                                  | _       | 200                               | Ω                        | Impedance to achieve maximum performance of ADC                                               |  |

Note 1: Device is functional at VBORMIN < VDD < VDDMIN, but will have degraded performance. Device functionality is tested, but not characterized. Analog modules (ADC, op amp/comparator and comparator voltage reference) may have degraded performance. Refer to Parameter BO10 in Table 30-13 for the minimum and maximum BOR values.

<sup>2:</sup> Parameter is characterized but not tested in manufacturing.

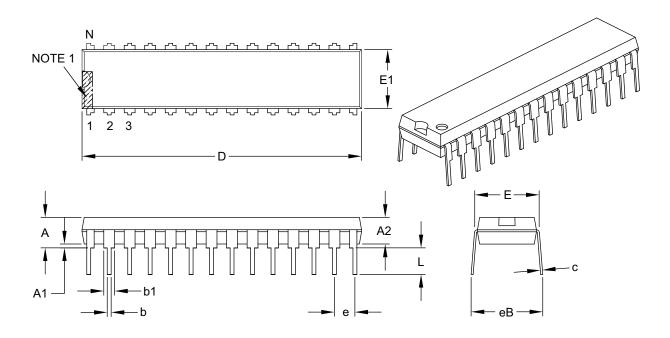

### 33.2 Package Details

### 28-Lead Skinny Plastic Dual In-Line (SP) - 300 mil Body [SPDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | INCHES |          |       |       |  |

|----------------------------|--------|----------|-------|-------|--|

| Dimension Limits           |        | MIN      | NOM   | MAX   |  |

| Number of Pins             |        | 28       |       |       |  |

| Pitch e                    |        | .100 BSC |       |       |  |

| Top to Seating Plane       | Α      | _        | _     | .200  |  |

| Molded Package Thickness   | A2     | .120     | .135  | .150  |  |

| Base to Seating Plane      | A1     | .015     | _     | _     |  |

| Shoulder to Shoulder Width | Е      | .290     | .310  | .335  |  |

| Molded Package Width       | E1     | .240     | .285  | .295  |  |

| Overall Length             | D      | 1.345    | 1.365 | 1.400 |  |

| Tip to Seating Plane       | L      | .110     | .130  | .150  |  |

| Lead Thickness             | С      | .008     | .010  | .015  |  |

| Upper Lead Width           | b1     | .040     | .050  | .070  |  |

| Lower Lead Width           | b      | .014     | .018  | .022  |  |

| Overall Row Spacing §      | eВ     | _        | _     | .430  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-070B

TABLE A-1: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                              | Update Description                                                                                                                                                       |  |  |  |  |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Section 30.0 "Electrical Characteristics" | Removed Voltage on VCAP with respect to Vss and added Note 5 in Absolute Maximum Ratings <sup>(1)</sup> .                                                                |  |  |  |  |

|                                           | Removed Parameter DC18 (VCORE) and Note 3 from the DC Temperature and Voltage Specifications (see Table 30-4).                                                           |  |  |  |  |

|                                           | Updated Note 1 in the DC Characteristics: Operating Current (IDD) (see Table 30-6).                                                                                      |  |  |  |  |

|                                           | Updated Note 1 in the DC Characteristics: Idle Current (IIDLE) (see Table 30-7).                                                                                         |  |  |  |  |

|                                           | Changed the Typical values for Parameters DC60a-DC60d and updated Note 1 in the DC Characteristics: Power-down Current (IPD) (see Table 30-8).                           |  |  |  |  |

|                                           | Updated Note 1 in the DC Characteristics: Doze Current (IDOZE) (see Table 30-9).                                                                                         |  |  |  |  |

|                                           | Updated Note 2 in the Electrical Characteristics: BOR (see Table 30-12).                                                                                                 |  |  |  |  |

|                                           | Updated Parameters CM20 and CM31, and added Parameters CM44 and CM45 in the AC/DC Characteristics: Op amp/Comparator (see Table 30-14).                                  |  |  |  |  |

|                                           | Added the Op amp/Comparator Reference Voltage Settling Time Specifications (see Table 30-15).                                                                            |  |  |  |  |

|                                           | Added Op amp/Comparator Voltage Reference DC Specifications (see Table 30-16).                                                                                           |  |  |  |  |

|                                           | Updated Internal FRC Accuracy Parameter F20a (see Table 30-21).                                                                                                          |  |  |  |  |

|                                           | Updated the Typical value and Units for Parameter CTMUI1, and added Parameters CTMUI4, CTMUFV1, and CTMUFV2 to the CTMU Current Source Specifications (see Table 30-55). |  |  |  |  |

| Section 31.0 "Packaging Information"      | Updated packages by replacing references of VLAP with TLA.                                                                                                               |  |  |  |  |

| "Product Identification System"           | Changed VLAP to TLA.                                                                                                                                                     |  |  |  |  |

### Revision E (April 2012)

This revision includes typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in Table A-3.

TABLE A-4: MAJOR SECTION UPDATES

| Section Name                           | Update Description                                                                              |  |  |  |  |  |

|----------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|--|

| "16-bit Microcontrollers               | The following 512-Kbyte devices were added to the General Purpose Families table                |  |  |  |  |  |

| and Digital Signal                     | (see Table 1):                                                                                  |  |  |  |  |  |

| Controllers (up to 512-Kbyte Flash and | • PIC24EP512GP202                                                                               |  |  |  |  |  |

| 48-Kbyte SRAM) with High-              | • PIC24EP512GP204                                                                               |  |  |  |  |  |

| Speed PWM, Op amps, and                | • PIC24EP512GP206                                                                               |  |  |  |  |  |

| Advanced Analog"                       | • dsPIC33EP512GP502                                                                             |  |  |  |  |  |

|                                        | • dsPIC33EP512GP504                                                                             |  |  |  |  |  |

|                                        | • dsPIC33EP512GP506                                                                             |  |  |  |  |  |

|                                        | The following 512-Kbyte devices were added to the Motor Control Families table (see Table 2):   |  |  |  |  |  |

|                                        | • PIC24EP512MC202                                                                               |  |  |  |  |  |

|                                        | • PIC24EP512MC204                                                                               |  |  |  |  |  |

|                                        | • PIC24EP512MC206                                                                               |  |  |  |  |  |

|                                        | • dsPIC33EP512MC202                                                                             |  |  |  |  |  |

|                                        | • dsPIC33EP512MC204                                                                             |  |  |  |  |  |

|                                        | • dsPIC33EP512MC206                                                                             |  |  |  |  |  |

|                                        | • dsPIC33EP512MC502                                                                             |  |  |  |  |  |

|                                        | • dsPIC33EP512MC504                                                                             |  |  |  |  |  |

|                                        | • dsPIC33EP512MC506                                                                             |  |  |  |  |  |

|                                        | Certain Pin Diagrams were updated to include the new 512-Kbyte devices.                         |  |  |  |  |  |

| Section 4.0 "Memory                    | Added a Program Memory Map for the new 512-Kbyte devices (see Figure 4-4).                      |  |  |  |  |  |

| Organization"                          | Added a Data Memory Map for the new dsPIC 512-Kbyte devices (see Figure 4-11).                  |  |  |  |  |  |

|                                        | Added a Data Memory Map for the new PIC24 512-Kbyte devices (see Figure 4-16).                  |  |  |  |  |  |

| Section 7.0 "Interrupt Controller"     | Updated the VECNUM bits in the INTTREG register (see Register 7-7).                             |  |  |  |  |  |

| Section 11.0 "I/O Ports"               | Added tip 6 to Section 11.5 "I/O Helpful Tips".                                                 |  |  |  |  |  |

| Section 27.0 "Special Features"        | The following modifications were made to the Configuration Byte Register Map (see Table 27-1):  |  |  |  |  |  |

|                                        | Added the column Device Memory Size (Kbytes)                                                    |  |  |  |  |  |

|                                        | Removed Notes 1 through 4                                                                       |  |  |  |  |  |

|                                        | Added addresses for the new 512-Kbyte devices                                                   |  |  |  |  |  |