Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 48-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc504-i-mv |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

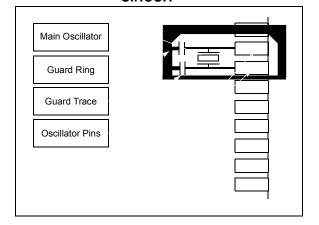

#### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

### 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

#### FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

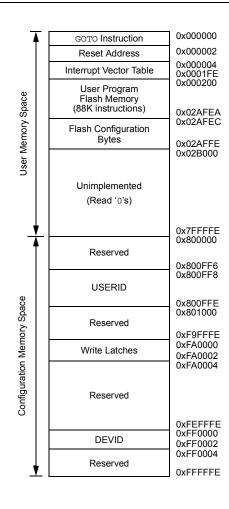

#### FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP256GP50X, dsPIC33EP256MC20X/50X AND PIC24EP256GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

| IABLE 4-2  | TABLE 4-21: ECANT REGISTER MAP WHEN WIN (CTCTRL1<0>) = 0 OR 1 FOR dSPIC33EPXXXMC/GP50X DEVICES ONLY |         |           |         |         |         |            |           |        |          |           |        |            |         |          |          |        |               |

|------------|-----------------------------------------------------------------------------------------------------|---------|-----------|---------|---------|---------|------------|-----------|--------|----------|-----------|--------|------------|---------|----------|----------|--------|---------------|

| File Name  | Addr.                                                                                               | Bit 15  | Bit 14    | Bit 13  | Bit 12  | Bit 11  | Bit 10     | Bit 9     | Bit 8  | Bit 7    | Bit 6     | Bit 5  | Bit 4      | Bit 3   | Bit 2    | Bit 1    | Bit 0  | All<br>Resets |

| C1CTRL1    | 0400                                                                                                | _       | —         | CSIDL   | ABAT    | CANCKS  | R          | EQOP<2:0  | >      | OPM      | /IODE<2:0 | >      | —          | CANCAP  | —        | —        | WIN    | 0480          |

| C1CTRL2    | 0402                                                                                                | _       | _         | —       | _       | _       | _          | —         | _      | —        | _         | _      |            | D       | NCNT<4:0 | >        |        | 0000          |

| C1VEC      | 0404                                                                                                | _       | —         | —       |         | F       | ILHIT<4:0> |           |        | —        |           |        | ICODE<6:0> |         |          | 0040     |        |               |

| C1FCTRL    | 0406                                                                                                | C       | DMABS<2:0 | >       |         | _       | —          | —         | _      | _        | _         | _      | FSA<4:0>   |         |          | 0000     |        |               |

| C1FIFO     | 0408                                                                                                |         | —         |         |         | FBP<    | 5:0>       |           |        | —        | _         |        | FNRB<5:0>  |         |          |          | 0000   |               |

| C1INTF     | 040A                                                                                                |         | —         | TXBO    | TXBP    | RXBP    | TXWAR      | RXWAR     | EWARN  | IVRIF    | WAKIF     | ERRIF  | _          | FIFOIF  | RBOVIF   | RBIF     | TBIF   | 0000          |

| C1INTE     | 040C                                                                                                |         | —         | —       |         | _       | —          | —         | _      | IVRIE    | WAKIE     | ERRIE  | _          | FIFOIE  | RBOVIE   | RBIE     | TBIE   | 0000          |

| C1EC       | 040E                                                                                                |         |           |         | TERRCN  | T<7:0>  |            |           |        |          |           |        | RERRCN     | NT<7:0> |          |          |        | 0000          |

| C1CFG1     | 0410                                                                                                | _       | _         | _       | _       | _       | _          | _         | _      | SJW<1    | :0>       |        |            | BRP     | <5:0>    |          |        | 0000          |

| C1CFG2     | 0412                                                                                                | _       | WAKFIL    | _       | _       | _       | SI         | =G2PH<2:( | )>     | SEG2PHTS | SAM       | S      | EG1PH<2    | :0>     | P        | RSEG<2:0 | >      | 0000          |

| C1FEN1     | 0414                                                                                                | FLTEN15 | FLTEN14   | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10    | FLTEN9    | FLTEN8 | FLTEN7   | FLTEN6    | FLTEN5 | FLTEN4     | FLTEN3  | FLTEN2   | FLTEN1   | FLTEN0 | FFFF          |

| C1FMSKSEL1 | 0418                                                                                                | F7MSł   | <<1:0>    | F6MSł   | <<1:0>  | F5MS    | K<1:0>     | F4MS      | K<1:0> | F3MSK<   | <1:0>     | F2MS   | K<1:0>     | F1MSH   | <<1:0>   | F0MS     | <<1:0> | 0000          |

| C1FMSKSEL2 | 041A                                                                                                | F15MS   | K<1:0>    | F14MS   | K<1:0>  | F13MS   | K<1:0>     | F12MS     | K<1:0> | F11MSK   | <1:0>     | F10MS  | K<1:0>     | F9MSk   | <<1:0>   | F8MSI    | <<1:0> | 0000          |

#### TABLE 4-21: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 OR 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-22: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

| File Name | Addr          | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8         | Bit 7        | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|---------------|---------|---------|---------|---------|---------|---------|---------|---------------|--------------|---------|---------|---------|---------|---------|---------|---------|---------------|

|           | 0400-<br>041E |         |         |         |         |         |         | S       | ee definition | when WIN     | = x     |         |         |         |         |         |         |               |

| C1RXFUL1  | 0420          | RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9  | RXFUL8        | RXFUL7       | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C1RXFUL2  | 0422          | RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24       | RXFUL23      | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C1RXOVF1  | 0428          | RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9  | RXOVF8        | RXOVF7       | RXOVF6  | RXOVF5  | RXOVF4  | RXOVF3  | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C1RXOVF2  | 042A          | RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24       | RXOVF23      | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 | 0000          |

| C1TR01CON | 0430          | TXEN1   | TXABT1  | TXLARB1 | TXERR1  | TXREQ1  | RTREN1  | TX1PF   | RI<1:0>       | TXEN0        | TXABAT0 | TXLARB0 | TXERR0  | TXREQ0  | RTREN0  | TX0PF   | RI<1:0> | 0000          |

| C1TR23CON | 0432          | TXEN3   | TXABT3  | TXLARB3 | TXERR3  | TXREQ3  | RTREN3  | TX3PF   | RI<1:0>       | TXEN2        | TXABAT2 | TXLARB2 | TXERR2  | TXREQ2  | RTREN2  | TX2PF   | RI<1:0> | 0000          |

| C1TR45CON | 0434          | TXEN5   | TXABT5  | TXLARB5 | TXERR5  | TXREQ5  | RTREN5  | TX5PF   | RI<1:0>       | TXEN4        | TXABAT4 | TXLARB4 | TXERR4  | TXREQ4  | RTREN4  | TX4PF   | RI<1:0> | 0000          |

| C1TR67CON | 0436          | TXEN7   | TXABT7  | TXLARB7 | TXERR7  | TXREQ7  | RTREN7  | TX7PF   | RI<1:0>       | TXEN6        | TXABAT6 | TXLARB6 | TXERR6  | TXREQ6  | RTREN6  | TX6PF   | RI<1:0> | xxxx          |

| C1RXD     | 0440          |         |         |         |         |         |         | E       | CAN1 Rece     | eive Data Wo | ord     |         |         |         |         |         |         | xxxx          |

| C1TXD     | 0442          |         |         |         |         |         |         | E       | CAN1 Trans    | smit Data Wo | ord     |         |         |         |         |         |         | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

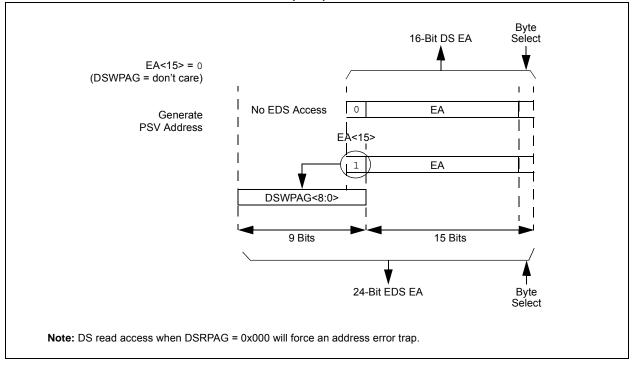

#### EXAMPLE 4-2: EXTENDED DATA SPACE (EDS) WRITE ADDRESS GENERATION

The paged memory scheme provides access to multiple 32-Kbyte windows in the EDS and PSV memory. The Data Space Page registers, DSxPAG, in combination with the upper half of the Data Space address, can provide up to 16 Mbytes of additional address space in the EDS and 8 Mbytes (DSRPAG only) of PSV address space. The paged data memory space is shown in Example 4-3.

The Program Space (PS) can be accessed with a DSRPAG of 0x200 or greater. Only reads from PS are supported using the DSRPAG. Writes to PS are not supported, so DSWPAG is dedicated to DS, including EDS only. The Data Space and EDS can be read from, and written to, using DSRPAG and DSWPAG, respectively.

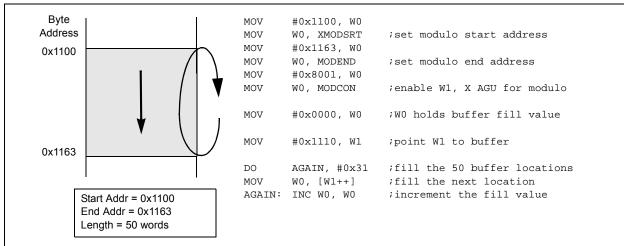

## 4.6 Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

| Note: | Y space Modulo Addressing EA calcula- |

|-------|---------------------------------------|

|       | tions assume word-sized data (LSb of  |

|       | every EA is always clear).            |

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

#### FIGURE 4-20: MODULO ADDRESSING OPERATION EXAMPLE

# 16.3 PWMx Control Registers

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | HS/HC-0 | R/W-0 | R/W-0               | R/W-0                  | R/W-0                  |

|--------|-----|--------|---------|-------|---------------------|------------------------|------------------------|

| PTEN   | —   | PTSIDL | SESTAT  | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15 |     |        |         |       |                     |                        | bit 8                  |

| R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-----------------------|-------------------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|------------------------|

| SYNCEN <sup>(1)</sup> | SYNCSRC2 <sup>(1)</sup> | SYNCSRC1 <sup>(1)</sup> | SYNCSRC0 <sup>(1)</sup> | SEVTPS3 <sup>(1)</sup> | SEVTPS2 <sup>(1)</sup> | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |

| bit 7                 | •                       |                         |                         |                        |                        |                        | bit 0                  |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit | t                  |

|-------------------|-----------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re  | ad as '0'          |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15  | PTEN: PWMx Module Enable bit                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = PWMx module is enabled</li> <li>0 = PWMx module is disabled</li> </ul>                                                                     |

| bit 14  | Unimplemented: Read as '0'                                                                                                                              |

| bit 13  | PTSIDL: PWMx Time Base Stop in Idle Mode bit                                                                                                            |

|         | <ul> <li>1 = PWMx time base halts in CPU Idle mode</li> <li>0 = PWMx time base runs in CPU Idle mode</li> </ul>                                         |

| bit 12  | SESTAT: Special Event Interrupt Status bit                                                                                                              |

|         | <ul> <li>1 = Special event interrupt is pending</li> <li>0 = Special event interrupt is not pending</li> </ul>                                          |

| bit 11  | SEIEN: Special Event Interrupt Enable bit                                                                                                               |

|         | 1 = Special event interrupt is enabled                                                                                                                  |

|         | 0 = Special event interrupt is disabled                                                                                                                 |

| bit 10  | EIPU: Enable Immediate Period Updates bit <sup>(1)</sup>                                                                                                |

|         | <ul> <li>1 = Active Period register is updated immediately</li> <li>0 = Active Period register updates occur on PWMx cycle boundaries</li> </ul>        |

| bit 9   | SYNCPOL: Synchronize Input and Output Polarity bit <sup>(1)</sup>                                                                                       |

|         | 1 = SYNCI1/SYNCO1 polarity is inverted (active-low)                                                                                                     |

|         | 0 = SYNCI1/SYNCO1 is active-high                                                                                                                        |

| bit 8   | SYNCOEN: Primary Time Base Sync Enable bit <sup>(1)</sup>                                                                                               |

|         | 1 = SYNCO1 output is enabled                                                                                                                            |

| L:1 7   | 0 = SYNCO1 output is disabled                                                                                                                           |

| bit 7   | SYNCEN: External Time Base Synchronization Enable bit <sup>(1)</sup>                                                                                    |

|         | <ul> <li>1 = External synchronization of primary time base is enabled</li> <li>0 = External synchronization of primary time base is disabled</li> </ul> |

|         |                                                                                                                                                         |

| Note 1: | These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user                                                   |

|         | application must program the period register with a value that is slightly larger than the expected period of                                           |

the external synchronization input signal.

2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| —      | —     | —     | —     | —     | —     | AMSK9 | AMSK8 |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| AMSK7  | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 |

| bit 7  |       |       |       |       |       |       | bit 0 |

#### REGISTER 19-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSK<9:0>: Address Mask Select bits

For 10-Bit Address:

1 = Enables masking for bit Ax of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax; bit match is required in this position

For 7-Bit Address (I2CxMSK<6:0> only):

1 = Enables masking for bit Ax + 1 of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax + 1; bit match is required in this position

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

|         |         |         |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

#### REGISTER 21-24: CxRXOVF1: ECANx RECEIVE BUFFER OVERFLOW REGISTER 1

| RXOVF7  | RXOVF6 | RXOVF5         | RXOVF4            | RXOVF3         | RXOVF2             | RXOVF1 | RXOVF0 |

|---------|--------|----------------|-------------------|----------------|--------------------|--------|--------|

| bit 7   |        |                |                   |                |                    |        | bit 0  |

|         |        |                |                   |                |                    |        |        |

| Legend: |        | C = Writable b | oit, but only '0' | can be writter | n to clear the bit |        |        |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                             |                    |  |  |

|-------------------|----------------------------------------------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                               | U = Unimplemented bit, read | as '0'             |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 15-0 RXOVF<15:0>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### REGISTER 21-25: CxRXOVF2: ECANx RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but or | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |  |

|-------------------|--------------------------|----------------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit         | W = Writable bit U = Unimplemented bit, read as '0'            |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |  |  |

bit 15-0 RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module attempted to write to a full buffer (set by module)

0 = No overflow condition (cleared by user software)

#### 21.5 ECAN Message Buffers

ECAN Message Buffers are part of RAM memory. They are not ECAN Special Function Registers. The user application must directly write into the RAM area that is configured for ECAN Message Buffers. The location and size of the buffer area is defined by the user application.

#### BUFFER 21-1: ECAN™ MESSAGE BUFFER WORD 0

| U-0           | U-0                       | U-0              | R/W-x         | R/W-x            | R/W-x            | R/W-x           | R/W-x |

|---------------|---------------------------|------------------|---------------|------------------|------------------|-----------------|-------|

|               | —                         |                  | SID10         | SID9             | SID8             | SID7            | SID6  |

| bit 15        |                           |                  |               |                  |                  |                 | bit 8 |

| R/W-x         | R/W-x                     | R/W-x            | R/W-x         | R/W-x            | R/W-x            | R/W-x           | R/W-x |

| SID5          | SID4                      | SID3             | SID2          | SID1             | SID0             | SRR             | IDE   |

| bit 7         |                           | •                |               |                  |                  |                 | bit 0 |

| Legend:       |                           |                  |               |                  |                  |                 |       |

| R = Readabl   | e bit                     | W = Writable     | bit           | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value at | POR                       | '1' = Bit is set |               | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

|               |                           |                  |               |                  |                  |                 |       |

| bit 15-13     | Unimplemen                | ted: Read as '   | כי            |                  |                  |                 |       |

| bit 12-2      | <b>SID&lt;10:0&gt;:</b> S | tandard Identifi | ier bits      |                  |                  |                 |       |

| bit 1         | SRR: Substitu             | ute Remote Re    | quest bit     |                  |                  |                 |       |

|               | When IDE =                | ):               |               |                  |                  |                 |       |

|               | 1 = Message               | will request rer | note transmis | ssion            |                  |                 |       |

|               | 0 = Normal m              | lessage          |               |                  |                  |                 |       |

|               | When IDE = 1              | L:               |               |                  |                  |                 |       |

|               | The SRR bit r             | must be set to ' | 1'.           |                  |                  |                 |       |

| bit 0         | IDE: Extende              | d Identifier bit |               |                  |                  |                 |       |

|               | 1 = Message               | will transmit Ex | tended Ident  | ifier            |                  |                 |       |

|               |                           | will transmit St |               |                  |                  |                 |       |

|               |                           |                  |               |                  |                  |                 |       |

#### BUFFER 21-2: ECAN™ MESSAGE BUFFER WORD 1

| U-0                                                                  | U-0   | U-0   | U-0   | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |

|----------------------------------------------------------------------|-------|-------|-------|-----------------------------------------|-------|-------|-------|--|

| —                                                                    | —     | —     | _     | EID17                                   | EID16 | EID15 | EID14 |  |

| bit 15                                                               |       |       |       |                                         |       |       | bit 8 |  |

|                                                                      |       |       |       |                                         |       |       |       |  |

| R/W-x                                                                | R/W-x | R/W-x | R/W-x | R/W-x                                   | R/W-x | R/W-x | R/W-x |  |

| EID13                                                                | EID12 | EID11 | EID10 | EID9                                    | EID8  | EID7  | EID6  |  |

| bit 7                                                                |       |       |       |                                         |       |       | bit 0 |  |

|                                                                      |       |       |       |                                         |       |       |       |  |

| Legend:                                                              |       |       |       |                                         |       |       |       |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |       |       |                                         |       |       |       |  |

| -n = Value at POR (1' = Bit is set                                   |       |       |       | '0' = Bit is cleared x = Bit is unknown |       |       |       |  |

|                                                                      |       |       |       |                                         |       |       |       |  |

bit 15-12 Unimplemented: Read as '0'

bit 11-0 EID<17:6>: Extended Identifier bits

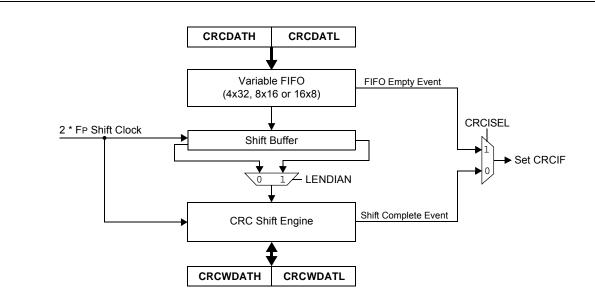

## 26.0 PROGRAMMABLE CYCLIC REDUNDANCY CHECK (CRC) GENERATOR

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Programmable Cyclic Redundancy Check (CRC)" (DS70346) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The programmable CRC generator offers the following features:

- User-programmable (up to 32nd order) polynomial CRC equation

- Interrupt output

- Data FIFO

The programmable CRC generator provides a hardware implemented method of quickly generating checksums for various networking and security applications. It offers the following features:

- User-programmable CRC polynomial equation, up to 32 bits

- Programmable shift direction (little or big-endian)

- · Independent data and polynomial lengths

- Configurable interrupt output

- Data FIFO

A simplified block diagram of the CRC generator is shown in Figure 26-1. A simple version of the CRC shift engine is shown in Figure 26-2.

#### FIGURE 26-1: CRC BLOCK DIAGRAM

| DC CH        | ARACTE | RISTICS                                                 | (unless o                       | <b>I Operatin</b><br>otherwise<br>g temperat | ture -40° | C ≤ TA ≤ | <b>/ to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |  |  |

|--------------|--------|---------------------------------------------------------|---------------------------------|----------------------------------------------|-----------|----------|-----------------------------------------------------------------|--|--|

| Param<br>No. | Symbol | Characteristic                                          | Min. Typ. Max. Units Conditions |                                              |           |          |                                                                 |  |  |

|              | VIL    | Input Low Voltage                                       |                                 |                                              |           |          |                                                                 |  |  |

| DI10         |        | Any I/O Pin and MCLR                                    | Vss                             | —                                            | 0.2 VDD   | V        |                                                                 |  |  |

| DI18         |        | I/O Pins with SDAx, SCLx                                | Vss                             | —                                            | 0.3 VDD   | V        | SMBus disabled                                                  |  |  |

| DI19         |        | I/O Pins with SDAx, SCLx                                | Vss                             | —                                            | 0.8       | V        | SMBus enabled                                                   |  |  |

|              | VIH    | Input High Voltage                                      |                                 |                                              |           |          |                                                                 |  |  |

| DI20         |        | I/O Pins Not 5V Tolerant                                | 0.8 VDD                         | —                                            | Vdd       | V        | (Note 3)                                                        |  |  |

|              |        | I/O Pins 5V Tolerant and MCLR                           | 0.8 VDD                         | —                                            | 5.5       | V        | (Note 3)                                                        |  |  |

|              |        | I/O Pins with SDAx, SCLx                                | 0.8 VDD                         | —                                            | 5.5       | V        | SMBus disabled                                                  |  |  |

|              |        | I/O Pins with SDAx, SCLx                                | 2.1                             | _                                            | 5.5       | V        | SMBus enabled                                                   |  |  |

|              | ICNPU  | Change Notification Pull-up Current                     |                                 |                                              |           |          |                                                                 |  |  |

| DI30         |        |                                                         | 150                             | 250                                          | 550       | μA       | VDD = 3.3V, VPIN = VSS                                          |  |  |

|              | ICNPD  | Change Notification<br>Pull-Down Current <sup>(4)</sup> |                                 |                                              |           |          |                                                                 |  |  |

| DI31         |        |                                                         | 20                              | 50                                           | 100       | μA       | Vdd = 3.3V, Vpin = Vdd                                          |  |  |

#### TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (VSS 0.3). Characterized but not tested.

**5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

- 8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

# TABLE 30-45:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| АС СНА |                       | rics                                         | Standard Op<br>(unless othe<br>Operating ter | rwise st            | <b>ated)</b><br>e -40°C ⊴ | ≤ Ta ≤ +8 | <b>o 3.6V</b><br>35°C for Industrial<br>125°C for Extended |

|--------|-----------------------|----------------------------------------------|----------------------------------------------|---------------------|---------------------------|-----------|------------------------------------------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                         | Тур. <sup>(2)</sup> | Max.                      | Units     | Conditions                                                 |

| SP70   | FscP                  | Maximum SCK1 Input<br>Frequency              | _                                            |                     | Lesser of FP or 15        | MHz       | (Note 3)                                                   |

| SP72   | TscF                  | SCK1 Input Fall Time                         | —                                            |                     |                           | ns        | See Parameter DO32<br>(Note 4)                             |

| SP73   | TscR                  | SCK1 Input Rise Time                         | —                                            |                     | —                         | ns        | See Parameter DO31<br>(Note 4)                             |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                   | —                                            |                     | _                         | ns        | See Parameter DO32<br>(Note 4)                             |

| SP31   | TdoR                  | SDO1 Data Output Rise Time                   | —                                            |                     | —                         | ns        | See Parameter DO31<br>(Note 4)                             |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —                                            | 6                   | 20                        | ns        |                                                            |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30                                           |                     | _                         | ns        |                                                            |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge   | 30                                           |                     |                           | ns        |                                                            |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge    | 30                                           |                     | —                         | ns        |                                                            |

| SP50   | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓<br>Input           | 120                                          |                     | —                         | ns        |                                                            |

| SP51   | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance       | 10                                           | _                   | 50                        | ns        | (Note 4)                                                   |

| SP52   | TscH2ssH<br>TscL2ssH  | SS1 ↑ after SCK1 Edge                        | 1.5 Tcy + 40                                 | _                   | _                         | ns        | (Note 4)                                                   |

| SP60   | TssL2doV              | SDO1 Data Output Valid after<br>SS1 Edge     | —                                            |                     | 50                        | ns        |                                                            |

Note 1: These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

# TABLE 30-46:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| АС СНА | ARACTERIS             | rics                                            | Standard Op<br>(unless othe<br>Operating ter | erwise st           | <b>ated)</b><br><sup>-</sup> e -40°C | $\leq$ Ta $\leq$ +8 | <b>o 3.6V</b><br>85°C for Industrial<br>125°C for Extended |

|--------|-----------------------|-------------------------------------------------|----------------------------------------------|---------------------|--------------------------------------|---------------------|------------------------------------------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                   | Min.                                         | Typ. <sup>(2)</sup> | Max.                                 | Units               | Conditions                                                 |

| SP70   | FscP                  | Maximum SCK1 Input<br>Frequency                 | —                                            | _                   | Lesser of<br>FP or 11                | MHz                 | (Note 3)                                                   |

| SP72   | TscF                  | SCK1 Input Fall Time                            | _                                            | _                   | _                                    | ns                  | See Parameter DO32<br>(Note 4)                             |

| SP73   | TscR                  | SCK1 Input Rise Time                            | —                                            | _                   | _                                    | ns                  | See Parameter DO31 (Note 4)                                |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                      | —                                            | —                   | —                                    | ns                  | See Parameter DO32<br>(Note 4)                             |

| SP31   | TdoR                  | SDO1 Data Output Rise Time                      | —                                            | _                   | —                                    | ns                  | See Parameter DO31<br>(Note 4)                             |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge       | —                                            | 6                   | 20                                   | ns                  |                                                            |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge    | 30                                           | —                   | —                                    | ns                  |                                                            |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge      | 30                                           | —                   | —                                    | ns                  |                                                            |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge       | 30                                           | _                   | —                                    | ns                  |                                                            |

| SP50   | TssL2scH,<br>TssL2scL | $\overline{SS1}$ ↓ to SCK1 ↑ or SCK1 ↓<br>Input | 120                                          | —                   | —                                    | ns                  |                                                            |

| SP51   | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance          | 10                                           | —                   | 50                                   | ns                  | (Note 4)                                                   |

| SP52   | TscH2ssH,<br>TscL2ssH | SS1 ↑ after SCK1 Edge                           | 1.5 Tcy + 40                                 | _                   | _                                    | ns                  | (Note 4)                                                   |

| SP60   | TssL2doV              | SDO1 Data Output Valid after                    | —                                            | —                   | 50                                   | ns                  |                                                            |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 91 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

| DC CHARACTERISTICS                 |             |                                                    |      | $\begin{array}{l} \mbox{Standard Operating Conditions:3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |       |                                   |  |  |

|------------------------------------|-------------|----------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------------------------------|--|--|

| Param<br>No. Symbol Characteristic |             |                                                    | Min. | Тур.                                                                                                                                                                                                                                                                                   | Max. | Units | Conditions                        |  |  |

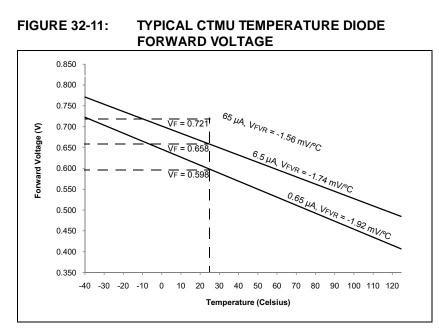

| CTMU Curr                          | rent Source | 9                                                  |      |                                                                                                                                                                                                                                                                                        |      |       |                                   |  |  |

| CTMUI1                             | Ιουτ1       | Base Range <sup>(1)</sup>                          | 0.29 |                                                                                                                                                                                                                                                                                        | 0.77 | μA    | CTMUICON<9:8> = 01                |  |  |

| CTMUI2                             | IOUT2       | 10x Range <sup>(1)</sup>                           | 3.85 |                                                                                                                                                                                                                                                                                        | 7.7  | μA    | CTMUICON<9:8> = 10                |  |  |

| CTMUI3                             | Ιουτ3       | 100x Range <sup>(1)</sup>                          | 38.5 | _                                                                                                                                                                                                                                                                                      | 77   | μA    | CTMUICON<9:8> = 11                |  |  |

| CTMUI4                             | IOUT4       | 1000x Range <sup>(1)</sup>                         | 385  | _                                                                                                                                                                                                                                                                                      | 770  | μA    | CTMUICON<9:8> = 00                |  |  |

| CTMUFV1                            | VF          | Temperature Diode Forward Voltage <sup>(1,2)</sup> | _    | 0.598                                                                                                                                                                                                                                                                                  | _    | V     | TA = +25°C,<br>CTMUICON<9:8> = 01 |  |  |

|                                    |             |                                                    | _    | 0.658                                                                                                                                                                                                                                                                                  | _    | V     | TA = +25°C,<br>CTMUICON<9:8> = 10 |  |  |

|                                    |             |                                                    | _    | 0.721                                                                                                                                                                                                                                                                                  | _    | V     | TA = +25°C,<br>CTMUICON<9:8> = 11 |  |  |

| CTMUFV2                            | VFVR        | Temperature Diode Rate of                          |      | -1.92                                                                                                                                                                                                                                                                                  | _    | mV/ºC | CTMUICON<9:8> = 01                |  |  |

|                                    |             | Change <sup>(1,2,3)</sup>                          | _    | -1.74                                                                                                                                                                                                                                                                                  | _    | mV/ºC | CTMUICON<9:8> = 10                |  |  |

|                                    |             |                                                    |      | -1.56                                                                                                                                                                                                                                                                                  | _    | mV/ºC | CTMUICON<9:8> = 11                |  |  |

#### TABLE 30-56: CTMU CURRENT SOURCE SPECIFICATIONS

Note 1: Nominal value at center point of current trim range (CTMUICON<15:10> = 000000).

2: Parameters are characterized but not tested in manufacturing.

**3:** Measurements taken with the following conditions:

- VREF+ = AVDD = 3.3V

- ADC configured for 10-bit mode

- ADC module configured for conversion speed of 500 ksps

- All PMDx bits are cleared (PMDx = 0)

- Executing a while(1) statement

- · Device operating from the FRC with no PLL

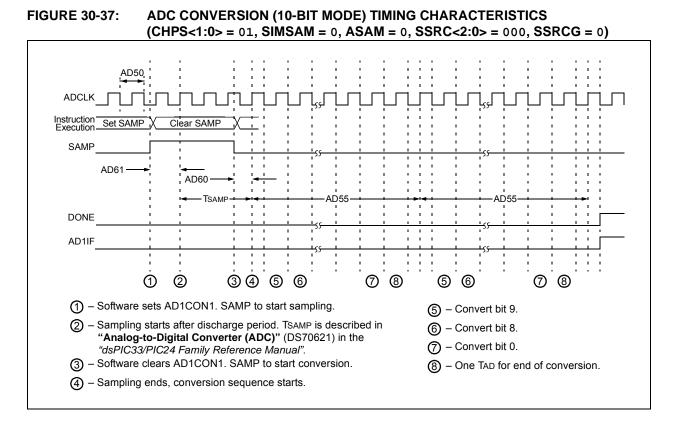

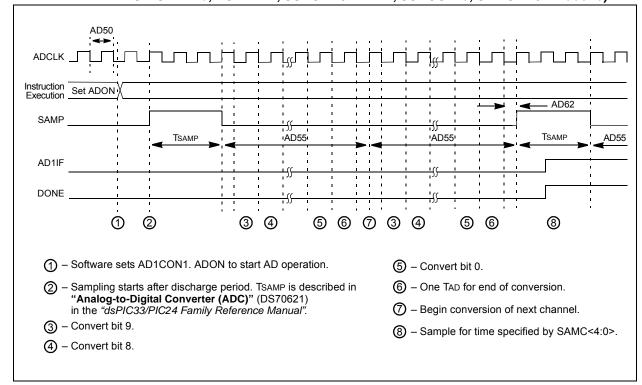

#### FIGURE 30-38: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 1, SSRC<2:0> = 111, SSRCG = 0, SAMC<4:0> = 00010)

DS70000657H-page 464

Temperature (Celsius)

70 80 90 100 110 120

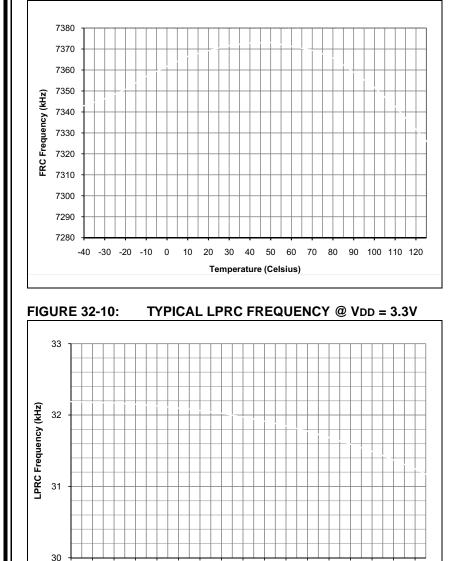

TYPICAL FRC FREQUENCY @ VDD = 3.3V

-40 -30 -20 -10

0 10 20 30 40 50 60

**FIGURE 32-9:**

# 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-124C Sheet 1 of 2

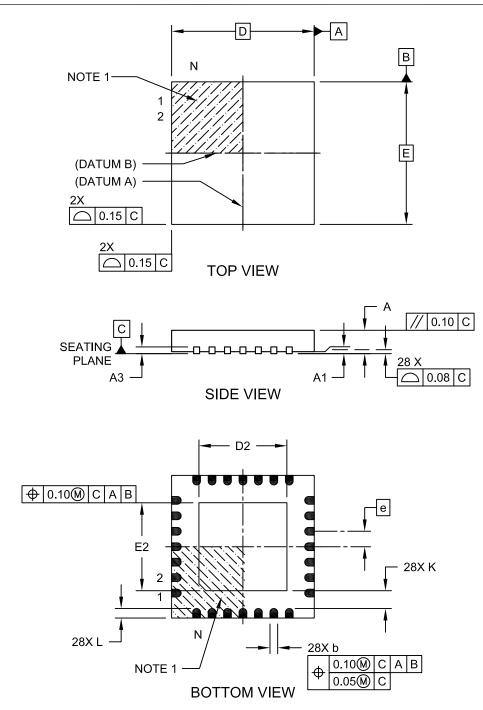

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | MILLIMETERS |                |          |       |  |

|-------------------------|-------------|----------------|----------|-------|--|

| Dimension               | MIN         | NOM            | MAX      |       |  |

| Number of Pins          | Ν           |                | 44       |       |  |

| Number of Pins per Side | ND          |                | 12       |       |  |

| Number of Pins per Side | NE          |                | 10       |       |  |

| Pitch                   | е           | 0.50 BSC       |          |       |  |

| Overall Height          | Α           | 0.80 0.90 1.00 |          |       |  |

| Standoff                | A1          | 0.025          | -        | 0.075 |  |

| Overall Width           | Е           |                | 6.00 BSC |       |  |

| Exposed Pad Width       | E2          | 4.40           | 4.55     | 4.70  |  |

| Overall Length          | D           |                | 6.00 BSC |       |  |

| Exposed Pad Length      | D2          | 4.40 4.55 4.70 |          |       |  |

| Contact Width           | b           | 0.20           | 0.25     | 0.30  |  |

| Contact Length          | L           | 0.20 0.25 0.30 |          |       |  |

| Contact-to-Exposed Pad  | К           | 0.20           | -        | -     |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-157C Sheet 2 of 2

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support