Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

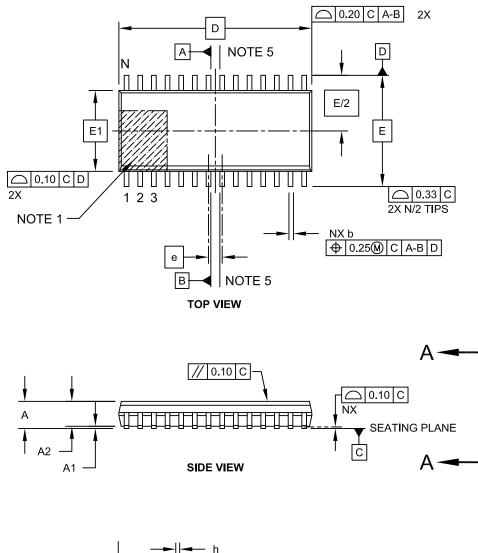

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc504-i-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

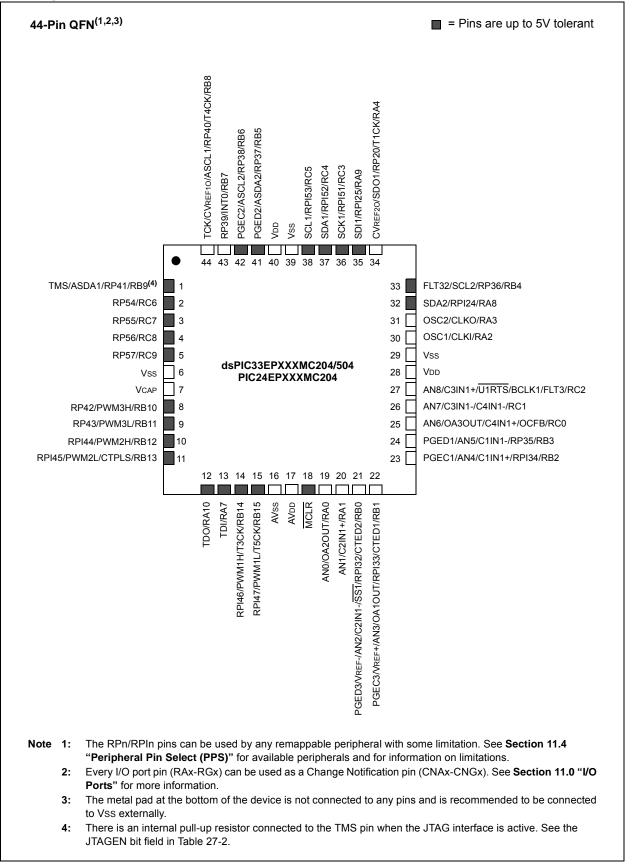

## Pin Diagrams (Continued)

## 3.5 **Programmer's Model**

The programmer's model for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X is shown in Figure 3-2. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register.

In addition to the registers contained in the programmer's model, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/

MC20X devices contain control registers for Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only), Bit-Reversed Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only) and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory mapped, as shown in Table 4-1.

| Register(s) Name                                      | Description                                               |

|-------------------------------------------------------|-----------------------------------------------------------|

| W0 through W15                                        | Working Register Array                                    |

| ACCA, ACCB                                            | 40-Bit DSP Accumulators                                   |

| PC                                                    | 23-Bit Program Counter                                    |

| SR                                                    | ALU and DSP Engine STATUS Register                        |

| SPLIM                                                 | Stack Pointer Limit Value Register                        |

| TBLPAG                                                | Table Memory Page Address Register                        |

| DSRPAG                                                | Extended Data Space (EDS) Read Page Register              |

| DSWPAG                                                | Extended Data Space (EDS) Write Page Register             |

| RCOUNT                                                | REPEAT Loop Count Register                                |

| DCOUNT <sup>(1)</sup>                                 | DO Loop Count Register                                    |

| DOSTARTH <sup>(1,2)</sup> , DOSTARTL <sup>(1,2)</sup> | DO Loop Start Address Register (High and Low)             |

| DOENDH <sup>(1)</sup> , DOENDL <sup>(1)</sup>         | DO Loop End Address Register (High and Low)               |

| CORCON                                                | Contains DSP Engine, DO Loop Control and Trap Status bits |

#### TABLE 3-1: PROGRAMMER'S MODEL REGISTER DESCRIPTIONS

Note 1: This register is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

2: The DOSTARTH and DOSTARTL registers are read-only.

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10                    | Bit 9          | Bit 8  | Bit 7 | Bit 6       | Bit 5           | Bit 4         | Bit 3  | Bit 2    | Bit 1        | Bit 0   | All<br>Reset |

|--------------|-------|--------|--------|------------|--------|--------|---------------------------|----------------|--------|-------|-------------|-----------------|---------------|--------|----------|--------------|---------|--------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF                    | SPI1EIF        | T3IF   | T2IF  | OC2IF       | IC2IF           | DMA0IF        | T1IF   | OC1IF    | IC1IF        | INTOIF  | 0000         |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF                     | OC3IF          | DMA2IF | _     | _           | _               | INT1IF        | CNIF   | CMIF     | MI2C1IF      | SI2C1IF | 0000         |

| IFS2         | 0804  | _      | _      | _          | _      |        |                           |                | _      | _     | IC4IF       | IC3IF           | DMA3IF        | C1IF   | C1RXIF   | SPI2IF       | SPI2EIF | 0000         |

| IFS3         | 0806  | _      | _      | _          | _      |        | QEI1IF                    | PSEMIF         | _      | _     | _           | _               | _             | _      | MI2C2IF  | SI2C2IF      | _       | 0000         |

| IFS4         | 0808  | _      | _      | CTMUIF     |        |        |                           | -              | _      | _     | C1TXIF      | _               | _             | CRCIF  | U2EIF    | U1EIF        |         | 0000         |

| IFS5         | 080A  | PWM2IF | PWM1IF | _          |        |        |                           |                | _      | _     | _           | _               | _             | _      | _        | _            |         | 0000         |

| IFS6         | 080C  | _      | _      | _          |        |        |                           |                | _      | _     | _           | _               | _             | _      | _        | _            | PWM3IF  | 0000         |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          |        |        |                           |                | _      | _     | _           | _               | _             | _      | _        | _            |         | 0000         |

| IFS9         | 0812  | _      | —      | _          | _      | _      |                           |                | _      | —     | PTG3IF      | PTG2IF          | PTG1IF        | PTG0IF | PTGWDTIF | PTGSTEPIF    |         | 0000         |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE                    | SPI1EIE        | T3IE   | T2IE  | OC2IE       | IC2IE           | DMA0IE        | T1IE   | OC1IE    | IC1IE        | INTOIE  | 0000         |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE                     | OC3IE          | DMA2IE | —     | _           | —               | INT1IE        | CNIE   | CMIE     | MI2C1IE      | SI2C1IE | 0000         |

| IEC2         | 0824  | _      | _      | _          | _      | _      |                           | _              | _      | _     | IC4IE       | IC3IE           | <b>DMA3IE</b> | C1IE   | C1RXIE   | SPI2IE       | SPI2EIE | 0000         |

| IEC3         | 0826  | _      | _      | _          | _      | _      | QEI1IE                    | PSEMIE         | _      | _     | _           | _               | _             | _      | MI2C2IE  | SI2C2IE      | _       | 0000         |

| IEC4         | 0828  | _      | _      | CTMUIE     | _      |        |                           | _              | _      | _     | C1TXIE      | _               | _             | CRCIE  | U2EIE    | U1EIE        | _       | 0000         |

| IEC5         | 082A  | PWM2IE | PWM1IE | _          | _      | _      |                           | _              | _      | _     | _           | _               | _             | _      | _        | _            | _       | 0000         |

| IEC6         | 082C  | _      | _      | _          | _      | _      |                           | _              | _      | _     | _           | _               | _             | _      | _        | _            | PWM3IE  | 0000         |

| IEC7         | 082E  | _      | _      | _          | _      | _      |                           | _              | _      | _     | _           | _               | _             | _      | _        | _            | _       | 0000         |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _      | _      |                           | _              | _      | _     | _           | _               | _             | _      | _        | _            | _       | 0000         |

| IEC9         | 0832  | _      | _      | _          | _      | _      |                           | _              | _      | _     | PTG3IE      | PTG2IE          | PTG1IE        | PTG0IE | PTGWDTIE | PTGSTEPIE    | _       | 0000         |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      |                           | OC1IP<2:0      | >      | _     |             | IC1IP<2:0>      |               | _      |          | INT0IP<2:0>  |         | 4444         |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      |                           | OC2IP<2:0      | >      | _     |             | IC2IP<2:0>      |               | _      | [        | DMA0IP<2:0>  |         | 4444         |

| IPC2         | 0844  | _      | l      | J1RXIP<2:0 | >      | _      |                           | SPI1IP<2:0     | )>     | _     |             | SPI1EIP<2:0     | >             |        |          | T3IP<2:0>    |         | 4444         |

| IPC3         | 0846  | _      | _      | _          | _      | _      | C                         | MA1IP<2:       | 0>     | _     |             | AD1IP<2:0>      |               |        |          | U1TXIP<2:0>  |         | 0444         |

| IPC4         | 0848  | _      |        | CNIP<2:0>  |        | _      |                           | CMIP<2:0       | >      | _     |             | MI2C1IP<2:0     | >             |        | 5        | SI2C1IP<2:0> |         | 4444         |

| IPC5         | 084A  | _      | _      | _          | _      | _      |                           | _              | _      | _     | _           | _               | _             |        |          | INT1IP<2:0>  |         | 0004         |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      |                           | OC4IP<2:0      | >      | _     |             | OC3IP<2:0>      |               |        | [        | DMA2IP<2:0>  |         | 4444         |

| IPC7         | 084E  | _      | 1      | U2TXIP<2:0 | >      | _      | U2RXIP<2:0> — INT2IP<2:0> |                |        |       | T5IP<2:0>   |                 | 4444          |        |          |              |         |              |

| IPC8         | 0850  | _      |        | C1IP<2:0>  |        | _      | C                         | 2:<br>2:<br>2: | 0>     | _     |             | SPI2IP<2:0>     |               |        | 5        | SPI2EIP<2:0> |         | 4444         |

| IPC9         | 0852  | _      | _      | _          | _      | _      |                           | IC4IP<2:0      | >      | _     |             | IC3IP<2:0>      |               |        | [        | DMA3IP<2:0>  |         | 0444         |

| IPC12        | 0858  | _      | _      | _          | _      | _      | N                         | 112C2IP<2:     | 0>     | _     |             | SI2C2IP<2:0     | >             | _      | _        | _            | _       | 0440         |

| IPC14        | 085C  | _      | _      | _          | _      | _      | (                         | QEI1IP<2:(     | )>     | _     | PSEMIP<2:0> |                 | >             | _      | _        | _            | _       | 0440         |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >      | _      |                           | U2EIP<2:0      |        | _     |             |                 |               | _      | <u> </u> | _            | _       | 4440         |

| IPC17        | 0862  | _      | _      | _          | _      | _      |                           | C1TXIP<2:      |        | _     |             |                 | —             | _      | _        | _            | _       | 0400         |

| IPC19        | 0866  | _      | _      |            | _      | _      |                           |                |        |       |             | L<br>CTMUIP<2:0 | >             |        | <u> </u> | _            | _       | 0040         |

### TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

DS70000657H-page 73

| TABLE 4   | 4-9:  | INPUT                           |                                                 | JRE 1 T | HROUG  | H INPU    | Т САРТ | URE 4 | REGIST       | ER MA        | Р        |       |       |       |          |          |       |               |

|-----------|-------|---------------------------------|-------------------------------------------------|---------|--------|-----------|--------|-------|--------------|--------------|----------|-------|-------|-------|----------|----------|-------|---------------|

| File Name | Addr. | Bit 15                          | Bit 14                                          | Bit 13  | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1    | Bit 0 | All<br>Resets |

| IC1CON1   | 0140  | _                               | —                                               | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | -            | _            | ICI<     | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC1CON2   | 0142  | _                               | _                                               |         | _      |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC1BUF    | 0144  |                                 |                                                 |         |        |           |        | Inp   | ut Capture ' | 1 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC1TMR    | 0146  |                                 | Input Capture 1 Timer                           |         |        |           |        |       |              |              |          |       |       |       |          | 0000     |       |               |

| IC2CON1   | 0148  |                                 | ICSIDL ICTSEL<2:0> ICI<1:0> ICOV ICBNE ICM<2:0> |         |        |           |        |       |              |              |          |       |       |       |          | 0000     |       |               |

| IC2CON2   | 014A  |                                 |                                                 |         |        |           |        |       |              |              |          |       |       |       |          | 000D     |       |               |

| IC2BUF    | 014C  |                                 | Input Capture 2 Buffer Register                 |         |        |           |        |       |              |              |          |       |       |       |          |          | xxxx  |               |

| IC2TMR    | 014E  |                                 |                                                 |         |        |           |        |       | Input Capt   | ture 2 Time  | r        |       |       |       |          |          |       | 0000          |

| IC3CON1   | 0150  |                                 | _                                               | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC3CON2   | 0152  |                                 | _                                               |         |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC3BUF    | 0154  |                                 |                                                 |         |        |           |        | Inp   | ut Capture 3 | 3 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC3TMR    | 0156  |                                 |                                                 |         |        |           |        |       | Input Capt   | ture 3 Time  | r        |       |       |       |          |          |       | 0000          |

| IC4CON1   | 0158  |                                 | _                                               | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC4CON2   | 015A  | _                               | _                                               |         | -      |           | -      | _     | IC32         | ICTRIG       | TRIGSTAT | -     |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC4BUF    | 015C  | Input Capture 4 Buffer Register |                                                 |         |        |           |        |       |              |              |          |       |       | xxxx  |          |          |       |               |

| IC4TMR    | 015E  |                                 |                                                 |         |        |           |        |       | Input Capt   | ure 4 Time   | r        |       |       |       |          |          |       | 0000          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-27: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC204/504 AND PIC24EPXXXGP/MC204 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5         | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |  |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|-------|---------------|-------|-------|--------|-------|-------|---------------|--|

| RPOR0        | 0680  |        |        |        | RP35R<5:0> |        |        |       |       |       |       |               |       | RP20F | ₹<5:0> |       |       | 0000          |  |

| RPOR1        | 0682  | _      | _      |        | RP37R<5:0> |        |        |       |       |       | —     | RP36R<5:0> 01 |       |       |        |       |       |               |  |

| RPOR2        | 0684  | _      | _      |        |            | RP39   | R<5:0> |       |       |       | —     | RP38R<5:0>    |       |       |        |       |       |               |  |

| RPOR3        | 0686  | _      | _      |        |            | RP41   | R<5:0> |       |       |       | —     | RP40R<5:0>    |       |       |        |       |       |               |  |

| RPOR4        | 0688  | _      | _      |        |            | RP43   | R<5:0> |       |       |       | —     | RP42R<5:0>    |       |       |        |       |       | 0000          |  |

| RPOR5        | 068A  | _      | —      |        | RP55R<5:0> |        |        |       |       |       | —     | RP54R<5:0>    |       |       |        |       |       | 0000          |  |

| RPOR6        | 068C  | _      | —      |        | RP57R<5:0> |        |        |       |       | _     | —     |               |       | RP56F | R<5:0> |       |       | 0000          |  |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-28: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC206/506 AND PIC24EPXXXGP/MC206 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12      | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5       | Bit 4      | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |  |

|--------------|-------|--------|--------|--------|-------------|--------|--------|-------|-------|-------|-------|-------------|------------|-------|--------|-------|-------|---------------|--|

| RPOR0        | 0680  | _      | _      |        | RP35R<5:0>  |        |        |       |       | _     | _     |             | •          | RP20F | R<5:0> |       |       | 0000          |  |

| RPOR1        | 0682  | _      |        |        |             | RP37F  | R<5:0> |       |       | _     | _     |             |            | RP36  | R<5:0> |       |       | 0000          |  |

| RPOR2        | 0684  | _      | —      |        |             | RP39F  | २<5:0> |       |       | _     | _     | RP38R<5:0>  |            |       |        |       |       |               |  |

| RPOR3        | 0686  | _      | —      |        |             | RP41F  | २<5:0> |       |       | _     | _     |             | RP40R<5:0> |       |        |       |       |               |  |

| RPOR4        | 0688  | _      | _      |        |             | RP43F  | २<5:0> |       |       | —     | _     |             | RP42R<5:0> |       |        |       |       |               |  |

| RPOR5        | 068A  | _      | _      |        |             | RP55F  | २<5:0> |       |       | —     | _     | RP54R<5:0>  |            |       |        |       |       | 0000          |  |

| RPOR6        | 068C  | _      | _      |        |             | RP57F  | २<5:0> |       |       | —     | _     |             |            | RP56  | R<5:0> |       |       | 0000          |  |

| RPOR7        | 068E  | _      | _      |        | RP97R<5:0>  |        |        |       |       | —     | _     | _           | _          | _     | _      | _     | _     | 0000          |  |

| RPOR8        | 0690  |        | _      |        | RP118R<5:0> |        |        |       |       | _     | _     |             |            |       |        |       |       | 0000          |  |

| RPOR9        | 0692  | —      | _      | _      |             |        |        |       | _     | _     | _     | RP120R<5:0> |            |       |        |       |       | 0000          |  |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-37: PMD REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     | _     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      |       | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  |        | _      | _      | —      | _      | CMPMD  | _     | -     | CRCMD  | _     |       |        |        | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  |        | _      | _      | —      | _      |        | _     | -     | —      | _     |       |        | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  |        | _      |        | —      | _      |        | _     |       | —      | _     |       |        |        | —      | —      |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  | _      |        |        | _      |        |        |       |       |        |       |       | DMA1MD | PTGMD  | _      |        |       | 0000          |

|              | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-38: PMD REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  |        | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      |        | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | —      | -      | _      |        |        | PWM3MD | PWM2MD | PWM1MD | _      | —     | —     | _      |        | —      | _      |       | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

|                                                     | Vector  | IRQ        |                   | Inte     | errupt Bit L | ocation      |

|-----------------------------------------------------|---------|------------|-------------------|----------|--------------|--------------|

| Interrupt Source                                    | #       | #          | IVT Address       | Flag     | Enable       | Priority     |

| QEI1 – QEI1 Position Counter Compare <sup>(2)</sup> | 66      | 58         | 0x000088          | IFS3<10> | IEC3<10>     | IPC14<10:8>  |

| Reserved                                            | 67-72   | 59-64      | 0x00008A-0x000094 | _        | _            | _            |

| U1E – UART1 Error Interrupt                         | 73      | 65         | 0x000096          | IFS4<1>  | IEC4<1>      | IPC16<6:4>   |

| U2E – UART2 Error Interrupt                         | 74      | 66         | 0x000098          | IFS4<2>  | IEC4<2>      | IPC16<10:8>  |

| CRC – CRC Generator Interrupt                       | 75      | 67         | 0x00009A          | IFS4<3>  | IEC4<3>      | IPC16<14:12> |

| Reserved                                            | 76-77   | 68-69      | 0x00009C-0x00009E | —        | _            | —            |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>          | 78      | 70         | 0x000A0           | IFS4<6>  | IEC4<6>      | IPC17<10:8>  |

| Reserved                                            | 79-84   | 71-76      | 0x0000A2-0x0000AC | —        | _            | —            |

| CTMU – CTMU Interrupt                               | 85      | 77         | 0x0000AE          | IFS4<13> | IEC4<13>     | IPC19<6:4>   |

| Reserved                                            | 86-101  | 78-93      | 0x0000B0-0x0000CE | —        | _            | —            |

| PWM1 – PWM Generator 1 <sup>(2)</sup>               | 102     | 94         | 0x0000D0          | IFS5<14> | IEC5<14>     | IPC23<10:8>  |

| PWM2 – PWM Generator 2 <sup>(2)</sup>               | 103     | 95         | 0x0000D2          | IFS5<15> | IEC5<15>     | IPC23<14:12> |

| PWM3 – PWM Generator 3 <sup>(2)</sup>               | 104     | 96         | 0x0000D4          | IFS6<0>  | IEC6<0>      | IPC24<2:0>   |

| Reserved                                            | 105-149 | 97-141     | 0x0001D6-0x00012E | —        | _            | —            |

| ICD – ICD Application                               | 150     | 142        | 0x000142          | IFS8<14> | IEC8<14>     | IPC35<10:8>  |

| JTAG – JTAG Programming                             | 151     | 143        | 0x000130          | IFS8<15> | IEC8<15>     | IPC35<14:12> |

| Reserved                                            | 152     | 144        | 0x000134          | —        | —            | _            |

| PTGSTEP – PTG Step                                  | 153     | 145        | 0x000136          | IFS9<1>  | IEC9<1>      | IPC36<6:4>   |

| PTGWDT – PTG Watchdog Time-out                      | 154     | 146        | 0x000138          | IFS9<2>  | IEC9<2>      | IPC36<10:8>  |

| PTG0 – PTG Interrupt 0                              | 155     | 147        | 0x00013A          | IFS9<3>  | IEC9<3>      | IPC36<14:12> |

| PTG1 – PTG Interrupt 1                              | 156     | 148        | 0x00013C          | IFS9<4>  | IEC9<4>      | IPC37<2:0>   |

| PTG2 – PTG Interrupt 2                              | 157     | 149        | 0x00013E          | IFS9<5>  | IEC9<5>      | IPC37<6:4>   |

| PTG3 – PTG Interrupt 3                              | 158     | 150        | 0x000140          | IFS9<6>  | IEC9<6>      | IPC37<10:8>  |

| Reserved                                            | 159-245 | 151-245    | 0x000142-0x0001FE | —        | —            | _            |

|                                                     | Lowe    | est Natura | I Order Priority  |          |              |              |

## TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

| R/W-0         | R/W-0        | R/W-0                                                 | R/W-0   | R/W-0             | R/W-0                 | R/W-0                | U-0   |

|---------------|--------------|-------------------------------------------------------|---------|-------------------|-----------------------|----------------------|-------|

| T5MD          | T4MD         | T3MD                                                  | T2MD    | T1MD              | QEI1MD <sup>(1)</sup> | PWMMD <sup>(1)</sup> | _     |

| bit 15        |              |                                                       |         |                   |                       |                      | bit   |

|               |              |                                                       |         |                   |                       |                      |       |

| R/W-0         | R/W-0        | R/W-0                                                 | R/W-0   | R/W-0             | U-0                   | R/W-0                | R/W-0 |

| I2C1MD        | U2MD         | U1MD                                                  | SPI2MD  | SPI1MD            | —                     | C1MD <sup>(2)</sup>  | AD1MD |

| bit 7         |              |                                                       |         |                   |                       |                      | bit   |

| Legend:       |              |                                                       |         |                   |                       |                      |       |

| R = Readabl   | e bit        | W = Writable                                          | bit     | U = Unimplen      | nented bit, read      | d as '0'             |       |

| -n = Value at | POR          | '1' = Bit is set                                      |         | '0' = Bit is clea | ared                  | x = Bit is unkno     | own   |

| bit 15        | 1 = Timer5 m | 5 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 14        | 1 = Timer4 m | 4 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 13        | 1 = Timer3 m | 3 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 12        | 1 = Timer2 m | 2 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 11        | 1 = Timer1 m | 1 Module Disal<br>odule is disable<br>odule is enable | ed      |                   |                       |                      |       |

| bit 10        | 1 = QEI1 mod | 11 Module Disa<br>Iule is disablec<br>Iule is enabled |         |                   |                       |                      |       |

| bit 9         | 1 = PWM mod  | /M Module Dis<br>dule is disabled<br>dule is enabled  | 1       |                   |                       |                      |       |

| bit 8         | Unimplemen   | ted: Read as '                                        | כי      |                   |                       |                      |       |

| bit 7         | 1 = I2C1 mod | 1 Module Disal<br>ule is disabled<br>ule is enabled   | ble bit |                   |                       |                      |       |

| bit 6         | 1 = UART2 m  | 2 Module Disa<br>odule is disabl<br>odule is enable   | ed      |                   |                       |                      |       |

| bit 5         | 1 = UART1 m  | 1 Module Disa<br>odule is disabl<br>odule is enable   | ed      |                   |                       |                      |       |

| bit 4         | 1 = SPI2 mod | 2 Module Disa<br>lule is disabled<br>lule is enabled  | ole bit |                   |                       |                      |       |

## REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This bit is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

## 11.5 I/O Helpful Tips

- 1. In some cases, certain pins, as defined in Table 30-11, under "Injection Current", have internal protection diodes to VDD and Vss. The term, "Injection Current", is also referred to as "Clamp Current". On designated pins, with sufficient external current-limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings, with respect to the Vss and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device, that is clamped internally by the VDD and Vss power rails, may affect the ADC accuracy by four to six counts.

- 2. I/O pins that are shared with any analog input pin (i.e., ANx) are always analog pins by default after any Reset. Consequently, configuring a pin as an analog input pin automatically disables the digital input pin buffer and any attempt to read the digital input level by reading PORTx or LATx will always return a '0', regardless of the digital logic level on the pin. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the Analog Pin Configuration registers in the I/O ports module (i.e., ANSELx) by setting the appropriate bit that corresponds to that I/O port pin to a '0'.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in this data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each pin has an internal weak pull-up resistor and pull-down resistor that can be configured using the CNPUx and CNPDx registers, respectively. These resistors eliminate the need for external resistors in certain applications. The internal pull-up is up to ~(VDD - 0.8), not VDD. This value is still above the minimum VIH of CMOS and TTL devices.

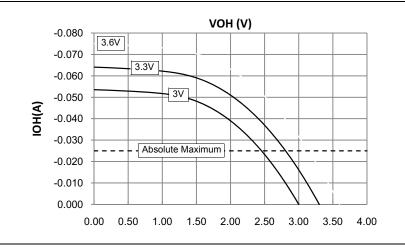

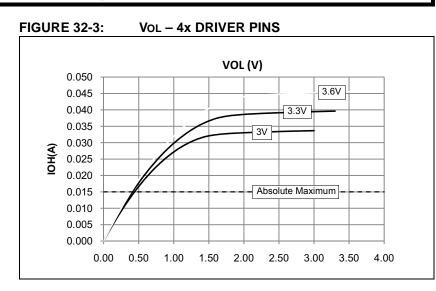

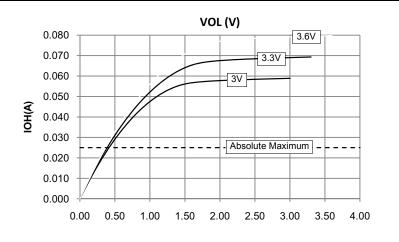

5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH, and at or below the VOL levels. However, for LEDs, unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of this data sheet. For example:

VOH = 2.4V @ IOH = -8 mA and VDD = 3.3VThe maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 30.0 "Electrical Characteristics" for additional information.

- 6. The Peripheral Pin Select (PPS) pin mapping rules are as follows:

- a) Only one "output" function can be active on a given pin at any time, regardless if it is a dedicated or remappable function (one pin, one output).

- b) It is possible to assign a "remappable output" function to multiple pins and externally short or tie them together for increased current drive.

- c) If any "dedicated output" function is enabled on a pin, it will take precedence over any remappable "output" function.

- d) If any "dedicated digital" (input or output) function is enabled on a pin, any number of "input" remappable functions can be mapped to the same pin.

- e) If any "dedicated analog" function(s) are enabled on a given pin, "digital input(s)" of any kind will all be disabled, although a single "digital output", at the user's cautionary discretion, can be enabled and active as long as there is no signal contention with an external analog input signal. For example, it is possible for the ADC to convert the digital output logic level, or to toggle a digital output on a comparator or ADC input provided there is no external analog input, such as for a built-in self-test.

- f) Any number of "input" remappable functions can be mapped to the same pin(s) at the same time, including to any pin with a single output from either a dedicated or remappable "output".

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|        |     |       |       | DD20  |         |       |       |

|--------|-----|-------|-------|-------|---------|-------|-------|

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

| bit 15 |     |       |       |       |         |       | bit 8 |

|        |     |       |       | RP35  | iR<5:0> |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

#### REGISTER 11-18: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP20  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

|       |     |       |       |       |        |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP35R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP35 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP20R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-19: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP37  | ′R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP36  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP37R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP37 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP36R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-3 for peripheral function numbers) |

## 15.2 Output Compare Control Registers

## REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0        | U-0                                                                                                                                                                      | R/W-0                                              | R/W-0           | R/W-0             | R/W-0            | U-0             | R/W-0  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------|-------------------|------------------|-----------------|--------|--|

| 0-0        | 0-0                                                                                                                                                                      | OCSIDL                                             | OCTSEL2         | OCTSEL1           | OCTSEL0          | 0-0             | ENFLTB |  |

| <br>bit 15 |                                                                                                                                                                          | OCSIDE                                             | OCTSEL2         | OCISELI           | OCTSELU          | —               | bit 8  |  |

| DIL 15     | Dit o                                                                                                                                                                    |                                                    |                 |                   |                  |                 |        |  |

| R/W-0      | U-0                                                                                                                                                                      | R/W-0, HSC                                         | R/W-0, HSC      | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |

| ENFLTA     |                                                                                                                                                                          | OCFLTB                                             | OCFLTA          | TRIGMODE          | OCM2             | OCM1            | OCM0   |  |

| bit 7      |                                                                                                                                                                          | 001218                                             | OOFEIN          | ITTOMODE          | 001112           | 0.0111          | bit 0  |  |

|            |                                                                                                                                                                          |                                                    |                 |                   |                  |                 | 2.1.0  |  |

| Legend:    |                                                                                                                                                                          | HSC = Hardw                                        | are Settable/Cl | earable bit       |                  |                 |        |  |

| R = Read   | able bit                                                                                                                                                                 | W = Writable I                                     | bit             | U = Unimplem      | nented bit, read | as '0'          |        |  |

| -n = Value | e at POR                                                                                                                                                                 | '1' = Bit is set                                   |                 | '0' = Bit is clea | ared             | x = Bit is unkn | own    |  |

|            |                                                                                                                                                                          |                                                    |                 |                   |                  |                 |        |  |

| bit 15-14  | Unimplemen                                                                                                                                                               | ted: Read as 'o                                    | )'              |                   |                  |                 |        |  |

| bit 13     | OCSIDL: Out                                                                                                                                                              | tput Compare x                                     | Stop in Idle Mo | de Control bit    |                  |                 |        |  |

|            |                                                                                                                                                                          | compare x Halts                                    |                 |                   |                  |                 |        |  |

|            | •                                                                                                                                                                        | compare x conti                                    | •               |                   | ode              |                 |        |  |

| bit 12-10  |                                                                                                                                                                          | D>: Output Com                                     | pare x Clock Se | elect bits        |                  |                 |        |  |

|            | 111 = Periph<br>110 = Reserv                                                                                                                                             | eral clock (FP)                                    |                 |                   |                  |                 |        |  |

|            | 101 = PTGO                                                                                                                                                               |                                                    |                 |                   |                  |                 |        |  |

|            |                                                                                                                                                                          | is the clock so                                    | urce of the OC  | k (only the sync  | hronous clock    | is supported)   |        |  |

|            |                                                                                                                                                                          | is the clock so                                    |                 |                   |                  |                 |        |  |

|            |                                                                                                                                                                          | is the clock so                                    |                 |                   |                  |                 |        |  |

|            |                                                                                                                                                                          | ( is the clock so<br>( is the clock so             |                 |                   |                  |                 |        |  |

| bit 9      |                                                                                                                                                                          | ted: Read as '0                                    |                 | -                 |                  |                 |        |  |

| bit 8      | -                                                                                                                                                                        | ult B Input Enab                                   |                 |                   |                  |                 |        |  |

|            |                                                                                                                                                                          | ompare Fault B                                     |                 | is enabled        |                  |                 |        |  |

|            | -                                                                                                                                                                        | compare Fault B                                    |                 | is disabled       |                  |                 |        |  |

| bit 7      |                                                                                                                                                                          | ult A Input Enab                                   |                 |                   |                  |                 |        |  |

|            |                                                                                                                                                                          | Compare Fault A<br>Compare Fault A                 |                 |                   |                  |                 |        |  |

| bit 6      | •                                                                                                                                                                        | •                                                  | ,               | is disabled       |                  |                 |        |  |

| bit 5      | -                                                                                                                                                                        | i <b>ted:</b> Read as '0<br>VM Fault B Cond        |                 |                   |                  |                 |        |  |

| DIL 5      |                                                                                                                                                                          | ult B condition of                                 |                 |                   |                  |                 |        |  |

|            |                                                                                                                                                                          | I Fault B condition                                |                 |                   |                  |                 |        |  |

| bit 4      | OCFLTA: PW                                                                                                                                                               | OCFLTA: PWM Fault A Condition Status bit           |                 |                   |                  |                 |        |  |

|            | 1 = PWM Fa                                                                                                                                                               | 1 = PWM Fault A condition on OCFA pin has occurred |                 |                   |                  |                 |        |  |

|            | 0 = No PWM Fault A condition on OCFA pin has occurred                                                                                                                    |                                                    |                 |                   |                  |                 |        |  |

| Note 1:    | OCxR and OCxF                                                                                                                                                            | RS are double-b                                    | ouffered in PWN | /I mode only.     |                  |                 |        |  |

| 2:         | OCxR and OCxRS are double-buffered in PWM mode only.<br>Each Output Compare x module (OCx) has one PTG clock source. See <b>Section 24.0</b> " <b>Peripheral Trigger</b> |                                                    |                 |                   |                  |                 |        |  |

|            | Generator (PTG) Module" for more information.                                                                                                                            |                                                    |                 |                   |                  |                 |        |  |

|            | PTGO4 = 0C1                                                                                                                                                              |                                                    |                 |                   |                  |                 |        |  |

|            | PTGO5 = OC2<br>PTGO6 = OC3                                                                                                                                               |                                                    |                 |                   |                  |                 |        |  |

|            | PTGO6 = OC3 $PTGO7 = OC4$                                                                                                                                                |                                                    |                 |                   |                  |                 |        |  |

|            |                                                                                                                                                                          |                                                    |                 |                   |                  |                 |        |  |

## **19.2** I<sup>2</sup>C Control Registers

#### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0            | U-0                             | R/W-0                                                                 | R/W-1, HC            | R/W-0                        | R/W-0             | R/W-0           | R/W-0          |  |

|------------------|---------------------------------|-----------------------------------------------------------------------|----------------------|------------------------------|-------------------|-----------------|----------------|--|

| I2CEN            | —                               | I2CSIDL                                                               | SCLREL               | IPMIEN <sup>(1)</sup>        | A10M              | DISSLW          | SMEN           |  |

| bit 15           |                                 |                                                                       |                      |                              |                   |                 | bit 8          |  |

|                  |                                 |                                                                       |                      |                              |                   |                 |                |  |

| R/W-0            | R/W-0                           | R/W-0                                                                 | R/W-0, HC            | R/W-0, HC                    | R/W-0, HC         | R/W-0, HC       | R/W-0, HC      |  |

| GCEN             | STREN                           | ACKDT                                                                 | ACKEN                | RCEN                         | PEN               | RSEN            | SEN            |  |

| bit 7            |                                 |                                                                       |                      |                              |                   |                 | bit 0          |  |

| Legend:          |                                 | HC = Hardware                                                         | Clearable bit        |                              |                   |                 |                |  |

| R = Readab       | le bit                          | W = Writable bi                                                       |                      | U = Unimpler                 | mented bit, rea   | d as '0'        |                |  |

| -n = Value a     | It POR                          | '1' = Bit is set                                                      |                      | '0' = Bit is cle             |                   | x = Bit is unk  | nown           |  |

|                  |                                 |                                                                       |                      |                              |                   |                 |                |  |

| bit 15           | I2CEN: I2Cx                     | Enable bit                                                            |                      |                              |                   |                 |                |  |

|                  |                                 | the I2Cx module                                                       |                      |                              |                   |                 | ;              |  |

| L:1 4 4          |                                 | the I2Cx module                                                       | ; all I-C ™ pins a   | are controlled               | by port function  | IS              |                |  |

| bit 14<br>bit 13 | -                               | ited: Read as '0'                                                     | do bit               |                              |                   |                 |                |  |

| DIC 13           |                                 | Stop in Idle Mo<br>ues module oper                                    |                      | rice enters an l             | dle mode          |                 |                |  |

|                  |                                 | s module operati                                                      |                      |                              |                   |                 |                |  |

| bit 12           | SCLREL: SC                      | Lx Release Con                                                        | rol bit (when op     | perating as I <sup>2</sup> C | slave)            |                 |                |  |

|                  | 1 = Releases                    |                                                                       |                      |                              |                   |                 |                |  |

|                  |                                 | Lx clock low (clo                                                     | ck stretch)          |                              |                   |                 |                |  |

|                  | If STREN = 1<br>Bit is R/W (i e | <u>.:</u><br>e., software can w                                       | rite '0' to initiate | e stretch and w              | rite '1' to relea | se clock) Harr  | lware is clear |  |

|                  | at the beginn                   | ing of every slav<br>reception. Hardv                                 | ve data byte tra     | ansmission. Ha               | ardware is clea   | r at the end o  |                |  |

|                  | If STREN = 0                    |                                                                       |                      |                              |                   |                 |                |  |

|                  |                                 | ., software can or                                                    |                      |                              |                   |                 |                |  |

| hit 11           | -                               | te transmission.<br>Iligent Peripheral                                |                      |                              | -                 | address byte re | eception.      |  |

| bit 11           |                                 | le is enabled; all                                                    |                      |                              |                   |                 |                |  |

|                  | $0 = IPMI \mod$                 |                                                                       |                      | , lon no me agea             |                   |                 |                |  |

| bit 10           | A10M: 10-Bit                    | Slave Address b                                                       | oit                  |                              |                   |                 |                |  |

|                  |                                 | is a 10-bit slave                                                     |                      |                              |                   |                 |                |  |

|                  |                                 | is a 7-bit slave a                                                    |                      |                              |                   |                 |                |  |

| bit 9            |                                 | able Slew Rate (                                                      |                      |                              |                   |                 |                |  |

|                  |                                 | 1 = Slew rate control is disabled<br>0 = Slew rate control is enabled |                      |                              |                   |                 |                |  |

| bit 8            |                                 | SMEN: SMBus Input Levels bit                                          |                      |                              |                   |                 |                |  |

|                  |                                 | /O pin thresholds                                                     |                      | SMBus speci                  | fication          |                 |                |  |

|                  |                                 | SMBus input thre                                                      |                      | ,                            |                   |                 |                |  |

| bit 7            | GCEN: Gene                      | eral Call Enable b                                                    | it (when operat      | ing as I <sup>2</sup> C slav | /e)               |                 |                |  |

|                  |                                 | nterrupt when a ge<br>call address disal                              |                      | ss is received ir            | n I2CxRSR (mo     | dule is enabled | for reception) |  |

|                  |                                 |                                                                       |                      |                              |                   |                 |                |  |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| _                                                                                                                                                                                                   |                                                                                                                            |                      |                         |                        |                      |                      |                      |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------|------------------------|----------------------|----------------------|----------------------|--|

| R/W-0                                                                                                                                                                                               | U-0                                                                                                                        | U-0                  | R/W-0                   | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |  |

| ADRC                                                                                                                                                                                                | —                                                                                                                          | —                    | SAMC4 <sup>(1)</sup>    | SAMC3 <sup>(1)</sup>   | SAMC2 <sup>(1)</sup> | SAMC1 <sup>(1)</sup> | SAMC0 <sup>(1)</sup> |  |

| bit 15                                                                                                                                                                                              | 5                                                                                                                          |                      |                         |                        |                      |                      |                      |  |

|                                                                                                                                                                                                     |                                                                                                                            |                      |                         |                        |                      |                      |                      |  |

| R/W-0                                                                                                                                                                                               | R/W-0                                                                                                                      | R/W-0                | R/W-0                   | R/W-0                  | R/W-0                | R/W-0                | R/W-0                |  |

| ADCS7 <sup>(2)</sup>                                                                                                                                                                                | ADCS6 <sup>(2)</sup>                                                                                                       | ADCS5 <sup>(2)</sup> | ADCS4 <sup>(2)</sup>    | ADCS3 <sup>(2)</sup>   | ADCS2 <sup>(2)</sup> | ADCS1 <sup>(2)</sup> | ADCS0 <sup>(2)</sup> |  |

| bit 7                                                                                                                                                                                               |                                                                                                                            |                      |                         |                        |                      |                      | bit 0                |  |

| r                                                                                                                                                                                                   |                                                                                                                            |                      |                         |                        |                      |                      |                      |  |

| Legend:                                                                                                                                                                                             |                                                                                                                            |                      |                         |                        |                      |                      |                      |  |

| R = Readable b                                                                                                                                                                                      |                                                                                                                            | W = Writable k       | bit                     | •                      | nented bit, read     | l as '0'             |                      |  |

| -n = Value at P                                                                                                                                                                                     | OR                                                                                                                         | '1' = Bit is set     |                         | '0' = Bit is clea      | ared                 | x = Bit is unkr      | nown                 |  |

| bit 15                                                                                                                                                                                              | 1 = ADC inter                                                                                                              |                      |                         |                        |                      |                      |                      |  |