Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                   |

|---------------------------|-----------------------------------------------------------------------------------|

| Product Status            | Obsolete                                                                          |

| Core Processor            | dsPIC                                                                             |

| Core Size                 | 16-Bit                                                                            |

| Speed                     | 60 MIPs                                                                           |

| Connectivity              | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                      |

| Peripherals               | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                     |

| lumber of I/O             | 35                                                                                |

| Program Memory Size       | 512KB (170K x 24)                                                                 |

| rogram Memory Type        | FLASH                                                                             |

| EPROM Size                | -                                                                                 |

| AM Size                   | 24K x 16                                                                          |

| oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Oata Converters           | A/D 9x10b/12b                                                                     |

| Scillator Type            | Internal                                                                          |

| perating Temperature      | -40°C ~ 125°C (TA)                                                                |

| Nounting Type             | Surface Mount                                                                     |

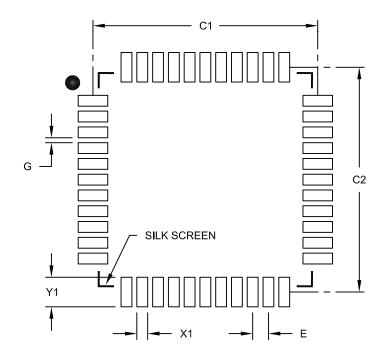

| ackage / Case             | 44-TQFP                                                                           |

| Supplier Device Package   | 44-TQFP (10x10)                                                                   |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc504t-e-pt |

TABLE 2: dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X MOTOR CONTROL FAMILIES

|                   |                                | (s                            |              |                      |               | Rei            | nappa                                          | ble Pe                       | eriphe | erals               |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

|-------------------|--------------------------------|-------------------------------|--------------|----------------------|---------------|----------------|------------------------------------------------|------------------------------|--------|---------------------|------------------|------------------------------------|---------|---------------|------------------------------|---------------------|------|-----|----------|-----------|--------------------------------|

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbytes) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM <sup>(4)</sup><br>(Channels) | Quadrature Encoder Interface | UART   | ( <sub>2</sub> )IdS | ECAN™ Technology | External Interrupts <sup>(3)</sup> | м_12Стм | CRC Generator | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | ОШТЭ | PTG | I/O Pins | Pins      | Packages                       |

| PIC24EP32MC202    | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| PIC24EP64MC202    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           | SPDIP,                         |

| PIC24EP128MC202   | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   | _                | 3                                  | 2       | 1             | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| PIC24EP256MC202   | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           | QFN-S                          |

| PIC24EP512MC202   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| PIC24EP32MC203    | 512                            | 32                            | 4            | ٠.                   | 4             | _              | _                                              | 1                            | ٠      | ٥                   |                  | ٠                                  | ٥       | 4             | •                            | 2/4                 | V    | V   | ٥.       | 00        | \                              |

| PIC24EP64MC203    | 1024                           | 64                            | 8            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   | _                | 3                                  | 2       | 1             | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| PIC24EP32MC204    | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| PIC24EP64MC204    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> ,          |

| PIC24EP128MC204   | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   | _                | 3                                  | 2       | 1             | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| PIC24EP256MC204   | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          | 70        | UQFN                           |

| PIC24EP512MC204   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| PIC24EP64MC206    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| PIC24EP128MC206   | 1024                           | 128                           | 16           | _                    |               |                |                                                |                              | •      |                     |                  | •                                  |         |               | 40                           | 0/4                 |      |     |          | 0.4       | TQFP,                          |

| PIC24EP256MC206   | 1024                           | 256                           | 32           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   | _                | 3                                  | 2       | 1             | 16                           | 3/4                 | Yes  | Yes | 53       | 64        | QFN                            |

| PIC24EP512MC206   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC202  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC202  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           | SPDIP,                         |

| dsPIC33EP128MC202 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   | _                | 3                                  | 2       | 1             | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| dsPIC33EP256MC202 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           | QFN-S                          |

| dsPIC33EP512MC202 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC203  | 512                            | 32                            | 4            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   |                  | 3                                  | 2       | 1             | 8                            | 3/4                 | Von  | Voo | 25       | 36        | VTLA                           |

| dsPIC33EP64MC203  | 1024                           | 64                            | 8            | ດ                    | 4             | 4              | 0                                              | ı                            | 2      | 2                   |                  | 9                                  | 2       | ı             | 0                            | 3/4                 | Yes  | Yes | 25       | 30        | VILA                           |

| dsPIC33EP32MC204  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC204  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          | 441       | VTLA <sup>(5)</sup> ,          |

| dsPIC33EP128MC204 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   | _                | 3                                  | 2       | 1             | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| dsPIC33EP256MC204 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          | 10        | UQFN                           |

| dsPIC33EP512MC204 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC206  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP128MC206 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   |                  | 3                                  | 2       | 1             | 16                           | 3/4                 | Yes  | Yes | 53       | 64        | TQFP,                          |

| dsPIC33EP256MC206 | 1024                           | 256                           | 32           | 3                    | 4             | 4              | ٥                                              | '                            | 2      | 2                   | _                | 3                                  | 2       | '             | 10                           | 3/4                 | 163  | 163 | 55       | 04        | QFN                            |

| dsPIC33EP512MC206 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC502  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC502  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           | SPDIP,                         |

| dsPIC33EP128MC502 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   | 1                | 3                                  | 2       | 1             | 6                            | 2/3 <sup>(1)</sup>  | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| dsPIC33EP256MC502 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           | QFN-S                          |

| dsPIC33EP512MC502 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                     |                  |                                    |         |               |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC503  | 512                            | 32                            | 4            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                   | 1                | 3                                  | 2       | 1             | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| dsPIC33EP64MC503  | 1024                           | 64                            | 8            | J                    | -             | 7              | J                                              | •                            |        | _                   | 1                | 3                                  | _       | '             | J                            | 0/7                 | 100  | 103 | 20       | - 50      | VILA                           |

Note 1: On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details.

<sup>2:</sup> Only SPI2 is remappable.

<sup>3:</sup> INT0 is not remappable.

<sup>4:</sup> Only the PWM Faults are remappable.

<sup>5:</sup> The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

TABLE 4-27: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC204/504 AND PIC24EPXXXGP/MC204 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5      | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|------------|------------|-------|--------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | _      |        | RP35R<5:0> |        |        |       | _     | _     | RP20R<5:0> |            |       |        |        |       |       |               |

| RPOR1        | 0682  | _      | _      |        | RP37R<5:0> |        |        |       | _     | _     |            |            | RP36F | R<5:0> |        |       | 0000  |               |

| RPOR2        | 0684  | _      | _      |        |            | RP39F  | R<5:0> |       |       | _     | _          | RP38R<5:0> |       |        |        |       |       | 0000          |

| RPOR3        | 0686  | ı      | _      |        |            | RP41F  | R<5:0> |       |       | _     | _          | RP40R<5:0> |       |        |        |       |       | 0000          |

| RPOR4        | 0688  | -      | _      |        |            | RP43F  | R<5:0> |       |       | _     | _          | RP42R<5:0> |       |        |        |       | 0000  |               |

| RPOR5        | 068A  | -      | _      |        | RP55R<5:0> |        |        |       | _     | _     |            |            | RP54F | R<5:0> |        |       | 0000  |               |

| RPOR6        | 068C  | _      | _      |        | RP57R<5:0> |        |        |       |       | _     | _          | •          | •     | RP56F  | R<5:0> |       |       | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-28: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC206/506 AND PIC24EPXXXGP/MC206 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | it 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 |       |        |  |   | Bit 7 | Bit 6       | Bit 5 | Bit 4      | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|----------------------------------------|-------|--------|--|---|-------|-------------|-------|------------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | _      |        |                                        | RP35F | R<5:0> |  |   | _     | _           |       |            | RP20F | R<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      | _      |        |                                        | RP37F | R<5:0> |  |   | _     | _           |       |            | RP36F | R<5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        |                                        | RP39F | R<5:0> |  |   | _     | _           |       |            | RP38F | R<5:0> |       |       | 0000          |

| RPOR3        | 0686  | _      | _      |        |                                        | RP41F | R<5:0> |  |   | _     | _           |       | RP40R<5:0> |       |        |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |                                        | RP43F | R<5:0> |  |   | _     | _           |       | RP42R<5:0> |       |        |       |       | 0000          |

| RPOR5        | 068A  | _      | _      |        |                                        | RP55F | R<5:0> |  |   | _     | _           |       | RP54R<5:0> |       |        |       | 0000  |               |

| RPOR6        | 068C  | _      | _      |        |                                        | RP57F | R<5:0> |  |   | _     | _           |       |            | RP56F | R<5:0> |       |       | 0000          |

| RPOR7        | 068E  | _      | _      |        | RP97R<5:0>                             |       |        |  | _ | _     | _           | _     | _          | _     | _      | _     | 0000  |               |

| RPOR8        | 0690  | ı      | _      |        | RP118R<5:0>                            |       |        |  | _ | _     | 1           | _     | _          | _     | _      | _     | 0000  |               |

| RPOR9        | 0692  | _      | _      | _      |                                        |       |        |  | _ | _     | RP120R<5:0> |       |            |       |        | 0000  |       |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

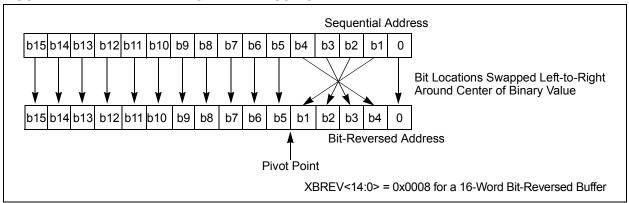

FIGURE 4-21: BIT-REVERSED ADDRESSING EXAMPLE

TABLE 4-64: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma      | al Addres | ss      |    |    | Bit-Rev    | ersed Ac | Idress  |

|----|----|------------|-----------|---------|----|----|------------|----------|---------|

| А3 | A2 | <b>A</b> 1 | Α0        | Decimal | А3 | A2 | <b>A</b> 1 | Α0       | Decimal |

| 0  | 0  | 0          | 0         | 0       | 0  | 0  | 0          | 0        | 0       |

| 0  | 0  | 0          | 1         | 1       | 1  | 0  | 0          | 0        | 8       |

| 0  | 0  | 1          | 0         | 2       | 0  | 1  | 0          | 0        | 4       |

| 0  | 0  | 1          | 1         | 3       | 1  | 1  | 0          | 0        | 12      |

| 0  | 1  | 0          | 0         | 4       | 0  | 0  | 1          | 0        | 2       |

| 0  | 1  | 0          | 1         | 5       | 1  | 0  | 1          | 0        | 10      |

| 0  | 1  | 1          | 0         | 6       | 0  | 1  | 1          | 0        | 6       |

| 0  | 1  | 1          | 1         | 7       | 1  | 1  | 1          | 0        | 14      |

| 1  | 0  | 0          | 0         | 8       | 0  | 0  | 0          | 1        | 1       |

| 1  | 0  | 0          | 1         | 9       | 1  | 0  | 0          | 1        | 9       |

| 1  | 0  | 1          | 0         | 10      | 0  | 1  | 0          | 1        | 5       |

| 1  | 0  | 1          | 1         | 11      | 1  | 1  | 0          | 1        | 13      |

| 1  | 1  | 0          | 0         | 12      | 0  | 0  | 1          | 1        | 3       |

| 1  | 1  | 0          | 1         | 13      | 1  | 0  | 1          | 1        | 11      |

| 1  | 1  | 1          | 0         | 14      | 0  | 1  | 1          | 1        | 7       |

| 1  | 1  | 1          | 1         | 15      | 1  | 1  | 1          | 1        | 15      |

## REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 4 | MATHERR: Math Error Status bit                                                                        |

|-------|-------------------------------------------------------------------------------------------------------|

|       | 1 = Math error trap has occurred                                                                      |

|       | 0 = Math error trap has not occurred                                                                  |

| bit 3 | ADDRERR: Address Error Trap Status bit                                                                |

|       | <ul><li>1 = Address error trap has occurred</li><li>0 = Address error trap has not occurred</li></ul> |

| bit 2 | STKERR: Stack Error Trap Status bit                                                                   |

|       | 1 = Stack error trap has occurred                                                                     |

|       | 0 = Stack error trap has not occurred                                                                 |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit                                                    |

|       | 1 = Oscillator failure trap has occurred                                                              |

|       | 0 = Oscillator failure trap has not occurred                                                          |

| bit 0 | Unimplemented: Read as '0'                                                                            |

Note 1: These bits are available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

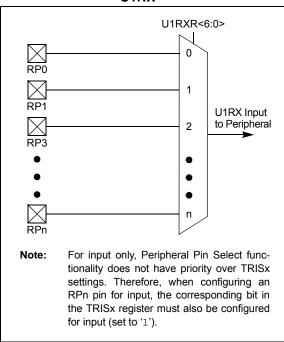

#### 11.4.4 INPUT MAPPING

The inputs of the Peripheral Pin Select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 11-1 through Register 11-17). Each register contains sets of 7-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 7-bit value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of Peripheral Pin Selections supported by the device.

For example, Figure 11-2 illustrates remappable pin selection for the U1RX input.

FIGURE 11-2: REMAPPABLE INPUT FOR U1RX

#### 11.4.4.1 Virtual Connections

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices support virtual (internal) connections to the output of the op amp/comparator module (see Figure 25-1 in Section 25.0 "Op Amp/Comparator Module"), and the PTG module (see Section 24.0 "Peripheral Trigger Generator (PTG) Module").

In addition, dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices support virtual connections to the filtered QEI module inputs: FINDX1, FHOME1, FINDX2 and FHOME2 (see Figure 17-1 in Section 17.0 "Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)".

Virtual connections provide a simple way of interperipheral connection without utilizing a physical pin. For example, by setting the FLT1R<6:0> bits of the RPINR12 register to the value of 'b0000001, the output of the analog comparator, C1OUT, will be connected to the PWM Fault 1 input, which allows the analog comparator to trigger PWM Faults without the use of an actual physical pin on the device.

Virtual connection to the QEI module allows peripherals to be connected to the QEI digital filter input. To utilize this filter, the QEI module must be enabled and its inputs must be connected to a physical RPn pin. Example 11-2 illustrates how the input capture module can be connected to the QEI digital filter.

## EXAMPLE 11-2: CONNECTING IC1 TO THE HOME1 QEI1 DIGITAL FILTER INPUT ON PIN 43 OF THE dsPIC33EPXXXMC206 DEVICE

## REGISTER 11-6: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|------------|-------|-------|-------|

| _     |       |       |       | OCFAR<6:0> | >     |       |       |

| bit 7 |       |       |       |            |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 **Unimplemented:** Read as '0'

bit 6-0 OCFAR<6:0>: Assign Output Compare Fault A (OCFA) to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

:

0000001 = Input tied to CMP1

0000000 = Input tied to Vss

## REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------------|-------|-------|-------|

| _      |       |       |       | SYNCI1R<6:0 | )>    |       |       |

| bit 15 |       |       |       |             |       |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-8 SYNCI1R<6:0>: Assign PWM Synchronization Input 1 to the Corresponding RPn Pin bits

(see Table 11-2 for input pin selection numbers)

1111001 = Input tied to RPI121

.

0000001 = Input tied to CMP1 0000000 = Input tied to Vss

bit 7-0 **Unimplemented:** Read as '0'

## **REGISTER 11-26: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8**

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| _      | _   |       |       | RP118 | 3R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 RP118R<5:0>: Peripheral Output Function is Assigned to RP118 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-0 **Unimplemented:** Read as '0'

### REGISTER 11-27: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|---------|-------|-------|

| _     | _   |       |       | RP120 | OR<5:0> |       |       |

| bit 7 |     |       |       |       |         |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-6 **Unimplemented:** Read as '0'

bit 5-0 RP120R<5:0>: Peripheral Output Function is Assigned to RP120 Output Pin bits

(see Table 11-3 for peripheral function numbers)

### REGISTER 13-2: TyCON: (TIMER3 AND TIMER5) CONTROL REGISTER

| R/W-0              | U-0 | R/W-0                | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------------------|-----|----------------------|-----|-----|-----|-----|-------|

| TON <sup>(1)</sup> | _   | TSIDL <sup>(2)</sup> | _   | _   | _   | _   | _     |

| bit 15             |     |                      |     |     |     |     | bit 8 |

| U-0   | R/W-0                | R/W-0                 | R/W-0                 | U-0 | U-0 | R/W-0                | U-0   |

|-------|----------------------|-----------------------|-----------------------|-----|-----|----------------------|-------|

| _     | TGATE <sup>(1)</sup> | TCKPS1 <sup>(1)</sup> | TCKPS0 <sup>(1)</sup> | _   | _   | TCS <sup>(1,3)</sup> |       |

| bit 7 |                      |                       |                       |     |     |                      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **TON:** Timery On bit<sup>(1)</sup>

1 = Starts 16-bit Timery

0 = Stops 16-bit Timery

bit 14 **Unimplemented:** Read as '0'

bit 13 **TSIDL:** Timery Stop in Idle Mode bit<sup>(2)</sup>

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-7 **Unimplemented:** Read as '0'

bit 6 **TGATE**: Timery Gated Time Accumulation Enable bit<sup>(1)</sup>

When TCS = 1: This bit is ignored.

When TCS = 0:

1 = Gated time accumulation is enabled 0 = Gated time accumulation is disabled

bit 5-4 TCKPS<1:0>: Timery Input Clock Prescale Select bits<sup>(1)</sup>

11 = 1:256

10 = 1:64

01 = 1:8

00 = 1:1

bit 3-2 **Unimplemented:** Read as '0'

bit 1 TCS: Timery Clock Source Select bit (1,3)

1 = External clock is from pin, TyCK (on the rising edge)

0 = Internal clock (FP)

bit 0 **Unimplemented:** Read as '0'

**Note 1:** When 32-bit operation is enabled (T2CON<3> = 1), these bits have no effect on Timery operation; all timer functions are set through TxCON.

- 2: When 32-bit timer operation is enabled (T32 = 1) in the Timerx Control register (TxCON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

- 3: The TyCK pin is not available on all timers. See the "Pin Diagrams" section for the available pins.

## 17.1 QEI Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note:

In the event you are not able to access the product page using the link above, enter this URL in your browser:

http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en555464

### 17.1.1 KEY RESOURCES

- "Quadrature Encoder Interface" (DS70601) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

## 18.3 SPIx Control Registers

#### REGISTER 18-1: SPIXSTAT: SPIX STATUS AND CONTROL REGISTER

| R/W-0  | U-0 | R/W-0   | U-0 | U-0 | R/W-0 | R/W-0       | R/W-0 |

|--------|-----|---------|-----|-----|-------|-------------|-------|

| SPIEN  | _   | SPISIDL | _   | _   |       | SPIBEC<2:0> | 1     |

| bit 15 |     |         |     |     |       |             |       |

| R/W-0 | R/C-0, HS | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R-0, HS, HC | R-0, HS, HC |

|-------|-----------|--------|--------|--------|--------|-------------|-------------|

| SRMPT | SPIROV    | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF      | SPIRBF      |

| bit 7 |           |        |        |        |        | •           | bit 0       |

| Legend:           | C = Clearable bit | HS = Hardware Settable bit | t HC = Hardware Clearable bit |

|-------------------|-------------------|----------------------------|-------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, re  | ad as '0'                     |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared       | x = Bit is unknown            |

bit 15 SPIEN: SPIx Enable bit

1 = Enables the module and configures SCKx, SDOx, SDIx and  $\overline{SSx}$  as serial port pins

0 = Disables the module

bit 14 **Unimplemented:** Read as '0'

bit 13 SPISIDL: SPIx Stop in Idle Mode bit

1 = Discontinues the module operation when device enters Idle mode

0 = Continues the module operation in Idle mode

bit 12-11 **Unimplemented:** Read as '0'

bit 10-8 SPIBEC<2:0>: SPIx Buffer Element Count bits (valid in Enhanced Buffer mode)

Master mode:

Number of SPIx transfers that are pending.

Slave mode:

Number of SPIx transfers that are unread.

bit 7 SRMPT: SPIx Shift Register (SPIxSR) Empty bit (valid in Enhanced Buffer mode)

1 = SPIx Shift register is empty and Ready-To-Send or receive the data

0 = SPIx Shift register is not empty

bit 6 SPIROV: SPIx Receive Overflow Flag bit

1 = A new byte/word is completely received and discarded; the user application has not read the previous data in the SPIxBUF register

0 = No overflow has occurred

bit 5 SRXMPT: SPIx Receive FIFO Empty bit (valid in Enhanced Buffer mode)

1 = RX FIFO is empty

0 = RX FIFO is not empty

bit 4-2 SISEL<2:0>: SPIx Buffer Interrupt Mode bits (valid in Enhanced Buffer mode)

111 = Interrupt when the SPIx transmit buffer is full (SPITBF bit is set)

110 = Interrupt when last bit is shifted into SPIxSR and as a result, the TX FIFO is empty

101 = Interrupt when the last bit is shifted out of SPIxSR and the transmit is complete

100 = Interrupt when one data is shifted into the SPIxSR and as a result, the TX FIFO has one open memory location

011 = Interrupt when the SPIx receive buffer is full (SPIRBF bit is set)

010 = Interrupt when the SPIx receive buffer is 3/4 or more full

001 = Interrupt when data is available in the receive buffer (SRMPT bit is set)

000 = Interrupt when the last data in the receive buffer is read and as a result, the buffer is empty (SRXMPT bit is set)

## REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

bit 3 S: Start bit

1 = Indicates that a Start (or Repeated Start) bit has been detected last

0 = Start bit was not detected last

Hardware is set or clear when a Start, Repeated Start or Stop is detected.

bit 2 **R\_W:** Read/Write Information bit (when operating as I<sup>2</sup>C slave)

1 = Read – Indicates data transfer is output from the slave

0 = Write - Indicates data transfer is input to the slave

Hardware is set or clear after reception of an I<sup>2</sup>C device address byte.

bit 1 RBF: Receive Buffer Full Status bit

1 = Receive is complete, I2CxRCV is full

0 = Receive is not complete, I2CxRCV is empty

Hardware is set when I2CxRCV is written with a received byte. Hardware is clear when software reads

I2CxRCV.

bit 0 TBF: Transmit Buffer Full Status bit

1 = Transmit in progress, I2CxTRN is full

0 = Transmit is complete, I2CxTRN is empty

Hardware is set when software writes to I2CxTRN. Hardware is clear at completion of a data transmission.

## REGISTER 21-6: CXINTF: ECANX INTERRUPT FLAG REGISTER

| U-0    | U-0 | R-0  | R-0  | R-0  | R-0   | R-0   | R-0   |

|--------|-----|------|------|------|-------|-------|-------|

| _      | _   | TXBO | TXBP | RXBP | TXWAR | RXWAR | EWARN |

| bit 15 |     |      |      |      |       |       | bit 8 |

| R/C-0 | R/C-0 | R/C-0 | U-0 | R/C-0  | R/C-0  | R/C-0 | R/C-0 |

|-------|-------|-------|-----|--------|--------|-------|-------|

| IVRIF | WAKIF | ERRIF | _   | FIFOIF | RBOVIF | RBIF  | TBIF  |

| bit 7 |       |       |     |        |        |       | bit 0 |

| Legend:           | C = Writable bit, but only '0' can be written to clear the bit |                      |                    |  |  |  |

|-------------------|----------------------------------------------------------------|----------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0'            |                      |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                               | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                |

|-----------|---------------------------------------------------------------------------|

| bit 13    | TXBO: Transmitter in Error State Bus Off bit                              |

|           | 1 = Transmitter is in Bus Off state                                       |

|           | 0 = Transmitter is not in Bus Off state                                   |

| bit 12    | <b>TXBP:</b> Transmitter in Error State Bus Passive bit                   |

|           | 1 = Transmitter is in Bus Passive state                                   |

|           | 0 = Transmitter is not in Bus Passive state                               |

| bit 11    | <b>RXBP:</b> Receiver in Error State Bus Passive bit                      |

|           | 1 = Receiver is in Bus Passive state                                      |

|           | 0 = Receiver is not in Bus Passive state                                  |

| bit 10    | TXWAR: Transmitter in Error State Warning bit                             |

|           | 1 = Transmitter is in Error Warning state                                 |

|           | 0 = Transmitter is not in Error Warning state                             |

| bit 9     | RXWAR: Receiver in Error State Warning bit                                |

|           | 1 = Receiver is in Error Warning state                                    |

|           | 0 = Receiver is not in Error Warning state                                |

| bit 8     | <b>EWARN:</b> Transmitter or Receiver in Error State Warning bit          |

|           | 1 = Transmitter or receiver is in Error Warning state                     |

|           | 0 = Transmitter or receiver is not in Error Warning state                 |

| bit 7     | IVRIF: Invalid Message Interrupt Flag bit                                 |

|           | 1 = Interrupt request has occurred                                        |

|           | 0 = Interrupt request has not occurred                                    |

| bit 6     | WAKIF: Bus Wake-up Activity Interrupt Flag bit                            |

|           | 1 = Interrupt request has occurred                                        |

|           | 0 = Interrupt request has not occurred                                    |

| bit 5     | <b>ERRIF:</b> Error Interrupt Flag bit (multiple sources in CxINTF<13:8>) |

|           | 1 = Interrupt request has occurred                                        |

| h:+ 4     | 0 = Interrupt request has not occurred                                    |

| bit 4     | Unimplemented: Read as '0'                                                |

| bit 3     | FIFOIF: FIFO Almost Full Interrupt Flag bit                               |

|           | 1 = Interrupt request has occurred                                        |

| h:+ 0     | 0 = Interrupt request has not occurred                                    |

| bit 2     | RBOVIF: RX Buffer Overflow Interrupt Flag bit                             |

|           | 1 = Interrupt request has occurred                                        |

|           | 0 = Interrupt request has not occurred                                    |

### REGISTER 27-1: DEVID: DEVICE ID REGISTER

| R      | R | R | R      | R                     | R | R | R      |

|--------|---|---|--------|-----------------------|---|---|--------|

|        |   |   | DEVID< | 23:16> <sup>(1)</sup> |   |   |        |

| bit 23 |   |   |        |                       |   |   | bit 16 |

|        |   |   |        |                       |   |   |        |

| R      | R | R | R      | R                     | R | R | R      |

|        |   |   | DEVID< | :15:8> <sup>(1)</sup> |   |   |        |

| bit 15 |   |   |        |                       |   |   | bit 8  |

|        |   |   |        |                       |   |   | _      |

| R      | R | R | R      | R                     | R | R | R      |

|        |   |   | DEVID  | <7·0>(1)              |   |   |        |

Legend: R = Read-Only bit U = Unimplemented bit

bit 23-0 **DEVID<23:0>:** Device Identifier bits<sup>(1)</sup>

bit 7

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for the list of device ID values.

### **REGISTER 27-2: DEVREV: DEVICE REVISION REGISTER**

| bit 16                      |  |  |  |  |  |  |  |  |

|-----------------------------|--|--|--|--|--|--|--|--|

| bit 16                      |  |  |  |  |  |  |  |  |

|                             |  |  |  |  |  |  |  |  |

|                             |  |  |  |  |  |  |  |  |

| R                           |  |  |  |  |  |  |  |  |

| DEVREV<15:8> <sup>(1)</sup> |  |  |  |  |  |  |  |  |

| bit 8                       |  |  |  |  |  |  |  |  |

|                             |  |  |  |  |  |  |  |  |

| R                           |  |  |  |  |  |  |  |  |

| DEVREV<7:0> <sup>(1)</sup>  |  |  |  |  |  |  |  |  |

| bit 0                       |  |  |  |  |  |  |  |  |

|                             |  |  |  |  |  |  |  |  |

**Legend:** R = Read-only bit U = Unimplemented bit

bit 23-0 **DEVREV<23:0>:** Device Revision bits<sup>(1)</sup>

**Note 1:** Refer to the "dsPIC33E/PIC24E Flash Programming Specification for Devices with Volatile Configuration Bits" (DS70663) for the list of device revision values.

bit 0

TABLE 30-39: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                     |      |       |                             |

|--------------------|-----------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                | Min.                                                                                                                                                                                                                                             | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |

| SP70               | FscP                  | Maximum SCK2 Input Frequency                 | _                                                                                                                                                                                                                                                | _                   | 15   | MHz   | (Note 3)                    |

| SP72               | TscF                  | SCK2 Input Fall Time                         | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP73               | TscR                  | SCK2 Input Rise Time                         | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                   | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                   | _                                                                                                                                                                                                                                                | _                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after SCK2 Edge       | _                                                                                                                                                                                                                                                | 6                   | 20   | ns    |                             |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge | 30                                                                                                                                                                                                                                               | _                   | _    | ns    |                             |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge   | 30                                                                                                                                                                                                                                               | _                   | _    | ns    |                             |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge    | 30                                                                                                                                                                                                                                               | _                   | _    | ns    |                             |

| SP50               | TssL2scH,<br>TssL2scL | SS2 ↓ to SCK2 ↑ or SCK2 ↓ Input              | 120                                                                                                                                                                                                                                              | _                   | _    | ns    |                             |

| SP51               | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance       | 10                                                                                                                                                                                                                                               | _                   | 50   | ns    | (Note 4)                    |

| SP52               | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                        | 1.5 Tcy + 40                                                                                                                                                                                                                                     | _                   | _    | ns    | (Note 4)                    |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

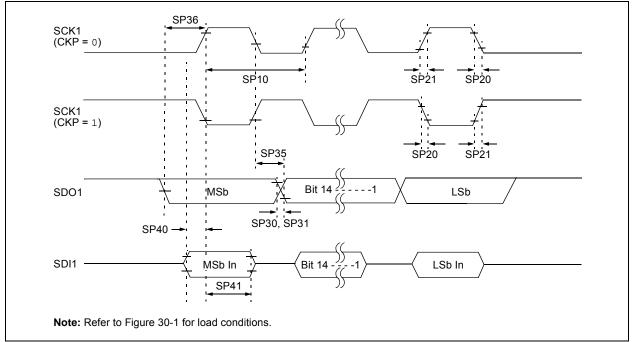

FIGURE 30-24: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

TABLE 30-43: SPI1 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING REQUIREMENTS

|        |                    |                                             | <b>.</b>                                                |                           |      |       |                    |  |  |

|--------|--------------------|---------------------------------------------|---------------------------------------------------------|---------------------------|------|-------|--------------------|--|--|

|        |                    | Standard Operating Conditions: 3.0V to 3.6V |                                                         |                           |      |       |                    |  |  |

| AC CHA | AC CHARACTERISTICS |                                             |                                                         | (unless otherwise stated) |      |       |                    |  |  |

|        |                    |                                             | Operating temperature -40°C ≤ TA ≤ +85°C for Industrial |                           |      |       |                    |  |  |

|        |                    |                                             | -40°C ≤ Ta ≤ +125°C for Extended                        |                           |      |       |                    |  |  |

| Param. | Symbol             | Characteristic <sup>(1)</sup>               | Min.                                                    | Typ. <sup>(2)</sup>       | Max. | Units | Conditions         |  |  |

| SP10   | FscP               | Maximum SCK1 Frequency                      | _                                                       | _                         | 10   | MHz   | (Note 3)           |  |  |

| SP20   | TscF               | SCK1 Output Fall Time                       | _                                                       | _                         | _    | ns    | See Parameter DO32 |  |  |

|        |                    | '                                           |                                                         |                           |      |       | (Note 4)           |  |  |

| SP21   | TscR               | SCK1 Output Rise Time                       | _                                                       | _                         | _    | ns    | See Parameter DO31 |  |  |

|        |                    | ·                                           |                                                         |                           |      |       | (Note 4)           |  |  |

| SP30   | TdoF               | SDO1 Data Output Fall Time                  | _                                                       | _                         | _    | ns    | See Parameter DO32 |  |  |

|        |                    | ·                                           |                                                         |                           |      |       | (Note 4)           |  |  |

| SP31   | TdoR               | SDO1 Data Output Rise Time                  | _                                                       | _                         | _    | ns    | See Parameter DO31 |  |  |

|        |                    | ·                                           |                                                         |                           |      |       | (Note 4)           |  |  |

| SP35   | TscH2doV,          | SDO1 Data Output Valid after                | _                                                       | 6                         | 20   | ns    |                    |  |  |

|        | TscL2doV           | SCK1 Edge                                   |                                                         |                           |      |       |                    |  |  |

| SP36   | TdoV2sc,           | SDO1 Data Output Setup to                   | 30                                                      | _                         | _    | ns    |                    |  |  |

|        | TdoV2scL           | First SCK1 Edge                             |                                                         |                           |      |       |                    |  |  |

| SP40   | TdiV2scH,          | Setup Time of SDI1 Data                     | 30                                                      | _                         | _    | ns    |                    |  |  |

|        | TdiV2scL           | Input to SCK1 Edge                          |                                                         |                           |      |       |                    |  |  |

| SP41   | TscH2diL,          | Hold Time of SDI1 Data Input                | 30                                                      |                           |      | ns    |                    |  |  |

|        | TscL2diL           | to SCK1 Edge                                |                                                         |                           |      |       |                    |  |  |

- **Note 1:** These parameters are characterized, but are not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK1 is 100 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI1 pins.

TABLE 30-49: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHARACTERISTICS |                                      |                               | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |                 |                 |              |                        |                        |    |                   |

|--------------------|--------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|--------------|------------------------|------------------------|----|-------------------|

| Param<br>No.       | Symbol Characteristic <sup>(4)</sup> |                               | Min. <sup>(1)</sup>                                                                                                                                                                                                                              | Max.            | Units           | Conditions   |                        |                        |    |                   |

| IM10               | TLO:SCL                              | Clock Low Time                | 100 kHz mode                                                                                                                                                                                                                                     | Tcy/2 (BRG + 2) | _               | μS           |                        |                        |    |                   |

|                    |                                      |                               | 400 kHz mode                                                                                                                                                                                                                                     | Tcy/2 (BRG + 2) | _               | μS           |                        |                        |    |                   |

|                    |                                      |                               | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                                                                        | Tcy/2 (BRG + 2) | _               | μS           |                        |                        |    |                   |

| IM11               | THI:SCL                              | Clock High Time               | 100 kHz mode                                                                                                                                                                                                                                     | Tcy/2 (BRG + 2) | _               | μS           |                        |                        |    |                   |

|                    |                                      |                               | 400 kHz mode                                                                                                                                                                                                                                     | Tcy/2 (BRG + 2) | _               | μS           |                        |                        |    |                   |

|                    |                                      |                               | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                                                                        | Tcy/2 (BRG + 2) | _               | μS           |                        |                        |    |                   |

| IM20               | TF:SCL                               | SDAx and SCLx                 | 100 kHz mode                                                                                                                                                                                                                                     | _               | 300             | ns           | CB is specified to be  |                        |    |                   |

|                    |                                      | Fall Time                     | 400 kHz mode                                                                                                                                                                                                                                     | 20 + 0.1 CB     | 300             | ns           | from 10 to 400 pF      |                        |    |                   |

|                    |                                      |                               | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                                                                        |                 | 100             | ns           |                        |                        |    |                   |

| IM21               | TR:SCL                               | Tr:scl                        | SDAx and SCLx                                                                                                                                                                                                                                    | 100 kHz mode    | _               | 1000         | ns                     | CB is specified to be  |    |                   |

|                    |                                      | Rise Time                     | 400 kHz mode                                                                                                                                                                                                                                     | 20 + 0.1 CB     | 300             | ns           | from 10 to 400 pF      |                        |    |                   |

|                    |                                      |                               | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                                                                        |                 | 300             | ns           |                        |                        |    |                   |

| IM25               | TSU:DAT                              | Data Input                    | 100 kHz mode                                                                                                                                                                                                                                     | 250             | _               | ns           |                        |                        |    |                   |

|                    |                                      | Setup Time                    | 400 kHz mode                                                                                                                                                                                                                                     | 100             | _               | ns           |                        |                        |    |                   |

|                    |                                      |                               | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                                                                        | 40              | _               | ns           |                        |                        |    |                   |

| IM26               | THD:DAT                              | THD:DAT                       | ID:DAT Data Input                                                                                                                                                                                                                                | 100 kHz mode    | 0               | _            | μS                     |                        |    |                   |

|                    |                                      | Hold Time                     | 400 kHz mode                                                                                                                                                                                                                                     | 0               | 0.9             | μS           |                        |                        |    |                   |

|                    |                                      |                               | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                                                                        | 0.2             | _               | μS           |                        |                        |    |                   |

| IM30               | Tsu:sta                              | Tsu:sta                       | Tsu:sta                                                                                                                                                                                                                                          | TSU:STA         | Start Condition | 100 kHz mode | Tcy/2 (BRG + 2)        | _                      | μS | Only relevant for |

|                    |                                      | Setup Time                    | 400 kHz mode                                                                                                                                                                                                                                     | Tcy/2 (BRG + 2) | _               | μS           | Repeated Start         |                        |    |                   |

|                    |                                      |                               | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                                                                        | Tcy/2 (BRG + 2) | _               | μS           | condition              |                        |    |                   |

| IM31               | THD:STA                              | THD:STA                       | Start Condition                                                                                                                                                                                                                                  | 100 kHz mode    | Tcy/2 (BRG + 2) | _            | μS                     | After this period, the |    |                   |

|                    |                                      | Hold Time                     | 400 kHz mode                                                                                                                                                                                                                                     | Tcy/2 (BRG +2)  | _               | μS           | first clock pulse is   |                        |    |                   |

|                    |                                      |                               | 1 MHz mode <sup>(2)</sup>                                                                                                                                                                                                                        | Tcy/2 (BRG + 2) | _               | μS           | generated              |                        |    |                   |

| IM33               | Tsu:sto                              | Stop Condition                | 100 kHz mode                                                                                                                                                                                                                                     | Tcy/2 (BRG + 2) | _               | μS           |                        |                        |    |                   |

|                    |                                      |                               |                                                                                                                                                                                                                                                  | S               | Setup Time      | 400 kHz mode | Tcy/2 (BRG + 2)        | _                      | μS |                   |