Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc506-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 4-6: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|------------|-------|----------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | )>      | —       |        | ICDIP<2:0  | >     | _        | —       | —           | _       | —       | _      | -           |        | 4400          |

| IPC36        | 0888  | -      | l      | PTG0IP<2:0 | )>      | _       | PT     | GWDTIP<    | 2:0>  | _        | P       | TGSTEPIP<2  | :0>     | —       | —      |             |        | 4440          |

| IPC37        | 088A  |        | _      | _          | _       | _       | F      | PTG3IP<2:0 | )>    | _        |         | PTG2IP<2:0> | >       | _       | F      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | —       | _      |            |       | —        | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | _      | —          | —       | —       | _      |            |       | —        | _       | DAE         | DOOVR   | _       | —      |             |        | 0000          |

| INTCON4      | 08C6  | -      | _      | —          | _       | _       | _      |            | _     | _        | _       | —           | —       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | -      | —      | —          | _       |         | ILR<   | 3:0>       |       |          |         |             | VECNU   | M<7:0>  |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4 | 4-31: | PER | IPHERA | L PIN S | ELECT | INPUT F | REGISTI | ER MAP | FOR ds | sPIC33E | EPXXXG | P50X D | EVICES | SONLY |  |

|---------|-------|-----|--------|---------|-------|---------|---------|--------|--------|---------|--------|--------|--------|-------|--|

|         |       |     |        |         |       |         |         |        |        |         |        |        |        |       |  |

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|------------|--------|-------|-------|-------|-------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | —      |        |        |        | INT1R<6:0> |        |       |       | _     | _     | —     | —     | —          | —     | —     | _     | 0000          |

| RPINR1       | 06A2  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       |       | INT2R<6:0> | •     |       |       | 0000          |

| RPINR3       | 06A6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ٦     | [2CKR<6:0  | >     |       |       | 0000          |

| RPINR7       | 06AE  |        |        |        |        | IC2R<6:0>  |        |       |       | _     |       |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  |        |        |        |        | IC4R<6:0>  |        |       |       | _     |       |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR18      | 06C4  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ι     | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19      | 06C6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22      | 06CC  |        |        |        | S      | CK2INR<6:0 | )>     |       |       | _     |       |       | :     | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23      | 06CE  | _      | _      | _      | —      | —          | _      | _     | —     | —     |       |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26      | 06D4  | —      | _      | _      | -      | _          | _      | —     |       | —     |       |       | (     | C1RXR<6:0  | >     |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-32:** PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|------------|--------|-------|-------|-------|-------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0    | 06A0  | _      |        |        |        | INT1R<6:0> |        |       |       | —     | —     | —     | —     | —          | —     | —     | _     | 0000          |

| RPINR1    | 06A2  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       |       | INT2R<6:0> |       |       |       | 0000          |

| RPINR3    | 06A6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | -     | F2CKR<6:0  | >     |       |       | 0000          |

| RPINR7    | 06AE  |        |        |        |        | IC2R<6:0>  |        |       |       | _     |       |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8    | 06B0  |        |        |        |        | IC4R<6:0>  |        |       |       | _     |       |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11   | 06B6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR12   | 06B8  |        |        |        |        | FLT2R<6:0> | •      |       |       | _     |       |       |       | FLT1R<6:0> | •     |       |       | 0000          |

| RPINR14   | 06BC  |        |        |        | (      | QEB1R<6:0  | >      |       |       | _     |       |       | (     | QEA1R<6:0  | >     |       |       | 0000          |

| RPINR15   | 06BE  |        |        |        | Н      | OME1R<6:0  | )>     |       |       | _     |       |       | I     | NDX1R<6:0  | >     |       |       | 0000          |

| RPINR18   | 06C4  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ι     | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19   | 06C6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22   | 06CC  | _      |        |        | S      | CK2INR<6:( | )>     |       |       | —     |       |       |       | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23   | 06CE  | _      | —      | —      |        | —          | —      |       | —     | —     |       |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26   | 06D4  | _      | _      | _      |        | —          | —      |       | —     | —     |       |       | (     | C1RXR<6:0  | >     |       |       | 0000          |

| RPINR37   | 06EA  | _      |        |        | S      | YNCI1R<6:0 | )>     |       |       | —     | —     | —     | —     | —          |       |       |       | 0000          |

| RPINR38   | 06EC  | _      |        |        | D      | CMP1R<6:   | 0>     |       |       | —     |       |       |       |            |       |       | _     | 0000          |

| RPINR39   | 06EE  | _      |        |        | D      | FCMP3R<6:  | 0>     |       |       | _     |       |       | D     | CMP2R<6:   | 0>    |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### TABLE 4-59: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | —      | _      | _      | _      | -      | _     | _     | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | _      | _     | _     | _     | _     | _     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-60: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | _       | _      | ANSB8  | _      |        | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0                 | R/W-0                                                                                                                                                                                                                                                                         | R/W-0                           | R/W-0                          | R/W-0            | U-0             | U-0             | U-0   |  |  |  |  |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|--|

| CHEN                  | SIZE                                                                                                                                                                                                                                                                          | DIR                             | HALF                           | NULLW            |                 |                 |       |  |  |  |  |  |  |

| bit 15                |                                                                                                                                                                                                                                                                               |                                 |                                |                  |                 |                 | bit   |  |  |  |  |  |  |

| U-0                   | U-0                                                                                                                                                                                                                                                                           | R/W-0                           | R/W-0                          | U-0              | U-0             | R/W-0           | R/W-0 |  |  |  |  |  |  |

|                       | 0-0                                                                                                                                                                                                                                                                           | AMODE1                          | AMODE0                         | 0-0              | 0-0             | MODE1           | MODE0 |  |  |  |  |  |  |

| bit 7                 |                                                                                                                                                                                                                                                                               | AWODET                          | 7 WIODE0                       |                  |                 | MODET           | bit   |  |  |  |  |  |  |

| Lovende               |                                                                                                                                                                                                                                                                               |                                 |                                |                  |                 |                 |       |  |  |  |  |  |  |

| Legend:<br>R = Readab | lo hit                                                                                                                                                                                                                                                                        | M - Mritabla                    | hit.                           |                  | monted bit rec  | ud aa '0'       |       |  |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                               | W = Writable                    |                                | -                | mented bit, rea |                 |       |  |  |  |  |  |  |

| -n = Value a          | IT POR                                                                                                                                                                                                                                                                        | '1' = Bit is set                |                                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |  |  |  |  |  |

| bit 15                | CHEN: DMA                                                                                                                                                                                                                                                                     | Channel Enabl                   | e bit                          |                  |                 |                 |       |  |  |  |  |  |  |

|                       | 1 = Channel<br>0 = Channel                                                                                                                                                                                                                                                    |                                 |                                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 14                |                                                                                                                                                                                                                                                                               | ata Transfer S                  | ze hit                         |                  |                 |                 |       |  |  |  |  |  |  |

|                       | 1 = Byte                                                                                                                                                                                                                                                                      |                                 |                                |                  |                 |                 |       |  |  |  |  |  |  |

|                       | 0 = Word                                                                                                                                                                                                                                                                      |                                 |                                |                  |                 |                 |       |  |  |  |  |  |  |

| bit 13                | <b>DIR:</b> DMA Transfer Direction bit (source/destination bus select)<br>1 = Reads from RAM address, writes to peripheral address                                                                                                                                            |                                 |                                |                  |                 |                 |       |  |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                               | om RAM addre<br>om peripheral a |                                | •                |                 |                 |       |  |  |  |  |  |  |

| bit 12                |                                                                                                                                                                                                                                                                               | Block Transfer                  |                                |                  |                 |                 |       |  |  |  |  |  |  |

|                       | 1 = Initiates i                                                                                                                                                                                                                                                               | nterrupt when                   | half of the data               | a has been mo    |                 |                 |       |  |  |  |  |  |  |

| bit 11                |                                                                                                                                                                                                                                                                               | Data Periphera                  |                                |                  |                 |                 |       |  |  |  |  |  |  |

|                       |                                                                                                                                                                                                                                                                               | write to periph                 |                                |                  | e (DIR bit must | also be clear)  |       |  |  |  |  |  |  |

| bit 10-6              | Unimplemen                                                                                                                                                                                                                                                                    | ted: Read as '                  | 0'                             |                  |                 |                 |       |  |  |  |  |  |  |

| bit 5-4               | AMODE<1:0                                                                                                                                                                                                                                                                     | -: DMA Chann                    | el Addressing                  | Mode Select b    | oits            |                 |       |  |  |  |  |  |  |

|                       | 11 = Reserve<br>10 = Periphe<br>01 = Register                                                                                                                                                                                                                                 |                                 | ressing mode<br>ut Post-Increm | nent mode        |                 |                 |       |  |  |  |  |  |  |

| bit 3-2               | Unimplemen                                                                                                                                                                                                                                                                    | ted: Read as '                  | 0'                             |                  |                 |                 |       |  |  |  |  |  |  |

| bit 1-0               | MODE<1:0>: DMA Channel Operating Mode Select bits                                                                                                                                                                                                                             |                                 |                                |                  |                 |                 |       |  |  |  |  |  |  |

|                       | <ul> <li>11 = One-Shot, Ping-Pong modes are enabled (one block transfer from/to each DMA buffer)</li> <li>10 = Continuous, Ping-Pong modes are enabled</li> <li>01 = One-Shot, Ping-Pong modes are disabled</li> <li>00 = Continuous, Ping-Pong modes are disabled</li> </ul> |                                 |                                |                  |                 |                 |       |  |  |  |  |  |  |

#### REGISTER 8-1: DMAXCON: DMA CHANNEL X CONTROL REGISTER

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER     | <u>R 10-2: PMD</u> 2                                                            | 2: PERIPHER                                         | AL MODULE       | DISABLE C         | ONTROL RE       | GISTER 2        |       |  |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------|-----------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|--|--|

| U-0          | U-0                                                                             | U-0                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |  |

| _            |                                                                                 | —                                                   |                 | IC4MD             | IC3MD           | IC2MD           | IC1MD |  |  |  |  |  |  |

| bit 15       |                                                                                 |                                                     |                 |                   |                 |                 | bit   |  |  |  |  |  |  |

| U-0          | U-0                                                                             | U-0                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |  |  |  |  |  |  |

|              |                                                                                 |                                                     |                 | OC4MD             | OC3MD           | OC2MD           | OC1MD |  |  |  |  |  |  |

| bit 7        |                                                                                 |                                                     |                 |                   |                 |                 | bit   |  |  |  |  |  |  |

|              |                                                                                 |                                                     |                 |                   |                 |                 |       |  |  |  |  |  |  |

| Legend:      | 1.1.1                                                                           |                                                     |                 |                   |                 |                 |       |  |  |  |  |  |  |

| R = Readab   |                                                                                 | W = Writable b                                      | Dit             | •                 | nented bit, rea |                 |       |  |  |  |  |  |  |

| -n = Value a | at POR                                                                          | '1' = Bit is set                                    |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |  |  |  |  |  |  |

| bit 15-12    | Unimplemen                                                                      | ted: Read as '0                                     | ,               |                   |                 |                 |       |  |  |  |  |  |  |

| bit 11       | -                                                                               | t Capture 4 Mod                                     |                 |                   |                 |                 |       |  |  |  |  |  |  |

|              | •                                                                               | ture 4 module is                                    |                 |                   |                 |                 |       |  |  |  |  |  |  |

|              | 0 = Input Cap                                                                   | oture 4 module is                                   | s enabled       |                   |                 |                 |       |  |  |  |  |  |  |

| bit 10       | IC3MD: Input                                                                    | t Capture 3 Mod                                     | ule Disable bit |                   |                 |                 |       |  |  |  |  |  |  |

|              | 1 = Input Capture 3 module is disabled<br>0 = Input Capture 3 module is enabled |                                                     |                 |                   |                 |                 |       |  |  |  |  |  |  |

|              |                                                                                 |                                                     |                 |                   |                 |                 |       |  |  |  |  |  |  |

| bit 9        |                                                                                 | Capture 2 Mod                                       |                 |                   |                 |                 |       |  |  |  |  |  |  |

|              |                                                                                 | oture 2 module is<br>oture 2 module is              |                 |                   |                 |                 |       |  |  |  |  |  |  |

| bit 8        | IC1MD: Input                                                                    | t Capture 1 Mod                                     | ule Disable bit |                   |                 |                 |       |  |  |  |  |  |  |

|              | 1 = Input Cap                                                                   | oture 1 module is<br>oture 1 module is              | s disabled      |                   |                 |                 |       |  |  |  |  |  |  |

| bit 7-4      |                                                                                 | ted: Read as '0                                     |                 |                   |                 |                 |       |  |  |  |  |  |  |

| bit 3        | OC4MD: Out                                                                      | put Compare 4                                       | Module Disable  | e bit             |                 |                 |       |  |  |  |  |  |  |

|              |                                                                                 | ompare 4 modul                                      |                 |                   |                 |                 |       |  |  |  |  |  |  |

|              | -                                                                               | ompare 4 modu                                       |                 |                   |                 |                 |       |  |  |  |  |  |  |

| bit 2        |                                                                                 | put Compare 3                                       |                 | e bit             |                 |                 |       |  |  |  |  |  |  |

|              | •                                                                               | ompare 3 modul                                      |                 |                   |                 |                 |       |  |  |  |  |  |  |

| L:1 4        | -                                                                               | ompare 3 modul                                      |                 | . h.:4            |                 |                 |       |  |  |  |  |  |  |

| bit 1        |                                                                                 | put Compare 2                                       |                 |                   |                 |                 |       |  |  |  |  |  |  |

|              | $\perp$ – Output Co                                                             | ompare 2 modu                                       |                 |                   |                 |                 |       |  |  |  |  |  |  |

|              | 0 = Output Co                                                                   | ompare 2 modul                                      | le is enabled   |                   |                 |                 |       |  |  |  |  |  |  |

| bit 0        | •                                                                               | ompare 2 modul<br>put Compare 1                     |                 | e bit             |                 |                 |       |  |  |  |  |  |  |

| bit 0        | OC1MD: Out                                                                      | ompare 2 modul<br>put Compare 1 l<br>ompare 1 modul | Module Disable  | e bit             |                 |                 |       |  |  |  |  |  |  |

#### ~

# 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70598) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Many of the device pins are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

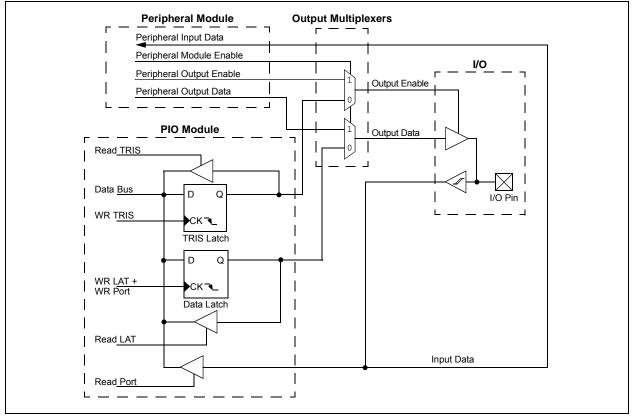

# 11.1 Parallel I/O (PIO) Ports

Generally, a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Latch register (LATx) read the latch. Writes to the Latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device is disabled. This means the corresponding LATx and TRISx registers and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

NOTES:

### 15.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 15.1.1 KEY RESOURCES

- "Output Compare" (DS70358) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 16.2 PWM Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 16.2.1 KEY RESOURCES

- "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0              | R/W-0                 | R/W-0                              | R/W-0           | R/W-0                       | R/W-0                          | R/W-0                | R/W-0           |  |  |  |  |  |  |

|------------------|-----------------------|------------------------------------|-----------------|-----------------------------|--------------------------------|----------------------|-----------------|--|--|--|--|--|--|

| _                | CLSRC4                | CLSRC3                             | CLSRC2          | CLSRC1                      | CLSRC0                         | CLPOL <sup>(2)</sup> | CLMOD           |  |  |  |  |  |  |

| bit 15           |                       |                                    | •               |                             |                                |                      | bit 8           |  |  |  |  |  |  |

|                  | <b>D</b> 4 4          | D 0.01 4                           | <b>D</b> 444    |                             | DAMA                           | DAMA                 | <b>D</b> 444.0  |  |  |  |  |  |  |

| R/W-1            | R/W-1                 | R/W-1                              | R/W-1           | R/W-1                       | R/W-0<br>FLTPOL <sup>(2)</sup> | R/W-0                | R/W-0           |  |  |  |  |  |  |

| FLTSRC4<br>bit 7 | FLTSRC3               | FLTSRC2                            | FLTSRC1         | FLTSRC0                     | FLIPOL-                        | FLTMOD1              | FLTMOD0<br>bit  |  |  |  |  |  |  |

|                  |                       |                                    |                 |                             |                                |                      | DI              |  |  |  |  |  |  |

| Legend:          |                       |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

| R = Readable     | bit                   | W = Writable                       | bit             | U = Unimpler                | mented bit, read               | l as '0'             |                 |  |  |  |  |  |  |

| -n = Value at I  | POR                   | '1' = Bit is set                   |                 | '0' = Bit is cle            | ared                           | x = Bit is unkr      | nown            |  |  |  |  |  |  |

|                  |                       |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

| bit 15           | Unimplemen            | ted: Read as '                     | 0'              |                             |                                |                      |                 |  |  |  |  |  |  |

| bit 14-10        | CLSRC<4:0>            | Current-Limit                      | Control Signa   | al Source Selec             | ct for PWM Ger                 | nerator # bits       |                 |  |  |  |  |  |  |

|                  | 11111 <b>= Fau</b>    | lt 32                              |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 11110 <b>= Res</b>    | erved                              |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | •                     |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | •                     |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | •<br>01100 = Reserved |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 01011 = Con           |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  |                       | Amp/Comparat                       | or 3            |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | •                     | Amp/Comparat                       |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  |                       | Amp/Comparat                       |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 00111 = Res           |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 00110 <b>= Res</b>    | erved                              |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 00101 = Res           | erved                              |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 00100 <b>= Res</b>    | erved                              |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 00011 <b>= Fau</b>    |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 00010 <b>= Fau</b>    |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 00001 <b>= Fau</b>    |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 00000 <b>= Fau</b>    | ( <i>)</i>                         |                 |                             | ~                              |                      |                 |  |  |  |  |  |  |

| bit 9            | CLPOL: Curr           | ent-Limit Polar                    | ity for PWM G   | enerator # bit <sup>(</sup> | 2)                             |                      |                 |  |  |  |  |  |  |

|                  |                       | cted current-lim                   |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | 0 = The selec         | cted current-lim                   | it source is ac | tive-high                   |                                |                      |                 |  |  |  |  |  |  |

| bit 8            | CLMOD: Cur            | rent-Limit Mode                    | e Enable for P  | WM Generator                | r # bit                        |                      |                 |  |  |  |  |  |  |

|                  |                       | imit mode is er<br>imit mode is di |                 |                             |                                |                      |                 |  |  |  |  |  |  |

|                  | ne PWMLOCK            |                                    |                 | <6>) is a '1', th           | e IOCONx regi                  | ster can only be     | e written aftei |  |  |  |  |  |  |

| the              | unlock sequen         | ce has been ex                     | ecuted.         |                             |                                |                      |                 |  |  |  |  |  |  |

|                  |                       |                                    |                 |                             |                                |                      |                 |  |  |  |  |  |  |

# REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

2: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0         | R/W-0                             | R/W-0                                                                                                                      | R/W-0                                          | R/W-0                              | R/W-0          | R/W-0           | R/W-0  |  |

|---------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------|----------------|-----------------|--------|--|

|               | F15B                              | P<3:0>                                                                                                                     |                                                |                                    | F14BI          | P<3:0>          |        |  |

| bit 15        |                                   |                                                                                                                            |                                                |                                    |                |                 | bit 8  |  |

| R/W-0         | R/W-0                             | R/W-0                                                                                                                      | R/W-0                                          | R/W-0                              | R/W-0          | R/W-0           | R/W-0  |  |

| 1010 0        | F13BP<3:0>                        |                                                                                                                            |                                                |                                    |                | P<3:0>          | 1010 0 |  |

| bit 7         |                                   |                                                                                                                            |                                                |                                    |                |                 | bit 0  |  |

| Legend:       |                                   |                                                                                                                            |                                                |                                    |                |                 |        |  |

| R = Readabl   | R = Readable bit W = Writable bit |                                                                                                                            |                                                | U = Unimplemented bit, read as '0' |                |                 |        |  |

| -n = Value at | t POR                             | '1' = Bit is set                                                                                                           | :                                              | '0' = Bit is clea                  | ared           | x = Bit is unkr | nown   |  |

| bit 15-12     | 1111 = Filte<br>1110 = Filte      | RX Buffer Ma<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in<br>r hits received in | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | differ<br>4                        |                |                 |        |  |

| bit 11-8      | F14BP<3:0;                        | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 4 bits (same val                   | ues as bits<15 | :12>)           |        |  |

| bit 7-4       | F13BP<3:0;                        | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 3 bits (same val                   | ues as bits<15 | :12>)           |        |  |

| bit 3-0       | F12BP<3:0:                        | RX Buffer Ma                                                                                                               | sk for Filter 1                                | 2 bits (same val                   | ues as bits<15 | :12>)           |        |  |

## REGISTER 21-15: CxBUFPNT4: ECANx FILTER 12-15 BUFFER POINTER REGISTER 4

#### BUFFER 21-5: ECAN™ MESSAGE BUFFER WORD 4

| R/W-x                                                                | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x | R/W-x           | R/W-x |  |

|----------------------------------------------------------------------|-------|------------------|-------|-------------------|-------|-----------------|-------|--|

|                                                                      |       |                  | Ву    | /te 3             |       |                 |       |  |

| bit 15 bit 8                                                         |       |                  |       |                   |       |                 |       |  |

|                                                                      |       |                  |       |                   |       |                 |       |  |

| R/W-x                                                                | R/W-x | R/W-x            | R/W-x | R/W-x             | R/W-x | R/W-x           | R/W-x |  |

|                                                                      |       |                  | Ву    | /te 2             |       |                 |       |  |

| bit 7                                                                |       |                  |       |                   |       |                 | bit 0 |  |

| Legend:                                                              |       |                  |       |                   |       |                 |       |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       |                   |       |                 |       |  |

| -n = Value at P                                                      | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared  | x = Bit is unkr | nown  |  |

bit 15-8 Byte 3<15:8>: ECAN Message Byte 3 bits

bit 7-0 Byte 2<7:0>: ECAN Message Byte 2 bits

#### BUFFER 21-6: ECAN™ MESSAGE BUFFER WORD 5

| R/W-x                                                         | R/W-x | R/W-x        | R/W-x           | R/W-x        | R/W-x           | R/W-x     | R/W-x |

|---------------------------------------------------------------|-------|--------------|-----------------|--------------|-----------------|-----------|-------|

|                                                               |       |              | В               | yte 5        |                 |           |       |

| bit 15                                                        |       |              |                 |              |                 |           | bit 8 |

| R/W-x                                                         | R/W-x | R/W-x        | R/W-x           | R/W-x        | R/W-x           | R/W-x     | R/W-x |

|                                                               |       |              |                 | yte 4        |                 |           |       |

| bit 7                                                         |       |              |                 | -            |                 |           | bit 0 |

|                                                               |       |              |                 |              |                 |           |       |

| Legend:                                                       |       |              |                 |              |                 |           |       |

| R = Readable I                                                | oit   | W = Writable | bit             | U = Unimplen | nented bit, rea | ad as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = B |       |              | x = Bit is unki | nown         |                 |           |       |

bit 15-8 Byte 5<15:8>: ECAN Message Byte 5 bits

bit 7-0 Byte 4<7:0>: ECAN Message Byte 4 bits

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER

| 11.0   | 11.0       | 11.0 | 11.0 | 11.0 |          |          |         |

|--------|------------|------|------|------|----------|----------|---------|

| U-0    | <u>U-0</u> | U-0  | U-0  | U-0  | R/W-0    | R/W-0    | R/W-0   |

| —      | _          |      |      |      | CH123NB1 | CH123NB0 | CH123SB |

| bit 15 |            |      |      |      |          |          | bit 8   |

|        |            |      |      |      |          |          |         |

| U-0    | U-0        | U-0  | U-0  | U-0  | R/W-0    | R/W-0    | R/W-0   |

| 0-0   | 0-0 | 0-0 | 0-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

|-------|-----|-----|-----|-----|----------|----------|---------|

| —     | —   | —   | _   |     | CH123NA1 | CH123NA0 | CH123SA |

| bit 7 |     |     |     |     |          |          | bit 0   |

# Legend:

| Legenu.           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-11 Unimplemented: Read as '0'

bit 10-9

CH123NB<1:0>: Channel 1, 2, 3 Negative Input Select for Sample MUXB bits

In 12-bit mode (AD21B = 1), CH123NB is Unimplemented and is Read as '0':

| Value           | ADC Channel |         |       |  |  |  |  |

|-----------------|-------------|---------|-------|--|--|--|--|

| value           | CH1         | CH2 CH3 |       |  |  |  |  |

| 11              | AN9         | AN10    | AN11  |  |  |  |  |

| 10 <b>(1,2)</b> | OA3/AN6     | AN7     | AN8   |  |  |  |  |

| 0x              | Vrefl       | Vrefl   | VREFL |  |  |  |  |

bit 8 **CH123SB:** Channel 1, 2, 3 Positive Input Select for Sample MUXB bit In 12-bit mode (AD21B = 1), CH123SB is Unimplemented and is Read as '0':

| Value          | Value ADC Channel |             |         |  |  |  |  |

|----------------|-------------------|-------------|---------|--|--|--|--|

| value          | CH1               | CH1 CH2 CH3 |         |  |  |  |  |

| 1 <b>(2)</b>   | OA1/AN3           | OA2/AN0     | OA3/AN6 |  |  |  |  |

| 0 <b>(1,2)</b> | OA2/AN0           | AN1         | AN2     |  |  |  |  |

bit 7-3 Unimplemented: Read as '0'

bit 2-1 **CH123NA<1:0>:** Channel 1, 2, 3 Negative Input Select for Sample MUXA bits In 12-bit mode (AD21B = 1), CH123NA is Unimplemented and is Read as '<u>0</u>':

| Value           |         | ADC Channel |       |  |  |  |  |

|-----------------|---------|-------------|-------|--|--|--|--|

| value           | CH1     | CH2 CH3     |       |  |  |  |  |

| 11              | AN9     | AN10        | AN11  |  |  |  |  |

| 10 <b>(1,2)</b> | OA3/AN6 | AN7         | AN8   |  |  |  |  |

| 0x              | VREFL   | VREFL       | Vrefl |  |  |  |  |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

# FIGURE 30-11: TIMERQ (QEI MODULE) EXTERNAL CLOCK TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

#### TABLE 30-30: QEI MODULE EXTERNAL CLOCK TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| АС СНА       | ARACTERIST                          | rics                                                         | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                |      |      |       |                                  |

|--------------|-------------------------------------|--------------------------------------------------------------|------------------------------------------------------|------------------------------------------------|------|------|-------|----------------------------------|

| Param<br>No. | Symbol Characteristic <sup>17</sup> |                                                              |                                                      | Min.                                           | Тур. | Max. | Units | Conditions                       |

| TQ10         | TtQH                                | TQCK High<br>Time                                            | Synchronous, with prescaler                          | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25 |      |      | ns    | Must also meet<br>Parameter TQ15 |

| TQ11         | TtQL                                | TQCK Low<br>Time                                             | Synchronous, with prescaler                          | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25 | —    | _    | ns    | Must also meet<br>Parameter TQ15 |

| TQ15         | TtQP                                | TQCP Input<br>Period                                         | Synchronous, with prescaler                          | Greater of 25 + 50<br>or<br>(1 Tcy/N) + 50     | —    | _    | ns    |                                  |

| TQ20         | TCKEXTMRL                           | Delay from External TQCK<br>Clock Edge to Timer<br>Increment |                                                      | _                                              | 1    | Тсү  | —     |                                  |

Note 1: These parameters are characterized but not tested in manufacturing.

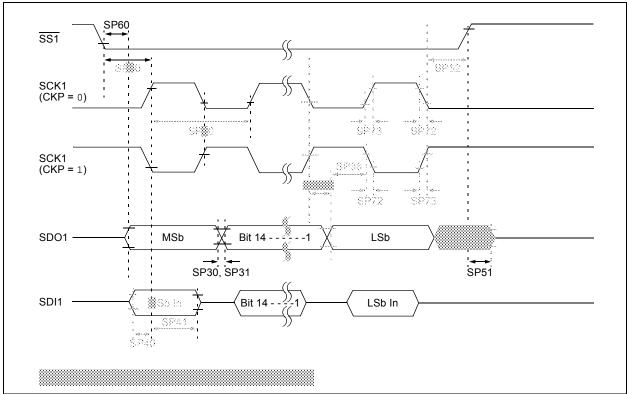

FIGURE 30-26: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

#### FIGURE 30-29: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

| AC CHA       | RACTER  | ISTICS                        |                           | Standard Operatin<br>(unless otherwise<br>Operating tempera | stated)<br>iture -40 | )°C ≤ Ta ≤ | +85°C for Industrial   |

|--------------|---------|-------------------------------|---------------------------|-------------------------------------------------------------|----------------------|------------|------------------------|

| Param<br>No. | Symbol  | Characteristic <sup>(4)</sup> |                           | Min. <sup>(1)</sup>                                         | -40<br>Max.          | Units      | Conditions             |

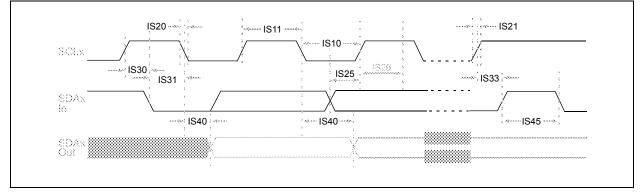

| IM10         | TLO:SCL | Clock Low Time                | 100 kHz mode              | Tcy/2 (BRG + 2)                                             | _                    | μS         |                        |

|              |         |                               | 400 kHz mode              | TCY/2 (BRG + 2)                                             |                      | μ <b>S</b> |                        |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μs         |                        |

| IM11         | THI:SCL | Clock High Time               | 100 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μS         |                        |

|              |         |                               | 400 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μs         |                        |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                             | _                    | μS         |                        |

| IM20         | TF:SCL  | SDAx and SCLx                 | 100 kHz mode              | _                                                           | 300                  | ns         | CB is specified to be  |

|              |         | Fall Time                     | 400 kHz mode              | 20 + 0.1 Св                                                 | 300                  | ns         | from 10 to 400 pF      |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | _                                                           | 100                  | ns         |                        |

| IM21         | TR:SCL  | SDAx and SCLx                 | 100 kHz mode              | _                                                           | 1000                 | ns         | CB is specified to be  |

|              |         | Rise Time                     | 400 kHz mode              | 20 + 0.1 Св                                                 | 300                  | ns         | from 10 to 400 pF      |

|              |         |                               | 1 MHz mode <sup>(2)</sup> |                                                             | 300                  | ns         |                        |

| IM25         | TSU:DAT | Data Input                    | 100 kHz mode              | 250                                                         |                      | ns         |                        |

|              |         | Setup Time                    | 400 kHz mode              | 100                                                         |                      | ns         |                        |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | 40                                                          |                      | ns         |                        |

| IM26         | THD:DAT | Data Input                    | 100 kHz mode              | 0                                                           |                      | μS         | -                      |

|              |         | Hold Time                     | 400 kHz mode              | 0                                                           | 0.9                  | μs         |                        |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | 0.2                                                         |                      | μS         |                        |

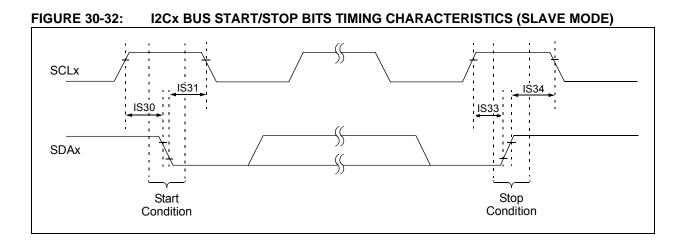

| IM30         | TSU:STA | Start Condition               | 100 kHz mode              | TCY/2 (BRG + 2)                                             | —                    | μS         | Only relevant for      |

|              |         | Setup Time                    | 400 kHz mode              | TCY/2 (BRG + 2)                                             | —                    | μS         | Repeated Start         |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                             |                      | μS         | condition              |

| IM31         | THD:STA | Start Condition               | 100 kHz mode              | TCY/2 (BRG + 2)                                             | —                    | μS         | After this period, the |

|              |         | Hold Time                     | 400 kHz mode              | TCY/2 (BRG +2)                                              | —                    | μS         | first clock pulse is   |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μS         | generated              |

| IM33         | Tsu:sto | Stop Condition                | 100 kHz mode              | TCY/2 (BRG + 2)                                             | _                    | μS         |                        |

|              |         | Setup Time                    | 400 kHz mode              | TCY/2 (BRG + 2)                                             |                      | μS         |                        |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μS         |                        |

| IM34         | THD:STO | Stop Condition                | 100 kHz mode              | TCY/2 (BRG + 2)                                             |                      | μS         |                        |

|              |         | Hold Time                     | 400 kHz mode              | TCY/2 (BRG + 2)                                             |                      | μS         |                        |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μS         |                        |

| IM40         | TAA:SCL | Output Valid                  | 100 kHz mode              | —                                                           | 3500                 | ns         |                        |

|              |         | From Clock                    | 400 kHz mode              |                                                             | 1000                 | ns         |                        |

|              |         |                               | 1 MHz mode <sup>(2)</sup> |                                                             | 400                  | ns         |                        |

| IM45         | TBF:SDA | Bus Free Time                 | 100 kHz mode              | 4.7                                                         |                      | μS         | Time the bus must be   |

|              |         |                               | 400 kHz mode              | 1.3                                                         |                      | μS         | free before a new      |

|              |         |                               | 1 MHz mode <sup>(2)</sup> | 0.5                                                         | —                    | μS         | transmission can star  |

| IM50         | Св      | Bus Capacitive L              | oading                    | —                                                           | 400                  | pF         |                        |

| IM51         | Tpgd    | Pulse Gobbler De              | elay                      | 65                                                          | 390                  | ns         | (Note 3)               |

#### TABLE 30-49: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

Note 1: BRG is the value of the l<sup>2</sup>C<sup>™</sup> Baud Rate Generator. Refer to "Inter-Integrated Circuit (l<sup>2</sup>C<sup>™</sup>)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual". Please see the Microchip web site for the latest family reference manual sections.

- 2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

- **3:** Typical value for this parameter is 130 ns.

- 4: These parameters are characterized, but not tested in manufacturing.

NOTES:

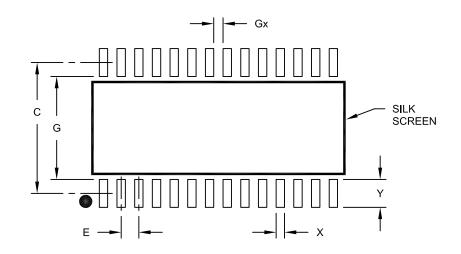

28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | Units            |      |          |      |  |

|--------------------------|------------------|------|----------|------|--|

| Dimension                | Dimension Limits |      |          | MAX  |  |

| Contact Pitch            | Е                |      | 1.27 BSC |      |  |

| Contact Pad Spacing      | С                |      | 9.40     |      |  |

| Contact Pad Width (X28)  | Х                |      |          | 0.60 |  |

| Contact Pad Length (X28) | Y                |      |          | 2.00 |  |

| Distance Between Pads    | Gx               | 0.67 |          |      |  |

| Distance Between Pads    | G                | 7.40 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2052A