Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                     |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 512KB (170K x 24)                                                                |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 24K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

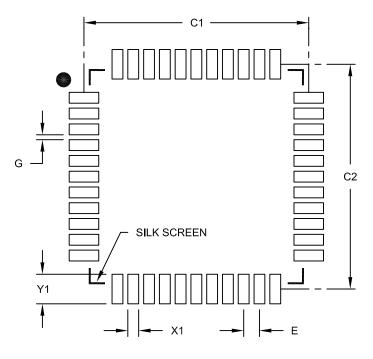

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep512mc506-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED) |             |                |     |                                                                                      |  |  |

|------------------------------------------------|-------------|----------------|-----|--------------------------------------------------------------------------------------|--|--|

| Pin Name <sup>(4)</sup>                        | Pin<br>Type | Buffer<br>Type | PPS | Description                                                                          |  |  |

| U2CTS                                          | Ι           | ST             | No  | UART2 Clear-To-Send.                                                                 |  |  |

| U2RTS                                          | 0           | —              | No  | UART2 Ready-To-Send.                                                                 |  |  |

| U2RX                                           | Ι           | ST             | Yes | UART2 receive.                                                                       |  |  |

| U2TX                                           | 0           | —              | Yes | UART2 transmit.                                                                      |  |  |

| BCLK2                                          | 0           | ST             | No  | UART2 IrDA <sup>®</sup> baud clock output.                                           |  |  |

| SCK1                                           | I/O         | ST             | No  | Synchronous serial clock input/output for SPI1.                                      |  |  |

| SDI1                                           | I           | ST             | No  | SPI1 data in.                                                                        |  |  |

| SDO1                                           | 0           | —              | No  | SPI1 data out.                                                                       |  |  |

| SS1                                            | I/O         | ST             | No  | SPI1 slave synchronization or frame pulse I/O.                                       |  |  |

| SCK2                                           | I/O         | ST             | Yes | Synchronous serial clock input/output for SPI2.                                      |  |  |

| SDI2                                           | I           | ST             | Yes | SPI2 data in.                                                                        |  |  |

| SDO2                                           | 0           | _              | Yes | SPI2 data out.                                                                       |  |  |

| SS2                                            | I/O         | ST             | Yes | SPI2 slave synchronization or frame pulse I/O.                                       |  |  |

| SCL1                                           | I/O         | ST             | No  | Synchronous serial clock input/output for I2C1.                                      |  |  |

| SDA1                                           | I/O         | ST             | No  | Synchronous serial data input/output for I2C1.                                       |  |  |

| ASCL1                                          | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C1.                            |  |  |

| ASDA1                                          | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C1.                             |  |  |

| SCL2                                           | I/O         | ST             | No  | Synchronous serial clock input/output for I2C2.                                      |  |  |

| SDA2                                           | I/O         | ST             | No  | Synchronous serial data input/output for I2C2.                                       |  |  |

| ASCL2                                          | I/O         | ST             | No  | Alternate synchronous serial clock input/output for I2C2.                            |  |  |

| ASDA2                                          | I/O         | ST             | No  | Alternate synchronous serial data input/output for I2C2.                             |  |  |

| TMS <sup>(5)</sup>                             | Ι           | ST             | No  | JTAG Test mode select pin.                                                           |  |  |

| TCK                                            | Ι           | ST             | No  | JTAG test clock input pin.                                                           |  |  |

| TDI                                            | I           | ST             | No  | JTAG test data input pin.                                                            |  |  |

| TDO                                            | 0           | _              | No  | JTAG test data output pin.                                                           |  |  |

| C1RX <sup>(2)</sup>                            | Ι           | ST             | Yes | ECAN1 bus receive pin.                                                               |  |  |

| C1TX <sup>(2)</sup>                            | 0           | _              | Yes | ECAN1 bus transmit pin.                                                              |  |  |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup>      | Ι           | ST             | Yes | PWM Fault Inputs 1 and 2.                                                            |  |  |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup>      | Ι           | ST             | No  | PWM Fault Inputs 3 and 4.                                                            |  |  |

| FLT32 <sup>(1,3)</sup>                         | Ι           | ST             | No  | PWM Fault Input 32 (Class B Fault).                                                  |  |  |

| DTCMP1-DTCMP3 <sup>(1)</sup>                   | Ι           | ST             | Yes | PWM Dead-Time Compensation Inputs 1 through 3.                                       |  |  |

| PWM1L-PWM3L <sup>(1)</sup>                     | 0           | —              | No  | PWM Low Outputs 1 through 3.                                                         |  |  |

| PWM1H-PWM3H <sup>(1)</sup>                     | 0           | —              | No  | PWM High Outputs 1 through 3.                                                        |  |  |

| SYNCI1 <sup>(1)</sup>                          | Ι           | ST             |     | PWM Synchronization Input 1.                                                         |  |  |

| SYNCO1 <sup>(1)</sup>                          | 0           |                | Yes | PWM Synchronization Output 1.                                                        |  |  |

| INDX1 <sup>(1)</sup>                           | Ι           | ST             | Yes | Quadrature Encoder Index1 pulse input.                                               |  |  |

| HOME1 <sup>(1)</sup>                           | Ι           | ST             | Yes | Quadrature Encoder Home1 pulse input.                                                |  |  |

| QEA1 <sup>(1)</sup>                            | Ι           | ST             | Yes | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer                       |  |  |

| QEB1 <sup>(1)</sup>                            | ,           | ст             | Vee | external clock/gate input in Timer mode.                                             |  |  |

|                                                | Ι           | ST             | Yes |                                                                                      |  |  |

| CNTCMP1 <sup>(1)</sup>                         | 0           |                | Yes | external clock/gate input in Timer mode.<br>Yes Quadrature Encoder Compare Output 1. |  |  |

|                                                | 0           |                | 162 |                                                                                      |  |  |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

ST = Schmitt Trigger input with CMOS levels

O = Output

PPS = Peripheral Pin Select

TTL = TTL input buffer

P = Power I = Input

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

## 3.6 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

### 3.6.1 KEY RESOURCES

- "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9          | Bit 8  | Bit 7 | Bit 6      | Bit 5           | Bit 4         | Bit 3         | Bit 2       | Bit 1        | Bit 0   | All<br>Reset |

|--------------|-------|--------|--------|------------|--------|--------|--------|----------------|--------|-------|------------|-----------------|---------------|---------------|-------------|--------------|---------|--------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF        | T3IF   | T2IF  | OC2IF      | IC2IF           | DMA0IF        | T1IF          | OC1IF       | IC1IF        | INTOIF  | 0000         |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF          | DMA2IF | _     | _          | _               | INT1IF        | CNIF          | CMIF        | MI2C1IF      | SI2C1IF | 0000         |

| IFS2         | 0804  | _      | _      | _          | _      |        |        |                | _      | _     | IC4IF      | IC3IF           | DMA3IF        | C1IF          | C1RXIF      | SPI2IF       | SPI2EIF | 0000         |

| IFS3         | 0806  | _      | _      | _          | _      |        | QEI1IF | PSEMIF         | _      | _     | _          | _               | _             | _             | MI2C2IF     | SI2C2IF      | _       | 0000         |

| IFS4         | 0808  | _      | _      | CTMUIF     |        |        |        |                | _      | _     | C1TXIF     | _               | _             | CRCIF         | U2EIF       | U1EIF        |         | 0000         |

| IFS5         | 080A  | PWM2IF | PWM1IF | _          |        |        |        |                | _      | _     | _          | _               | _             | _             | _           | _            |         | 0000         |

| IFS6         | 080C  | _      | _      | _          |        |        |        |                | _      | _     | _          | _               | _             | _             | _           | _            | PWM3IF  | 0000         |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          |        |        |        |                | _      | _     | _          | _               | _             | _             | _           | _            |         | 0000         |

| IFS9         | 0812  | _      | —      | _          | _      | _      |        |                | _      | —     | PTG3IF     | PTG2IF          | PTG1IF        | PTG0IF        | PTGWDTIF    | PTGSTEPIF    |         | 0000         |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE        | T3IE   | T2IE  | OC2IE      | IC2IE           | DMA0IE        | T1IE          | OC1IE       | IC1IE        | INTOIE  | 0000         |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE          | DMA2IE | —     | _          | —               | INT1IE        | CNIE          | CMIE        | MI2C1IE      | SI2C1IE | 0000         |

| IEC2         | 0824  | _      | _      | _          | _      | _      |        | _              | _      | _     | IC4IE      | IC3IE           | <b>DMA3IE</b> | C1IE          | C1RXIE      | SPI2IE       | SPI2EIE | 0000         |

| IEC3         | 0826  | _      | _      | _          | _      | _      | QEI1IE | PSEMIE         | _      | _     | _          | _               | _             | _             | MI2C2IE     | SI2C2IE      | _       | 0000         |

| IEC4         | 0828  | _      | _      | CTMUIE     | _      |        |        | _              | _      | _     | C1TXIE     | _               | _             | CRCIE         | U2EIE       | U1EIE        | _       | 0000         |

| IEC5         | 082A  | PWM2IE | PWM1IE | _          | _      | _      |        | _              | _      | _     | _          | _               | _             | _             | _           | _            | _       | 0000         |

| IEC6         | 082C  | _      | _      | _          | _      | _      |        | _              | _      | _     | _          | _               | _             | _             | _           | _            | PWM3IE  | 0000         |

| IEC7         | 082E  | _      | _      | _          | _      | _      |        | _              | _      | _     | _          | _               | _             | _             | _           | _            | _       | 0000         |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _      | _      |        | _              | _      | _     | _          | _               | _             | _             | _           | _            | _       | 0000         |

| IEC9         | 0832  | _      | _      | _          | _      | _      |        | _              | _      | _     | PTG3IE     | PTG2IE          | PTG1IE        | PTG0IE        | PTGWDTIE    | PTGSTEPIE    | _       | 0000         |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      |        | OC1IP<2:0      | >      | _     | IC1IP<2:0> |                 | _             |               | INT0IP<2:0> |              | 4444    |              |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      |        | OC2IP<2:0      | >      | _     |            | IC2IP<2:0>      |               | — DMA0IP<2:0> |             |              | 4444    |              |

| IPC2         | 0844  | _      | l      | J1RXIP<2:0 | >      | _      |        | SPI1IP<2:0     | )>     | _     |            | SPI1EIP<2:0     | >             |               |             | T3IP<2:0>    |         | 4444         |

| IPC3         | 0846  | _      | _      | _          | _      | _      | C      | MA1IP<2:       | 0>     | _     |            | AD1IP<2:0>      |               |               |             | U1TXIP<2:0>  |         | 0444         |

| IPC4         | 0848  | _      |        | CNIP<2:0>  |        | _      |        | CMIP<2:0       | >      | _     |            | MI2C1IP<2:0     | >             |               | 5           | SI2C1IP<2:0> |         | 4444         |

| IPC5         | 084A  | _      | _      | _          | _      | _      |        | _              | _      | _     | _          | _               | _             |               |             | INT1IP<2:0>  |         | 0004         |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      |        | OC4IP<2:0      | >      | _     |            | OC3IP<2:0>      |               |               | [           | DMA2IP<2:0>  |         | 4444         |

| IPC7         | 084E  | _      | 1      | U2TXIP<2:0 | >      | _      | ι      | J2RXIP<2:      | 0>     | _     |            | INT2IP<2:0>     |               |               |             | T5IP<2:0>    |         | 4444         |

| IPC8         | 0850  | _      |        | C1IP<2:0>  |        | _      | C      | 2:<br>2:<br>2: | 0>     | _     |            | SPI2IP<2:0>     |               |               | 5           | SPI2EIP<2:0> |         | 4444         |

| IPC9         | 0852  | _      | _      | _          | _      | _      |        | IC4IP<2:0      | >      | _     |            | IC3IP<2:0>      |               |               | [           | DMA3IP<2:0>  |         | 0444         |

| IPC12        | 0858  | _      | _      | _          | _      | _      | N      | 112C2IP<2:     | 0>     | _     |            | SI2C2IP<2:0     | >             | _             | _           | _            | _       | 0440         |

| IPC14        | 085C  | _      | _      | _          | _      | _      | (      | QEI1IP<2:(     | )>     | _     |            | PSEMIP<2:0      | >             | _             | _           | _            | _       | 0440         |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >      | _      |        | U2EIP<2:0      |        | _     |            | U1EIP<2:0>      |               | _             | <u> </u>    | _            | _       | 4440         |

| IPC17        | 0862  | _      | _      | _          | _      | _      |        | C1TXIP<2:      |        | _     | _          | _               | —             | _             | _           | _            | _       | 0400         |

| IPC19        | 0866  | _      | _      |            | _      | _      |        |                |        |       |            | L<br>CTMUIP<2:0 | >             |               | <u> </u>    | _            | _       | 0040         |

### TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

DS70000657H-page 73

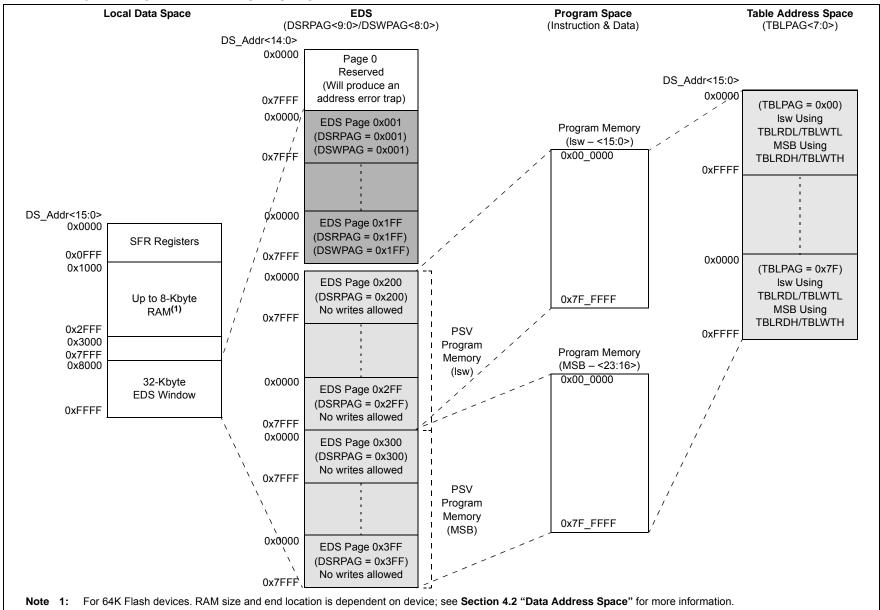

#### EXAMPLE 4-3: PAGED DATA MEMORY SPACE

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 8-9: DSADRH: DMA MOST RECENT RAM HIGH ADDRESS REGISTER

| U-0            | U-0                                                                  | U-0 | U-0   | U-0     | U-0 | U-0 | U-0   |

|----------------|----------------------------------------------------------------------|-----|-------|---------|-----|-----|-------|

| —              | —                                                                    | —   | —     | —       | —   | -   | —     |

| bit 15         |                                                                      |     |       |         |     |     | bit 8 |

|                |                                                                      |     |       |         |     |     |       |

| R-0            | R-0                                                                  | R-0 | R-0   | R-0     | R-0 | R-0 | R-0   |

|                |                                                                      |     | DSADR | <23:16> |     |     |       |

| bit 7          |                                                                      |     |       |         |     |     | bit 0 |

|                |                                                                      |     |       |         |     |     |       |

| Legend:        |                                                                      |     |       |         |     |     |       |

| R = Readable b | t = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |       |         |     |     |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 15-8 Unimplemented: Read as '0'

bit 7-0 DSADR<23:16>: Most Recent DMA Address Accessed by DMA bits

#### REGISTER 8-10: DSADRL: DMA MOST RECENT RAM LOW ADDRESS REGISTER

| R-0              | R-0 | R-0              | R-0                                       | R-0      | R-0 | R-0 | R-0   |

|------------------|-----|------------------|-------------------------------------------|----------|-----|-----|-------|

|                  |     |                  | DSAD                                      | DR<15:8> |     |     |       |

| bit 15           |     |                  |                                           |          |     |     | bit 8 |

|                  |     |                  |                                           |          |     |     |       |

| R-0              | R-0 | R-0              | R-0                                       | R-0      | R-0 | R-0 | R-0   |

|                  |     |                  | DSA                                       | DR<7:0>  |     |     |       |

| bit 7            |     |                  |                                           |          |     |     | bit 0 |

|                  |     |                  |                                           |          |     |     |       |

| Legend:          |     |                  |                                           |          |     |     |       |

| R = Readable b   | it  | W = Writable bit | le bit U = Unimplemented bit, read as '0' |          |     |     |       |

| -n = Value at PC | OR  | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown   |          |     |     | own   |

bit 15-0 DSADR<15:0>: Most Recent DMA Address Accessed by DMA bits

| U-0    | U-0 | U-0 | U-0 | U-0   | U-0   | U-0   | U-0   |

|--------|-----|-----|-----|-------|-------|-------|-------|

| _      |     |     |     | _     | —     |       | —     |

| bit 15 |     |     |     |       |       |       | bit 8 |

|        |     |     |     |       |       |       |       |

| U-0    | U-0 | U-0 | U-0 | R-0   | R-0   | R-0   | R-0   |

| —      | —   | —   | _   | PPST3 | PPST2 | PPST1 | PPST0 |

| bit 7  |     |     |     |       |       |       | bit 0 |

#### REGISTER 8-14: DMAPPS: DMA PING-PONG STATUS REGISTER

| Legend:                               |                                                                                                                                                                    |                                                          |                                    |                    |  |  |  |  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit<br>-n = Value at POR |                                                                                                                                                                    | W = Writable bit                                         | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|                                       |                                                                                                                                                                    | '1' = Bit is set                                         | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

| bit 15-4                              | Unimplo                                                                                                                                                            | montod: Dood os 'o'                                      |                                    |                    |  |  |  |  |

| bit 3                                 | <ul> <li>Unimplemented: Read as '0'</li> <li>PPST3: DMA Channel 3 Ping-Pong Mode Status Flag bit</li> </ul>                                                        |                                                          |                                    |                    |  |  |  |  |

| bit 5                                 | 1 = DMA                                                                                                                                                            | ASTB3 register is selected<br>ASTA3 register is selected | vioue Status Flag bit              |                    |  |  |  |  |

| bit 2                                 | <ul> <li><b>PPST2:</b> DMA Channel 2 Ping-Pong Mode Status Flag bit</li> <li>1 = DMASTB2 register is selected</li> <li>0 = DMASTA2 register is selected</li> </ul> |                                                          |                                    |                    |  |  |  |  |

| bit 1                                 | bit 1 PPST1: DMA Channel 1 Ping-Pong Mode Status Flag bit                                                                                                          |                                                          |                                    |                    |  |  |  |  |

|                                       |                                                                                                                                                                    | 1 - DMACTD4 register is calented                         |                                    |                    |  |  |  |  |

- 1 = DMASTB1 register is selected0 = DMASTA1 register is selected

- bit 0 PPST0: DMA Channel 0 Ping-Pong Mode Status Flag bit

- 1 = DMASTB0 register is selected

- 0 = DMASTA0 register is selected

### REGISTER 11-8: RPINR14: PERIPHERAL PIN SELECT INPUT REGISTER 14 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|---------------------------|----------------------------------------------------------------------------------------------------|----------------------------|-------------------|-----------------|-----------------|-------|

| —            |                           |                                                                                                    |                            | QEB1R<6:0>        |                 |                 |       |

| bit 15       |                           |                                                                                                    |                            |                   |                 |                 | bit 8 |

|              |                           |                                                                                                    |                            |                   |                 |                 |       |

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |                           |                                                                                                    |                            | QEA1R<6:0>        |                 |                 |       |

| bit 7        |                           |                                                                                                    |                            |                   |                 |                 | bit 0 |

|              |                           |                                                                                                    |                            |                   |                 |                 |       |

| Legend:      |                           |                                                                                                    |                            |                   |                 |                 |       |

| R = Readat   | ole bit                   | W = Writable                                                                                       | bit                        | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value a | at POR                    | '1' = Bit is set                                                                                   |                            | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 1111001 =                 | 1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss                    | 121<br>P1                  |                   |                 |                 |       |

| bit 7        | Unimpleme                 | nted: Read as '                                                                                    | 0'                         |                   |                 |                 |       |

| bit 6-0      | (see Table 1<br>1111001 = | >: Assign A (QE<br>1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss | selection nun<br>121<br>P1 |                   | n Pin bits      |                 |       |

| U-0    | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|------------|-------|-------|--------|-------|-------|

| —      | —   |            |       | RP43  | R<5:0> |       |       |

| bit 15 |     |            |       |       |        |       | bit 8 |

|        |     |            |       |       |        |       |       |

| U-0    | U-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

| —      | —   | RP42R<5:0> |       |       |        |       |       |

#### REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

|   | bit | 7 |

|---|-----|---|

| 1 |     |   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP55  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP54  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP55R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP54R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 0

| R/W-0        | R/W-0                                                                                                    | R/W-0                              | R/W-0          | U-0                                                                                                | U-0                | U-0              | U-0          |  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------------------------------------------------------------------------------------------|--------------------|------------------|--------------|--|--|--|--|--|

|              | TRGD                                                                                                     | V<3:0>                             |                | —                                                                                                  |                    | —                | _            |  |  |  |  |  |

| bit 15       |                                                                                                          |                                    |                |                                                                                                    |                    |                  | bit 8        |  |  |  |  |  |

|              |                                                                                                          |                                    |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

| U-0          | U-0                                                                                                      | R/W-0                              | R/W-0          | R/W-0                                                                                              | R/W-0              | R/W-0            | R/W-0        |  |  |  |  |  |

| _            |                                                                                                          |                                    |                | TRGSTF                                                                                             | RT<5:0> <b>(1)</b> |                  |              |  |  |  |  |  |

| bit 7        |                                                                                                          |                                    |                |                                                                                                    |                    |                  | bit          |  |  |  |  |  |

|              |                                                                                                          |                                    |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

| Legend:      | 1. 1.4                                                                                                   |                                    |                |                                                                                                    |                    | (0)              |              |  |  |  |  |  |

| R = Readab   |                                                                                                          | W = Writable                       |                | •                                                                                                  | nented bit, read   |                  |              |  |  |  |  |  |

| -n = Value a | t POR                                                                                                    | '1' = Bit is set                   |                | '0' = Bit is clea                                                                                  | ared               | x = Bit is unkn  | own          |  |  |  |  |  |

|              |                                                                                                          |                                    |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

| bit 15-12    |                                                                                                          | <b>)&gt;:</b> Trigger # Ou         | -              |                                                                                                    |                    |                  |              |  |  |  |  |  |

|              |                                                                                                          | per output for ev                  |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

|              | 1110 = Trigger output for every 15th trigger event                                                       |                                    |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

|              | 1101 = Trigger output for every 14th trigger event<br>1100 = Trigger output for every 13th trigger event |                                    |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

|              | 1000 = Trigger output for every 13th trigger event                                                       |                                    |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

|              | 1010 = Trigger output for every 11th trigger event                                                       |                                    |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

|              |                                                                                                          | ger output for ev                  |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

|              |                                                                                                          | per output for ev                  |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

|              |                                                                                                          | per output for ev                  |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

|              |                                                                                                          | ger output for ev                  |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

|              |                                                                                                          | ger output for ev                  |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

|              | 0100 = Trigg                                                                                             | ger output for ev                  | ery 5th trigge | r event                                                                                            |                    |                  |              |  |  |  |  |  |

|              |                                                                                                          | ger output for ev                  |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

|              |                                                                                                          | ger output for ev                  |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

|              |                                                                                                          | ger output for ev                  |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

|              | 0000 = Trigg                                                                                             | ger output for ev                  | ery trigger ev | ent                                                                                                |                    |                  |              |  |  |  |  |  |

| bit 11-6     | -                                                                                                        | nted: Read as '                    |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

| bit 5-0      | TRGSTRT<5:0>: Trigger Postscaler Start Enable Select bits <sup>(1)</sup>                                 |                                    |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

| oft 5-0      | 111111 <b>=</b> W                                                                                        | aits 63 PWM cy                     | cles before g  | 111111 = Waits 63 PWM cycles before generating the first trigger event after the module is enabled |                    |                  |              |  |  |  |  |  |

|              |                                                                                                          |                                    |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

|              | •                                                                                                        |                                    |                | ·                                                                                                  |                    |                  |              |  |  |  |  |  |

|              | •                                                                                                        |                                    |                | -                                                                                                  |                    |                  |              |  |  |  |  |  |

|              | •                                                                                                        |                                    |                | -                                                                                                  |                    |                  |              |  |  |  |  |  |

|              | •<br>•<br>•                                                                                              | aits 2 PW/M ava                    | les hefore co  | nerating the fire                                                                                  | t trigger event :  | after the module | a is anabled |  |  |  |  |  |

|              |                                                                                                          | /aits 2 PWM cyc<br>/aits 1 PWM cyc |                |                                                                                                    |                    |                  |              |  |  |  |  |  |

### REGISTER 16-12: TRGCONx: PWMx TRIGGER CONTROL REGISTER

| R/W-1           | R/W-1              | R/W-0                                                               | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           | R/W-0  |

|-----------------|--------------------|---------------------------------------------------------------------|----------------------------|----------------------|---------------------------|-----------------|--------|

| PENH            | PENL               | POLH                                                                | POLL                       | PMOD1 <sup>(1)</sup> | PMOD0 <sup>(1)</sup>      | OVRENH          | OVRENL |

| bit 15          |                    | •                                                                   |                            |                      |                           |                 | bit    |

| R/W-0           | R/W-0              | R/W-0                                                               | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           |        |

| -               | -                  | -                                                                   |                            | -                    | -                         | -               | R/W-0  |

| OVRDAT1         | OVRDAT0            | FLTDAT1                                                             | FLTDAT0                    | CLDAT1               | CLDAT0                    | SWAP            | OSYNC  |

| bit 7           |                    |                                                                     |                            |                      |                           |                 | bit    |

| Legend:         |                    |                                                                     |                            |                      |                           |                 |        |

| R = Readable    | bit                | W = Writable                                                        | bit                        | U = Unimpler         | nented bit, read          | l as '0'        |        |

| -n = Value at F | POR                | '1' = Bit is set                                                    |                            | '0' = Bit is cle     | ared                      | x = Bit is unkr | nown   |

| bit 15          |                    | xH Output Pin                                                       | Ownorshin hit              |                      |                           |                 |        |

| bit 15          |                    | odule controls                                                      | •                          |                      |                           |                 |        |

|                 |                    | dule controls F                                                     |                            |                      |                           |                 |        |

| bit 14          |                    | L Output Pin                                                        | •                          |                      |                           |                 |        |

|                 | 1 = PWMx mo        | odule controls                                                      | PWMxL pin                  |                      |                           |                 |        |

|                 | 0 = GPIO mo        | dule controls F                                                     | WMxL pin                   |                      |                           |                 |        |

| bit 13          | POLH: PWM          | xH Output Pin                                                       | Polarity bit               |                      |                           |                 |        |

|                 |                    | oin is active-low                                                   |                            |                      |                           |                 |        |

|                 |                    | oin is active-hig                                                   | •                          |                      |                           |                 |        |

| bit 12          |                    | L Output Pin F                                                      | •                          |                      |                           |                 |        |

|                 |                    | in is active-low<br>in is active-hig                                |                            |                      |                           |                 |        |

| bit 11-10       | PMOD<1:0>:         | PWMx # I/O F                                                        | in Mode bits <sup>(1</sup> | )                    |                           |                 |        |

|                 | 11 = Reserve       | ,                                                                   |                            |                      |                           |                 |        |

|                 |                    | /O pin pair is ir<br>/O pin pair is ir                              |                            |                      |                           |                 |        |

|                 |                    | O pin pair is in<br>O pin pair is ir                                |                            |                      |                           |                 |        |

| bit 9           |                    | verride Enable                                                      | •                          |                      |                           |                 |        |

|                 |                    | <1> controls or                                                     |                            |                      |                           |                 |        |

|                 |                    | nerator contro                                                      | •                          | •                    |                           |                 |        |

| bit 8           | OVRENL: Ov         | erride Enable                                                       | for PWMxL Pir              | n bit                |                           |                 |        |

|                 | 1 = OVRDAT         | <0> controls or                                                     | utput on PWM               | xL pin               |                           |                 |        |

|                 | •                  | nerator contro                                                      |                            |                      |                           |                 |        |

| bit 7-6         |                    | DVRDAT<1:0>: Data for PWMxH, PWMxL Pins if Override is Enabled bits |                            |                      |                           |                 |        |

|                 |                    |                                                                     |                            |                      | by OVRDAT<<br>by OVRDAT<0 |                 |        |

| bit 5-4         | FLTDAT<1:0         | >: Data for PW                                                      | MxH and PWN                | ۰<br>MxL Pins if FLT | MOD is Enable             | ed bits         |        |

|                 | If Fault is active | ve, PWMxH is                                                        | driven to the s            | tate specified       | by FLTDAT<1>.             |                 |        |

|                 | If Fault is active | ve, PWMxL is                                                        | driven to the s            | tate specified b     | by FLTDAT<0>.             |                 |        |

| bit 3-2         | CLDAT<1:0>         | : Data for PWN                                                      | /IxH and PWM               | xL Pins if CLM       | 10D is Enabled            | bits            |        |

|                 |                    |                                                                     |                            | •                    | ecified by CLDA           |                 |        |

|                 |                    | IS AULIVE. F VVI                                                    |                            |                      |                           |                 |        |

| Note 1: The     |                    |                                                                     |                            |                      | enabled (PTEN             |                 |        |

# REGISTER 16-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup>

2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

| U-0                                | U-0   | U-0   | U-0   | R/W-0                                   | R/W-0 | R/W-0  | R/W-0 |

|------------------------------------|-------|-------|-------|-----------------------------------------|-------|--------|-------|

| —                                  | -     | —     | —     |                                         | LEB   | <11:8> |       |

| bit 15                             |       |       |       |                                         |       |        | bit 8 |

|                                    |       |       |       |                                         |       |        |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0  | R/W-0 |

|                                    |       |       | LEE   | 3<7:0>                                  |       |        |       |

| bit 7                              |       |       |       |                                         |       |        | bit 0 |

|                                    |       |       |       |                                         |       |        |       |

| Legend:                            |       |       |       |                                         |       |        |       |

| R = Readable bit W = Writable bit  |       |       |       | U = Unimplemented bit, read as '0'      |       |        |       |

| -n = Value at POR '1' = Bit is set |       |       |       | '0' = Bit is cleared x = Bit is unknown |       |        |       |

### REGISTER 16-17: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER

bit 15-12 Unimplemented: Read as '0'

bit 11-0 LEB<11:0>: Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits

| U-0                   | U-0                                | HS, R/C-0                          | R/W-0            | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

|-----------------------|------------------------------------|------------------------------------|------------------|------------------|------------------|-----------------------|----------|

| _                     | —                                  | PCHEQIRQ                           | PCHEQIEN         | PCLEQIRQ         | PCLEQIEN         | POSOVIRQ              | POSOVIEN |

| bit 15                |                                    |                                    |                  |                  |                  |                       | bit 8    |

|                       |                                    |                                    |                  |                  |                  |                       |          |

| HS, R/C-0             | R/W-0                              | HS, R/C-0                          | R/W-0            | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

| PCIIRQ <sup>(1)</sup> | PCIIEN                             | VELOVIRQ                           | VELOVIEN         | HOMIRQ           | HOMIEN           | IDXIRQ                | IDXIEN   |

| bit 7                 |                                    |                                    |                  |                  |                  |                       | bit 0    |

| r                     |                                    |                                    |                  |                  |                  |                       |          |

| Legend:               |                                    | HS = Hardware                      |                  | C = Clearable    |                  |                       |          |

| R = Readable I        |                                    | W = Writable b                     | bit              | •                | nented bit, rea  |                       |          |

| -n = Value at P       | OR                                 | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unkr       | iown     |

|                       |                                    |                                    |                  |                  |                  |                       |          |

| bit 15-14             | -                                  | ted: Read as '0                    |                  |                  |                  | .,                    |          |

| bit 13                |                                    | Position Counte                    | er Greater Tha   | n or Equal Cor   | npare Status b   | it                    |          |

|                       |                                    | T ≥ QEI1GEC<br>T < QEI1GEC         |                  |                  |                  |                       |          |

| bit 12                |                                    | Position Counte                    | r Greater Tha    | n or Equal Con   | npare Interrupt  | Enable bit            |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    | s disabled                         |                  |                  |                  |                       |          |

| bit 11                |                                    | Position Counte                    | r Less Than o    | r Equal Compa    | are Status bit   |                       |          |

|                       | 1 = POS1CN                         |                                    |                  |                  |                  |                       |          |

| bit 10                |                                    | Position Counte                    | r Less Than or   | - Equal Compa    | ire Interrunt En | ahla hit              |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 9                 | POSOVIRQ:                          | Position Counte                    | er Overflow Sta  | itus bit         |                  |                       |          |

|                       | 1 = Overflow                       |                                    |                  |                  |                  |                       |          |

|                       |                                    | ow has occurred                    |                  |                  |                  |                       |          |

| bit 8                 |                                    | Position Counte                    | r Overflow Inte  | errupt Enable b  | Dit              |                       |          |

|                       | 1 = Interrupt i<br>0 = Interrupt i |                                    |                  |                  |                  |                       |          |

| bit 7                 | •                                  | tion Counter (H                    | oming) Initializ | ation Process    | Complete Stat    | us bit <sup>(1)</sup> |          |

|                       |                                    | T was reinitialize                 | •                |                  | · · · · · · · ·  |                       |          |

|                       | 0 = POS1CN                         | T was not reiniti                  | alized           |                  |                  |                       |          |

| bit 6                 | PCIIEN: Posi                       | tion Counter (He                   | oming) Initializ | ation Process    | Complete inter   | rupt Enable bit       |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 5                 | 0 = Interrupt i                    |                                    | r Overflow Sta   | tuo hit          |                  |                       |          |

| DIL 5                 | 1 = Overflow                       | Velocity Counter                   | I Overnow Sta    |                  |                  |                       |          |

|                       |                                    | ow has not occu                    | irred            |                  |                  |                       |          |

| bit 4                 | VELOVIEN:                          | /elocity Counter                   | Overflow Inte    | rrupt Enable bi  | it               |                       |          |

|                       | 1 = Interrupt i                    | s enabled                          |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 3                 |                                    | atus Flag for Ho                   |                  | us bit           |                  |                       |          |

|                       |                                    | ent has occurred<br>event has occu |                  |                  |                  |                       |          |

|                       |                                    |                                    |                  |                  |                  |                       |          |

#### REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER

**Note 1:** This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

#### REGISTER 17-17: INT1TMRH: INTERVAL 1 TIMER HIGH WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | INTTM | R<31:24>          |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INTTM | R<23:16>          |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

|                 |       |                  |       |                   |                 |                 |       |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

bit 15-0 INTTMR<31:16>: High Word Used to Form 32-Bit Interval Timer Register (INT1TMR) bits

#### REGISTER 17-18: INT1TMRL: INTERVAL 1 TIMER LOW WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | INTTM | IR<15:8>         |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | INTT  | /IR<7:0>         |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable I  | bit   | W = Writable b   | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 INTTMR<15:0>: Low Word Used to Form 32-Bit Interval Timer Register (INT1TMR) bits

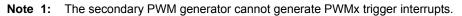

## 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70582) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

Note: <u>Hardware</u> flow control using UxRTS and UxCTS is not available on all pin count devices. See the "**Pin Diagrams**" section for availability.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 20-1: UARTx SIMPLIFIED BLOCK DIAGRAM

© 2011-2013 Microchip Technology Inc.

#### REGISTER 21-22: CxRXFUL1: ECANx RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXFUL7 | RXFUL6 | RXFUL5 | RXFUL4 | RXFUL3 | RXFUL2 | RXFUL1 | RXFUL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Writable bit, but on | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |

|-------------------|--------------------------|----------------------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit                                          | , read as '0'      |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared                                           | x = Bit is unknown |  |  |

bit 15-0 **RXFUL<15:0>:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (cleared by user software)

#### REGISTER 21-23: CxRXFUL2: ECANx RECEIVE BUFFER FULL REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Writable bit, but only ( | C = Writable bit, but only '0' can be written to clear the bit |                    |  |  |  |