#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 28-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gp502t-e-so |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

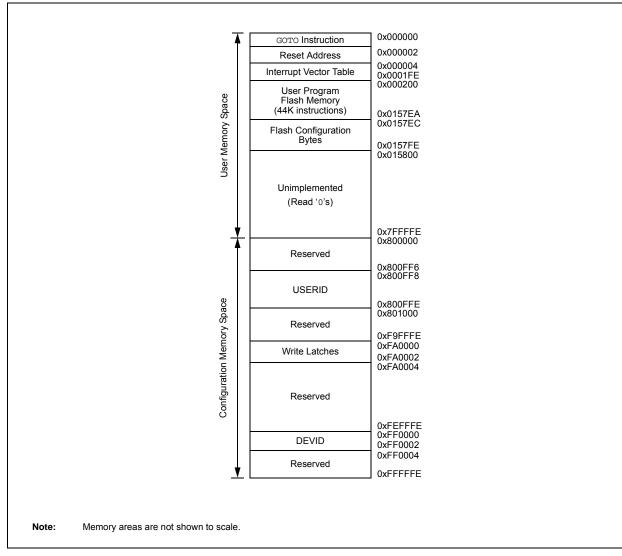

#### FIGURE 4-3: PROGRAM MEMORY MAP FOR dsPIC33EP128GP50X, dsPIC33EP128MC20X/50X AND PIC24EP128GP/MC20X DEVICES

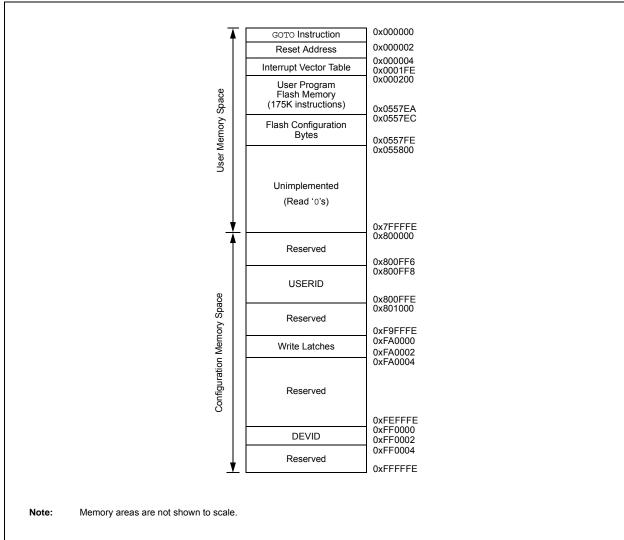

### FIGURE 4-5: PROGRAM MEMORY MAP FOR dsPIC33EP512GP50X, dsPIC33EP512MC20X/50X AND PIC24EP512GP/MC20X DEVICES

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12        | Bit 11 | Bit 10     | Bit 9          | Bit 8  | Bit 7 | Bit 6        | Bit 5            | Bit 4         | Bit 3    | Bit 2        | Bit 1           | Bit 0         | All<br>Reset |

|--------------|-------|--------|--------|------------|---------------|--------|------------|----------------|--------|-------|--------------|------------------|---------------|----------|--------------|-----------------|---------------|--------------|

| IFS0         | 0800  | _      | DMA1IF | AD1IF      | U1TXIF        | U1RXIF | SPI1IF     | SPI1EIF        | T3IF   | T2IF  | OC2IF        | IC2IF            | DMA0IF        | T1IF     | OC1IF        | IC1IF           | INTOIF        | 0000         |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF          | T4IF   | OC4IF      | OC3IF          | DMA2IF | _     | _            | _                | INT1IF        | CNIF     | CMIF         | MI2C1IF         | SI2C1IF       | 0000         |

| IFS2         | 0804  | _      | _      | _          | _             |        |            |                | —      | _     | IC4IF        | IC3IF            | DMA3IF        | C1IF     | C1RXIF       | SPI2IF          | SPI2EIF       | 0000         |

| IFS3         | 0806  | _      | _      | _          | _             |        | QEI1IF     | PSEMIF         | —      | _     | _            | _                | _             | _        | MI2C2IF      | SI2C2IF         |               | 0000         |

| IFS4         | 0808  | _      | _      | CTMUIF     |               |        |            | -              | —      | _     | C1TXIF       | _                | _             | CRCIF    | U2EIF        | U1EIF           | _             | 0000         |

| IFS5         | 080A  | PWM2IF | PWM1IF | _          |               |        |            |                | —      | _     | _            | _                | _             | _        | _            | _               | _             | 0000         |

| IFS6         | 080C  | _      | _      | _          |               |        |            |                | —      | _     | _            | _                | _             | _        | _            | _               | PWM3IF        | 0000         |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          |               |        |            |                | —      | _     | _            | _                | _             | _        | _            | _               | _             | 0000         |

| IFS9         | 0812  | _      | —      | _          | _             | _      |            |                | _      | _     | PTG3IF       | PTG2IF           | PTG1IF        | PTG0IF   | PTGWDTIF     | PTGSTEPIF       | _             | 0000         |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | <b>U1TXIE</b> | U1RXIE | SPI1IE     | SPI1EIE        | T3IE   | T2IE  | OC2IE        | IC2IE            | DMA0IE        | T1IE     | OC1IE        | IC1IE           | INTOIE        | 0000         |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE          | T4IE   | OC4IE      | OC3IE          | DMA2IE | —     | _            | -                | INT1IE        | CNIE     | CMIE         | MI2C1IE         | SI2C1IE       | 0000         |

| IEC2         | 0824  | _      | _      | _          | _             | _      |            | _              | _      | _     | IC4IE        | IC3IE            | <b>DMA3IE</b> | C1IE     | C1RXIE       | SPI2IE          | SPI2EIE       | 0000         |

| IEC3         | 0826  | _      | _      | _          | _             | _      | QEI1IE     | PSEMIE         | _      | _     | _            | _                | _             | _        | MI2C2IE      | SI2C2IE         | _             | 0000         |

| IEC4         | 0828  | _      | _      | CTMUIE     | _             |        |            | _              | _      | _     | C1TXIE       | _                | _             | CRCIE    | U2EIE        | U1EIE           |               | 0000         |

| IEC5         | 082A  | PWM2IE | PWM1IE | _          | _             | _      |            | _              | _      | _     | _            | _                | _             | _        | _            | _               | _             | 0000         |

| IEC6         | 082C  | _      | _      | _          | _             | _      |            | _              | _      | _     | _            | _                | _             |          | _            | _               | <b>PWM3IE</b> | 0000         |

| IEC7         | 082E  | _      | _      | _          | _             | _      |            | _              | _      | _     | _            | _                | _             |          | _            | _               | _             | 0000         |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _             | _      |            | _              | _      | _     | _            | _                | _             |          | _            | _               | _             | 0000         |

| IEC9         | 0832  | _      | _      | _          | _             | _      |            | _              | _      | _     | PTG3IE       | PTG2IE           | PTG1IE        | PTG0IE   | PTGWDTIE     | PTGSTEPIE       | _             | 0000         |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |               | _      |            | OC1IP<2:0      | >      | _     |              | IC1IP<2:0>       |               | _        | INT0IP<2:0>  |                 |               | 4444         |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |               | _      |            | OC2IP<2:0      | >      | _     |              | IC2IP<2:0>       |               |          | DMA0IP<2:0>  |                 |               | 4444         |

| IPC2         | 0844  | _      | I      | J1RXIP<2:0 | >             | _      |            | SPI1IP<2:0     | )>     | _     |              | SPI1EIP<2:0      | >             |          |              | T3IP<2:0>       |               | 4444         |

| IPC3         | 0846  | _      | _      | _          | _             | _      | C          | MA1IP<2:       | 0>     | _     |              | AD1IP<2:0>       |               |          |              | J1TXIP<2:0>     |               | 0444         |

| IPC4         | 0848  | _      |        | CNIP<2:0>  |               | _      |            | CMIP<2:0       | >      | _     |              | MI2C1IP<2:0      | >             |          | 5            | SI2C1IP<2:0>    |               | 4444         |

| IPC5         | 084A  | _      | _      | _          | _             | _      |            | _              | —      | _     | _            | _                | _             |          |              | INT1IP<2:0>     |               | 0004         |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |               | _      |            | OC4IP<2:0      | >      | _     |              | OC3IP<2:0>       |               |          | [            | )<br>MA2IP<2:0> |               | 4444         |

| IPC7         | 084E  | _      |        | U2TXIP<2:0 | >             | _      | ι          | J2RXIP<2:      | 0>     | _     |              | INT2IP<2:0>      |               | _        |              | T5IP<2:0>       |               | 4444         |

| IPC8         | 0850  | _      |        | C1IP<2:0>  |               | _      | 0          | 21RXIP<2:      | 0>     | _     | SPI2IP<2:0>  |                  | _             | 5        | SPI2EIP<2:0> |                 | 4444          |              |

| IPC9         | 0852  | _      | _      |            | _             | _      |            | IC4IP<2:0      | >      | _     | IC3IP<2:0>   |                  | _             | [        | DMA3IP<2:0>  |                 | 0444          |              |

| IPC12        | 0858  | _      | _      | _          | _             | _      | N          | MI2C2IP<2:0> — |        |       | SI2C2IP<2:0> |                  | _             | _        | _            | _               | 0440          |              |

| IPC14        | 085C  | _      | _      | _          | _             | _      | (          | QEI1IP<2:0> —  |        | _     |              | PSEMIP<2:0       | >             | _        | _            | _               | _             | 0440         |

| IPC16        | 0860  | _      |        | CRCIP<2:0  | >             | _      | U2EIP<2:0> |                | _      |       | U1EIP<2:0>   |                  |               | <u> </u> | _            |                 | 444(          |              |

| IPC17        | 0862  | _      | _      | _          | _             | _      |            | C1TXIP<2:      |        | _     |              |                  | _             |          | 0400         |                 |               |              |

| IPC19        | 0866  |        | _      | _          |               |        |            |                |        |       |              | L<br>CTMUIP<2:0: |               |          | _            |                 |               | 0040         |

# TABLE 4-7: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

DS70000657H-page 73

## TABLE 4-37: PMD REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | _      | _     | _     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | _      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      |       | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  |        | _      | _      | —      | _      | CMPMD  | _     | -     | CRCMD  | _     |       |        |        | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  |        | _      | _      | —      | _      |        | _     | -     | —      | _     |       |        | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  |        | —      |        | —      | _      |        | _     |       | —      | _     |       |        |        | —      | _      |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  | _      |        |        | _      |        |        |       |       |        |       |       | DMA1MD | PTGMD  | _      |        |       | 0000          |

|              | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | _     | _     | DMA2MD | FIGMD  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-38: PMD REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | —      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | _      | AD1MD | 0000          |

| PMD2         | 0762  | _      | _      | _      | _      | IC4MD  | IC3MD  | IC2MD  | IC1MD  |        | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      |        | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      | —      | _      |        |        | PWM3MD | PWM2MD | PWM1MD | _      | —     | —     | _      |        | —      | _      |       | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

### 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

# 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

|                                                     | Vector  | IRQ    |                   | Inte     | errupt Bit L | ocation      |  |

|-----------------------------------------------------|---------|--------|-------------------|----------|--------------|--------------|--|

| Interrupt Source                                    | #       | #      | IVT Address       | Flag     | Enable       | Priority     |  |

| QEI1 – QEI1 Position Counter Compare <sup>(2)</sup> | 66      | 58     | 0x000088          | IFS3<10> | IEC3<10>     | IPC14<10:8>  |  |

| Reserved                                            | 67-72   | 59-64  | 0x00008A-0x000094 | _        | _            | _            |  |

| U1E – UART1 Error Interrupt                         | 73      | 65     | 0x000096          | IFS4<1>  | IEC4<1>      | IPC16<6:4>   |  |

| U2E – UART2 Error Interrupt                         | 74      | 66     | 0x000098          | IFS4<2>  | IEC4<2>      | IPC16<10:8>  |  |

| CRC – CRC Generator Interrupt                       | 75      | 67     | 0x00009A          | IFS4<3>  | IEC4<3>      | IPC16<14:12> |  |

| Reserved                                            | 76-77   | 68-69  | 0x00009C-0x00009E | —        | _            | —            |  |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>          | 78      | 70     | 0x000A0           | IFS4<6>  | IEC4<6>      | IPC17<10:8>  |  |

| Reserved                                            | 79-84   | 71-76  | 0x0000A2-0x0000AC | —        | _            | —            |  |

| CTMU – CTMU Interrupt                               | 85      | 77     | 0x0000AE          | IFS4<13> | IEC4<13>     | IPC19<6:4>   |  |

| Reserved                                            | 86-101  | 78-93  | 0x0000B0-0x0000CE | —        | _            | —            |  |

| PWM1 – PWM Generator 1 <sup>(2)</sup>               | 102     | 94     | 0x0000D0          | IFS5<14> | IEC5<14>     | IPC23<10:8>  |  |

| PWM2 – PWM Generator 2 <sup>(2)</sup>               | 103     | 95     | 0x0000D2          | IFS5<15> | IEC5<15>     | IPC23<14:12> |  |

| PWM3 – PWM Generator 3 <sup>(2)</sup>               | 104     | 96     | 0x0000D4          | IFS6<0>  | IEC6<0>      | IPC24<2:0>   |  |

| Reserved                                            | 105-149 | 97-141 | 0x0001D6-0x00012E | —        | _            | —            |  |

| ICD – ICD Application                               | 150     | 142    | 0x000142          | IFS8<14> | IEC8<14>     | IPC35<10:8>  |  |

| JTAG – JTAG Programming                             | 151     | 143    | 0x000130          | IFS8<15> | IEC8<15>     | IPC35<14:12> |  |

| Reserved                                            | 152     | 144    | 0x000134          | —        | _            | _            |  |

| PTGSTEP – PTG Step                                  | 153     | 145    | 0x000136          | IFS9<1>  | IEC9<1>      | IPC36<6:4>   |  |

| PTGWDT – PTG Watchdog Time-out                      | 154     | 146    | 0x000138          | IFS9<2>  | IEC9<2>      | IPC36<10:8>  |  |

| PTG0 – PTG Interrupt 0                              | 155     | 147    | 0x00013A          | IFS9<3>  | IEC9<3>      | IPC36<14:12> |  |

| PTG1 – PTG Interrupt 1                              | 156     | 148    | 0x00013C          | IFS9<4>  | IEC9<4>      | IPC37<2:0>   |  |

| PTG2 – PTG Interrupt 2                              | 157     | 149    | 0x00013E          | IFS9<5>  | IEC9<5>      | IPC37<6:4>   |  |

| PTG3 – PTG Interrupt 3                              | 158     | 150    | 0x000140          | IFS9<6>  | IEC9<6>      | IPC37<10:8>  |  |

| Reserved 159-245 151-245 0x000142-0x0001FE — — —    |         |        |                   |          |              |              |  |

| Lowest Natural Order Priority                       |         |        |                   |          |              |              |  |

# TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

| R/W-0                 | R/W-0                                         | R/W-0                                                | R/W-0                                         | R/W-0                              | U-0              | U-0             | U-0     |

|-----------------------|-----------------------------------------------|------------------------------------------------------|-----------------------------------------------|------------------------------------|------------------|-----------------|---------|

| CHEN                  | SIZE                                          | DIR                                                  | HALF                                          | NULLW                              |                  |                 |         |

| bit 15                |                                               |                                                      |                                               |                                    |                  |                 | bit     |

| U-0                   | U-0                                           | R/W-0                                                | R/W-0                                         | U-0                                | U-0              | R/W-0           | R/W-0   |

|                       | 0-0                                           | AMODE1                                               | AMODE0                                        | 0-0                                | 0-0              | MODE1           | MODE0   |

| bit 7                 |                                               | AWODET                                               | 7 WIODE0                                      |                                    |                  | MODET           | bit     |

| Lovende               |                                               |                                                      |                                               |                                    |                  |                 |         |

| Legend:<br>R = Readab | lo hit                                        | M - Mritabla                                         | hit.                                          |                                    | monted bit rec   | ud aa '0'       |         |

|                       |                                               | W = Writable                                         |                                               | -                                  | mented bit, rea  |                 |         |

| -n = Value a          | IT POR                                        | '1' = Bit is set                                     |                                               | '0' = Bit is cle                   | ared             | x = Bit is unkr | lown    |

| bit 15                | CHEN: DMA                                     | Channel Enabl                                        | e bit                                         |                                    |                  |                 |         |

|                       | 1 = Channel<br>0 = Channel                    |                                                      |                                               |                                    |                  |                 |         |

| bit 14                |                                               | ata Transfer S                                       | ze hit                                        |                                    |                  |                 |         |

|                       | 1 = Byte                                      |                                                      |                                               |                                    |                  |                 |         |

|                       | 0 = Word                                      |                                                      |                                               |                                    |                  |                 |         |

| bit 13                | DIR: DMA Tra                                  | ansfer Directior                                     | n bit (source/d                               | estination bus                     | select)          |                 |         |

|                       |                                               | om RAM addre<br>om peripheral a                      |                                               | •                                  |                  |                 |         |

| bit 12                |                                               | Block Transfer                                       |                                               |                                    |                  |                 |         |

|                       | 1 = Initiates i                               | nterrupt when                                        | half of the data                              | a has been mo                      |                  |                 |         |

| bit 11                |                                               | Data Periphera                                       |                                               |                                    |                  |                 |         |

|                       |                                               | write to periph                                      |                                               |                                    | e (DIR bit must  | also be clear)  |         |

| bit 10-6              | Unimplemen                                    | ted: Read as '                                       | 0'                                            |                                    |                  |                 |         |

| bit 5-4               | AMODE<1:0                                     | -: DMA Chann                                         | el Addressing                                 | Mode Select b                      | oits             |                 |         |

|                       | 11 = Reserve<br>10 = Periphe<br>01 = Register |                                                      | ressing mode<br>ut Post-Increm                | nent mode                          |                  |                 |         |

| bit 3-2               | •                                             | ted: Read as '                                       |                                               |                                    |                  |                 |         |

| bit 1-0               | -                                             | DMA Channel                                          |                                               | de Select bits                     |                  |                 |         |

|                       | 11 = One-Sho<br>10 = Continue                 | ot, Ping-Pong r<br>ous, Ping-Pong<br>ot, Ping-Pong r | nodes are ena<br>modes are e<br>nodes are dis | abled (one bloc<br>nabled<br>abled | ck transfer fror | n/to each DMA t | ouffer) |

## REGISTER 8-1: DMAXCON: DMA CHANNEL X CONTROL REGISTER

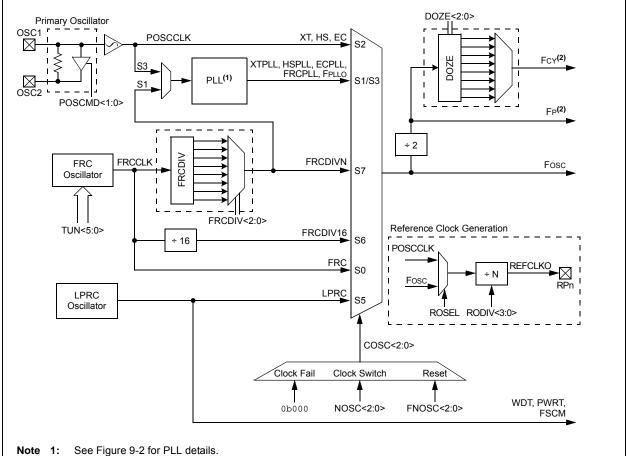

# 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

# FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

# REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- $\label{eq:constraint} \textbf{2:} \quad \text{This bit is cleared when the ROI bit is set and an interrupt occurs.}$

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

# REGISTER 11-17: RPINR39: PERIPHERAL PIN SELECT INPUT REGISTER 39 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0                     | R/W-0                                                     | R/W-0                | R/W-0             | R/W-0           | R/W-0           | R/W-0          |

|--------------|---------------------------|-----------------------------------------------------------|----------------------|-------------------|-----------------|-----------------|----------------|

| _            |                           |                                                           |                      | DTCMP3R<6:0       | )>              |                 |                |

| bit 15       |                           |                                                           |                      |                   |                 |                 | bit 8          |

|              | DAMA                      | DAMO                                                      | DAMO                 | DAMO              |                 | DAALO           | DAVO           |

| U-0          | R/W-0                     | R/W-0                                                     | R/W-0                | R/W-0             | R/W-0           | R/W-0           | R/W-0          |

|              |                           |                                                           |                      | DTCMP2R<6:0       | )>              |                 |                |

| bit 7        |                           |                                                           |                      |                   |                 |                 | bit 0          |

| Legend:      |                           |                                                           |                      |                   |                 |                 |                |

| R = Readab   | ole bit                   | W = Writable                                              | bit                  | U = Unimplen      | nented bit, rea | ad as '0'       |                |

| -n = Value a | at POR                    | '1' = Bit is set                                          |                      | '0' = Bit is clea | ared            | x = Bit is unkr | nown           |

|              |                           | Input tied to CMI                                         |                      |                   |                 |                 |                |

|              |                           | Input tied to Vss                                         |                      |                   |                 |                 |                |

| bit 7        | -                         | nted: Read as 'o                                          |                      |                   |                 |                 |                |

| bit 6-0      | (see Table 1<br>1111001 = | 6:0>: Assign PW<br>1-2 for input pin<br>Input tied to RPI | selection nun<br>121 |                   | n Input 2 to th | ne Correspondin | g RPn Pin bits |

|              |                           | Input tied to CMI<br>Input tied to Vss                    |                      |                   |                 |                 |                |

| U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         —       —       BCH <sup>(1)</sup> BCL <sup>(1)</sup> BPHH       BPHL       BPLL       BPLL         bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0         | R/W-0                                                                                                                     | R/W-0                            | R/W-0                            | R/W-0                   | R/W-0            | U-0               | U-0           |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------|-------------------------|------------------|-------------------|---------------|--|--|--|

| U-0       U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0          BCH <sup>(1)</sup> BCL <sup>(1)</sup> BPHH       BPHL       BPLH       BPLH         bit 7        B       Readable bit       U = Unimplemented bit, read as '0'           n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PWMxH Rising Edge Trigger Enable bit       1 = Reading-Edge Blanking ignores rising edge of PWMxH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | PHR           | PHF                                                                                                                       | PLR                              | PLF                              | FLTLEBEN                | CLLEBEN          | _                 |               |  |  |  |

| —         BCH <sup>(1)</sup> BCL <sup>(1)</sup> BPHH         BPHL         BPLH         BPLH         BPLH           bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15        |                                                                                                                           |                                  |                                  |                         |                  |                   | bit           |  |  |  |

| —         BCH <sup>(1)</sup> BCL <sup>(1)</sup> BPHH         BPHL         BPLH         BPLH         BPLH           bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | U-0           | U-0                                                                                                                       | R/W-0                            | R/W-0                            | R/W-0                   | R/W-0            | R/W-0             | R/W-0         |  |  |  |

| bit 7 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown bit 15 PHR: PWMxH Rising Edge Trigger Enable bit 1 = Rising edge of PWMxH will trigger Leading-Edge Blanking counter 0 = Leading-Edge Blanking ignores rising edge of PWMxH bit 1 PHF: PWMxH Raling Edge Trigger Enable bit 1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter 0 = Leading-Edge Blanking ignores falling edge of PWMxH bit 1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter 0 = Leading-Edge Blanking ignores falling edge of PWMxH bit 1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter 0 = Leading-Edge Blanking ignores rising edge of PWMxL bit 1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter 0 = Leading-Edge Blanking ignores rising edge of PWMxL bit 1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter 0 = Leading-Edge Blanking is applied to selected Fault input 1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter 0 = Leading-Edge Blanking is applied to selected Fault input 0 = Leading-Edge Blanking is applied to selected Fault input 0 = Leading-Edge Blanking is applied to selected Fault input 0 = Leading-Edge Blanking is applied to selected Crurent-limit input 0 = Leading-Edge Blanking is not applied to selected crurent-limit input 0 = Leading-Edge Blanking is not applied to selected crurent-limit input 0 = Leading-Edge Blanking is not applied to selected crurent-limit input 0 = Leading-Edge Blanking is not applied to selected Crurent-limit input 0 = Leading-Edge Blanking Signal High Enable bit 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high 0 = No blanking when selected blanking signal is low 0 = No blanking when selected blanking signal is low 0 = No blanking when selected blanking signal is low 0 = No blanking when selected blanking signal is low 0 = No blanking when PWMxH ubpt Enable bit 1 = Sta | _             |                                                                                                                           |                                  |                                  | 1                       | r                | 1                 | BPLL          |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PVMxH Rising Edge Trigger Enable bit       1 = Rising edge of PVMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PVMxH         bit 14       PHF: PVMxH Falling Edge Trigger Enable bit       1 = Falling edge of PVMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores falling edge of PVMxH         bit 13       PLR: PVMxL Rising Edge Trigger Enable bit       1 = Rising edge of PVMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PVMxL         bit 12       PLF: PVMxL Falling Edge Trigger Enable bit       1 = Falling edge of PVMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PVMxL         bit 11       FLTEBEN: Fault Input Leading-Edge Blanking Enable bit       1 = Leading-Edge Blanking is not applied to selected Fault input         bit 10       CLLEBEN: Current-Limit Leading-Edge Blanking is not applied to selected current-limit input       0 = Leading-Edge Blanking is not applied to selected current-limit input         bit 5       BCH: Blanking in Selected Blanking Signal High Enable bit       1 = Leading-Edge Blanking is inplied to selected current-limit input         bit 5       BCH: Blanking in Selected Blanking signal is high       1 = State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 7         |                                                                                                                           |                                  |                                  |                         |                  |                   | bit           |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       PHR: PVMxH Rising Edge Trigger Enable bit       1 = Rising edge of PVMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PVMxH         bit 14       PHF: PVMxH Falling Edge Trigger Enable bit       1 = Falling edge of PVMxH will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores falling edge of PVMxH         bit 13       PLR: PVMxL Rising Edge Trigger Enable bit       1 = Rising edge of PVMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PVMxL         bit 12       PLF: PVMxL Falling Edge Trigger Enable bit       1 = Falling edge of PVMxL will trigger Leading-Edge Blanking counter       0 = Leading-Edge Blanking ignores rising edge of PVMxL         bit 11       FLTEBEN: Fault Input Leading-Edge Blanking Enable bit       1 = Leading-Edge Blanking is not applied to selected Fault input         bit 10       CLLEBEN: Current-Limit Leading-Edge Blanking is not applied to selected current-limit input       0 = Leading-Edge Blanking is not applied to selected current-limit input         bit 5       BCH: Blanking in Selected Blanking Signal High Enable bit       1 = Leading-Edge Blanking is inplied to selected current-limit input         bit 5       BCH: Blanking in Selected Blanking signal is high       1 = State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Legend:       |                                                                                                                           |                                  |                                  |                         |                  |                   |               |  |  |  |

| <ul> <li>PHR: PWMxH Rising Edge Trigger Enable bit         <ul> <li>I = Rising edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>I = Raiding-Edge Blanking ignores rising edge of PWMxH</li> </ul> </li> <li>PHF: PWMxH Falling Edge Trigger Enable bit         <ul> <li>I = Falling edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>I = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>I = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>I = Rising edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>I = cading-Edge Blanking ignores rising edge of PWMxL</li> </ul> </li> <li>PLF: PWMxL Falling Edge Trigger Enable bit         <ul> <li>I = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>I = Leading-Edge Blanking ignores raling edge of PWMxL</li> </ul> </li> <li>DE: PWMxL Falling Edge Trigger Enable bit         <ul> <li>I = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>I = Leading-Edge Blanking is applied to selected Fault input</li> <li>I = Leading-Edge Blanking is not applied to selected Fault input</li> <li>I = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>I = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>I = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>I = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>I = Leading-Edge Blanking is not applied to selected blanking signal is high</li> <li>I = State blanking of current-limit and/or Fault input signals) when selected blanking signal is high</li> <li>I = State blanking (of current-limit and/or Fault input signals) when selected</li></ul></li></ul>                                                                                                                                                                                                                                                                      | -             | e bit                                                                                                                     | W = Writable                     | bit                              | U = Unimpler            | mented bit, read | as '0'            |               |  |  |  |

| 1 = Rising edge of PWMxH will rigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores rising edge of PWMxH         bit 14       PHF: PWMxH Falling Edge Trigger Enable bit         1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxH         bit 13       PLR: PWMxL Rising Edge Trigger Enable bit         1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores rising edge of PWMxL         bit 12       PLF: PWMxL Falling Edge Trigger Enable bit         1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 12       PLF: PWMxL Falling Edge Trigger Enable bit         1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking is applied to selected Fault input         0 = Leading-Edge Blanking is applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking Signal High Enable bit <sup>(1)</sup> 1 = Leading-Edge Blanking Signal Low Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high         bit 4       BCL: Blanking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -n = Value at | POR                                                                                                                       | '1' = Bit is set                 | :                                | '0' = Bit is cle        | ared             | x = Bit is unkr   | nown          |  |  |  |

| <ul> <li>1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxH</li> <li>bit 13 PLR: PWMxL Rising Edge Trigger Enable bit</li> <li>1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>bit 12 PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxL</li> <li>bit 12 PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxL</li> <li>bit 11 FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit</li> <li>1 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking Signal High Enable bit</li> <li>1 = State blanking (or current-limit and/or Fault input signals) when selected blanking signal is high</li> <li>0 = No blanking when selected blanking Signal is low</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>No blanking when PWMxH output is low</li> <li>1 = State blanking (of current-limit and/or Fault input signals</li></ul>                                                                                               | bit 15        | 1 = Rising ed                                                                                                             | ge of PWMxH                      | will trigger Le                  | ading-Edge Bla          |                  |                   |               |  |  |  |

| <ul> <li>1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores rising edge of PWMxL</li> <li>bit 12 PLF: PWMxL Falling Edge Trigger Enable bit</li> <li>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter</li> <li>0 = Leading-Edge Blanking ignores falling edge of PWMxL</li> <li>bit 11 FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit</li> <li>1 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when selected blanking signal is high</li> <li>bit 4 BCL: Blanking in Selected Blanking Signal Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when Selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>bit 3 BPHH: Blanking in PWMxH dutput is high</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 =</li></ul>                                                                                               | bit 14        | 1 = Falling edge of PWMxH will trigger Leading-Edge Blanking counter                                                      |                                  |                                  |                         |                  |                   |               |  |  |  |

| 1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter         0 = Leading-Edge Blanking ignores falling edge of PWMxL         bit 11       FLTLEBEN: Fault Input Leading-Edge Blanking Enable bit         1 = Leading-Edge Blanking is applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected Fault input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = Leading-Edge Blanking is not applied to selected current-limit input         0 = No blanking in Selected Blanking Signal High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         bit 3       BPHH: Blanking in PWMxH High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high         bit 2       BPHL: Blanking in PWMxH Low Enable bit         1 = State blanking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 13        | 1 = Rising edge of PWMxL will trigger Leading-Edge Blanking counter                                                       |                                  |                                  |                         |                  |                   |               |  |  |  |

| <ul> <li>1 = Leading-Edge Blanking is applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>0 = Leading-Edge Blanking is not applied to selected Fault input</li> <li>1 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking Signal High Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL dutput is high</li> <li>0 = No blanking when PWMxL cutput is high</li> <li>0 = No blanking when PWMxL cutput is high</li> <li>0 = No blanking when PWMxL cutput is high</li> </ul>                                                                                                  | bit 12        | <b>PLF:</b> PWMxL Falling Edge Trigger Enable bit<br>1 = Falling edge of PWMxL will trigger Leading-Edge Blanking counter |                                  |                                  |                         |                  |                   |               |  |  |  |

| <ul> <li>1 = Leading-Edge Blanking is applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>0 = Leading-Edge Blanking is not applied to selected current-limit input</li> <li>bit 9-6</li> <li>Unimplemented: Read as '0'</li> <li>BCH: Blanking in Selected Blanking Signal High Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is hig</li> <li>0 = No blanking when selected blanking Signal Low Enable bit<sup>(1)</sup></li> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking in Current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 2</li> <li>BPHL: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>bit 1</li> <li>BPLH: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is high</li> <li>bit 0</li> <li>BPLL: Blanking in PWMxL Low Enable bit</li> <li>1 = State blanking (of curr</li></ul>                                                                                             | bit 11        | 1 = Leading-E                                                                                                             | Edge Blanking                    | is applied to                    | selected Fault in       | nput             |                   |               |  |  |  |

| bit 5       BCH: Blanking in Selected Blanking Signal High Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high         bit 4       BCL: Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         bit 4       BCL: Blanking in Selected Blanking Signal Low Enable bit <sup>(1)</sup> 1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low         bit 3       BPHH: Blanking in PWMxH High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high         0 = No blanking when PWMxH output is high         bit 2       BPHL: Blanking in PWMxH Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low         0 = No blanking when PWMxH output is low         bit 1       BPLH: Blanking in PWMxH tigh Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         bit 1       BPLH: Blanking in PWMxL High Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         bit 0       BPLL: Blanking in PWMxL Low Enable bit         1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high         bit 0<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 10        | 1 = Leading-E                                                                                                             | Edge Blanking                    | is applied to                    | selected current        | t-limit input    |                   |               |  |  |  |

| <ul> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is high</li> <li>bit 4 BCL: Blanking in Selected Blanking Signal Low Enable bit<sup>(1)</sup> <ol> <li>1 = State blanking (of current-limit and/or Fault input signals) when selected blanking signal is low</li> <li>0 = No blanking when selected blanking signal is low</li> <li>0 = No blanking in PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking when PWMxH High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is high</li> <li>0 = No blanking when PWMxH output is high</li> </ol> </li> <li>bit 2 BPHL: Blanking in PWMxH Low Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxH output is low</li> <li>0 = No blanking when PWMxH output is low</li> <li>bit 1 BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is low</li> <li>bit 1 BPLH: Blanking in PWMxL High Enable bit</li> <li>1 = State blanking (of current-limit and/or Fault input signals) when PWMxL output is high</li> <li>0 = No blanking when PWMxL output is low</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 9-6       | Unimplemen                                                                                                                | ted: Read as '                   | 0'                               |                         |                  |                   |               |  |  |  |