#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

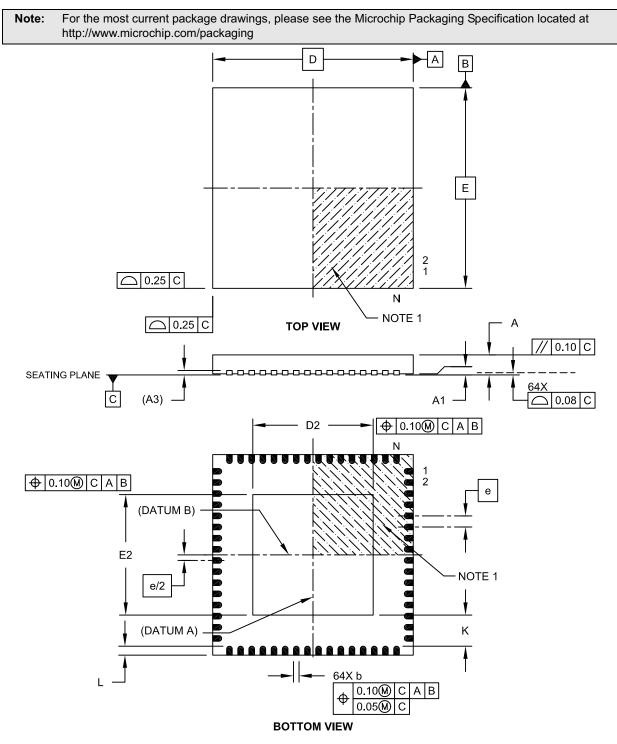

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gp504-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

## 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

## 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

#### FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

|                 |       |                                        |                         |         |         |         |             |         |         |             |        |        |        |          |          |       |        | All    |

|-----------------|-------|----------------------------------------|-------------------------|---------|---------|---------|-------------|---------|---------|-------------|--------|--------|--------|----------|----------|-------|--------|--------|

| File Name       | Addr. | Bit 15                                 | Bit 14                  | Bit 13  | Bit 12  | Bit 11  | Bit 10      | Bit 9   | Bit 8   | Bit 7       | Bit 6  | Bit 5  | Bit 4  | Bit 3    | Bit 2    | Bit 1 | Bit 0  | Resets |

| PTGCST          | 0AC0  | PTGEN                                  | —                       | PTGSIDL | PTGTOGL |         | PTGSWT      | PTGSSEN | PTGIVIS | PTGSTRT     | PTGWTO | _      | _      | —        | —        | PTGIT | M<1:0> | 0000   |

| PTGCON          | 0AC2  | F                                      | PTGCLK<2:0> PTGDIV<4:0> |         |         |         |             |         | PTGPWD  | <3:0>       |        | _      | P      | TGWDT<2: | 0>       | 0000  |        |        |

| PTGBTE          | 0AC4  | ADCTS<4:1> IC4TSS IC3TSS IC2TSS IC1TSS |                         |         |         | IC1TSS  | OC4CS       | OC3CS   | OC2CS   | OC1CS       | OC4TSS | OC3TSS | OC2TSS | OC1TSS   | 0000     |       |        |        |

| PTGHOLD         | 0AC6  | PTGHOLD<15:0>                          |                         |         |         |         |             |         |         | 0000        |        |        |        |          |          |       |        |        |

| <b>PTGT0LIM</b> | 0AC8  |                                        | PTGT0LIM<15:0>          |         |         |         |             |         |         |             | 0000   |        |        |          |          |       |        |        |

| PTGT1LIM        | 0ACA  |                                        | PTGT1LIM<15:0>          |         |         |         |             |         |         |             | 0000   |        |        |          |          |       |        |        |

| PTGSDLIM        | 0ACC  |                                        | PTGSDLIM<15:0>          |         |         |         |             |         |         |             | 0000   |        |        |          |          |       |        |        |

| <b>PTGC0LIM</b> | 0ACE  | PTGC0LIM<15:0>                         |                         |         |         |         |             |         |         | 0000        |        |        |        |          |          |       |        |        |

| PTGC1LIM        | 0AD0  | PTGC1LIM<15:0>                         |                         |         |         |         |             |         |         | 0000        |        |        |        |          |          |       |        |        |

| PTGADJ          | 0AD2  |                                        |                         |         |         |         |             |         | PTGADJ< | :15:0>      |        |        |        |          |          |       |        | 0000   |

| PTGL0           | 0AD4  |                                        |                         |         |         |         |             |         | PTGL0<  | 15:0>       |        |        |        |          |          |       |        | 0000   |

| PTGQPTR         | 0AD6  | —                                      | —                       | —       | —       | _       | —           | —       | _       | —           | —      | -      |        | P        | TGQPTR<4 | 4:0>  |        | 0000   |

| PTGQUE0         | 0AD8  |                                        |                         |         | STEP    | 1<7:0>  |             |         |         |             |        |        | STEPO  | )<7:0>   |          |       |        | 0000   |

| PTGQUE1         | 0ADA  |                                        |                         |         | STEP    | '3<7:0> |             |         |         |             |        |        | STEP2  | 2<7:0>   |          |       |        | 0000   |

| PTGQUE2         | 0ADC  |                                        |                         |         | STEP    | 25<7:0> |             |         |         |             |        |        | STEP4  | <7:0>    |          |       |        | 0000   |

| PTGQUE3         | 0ADE  |                                        |                         |         | STEP    | 7<7:0>  |             |         |         |             |        |        | STEP6  | 6<7:0>   |          |       |        | 0000   |

| PTGQUE4         | 0AE0  | STEP9<7:0>                             |                         |         |         |         | STEP8<7:0>  |         |         |             | 0000   |        |        |          |          |       |        |        |

| PTGQUE5         | 0AE2  | STEP11<7:0>                            |                         |         |         |         | STEP10<7:0> |         |         |             |        | 0000   |        |          |          |       |        |        |

| PTGQUE6         | 0AE4  | STEP13<7:0>                            |                         |         |         |         | STEP12<7:0> |         |         |             |        | 0000   |        |          |          |       |        |        |

| PTGQUE7         | 0AE6  |                                        |                         |         | STEP    | 15<7:0> |             |         |         | STEP14<7:0> |        |        |        | 0000     |          |       |        |        |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 78

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

|             | -                   | SV SI ACE BOON |              |                        |                |   |                        |  |

|-------------|---------------------|----------------|--------------|------------------------|----------------|---|------------------------|--|

| 0/11        |                     |                | Before       |                        | After          |   |                        |  |

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DATPAG         |   | Page<br>Description    |  |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0 | See Note 1             |  |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1 | PSV: First MSB<br>page |  |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0 | See Note 1             |  |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0 | See Note 1             |  |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0 | See Note 1             |  |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0 | See Note 1             |  |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1 | PSV: Last Isw<br>page  |  |

## TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

| Oscillator Mode                                            | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | See<br>Notes |

|------------------------------------------------------------|-------------------|-------------|------------|--------------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)              | Internal          | xx          | 111        | 1, 2         |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)            | Internal          | xx          | 110        | 1            |

| Low-Power RC Oscillator (LPRC)                             | Internal          | xx          | 101        | 1            |

| Primary Oscillator (HS) with PLL (HSPLL)                   | Primary           | 10          | 011        |              |

| Primary Oscillator (XT) with PLL (XTPLL)                   | Primary           | 01          | 011        |              |

| Primary Oscillator (EC) with PLL (ECPLL)                   | Primary           | 0.0         | 011        | 1            |

| Primary Oscillator (HS)                                    | Primary           | 10          | 010        |              |

| Primary Oscillator (XT)                                    | Primary           | 01          | 010        |              |

| Primary Oscillator (EC)                                    | Primary           | 00          | 010        | 1            |

| Fast RC Oscillator (FRC) with Divide-by-N and PLL (FRCPLL) | Internal          | xx          | 001        | 1            |

| Fast RC Oscillator (FRC)                                   | Internal          | xx          | 000        | 1            |

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

2: This is the default oscillator mode for an unprogrammed (erased) device.

#### 9.2 Oscillator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your brouger. |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | this URL in your browser:<br>http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464           |

#### 9.2.1 KEY RESOURCES

- "Oscillator" (DS70580) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- · Development Tools

## **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 4 Unimplemented: Read as '0'

- bit 3 **CF:** Clock Fail Detect bit<sup>(3)</sup>

- 1 = FSCM has detected clock failure

- 0 = FSCM has not detected clock failure

- bit 2-1 Unimplemented: Read as '0'

- bit 0 OSWEN: Oscillator Switch Enable bit

- 1 = Requests oscillator switch to selection specified by the NOSC<2:0> bits

- 0 = Oscillator switch is complete

- **Note 1:** Writes to this register require an unlock sequence. Refer to **"Oscillator"** (DS70580) in the *"dsPIC33/ PIC24 Family Reference Manual"* (available from the Microchip web site) for details.

- 2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transitional clock source between the two PLL modes.

- **3:** This bit should only be cleared in software. Setting the bit in software (= 1) will have the same effect as an actual oscillator failure and trigger an oscillator failure trap.

| U-0          | U-0                 | U-0                                | U-0   | U-0                                | U-0             | U-0                | U-0   |  |

|--------------|---------------------|------------------------------------|-------|------------------------------------|-----------------|--------------------|-------|--|

| —            | —                   | —                                  | _     | —                                  | —               | —                  | _     |  |

| bit 15       |                     |                                    |       |                                    |                 |                    | bit 8 |  |

|              |                     |                                    |       |                                    |                 |                    |       |  |

| U-0          | R/W-0               | R/W-0                              | R/W-0 | R/W-0                              | R/W-0           | R/W-0              | R/W-0 |  |

| —            |                     |                                    |       | INT2R<6:0>                         |                 |                    |       |  |

| bit 7        |                     |                                    |       |                                    |                 |                    | bit 0 |  |

|              |                     |                                    |       |                                    |                 |                    |       |  |

| Legend:      |                     |                                    |       |                                    |                 |                    |       |  |

| R = Readal   | ole bit             | W = Writable bit                   |       | U = Unimplemented bit, read as '0' |                 |                    |       |  |

| -n = Value a | at POR              | '1' = Bit is set                   |       | '0' = Bit is cle                   | ared            | x = Bit is unknown |       |  |

|              |                     |                                    |       |                                    |                 |                    |       |  |

| bit 15-7     | Unimplemen          | ted: Read as 'd                    | )'    |                                    |                 |                    |       |  |

| bit 6-0      |                     | Assign Externa<br>-2 for input pin |       |                                    | orresponding RI | Pn Pin bits        |       |  |

|              | 1111001 <b>= lr</b> | put tied to RPI                    | 121   |                                    |                 |                    |       |  |

|              |                     |                                    |       |                                    |                 |                    |       |  |

|              |                     |                                    |       |                                    |                 |                    |       |  |

|              | 0000001 – Ir        | put tied to CMI                    | ⊃1    |                                    |                 |                    |       |  |

|              |                     | put tied to Civil                  |       |                                    |                 |                    |       |  |

|              |                     |                                    |       |                                    |                 |                    |       |  |

|              |                     |                                    |       |                                    |                 |                    |       |  |

#### REGISTER 11-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

#### REGISTER 11-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

| U-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0<br>— T2CKR<6:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |                     |                  |       |                  |                  |                    |       |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------|------------------|-------|------------------|------------------|--------------------|-------|--|--|--|

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0          | U-0                 | U-0              | U-0   | U-0              | U-0              | U-0                | U-0   |  |  |  |

| U-0       R/W-0       R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _            | -                   | —                | _     | —                | —                | —                  | —     |  |  |  |

| —       T2CKR<6:0>         bit 7       t         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 15       |                     |                  |       |                  |                  |                    | bit 8 |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                  |                  |                    |       |  |  |  |

| bit 7       Image: Constraint of the system of | U-0          | R/W-0               | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0              | R/W-0 |  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . <td< td=""><td>—</td><td></td><td colspan="9">T2CKR&lt;6:0&gt;</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —            |                     | T2CKR<6:0>       |       |                  |                  |                    |       |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 7        |                     |                  |       |                  |                  |                    | bit 0 |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |                     |                  |       |                  |                  |                    |       |  |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-7       Unimplemented: Read as '0'         bit 6-0       T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits (see Table 11-2 for input pin selection numbers)         1111001 = Input tied to RPI121         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Legend:      |                     |                  |       |                  |                  |                    |       |  |  |  |

| bit 15-7 Unimplemented: Read as '0'<br>bit 6-0 T2CKR<6:0>: Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121<br>0000001 = Input tied to CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R = Readab   | ole bit             | W = Writable I   | bit   | U = Unimpler     | mented bit, read | as '0'             |       |  |  |  |

| bit 6-0 <b>T2CKR&lt;6:0&gt;:</b> Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -n = Value a | at POR              | '1' = Bit is set |       | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |  |  |

| bit 6-0 <b>T2CKR&lt;6:0&gt;:</b> Assign Timer2 External Clock (T2CK) to the Corresponding RPn pin bits<br>(see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |                     |                  |       |                  |                  |                    |       |  |  |  |

| (see Table 11-2 for input pin selection numbers)<br>1111001 = Input tied to RPI121<br>0000001 = Input tied to CMP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 15-7     | Unimplemen          | ted: Read as 'd  | )'    |                  |                  |                    |       |  |  |  |

| 1111001 = Input tied to RPI121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 6-0      |                     | •                |       | · · ·            | he Correspondir  | ng RPn pin bits    | 5     |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       | ,                |                  |                    |       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                  |                  |                    |       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |                     |                  |       |                  |                  |                    |       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 0000001 = Ir        | nout tied to CM  | ⊃1    |                  |                  |                    |       |  |  |  |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |                     |                  |       |                  |                  |                    |       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |              | 0000000 <b>- II</b> | iput tied to vss |       |                  |                  |                    |       |  |  |  |

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                        | U-0                                                                        | R/W-0           | R/W-0      | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |  |

|----------------------------|----------------------------------------------------------------------------|-----------------|------------|------------------------------------|-------|--------------------|-------|--|--|

| _                          | —                                                                          |                 | RP39R<5:0> |                                    |       |                    |       |  |  |

| bit 15                     |                                                                            |                 |            |                                    |       |                    | bit 8 |  |  |

|                            |                                                                            |                 |            |                                    |       |                    |       |  |  |

| U-0                        | U-0                                                                        | R/W-0           | R/W-0      | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |  |

| —                          | —                                                                          |                 | RP38R<5:0> |                                    |       |                    |       |  |  |

| bit 7                      |                                                                            |                 |            |                                    |       |                    | bit 0 |  |  |

|                            |                                                                            |                 |            |                                    |       |                    |       |  |  |

| Legend:                    |                                                                            |                 |            |                                    |       |                    |       |  |  |

| R = Readable               | e bit                                                                      | W = Writable    | bit        | U = Unimplemented bit, read as '0' |       |                    |       |  |  |

| -n = Value at POR '1' = Bi |                                                                            |                 |            | '0' = Bit is clea                  | ared  | x = Bit is unknown |       |  |  |

|                            |                                                                            |                 |            |                                    |       |                    |       |  |  |

| bit 15-14                  | Unimplemer                                                                 | nted: Read as ' | 0'         |                                    |       |                    |       |  |  |

| bit 13-8                   | RP39R<5:0>: Peripheral Output Function is Assigned to RP39 Output Pin bits |                 |            |                                    |       |                    |       |  |  |

#### REGISTER 11-20: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

|         | (see Table 11-3 for peripheral function numbers)                           |

|---------|----------------------------------------------------------------------------|

| bit 7-6 | Unimplemented: Read as '0'                                                 |

| bit 5-0 | RP38R<5:0>: Peripheral Output Function is Assigned to RP38 Output Pin bits |

|         | (see Table 11-3 for peripheral function numbers)                           |

#### REGISTER 11-21: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP41  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|

| —     | —   |       | RP40R<5:0> |       |       |       |       |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP41R<5:0>:** Peripheral Output Function is Assigned to RP41 Output Pin bits (see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP40R<5:0>:** Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 11-3 for peripheral function numbers)

| R/W-0         | R/W-0       | R/W-0                                  | U-0          | U-0              | U-0             | U-0               | U-0    |

|---------------|-------------|----------------------------------------|--------------|------------------|-----------------|-------------------|--------|

| FRMEN         | SPIFSD      | FRMPOL                                 | —            | —                | _               | —                 | —      |

| bit 15        |             |                                        |              |                  |                 |                   | bit 8  |

|               |             |                                        |              |                  |                 |                   |        |

| U-0           | U-0         | U-0                                    | U-0          | U-0              | U-0             | R/W-0             | R/W-0  |

| _             | <u> </u>    | —                                      | _            |                  | _               | FRMDLY            | SPIBEN |

| bit 7         |             |                                        |              |                  |                 |                   | bit 0  |

|               |             |                                        |              |                  |                 |                   |        |

| Legend:       |             |                                        |              |                  |                 |                   |        |

| R = Readable  | e bit       | W = Writable b                         | pit          | U = Unimpler     | nented bit, rea | ad as '0'         |        |

| -n = Value at | POR         | '1' = Bit is set                       |              | '0' = Bit is cle | ared            | x = Bit is unkr   | nown   |

|               |             |                                        |              |                  |                 |                   |        |

| bit 15        | FRMEN: Fra  | med SPIx Suppo                         | ort bit      |                  |                 |                   |        |

|               |             | SPIx support is e<br>SPIx support is d |              | x pin is used as | Frame Sync      | oulse input/outpu | ıt)    |

| bit 14        | SPIFSD: Fra | me Sync Pulse [                        | Direction Co | ontrol bit       |                 |                   |        |

|               |             | ync pulse input (<br>ync pulse output  |              |                  |                 |                   |        |

| bit 13        | FRMPOL: Fr  | ame Sync Pulse                         | Polarity bit | t                |                 |                   |        |

|               |             | ync pulse is activ                     | •            |                  |                 |                   |        |

|               |             | ync pulse is activ                     |              |                  |                 |                   |        |

| bit 12-2      | -           | nted: Read as '0                       |              |                  |                 |                   |        |

| bit 1         |             | ame Sync Pulse                         | -            |                  |                 |                   |        |

|               |             | ync pulse coincio<br>ync pulse preceo  |              |                  |                 |                   |        |

| bit 0         | SPIBEN: En  | hanced Buffer Er                       | nable bit    |                  |                 |                   |        |

|               |             | d buffer is enable                     |              |                  |                 |                   |        |

|               | 0 = Enhance | d buffer is disabl                     | ed (Standa   | rd mode)         |                 |                   |        |

|               |             |                                        |              |                  |                 |                   |        |

#### REGISTER 18-3: SPIXCON2: SPIX CONTROL REGISTER 2

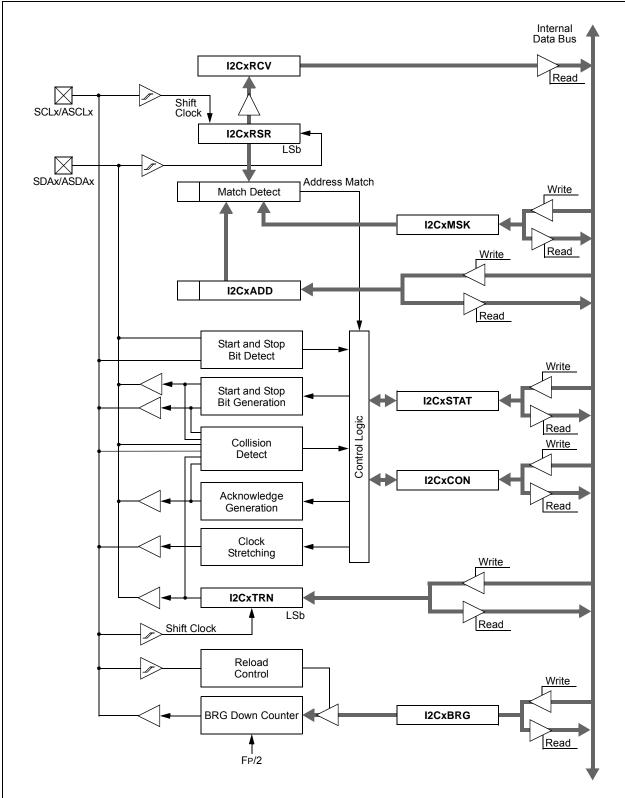

FIGURE 19-1: I2Cx BLOCK DIAGRAM (X = 1 OR 2)

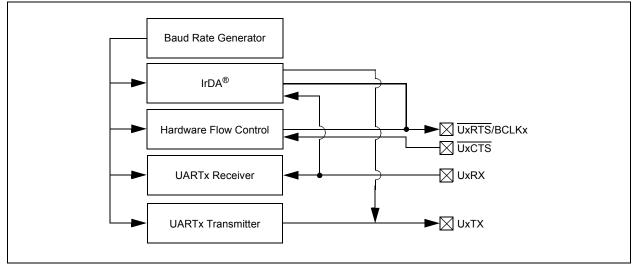

## 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "UART" (DS70582) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two UART modules.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

Note: <u>Hardware</u> flow control using UxRTS and UxCTS is not available on all pin count devices. See the "**Pin Diagrams**" section for availability.

The primary features of the UARTx module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 4.375 Mbps to 67 bps at 16x mode at 70 MIPS

- Baud Rates Ranging from 17.5 Mbps to 267 bps at 4x mode at 70 MIPS

- 4-Deep First-In First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-bit mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- A Separate Interrupt for all UARTx Error Conditions

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- Support for Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UARTx module is shown in Figure 20-1. The UARTx module consists of these key hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### FIGURE 20-1: UARTx SIMPLIFIED BLOCK DIAGRAM

© 2011-2013 Microchip Technology Inc.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                                                                          | U-0        | U-0                                 | U-0            | U-0                                | U-0    | U-0                | U-0    |  |