Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Betails                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gp504-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

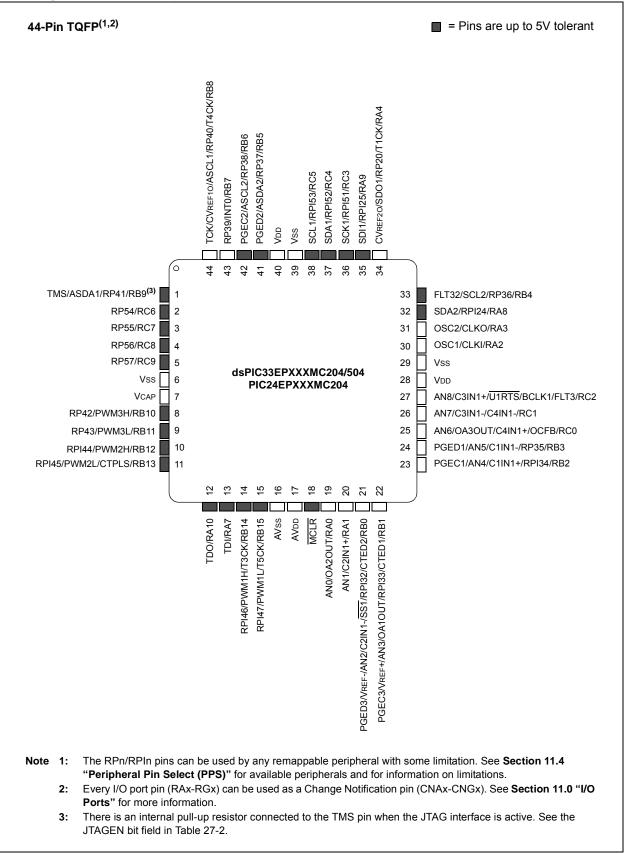

### Pin Diagrams (Continued)

### **Pin Diagrams (Continued)**

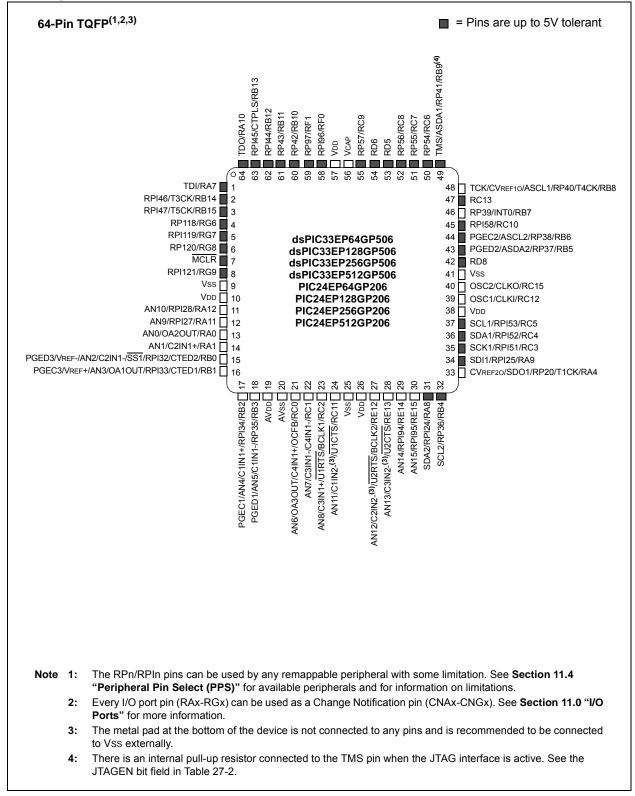

#### FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP256GP50X, dsPIC33EP256MC20X/50X AND PIC24EP256GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

| TABLE 4 | 4-31: | PER | IPHERA | L PIN S | ELECT | INPUT F | REGISTI | ER MAP | FOR de | sPIC33E | EPXXXG | P50X D | EVICES | SONLY |  |

|---------|-------|-----|--------|---------|-------|---------|---------|--------|--------|---------|--------|--------|--------|-------|--|

|         |       |     |        |         |       |         |         |        |        |         |        |        |        |       |  |

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6     | Bit 5     | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|-----------|--------|------------|--------|-------|-------|-------|-----------|-----------|-------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | —      |        |           |        | INT1R<6:0> |        |       |       | _     | _         | —         | —     | —          | —     | —     | _     | 0000          |

| RPINR1       | 06A2  |        | _      | _         | _      | _          | _      | _     | _     | _     |           |           |       | INT2R<6:0> | •     |       |       | 0000          |

| RPINR3       | 06A6  |        | _      | _         | _      | _          | _      | _     |       |       | ٦         | [2CKR<6:0 | >     |            |       | 0000  |       |               |

| RPINR7       | 06AE  |        |        | IC2R<6:0> |        |            |        |       |       | _     |           |           |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  |        |        |           |        | IC4R<6:0>  |        |       |       | _     |           |           |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6  |        | _      | _         | _      | _          | _      | _     | _     | _     |           |           | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR18      | 06C4  |        | _      | _         | _      | _          | _      | _     | _     | _     |           |           | ι     | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19      | 06C6  |        | _      | _         | _      | _          | _      | _     | _     | _     |           |           | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22      | 06CC  |        |        |           | S      | CK2INR<6:0 | )>     |       |       | _     |           |           | :     | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23      | 06CE  | _      | _      | _         | —      | —          | _      | _     | —     | —     | 0000 -0.0 |           |       |            |       |       |       | 0000          |

| RPINR26      | 06D4  | —      | _      | _         | -      | _          | _      | —     |       | —     |           |           | (     | C1RXR<6:0  | >     |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-32:** PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13       | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4     | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------------|--------|------------|--------|-------|-------|-------|-------|-------|-----------|------------|-------|-------|-------|---------------|

| RPINR0    | 06A0  | _      |        |              |        | INT1R<6:0> |        |       |       | —     | —     | —     | —         | —          | —     | —     | _     | 0000          |

| RPINR1    | 06A2  |        | _      | _            | _      | _          | _      | _     | _     | _     |       |       |           | INT2R<6:0> |       |       |       | 0000          |

| RPINR3    | 06A6  |        | _      | _            | _      | _          | _      | _     | _     | _     |       |       | -         | F2CKR<6:0  | >     |       |       | 0000          |

| RPINR7    | 06AE  |        |        |              |        | IC2R<6:0>  |        |       |       | _     |       |       |           | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8    | 06B0  |        |        | IC4R<6:0>    |        |            |        |       | _     |       |       |       | IC3R<6:0> |            |       |       | 0000  |               |

| RPINR11   | 06B6  |        | _      |              |        |            |        | _     | _     |       |       | (     | DCFAR<6:0 | >          |       |       | 0000  |               |

| RPINR12   | 06B8  |        |        |              |        | FLT2R<6:0> | •      |       |       | _     |       |       |           | FLT1R<6:0> | •     |       |       | 0000          |

| RPINR14   | 06BC  |        |        |              | (      | QEB1R<6:0  | >      |       |       | _     |       |       | (         | QEA1R<6:0  | >     |       |       | 0000          |

| RPINR15   | 06BE  |        |        |              | Н      | OME1R<6:0  | )>     |       |       | _     |       |       | I         | NDX1R<6:0  | >     |       |       | 0000          |

| RPINR18   | 06C4  |        | _      | _            | _      | _          | _      | _     | _     | _     |       |       | ι         | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19   | 06C6  |        | _      | _            | _      | _          | _      | _     | _     | _     |       |       | ι         | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22   | 06CC  | _      |        |              | S      | CK2INR<6:( | )>     |       |       | —     |       |       |           | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23   | 06CE  | _      | —      | —            |        | —          | —      |       | —     | —     |       |       |           | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26   | 06D4  | _      | _      | _            |        | —          | —      |       | —     | —     |       |       | (         | C1RXR<6:0  | >     |       |       | 0000          |

| RPINR37   | 06EA  | _      |        | SYNCI1R<6:0> |        |            |        |       |       | —     | —     | —     | —         | —          |       |       |       | 0000          |

| RPINR38   | 06EC  | _      |        |              | D      | CMP1R<6:   | 0>     |       |       | —     | —     | —     | —         | _          |       |       |       | 0000          |

| RPINR39   | 06EE  | _      |        |              | D      | FCMP3R<6:  | 0>     |       |       | _     |       |       | D         | CMP2R<6:   | 0>    |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### TABLE 4-34: NVM REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3    | Bit 2 | Bit 1   | Bit 0 | All<br>Resets |  |  |  |  |

|-----------|-------|--------|--------|--------|---------|--------|--------|-------|-------|----------|-------|-------|--------|----------|-------|---------|-------|---------------|--|--|--|--|

| NVMCON    | 0728  | WR     | WREN   | WRERR  | NVMSIDL | _      | _      | —     | _     | _        | _     | _     | —      |          | NVMC  | )P<3:0> |       | 0000          |  |  |  |  |

| NVMADRL   | 072A  |        |        |        |         |        |        |       | NVMAD | )R<15:0> |       |       |        |          |       |         | 0000  |               |  |  |  |  |

| NVMADRH   | 072C  | _      | _      | _      | _       | -      | _      | _     | _     |          |       |       | NVMADF | R<23:16> |       |         | 0000  |               |  |  |  |  |

| NVMKEY    | 072E  |        |        | _      | —       | _      |        | —     | -     |          |       |       | NVMKE  | Y<7:0>   |       |         |       |               |  |  |  |  |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-35: SYSTEM CONTROL REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8      | Bit 7   | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|-----------|--------|--------|--------|-----------|------------|---------|--------|--------|-------|-------|--------|-------|-------|---------------|

| RCON      | 0740  | TRAPR  | IOPUWR | _         | _      | VREGSF | _      | СМ        | VREGS      | EXTR    | SWR    | SWDTEN | WDTO  | SLEEP | IDLE   | BOR   | POR   | Note 1        |

| OSCCON    | 0742  | _      | 0      | COSC<2:0> |        | —      |        | NOSC<2:0> |            | CLKLOCK | IOLOCK | LOCK   | _     | CF    | _      | _     | OSWEN | Note 2        |

| CLKDIV    | 0744  | ROI    | [      | OOZE<2:0> |        | DOZEN  | F      | RCDIV<2:0 | >          | PLLPOS  | T<1:0> | _      |       | F     | LLPRE< | 4:0>  |       | 0030          |

| PLLFBD    | 0746  | _      | _      | _         | _      | —      | _      | _         | DLL DNL 60 |         |        |        |       | 0030  |        |       |       |               |

| OSCTUN    | 0748  | _      | _      | _         | _      | —      | _      | _         | _          | _       |        |        |       | TUN≤  | <5:0>  |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration Fuses.

### TABLE 4-36: REFERENCE CLOCK REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| REFOCON   | 074E  | ROON   | —      | ROSSLP | ROSEL  |        | RODI   | V<3:0> |       | _     | _     | —     | _     | _     | —     | _     | -     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-49: PORTD REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|--------|--------|-------|-------|-------|-------|-------|---------------|

| TRISD        | 0E30  | _      | _      | _      |        | _      | _      | _     | TRISD8 |       | TRISD6 | TRISD5 |       |       |       |       | _     | 0160          |

| PORTD        | 0E32  | _      | _      |        | _      | _      | _      |       | RD8    | —     | RD6    | RD5    | —     | _     | _     | _     |       | xxxx          |

| LATD         | 0E34  | _      | _      |        | _      | _      | _      |       | LATD8  | —     | LATD6  | LATD5  | —     | _     | _     | _     |       | xxxx          |

| ODCD         | 0E36  | _      |        |        | -      |        |        |       | ODCD8  | —     | ODCD6  | ODCD5  | —     | _     | _     | _     |       | 0000          |

| CNEND        | 0E38  | _      |        |        | -      |        |        |       | CNIED8 | —     | CNIED6 | CNIED5 | —     | _     | _     | _     |       | 0000          |

| CNPUD        | 0E3A  | _      | _      |        | _      | _      | _      |       | CNPUD8 | —     | CNPUD6 | CNPUD5 | —     | _     | _     | _     |       | 0000          |

| CNPDD        | 0E3C  | _      | _      |        | _      | _      | _      |       | CNPDD8 | —     | CNPDD6 | CNPDD5 | —     | _     | _     | _     |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-50: PORTE REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISE        | 0E40  | TRISE15 | TRISE14 | TRISE13 | TRISE12 | —      | _      | _     | —     | _     |       | -     | —     | —     | _     | —     |       | F000          |

| PORTE        | 0E42  | RE15    | RE14    | RE13    | RE12    | _      | —      | —     | —     | -     | —     | —     | _     | —     | —     | —     | —     | xxxx          |

| LATE         | 0E44  | LATE15  | LATE14  | LATE13  | LATE12  | _      | _      |       | —     | _     | _     |       | _     | —     | -     | —     | _     | xxxx          |

| ODCE         | 0E46  | ODCE15  | ODCE14  | ODCE13  | ODCE12  | —      | -      | -     | _     |       |       | -     | —     | —     | _     | _     | -     | 0000          |

| CNENE        | 0E48  | CNIEE15 | CNIEE14 | CNIEE13 | CNIEE12 | _      | —      | —     | —     | -     | —     | —     | _     | —     | —     | —     | —     | 0000          |

| CNPUE        | 0E4A  | CNPUE15 | CNPUE14 | CNPUE13 | CNPUE12 | _      | _      |       | —     | _     | _     |       | _     | —     | -     | —     | _     | 0000          |

| CNPDE        | 0E4C  | CNPDE15 | CNPDE14 | CNPDE13 | CNPDE12 | _      | _      | _     | _     | -     | _     | —     | _     | —     | _     | _     | _     | 0000          |

| ANSELE       | 0E4E  | ANSE15  | ANSE14  | ANSE13  | ANSE12  |        | —      | _     | —     | _     | _     | _     |       |       | _     |       | _     | F000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-51: PORTF REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISF        | 0E50  | —      | -      | —      |        | —      |        | —     | -     | -     | —     | -     | -     | —     | -     | TRISF1 | TRISF0 | 0003          |

| PORTF        | 0E52  | —      | —      | _      | —      | —      | —      | —     | _     | —     | —     | —     | —     | —     | —     | RF1    | RF0    | xxxx          |

| LATF         | 0E54  | —      | —      | —      | —      | —      | —      | —     | —     | —     | —     | —     | —     | —     | —     | LATF1  | LATF0  | xxxx          |

| ODCF         | 0E56  | _      | -      | _      | -      | —      | -      | —     |       |       | —     |       |       | _     | -     | ODCF1  | ODCF0  | 0000          |

| CNENF        | 0E58  |        | —      | -      |        | —      | -      | _     | -     | -     | —     | -     | -     | —     | -     | CNIEF1 | CNIEF0 | 0000          |

| CNPUF        | 0E5A  | —      | —      | —      | —      | —      | —      | —     | —     | —     | —     | —     | —     | —     | —     | CNPUF1 | CNPUF0 | 0000          |

| CNPDF        | 0E5C  | _      | _      | _      | _      | -      |        | _     | _     | _     | _     | _     | _     | _     | -     | CNPDF1 | CNPDF0 | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

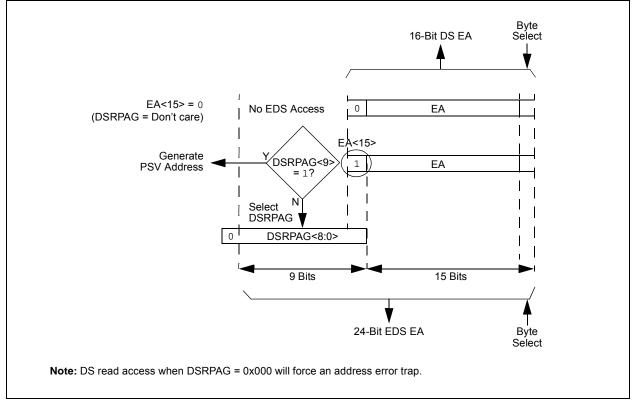

### 4.4.1 PAGED MEMORY SCHEME

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture extends the available Data Space through a paging scheme, which allows the available Data Space to be accessed using MOV instructions in a linear fashion for pre-modified and post-modified Effective Addresses (EA). The upper half of the base Data Space address is used in conjunction with the Data Space Page registers, the 10-bit Read Page register (DSRPAG) or the 9-bit Write Page register (DSWPAG), to form an Extended Data Space (EDS) address or Program Space Visibility (PSV) address. The Data Space Page registers are located in the SFR space.

Construction of the EDS address is shown in Example 4-1. When DSRPAG<9> = 0 and the base address bit, EA<15> = 1, the DSRPAG<8:0> bits are concatenated onto EA<14:0> to form the 24-bit EDS read address. Similarly, when base address bit, EA<15> = 1, DSWPAG<8:0> are concatenated onto EA<14:0> to form the 24-bit EDS write address.

### 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

### 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

### TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

| R/W-0                | R/W-0                   | R/W-0                | R/W-0 | R/C-0 | R/C-0 | R-0   | R/W-0 |

|----------------------|-------------------------|----------------------|-------|-------|-------|-------|-------|

| OA                   | OB                      | SA                   | SB    | OAB   | SAB   | DA    | DC    |

| bit 15               |                         |                      |       |       |       |       | bit 8 |

|                      |                         |                      |       |       |       |       |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup>    | R/W-0 <sup>(3)</sup> | R-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|                      | IPL<2:0> <sup>(2)</sup> |                      | RA    | Ν     | OV    | Z     | С     |

| bit 7                |                         |                      |       |       |       |       | bit 0 |

|                      |                         |                      |       |       |       |       |       |

# REGISTER 7-1: SR: CPU STATUS REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                       |                    |

|-------------------|-------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup>        |

|---------|----------------------------------------------------------------------------|

|         | 111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled |

|         | 110 = CPU Interrupt Priority Level is 6 (14)                               |

|         | 101 = CPU Interrupt Priority Level is 5 (13)                               |

|         | 100 = CPU Interrupt Priority Level is 4 (12)                               |

|         | 011 = CPU Interrupt Priority Level is 3 (11)                               |

|         | 010 = CPU Interrupt Priority Level is 2 (10)                               |

|         | 001 = CPU Interrupt Priority Level is 1 (9)                                |

|         | 000 = CPU Interrupt Priority Level is 0 (8)                                |

- **Note 1:** For complete register details, see Register 3-1.

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- **3:** The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

| U-0                               | U-0                                                                                                      | U-0                     | U-0            | U-0              | U-0              | U-0             | U-0   |  |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------|----------------|------------------|------------------|-----------------|-------|--|--|--|

| -                                 | —                                                                                                        | —                       | —              | —                | —                | —               | —     |  |  |  |

| bit 15                            |                                                                                                          |                         |                |                  |                  |                 |       |  |  |  |

| U-0                               | U-0                                                                                                      | U-0                     | U-0            | R-1              | R-1              | R-1             | R-1   |  |  |  |

| _                                 | _                                                                                                        | _                       | _              | LSTCH<3:0>       |                  |                 |       |  |  |  |

| bit 7                             |                                                                                                          |                         |                |                  |                  |                 | bit 0 |  |  |  |

| Legend:                           |                                                                                                          |                         |                |                  |                  |                 |       |  |  |  |

| R = Readable bit W = Writable bit |                                                                                                          |                         | bit            | U = Unimpler     | mented bit, read | 1 as '0'        |       |  |  |  |

| -n = Value a                      | -n = Value at POR '1' = Bit is                                                                           |                         |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |

|                                   |                                                                                                          |                         |                |                  |                  |                 |       |  |  |  |

| bit 15-4                          | Unimplemen                                                                                               | ted: Read as '          | 0'             |                  |                  |                 |       |  |  |  |

| bit 3-0                           | LSTCH<3:0>                                                                                               | : Last DMAC C           | hannel Active  | e Status bits    |                  |                 |       |  |  |  |

|                                   | 1111 = No DI<br>1110 = Rese                                                                              | MA transfer has<br>rved | s occurred sir | nce system Res   | set              |                 |       |  |  |  |

|                                   | •                                                                                                        |                         |                |                  |                  |                 |       |  |  |  |

|                                   | •                                                                                                        |                         |                |                  |                  |                 |       |  |  |  |

|                                   | •                                                                                                        |                         |                |                  |                  |                 |       |  |  |  |

|                                   |                                                                                                          | data transfer wa        |                |                  |                  |                 |       |  |  |  |

|                                   | 0010 = Last data transfer was handled by Channel 2<br>0001 = Last data transfer was handled by Channel 1 |                         |                |                  |                  |                 |       |  |  |  |

# REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

0000 = Last data transfer was handled by Channel 0 0000 = Last data transfer was handled by Channel 0

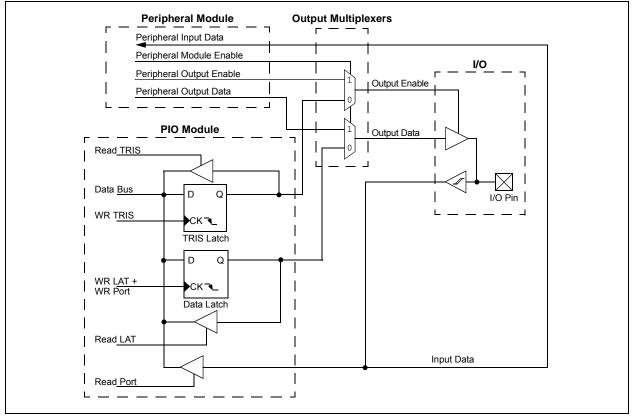

# 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70598) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Many of the device pins are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

# 11.1 Parallel I/O (PIO) Ports

Generally, a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Latch register (LATx) read the latch. Writes to the Latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device is disabled. This means the corresponding LATx and TRISx registers and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

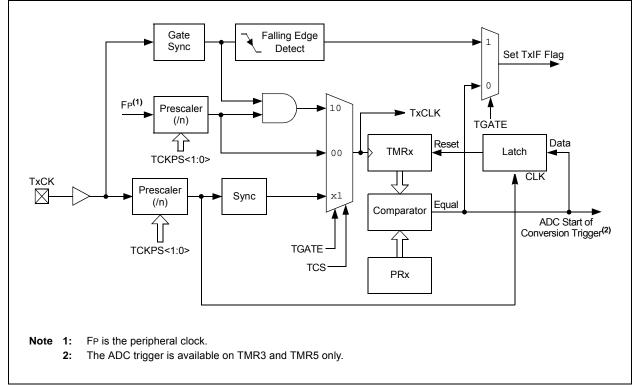

### FIGURE 13-2: TYPE C TIMER BLOCK DIAGRAM (x = 3 AND 5)

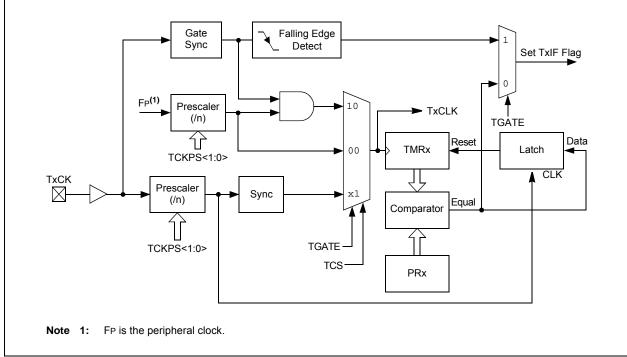

# FIGURE 13-1:TYPE B TIMER BLOCK DIAGRAM (x = 2 AND 4)

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                                   | R/W-0 | R/W-0            | R/W-0                                 | R/W-0                                                            | R/W-0                                                                                                  | R/W-0                                                                                                    |  |  |

|-----------------------------------|-------|------------------|---------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|

|                                   |       | QEIG             | EC<31:24>                             |                                                                  |                                                                                                        |                                                                                                          |  |  |

|                                   |       |                  |                                       |                                                                  |                                                                                                        | bit 8                                                                                                    |  |  |

|                                   | DAMO  |                  |                                       |                                                                  | DAMO                                                                                                   |                                                                                                          |  |  |

| R/W-U                             | R/W-0 |                  |                                       | R/W-U                                                            | R/W-U                                                                                                  | R/W-0                                                                                                    |  |  |

|                                   |       | QEIGE            | EC<23:16>                             |                                                                  |                                                                                                        |                                                                                                          |  |  |

|                                   |       |                  |                                       |                                                                  |                                                                                                        | bit (                                                                                                    |  |  |

|                                   |       |                  |                                       |                                                                  |                                                                                                        |                                                                                                          |  |  |

| R = Readable bit W = Writable bit |       |                  | U = Unimplemented bit, read as '0'    |                                                                  |                                                                                                        |                                                                                                          |  |  |

| -n = Value at POR                 |       | '1' = Bit is set |                                       | ared                                                             | x = Bit is unknown                                                                                     |                                                                                                          |  |  |

|                                   |       | W = Writable bi  | R/W-0 R/W-0 QEIGI<br>W = Writable bit | R/W-0 R/W-0 R/W-0 QEIGEC<23:16><br>W = Writable bit U = Unimplem | R/W-0     R/W-0     R/W-0       QEIGEC<23:16>       W = Writable bit       U = Unimplemented bit, real | R/W-0       R/W-0       R/W-0       R/W-0         QEIGEC<23:16>       U = Unimplemented bit, read as '0' |  |  |

### REGISTER 17-15: QEI1GECH: QEI1 GREATER THAN OR EQUAL COMPARE HIGH WORD REGISTER

bit 15-0 QEIGEC<31:16>: High Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

### REGISTER 17-16: QEI1GECL: QEI1 GREATER THAN OR EQUAL COMPARE LOW WORD REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|------------------------------------|---------|-------|-------|-------|

|                                    |       |       | QEIGE                              | C<15:8> |       |       |       |

| bit 15                             |       |       |                                    |         |       |       | bit 8 |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |       | QEIG                               | EC<7:0> |       |       |       |

| bit 7                              |       |       |                                    |         |       |       | bit 0 |

| Legend:                            |       |       |                                    |         |       |       |       |

| R = Readable bit W = Writable bit  |       |       | U = Unimplemented bit, read as '0' |         |       |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit i     |         |       | nown  |       |

bit 15-0 QEIGEC<15:0>: Low Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                                                              | U-0                                                                                      | U-0                                                                                                                | R/W-0                       | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |  |  |  |  |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------|--------------------------|-----------------------|-----------------------|--|--|--|--|

| CH0NB                                                              | _                                                                                        | —                                                                                                                  | CH0SB4 <sup>(1)</sup>       | CH0SB3 <sup>(1)</sup> | CH0SB2 <sup>(1)</sup>    | CH0SB1 <sup>(1)</sup> | CH0SB0 <sup>(1)</sup> |  |  |  |  |

| bit 15                                                             | •                                                                                        |                                                                                                                    |                             | •                     |                          |                       | bit 8                 |  |  |  |  |

|                                                                    |                                                                                          |                                                                                                                    |                             |                       |                          |                       |                       |  |  |  |  |

| R/W-0                                                              | U-0                                                                                      | U-0                                                                                                                | R/W-0                       | R/W-0                 | R/W-0                    | R/W-0                 | R/W-0                 |  |  |  |  |

| CH0NA                                                              |                                                                                          |                                                                                                                    | CH0SA4 <sup>(1)</sup>       | CH0SA3 <sup>(1)</sup> | CH0SA2 <sup>(1)</sup>    | CH0SA1 <sup>(1)</sup> | CH0SA0 <sup>(1)</sup> |  |  |  |  |

| bit 7                                                              |                                                                                          |                                                                                                                    |                             |                       |                          |                       | bit (                 |  |  |  |  |

|                                                                    |                                                                                          |                                                                                                                    |                             |                       |                          |                       |                       |  |  |  |  |

| Legend:                                                            |                                                                                          |                                                                                                                    |                             |                       |                          |                       |                       |  |  |  |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |                                                                                          |                                                                                                                    |                             |                       |                          |                       |                       |  |  |  |  |

| -n = Value                                                         | e at POR                                                                                 | '1' = Bit is set                                                                                                   |                             | '0' = Bit is cle      | ared                     | x = Bit is unkr       | iown                  |  |  |  |  |

| bit 15                                                             |                                                                                          | nannel 0 Negative                                                                                                  | Input Soloot fo             | r Samala MUV          | 'D hit                   |                       |                       |  |  |  |  |

| DIL 15                                                             |                                                                                          | el 0 negative input                                                                                                |                             |                       |                          |                       |                       |  |  |  |  |

|                                                                    |                                                                                          | el 0 negative input                                                                                                |                             |                       |                          |                       |                       |  |  |  |  |

| bit 14-13                                                          | Unimplem                                                                                 | ented: Read as 'o                                                                                                  | )'                          |                       |                          |                       |                       |  |  |  |  |

| bit 12-8                                                           | CH0SB<4:                                                                                 | 0>: Channel 0 Po                                                                                                   | sitive Input Sele           | ect for Sample        | MUXB bits <sup>(1)</sup> |                       |                       |  |  |  |  |

|                                                                    |                                                                                          | pen; use this sele                                                                                                 |                             |                       |                          | ement                 |                       |  |  |  |  |

|                                                                    | 11110 <b>= C</b>                                                                         | nannel 0 positive in                                                                                               | put is connected            | to the CTMU te        | emperature mea           | surement diode        | (CTMU TEMF            |  |  |  |  |

|                                                                    |                                                                                          | 11101 = Reserved<br>11100 = Reserved                                                                               |                             |                       |                          |                       |                       |  |  |  |  |

|                                                                    |                                                                                          | 11100 = Reserved<br>11011 = Reserved                                                                               |                             |                       |                          |                       |                       |  |  |  |  |

|                                                                    |                                                                                          | 11011 – Reserved<br>11010 = Channel 0 positive input is the output of OA3/AN6 <sup>(2,3)</sup>                     |                             |                       |                          |                       |                       |  |  |  |  |

|                                                                    |                                                                                          | 11001 = Channel 0 positive input is the output of OA2/AN0 <sup>(2)</sup>                                           |                             |                       |                          |                       |                       |  |  |  |  |

|                                                                    | 11000 <b>= C</b>                                                                         | hannel 0 positive                                                                                                  | input is the outp           | out of OA1/AN3        | <sub>3</sub> (2)         |                       |                       |  |  |  |  |

|                                                                    | 10111 <b>= R</b>                                                                         | eserved                                                                                                            |                             |                       |                          |                       |                       |  |  |  |  |

|                                                                    | •                                                                                        |                                                                                                                    |                             |                       |                          |                       |                       |  |  |  |  |

|                                                                    | •                                                                                        |                                                                                                                    |                             |                       |                          |                       |                       |  |  |  |  |

|                                                                    | 10000 <b>= R</b>                                                                         | eserved                                                                                                            |                             |                       |                          |                       |                       |  |  |  |  |

|                                                                    | 01111 <b>= C</b>                                                                         | 01111 = Channel 0 positive input is AN15 <sup>(3)</sup>                                                            |                             |                       |                          |                       |                       |  |  |  |  |

|                                                                    | 01110 = C                                                                                | 01110 = Channel 0 positive input is AN14 <sup>(3)</sup><br>01101 = Channel 0 positive input is AN13 <sup>(3)</sup> |                             |                       |                          |                       |                       |  |  |  |  |

|                                                                    | 01101 = C                                                                                | nannel 0 positive                                                                                                  | Input is AN130              |                       |                          |                       |                       |  |  |  |  |

|                                                                    | •                                                                                        |                                                                                                                    |                             |                       |                          |                       |                       |  |  |  |  |

|                                                                    | •                                                                                        |                                                                                                                    |                             |                       |                          |                       |                       |  |  |  |  |

|                                                                    | 00010 <b>= C</b>                                                                         | hannel 0 positive                                                                                                  | input is AN2 <sup>(3)</sup> |                       |                          |                       |                       |  |  |  |  |

|                                                                    |                                                                                          | 00001 = Channel 0 positive input is AN1 <sup>(3)</sup><br>00000 = Channel 0 positive input is AN0 <sup>(3)</sup>   |                             |                       |                          |                       |                       |  |  |  |  |

| L:1 7                                                              |                                                                                          | •                                                                                                                  | •                           |                       | A 64                     |                       |                       |  |  |  |  |

| bit 7                                                              |                                                                                          | nannel 0 Negative                                                                                                  | ·                           | r Sample MUX          | ADI                      |                       |                       |  |  |  |  |

|                                                                    |                                                                                          | el 0 negative input                                                                                                |                             |                       |                          |                       |                       |  |  |  |  |

| bit 6-5                                                            |                                                                                          | ented: Read as '                                                                                                   |                             |                       |                          |                       |                       |  |  |  |  |

| Note 1:                                                            | to determine I                                                                           | AN7 are repurpos<br>now enabling a pa                                                                              |                             |                       |                          |                       |                       |  |  |  |  |

| -                                                                  | and 3.                                                                                   |                                                                                                                    |                             |                       |                          |                       | - >                   |  |  |  |  |

| 2:                                                                 | The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); |                                                                                                                    |                             |                       |                          |                       |                       |  |  |  |  |

### REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER

3: See the "**Pin Diagrams**" section for the available analog channels for each device.

otherwise, the ANx input is used.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0      | R/W-0                                 | R/W-0                                                                                                                                       | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |  |  |  |  |  |

|------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------------------|-----------------|--------|--|--|--|--|--|

| ADCTS4     | ADCTS3                                | ADCTS2                                                                                                                                      | ADCTS1         | IC4TSS           | IC3TSS                       | IC2TSS          | IC1TSS |  |  |  |  |  |

| bit 15     |                                       |                                                                                                                                             |                |                  |                              |                 | bit 8  |  |  |  |  |  |

| R/W-0      | R/W-0                                 | R/W-0                                                                                                                                       | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |  |  |  |  |  |

| OC4CS      |                                       | OC2CS                                                                                                                                       | OC1CS          | OC4TSS           | OC3TSS                       | OC2TSS          | OC1TSS |  |  |  |  |  |

| bit 7      |                                       | 00100                                                                                                                                       |                |                  |                              |                 | bit (  |  |  |  |  |  |

| Legend:    |                                       |                                                                                                                                             |                |                  |                              |                 |        |  |  |  |  |  |

| R = Reada  | ble bit                               | W = Writable                                                                                                                                | bit            | U = Unimplei     | mented bit, read             | l as '0'        |        |  |  |  |  |  |

| -n = Value | at POR                                | '1' = Bit is set                                                                                                                            |                | '0' = Bit is cle |                              | x = Bit is unkr | nown   |  |  |  |  |  |

|            |                                       |                                                                                                                                             |                |                  |                              |                 |        |  |  |  |  |  |

| bit 15     | ADCTS4: Sa                            | mple Trigger P                                                                                                                              | TGO15 for AE   | OC bit           |                              |                 |        |  |  |  |  |  |

|            | 1 = Generate                          | es Trigger wher                                                                                                                             | the broadcas   | t command is     | executed                     |                 |        |  |  |  |  |  |

|            | 0 = Does not                          | generate Trigg                                                                                                                              | er when the b  | roadcast com     | mand is execute              | ed              |        |  |  |  |  |  |

| bit 14     |                                       | mple Trigger P                                                                                                                              |                |                  |                              |                 |        |  |  |  |  |  |

|            |                                       | 1 = Generates Trigger when the broadcast command is executed                                                                                |                |                  |                              |                 |        |  |  |  |  |  |

| bit 13     |                                       | <ul> <li>0 = Does not generate Trigger when the broadcast command is executed</li> <li>ADCTS2: Sample Trigger PTGO13 for ADC bit</li> </ul> |                |                  |                              |                 |        |  |  |  |  |  |

| DIE 13     |                                       | es Trigger wher                                                                                                                             |                |                  | evecuted                     |                 |        |  |  |  |  |  |

|            |                                       |                                                                                                                                             |                |                  | mand is execute              | ed              |        |  |  |  |  |  |

| bit 12     |                                       | mple Trigger P                                                                                                                              |                |                  |                              |                 |        |  |  |  |  |  |

|            | 1 = Generate                          | es Trigger wher                                                                                                                             | the broadcas   | t command is     | executed                     |                 |        |  |  |  |  |  |

|            |                                       | 0 = Does not generate Trigger when the broadcast command is executed                                                                        |                |                  |                              |                 |        |  |  |  |  |  |

| bit 11     | -                                     | ger/Synchroniz                                                                                                                              |                |                  |                              |                 |        |  |  |  |  |  |

|            |                                       |                                                                                                                                             |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |  |

| bit 10     | IC3TSS: Trig                          | ger/Synchroniz                                                                                                                              | ation Source f | for IC3 bit      |                              |                 |        |  |  |  |  |  |

|            |                                       |                                                                                                                                             |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |  |

| bit 9      | IC2TSS: Trig                          | ger/Synchroniz                                                                                                                              | ation Source f | for IC2 bit      |                              |                 |        |  |  |  |  |  |

|            |                                       |                                                                                                                                             |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |  |

| bit 8      |                                       | ger/Synchroniz                                                                                                                              |                |                  |                              |                 |        |  |  |  |  |  |

|            |                                       |                                                                                                                                             |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |  |

| bit 7      |                                       | = Does not generate Trigger/Synchronization when the broadcast command is executed<br>DC4CS: Clock Source for OC4 bit                       |                |                  |                              |                 |        |  |  |  |  |  |

|            |                                       | es clock pulse v<br>generate clock                                                                                                          |                |                  | d is executed command is exe | cuted           |        |  |  |  |  |  |

| bit 6      |                                       | ck Source for C                                                                                                                             | -              |                  |                              |                 |        |  |  |  |  |  |

|            |                                       | es clock pulse v<br>aenerate clock                                                                                                          |                |                  | d is executed command is exe | cuted           |        |  |  |  |  |  |

| bit 5      |                                       | ck Source for C                                                                                                                             | -              |                  |                              |                 |        |  |  |  |  |  |

|            | 1 = Generate                          | es clock pulse v                                                                                                                            | when the broad |                  | d is executed command is exe | cuted           |        |  |  |  |  |  |

|            | This register is rea<br>PTGSTRT = 1). | -                                                                                                                                           |                |                  |                              |                 | and    |  |  |  |  |  |

|            | This register is on                   | lv used with the                                                                                                                            | PTGCTRI. OI    | PTION = 1111     | Step command                 | L               |        |  |  |  |  |  |

|            |                                       | .,                                                                                                                                          |                |                  | c.op commune                 | •               |        |  |  |  |  |  |

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup>

## 29.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 29.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 29.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 29.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 29.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

#### TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                                                  | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |            |                    |

|--------------------|--------|------------------------------------------------------------------|-------------------------------------------------------|-----|-----|------------|--------------------|

| Param<br>No.       | Symbol | Characteristic                                                   | Min. Typ. <sup>(1)</sup> Max. Units Condition         |     |     | Conditions |                    |

| OS50               | Fplli  | PLL Voltage Controlled Oscillator<br>(VCO) Input Frequency Range | 0.8                                                   | _   | 8.0 | MHz        | ECPLL, XTPLL modes |

| OS51               | Fvco   | On-Chip VCO System Frequency                                     | 120                                                   | —   | 340 | MHz        |                    |

| OS52               | TLOCK  | PLL Start-up Time (Lock Time)                                    | 0.9                                                   | 1.5 | 3.1 | ms         |                    |

| OS53               | DCLK   | CLKO Stability (Jitter) <sup>(2)</sup>                           | -3                                                    | 0.5 | 3   | %          |                    |

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: This jitter specification is based on clock cycle-by-clock cycle measurements. To get the effective jitter for individual time bases, or communication clocks used by the application, use the following formula:

$$Effective Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Time Base or Communication Clock}}}$$

For example, if Fosc = 120 MHz and the SPIx bit rate = 10 MHz, the effective jitter is as follows:

Effective Jitter =

$$\frac{DCLK}{\sqrt{\frac{120}{10}}} = \frac{DCLK}{\sqrt{12}} = \frac{DCLK}{3.464}$$

### TABLE 30-19: INTERNAL FRC ACCURACY

| AC CHA       | RACTERISTICS           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq T A \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq T A \leq +125^\circ C \mbox{ for Extended} \end{array}$ |            |             |       |                                         |                |  |

|--------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|-------|-----------------------------------------|----------------|--|