Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

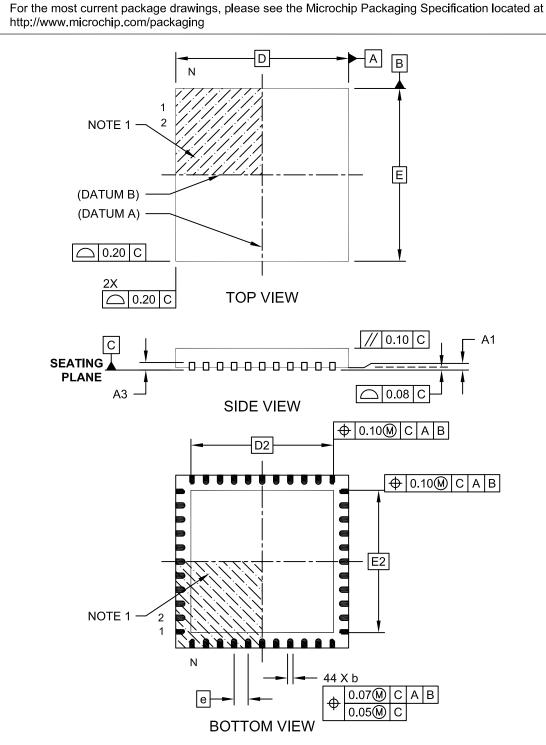

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gp504-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

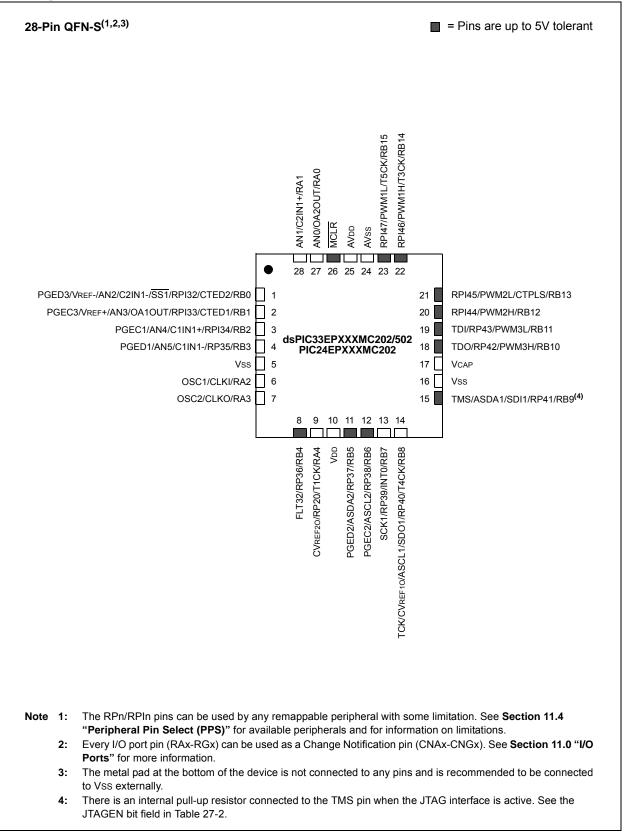

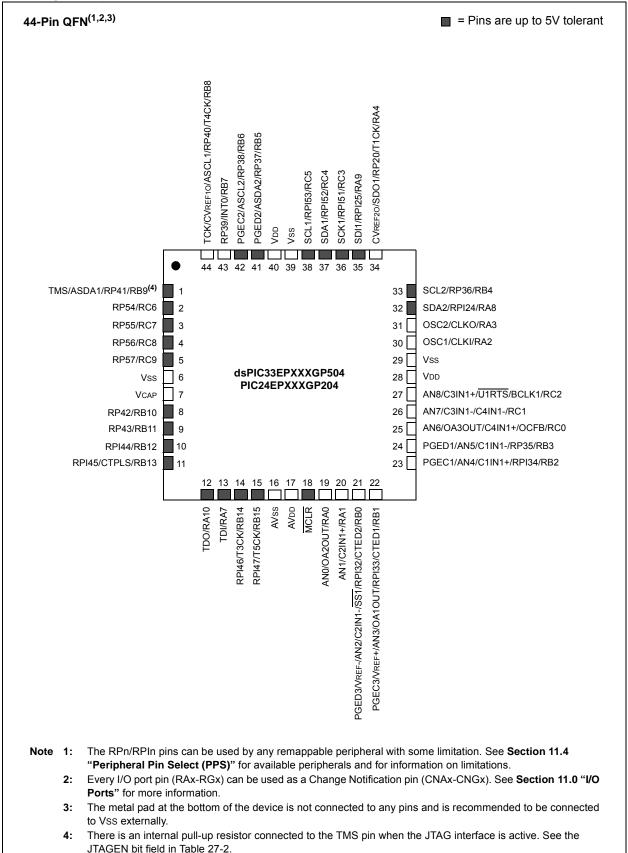

## Pin Diagrams (Continued)

## **Pin Diagrams (Continued)**

| TABLE 1-1: PINC                           |             | O DESC         | RIPT | IONS (CONTINUED)                                                                 |

|-------------------------------------------|-------------|----------------|------|----------------------------------------------------------------------------------|

| Pin Name <sup>(4)</sup>                   | Pin<br>Type | Buffer<br>Type | PPS  | Description                                                                      |

| U2CTS                                     | Ι           | ST             | No   | UART2 Clear-To-Send.                                                             |

| U2RTS                                     | 0           | —              | No   | UART2 Ready-To-Send.                                                             |

| U2RX                                      | Ι           | ST             | Yes  | UART2 receive.                                                                   |

| U2TX                                      | 0           | —              | Yes  | UART2 transmit.                                                                  |

| BCLK2                                     | 0           | ST             | No   | UART2 IrDA <sup>®</sup> baud clock output.                                       |

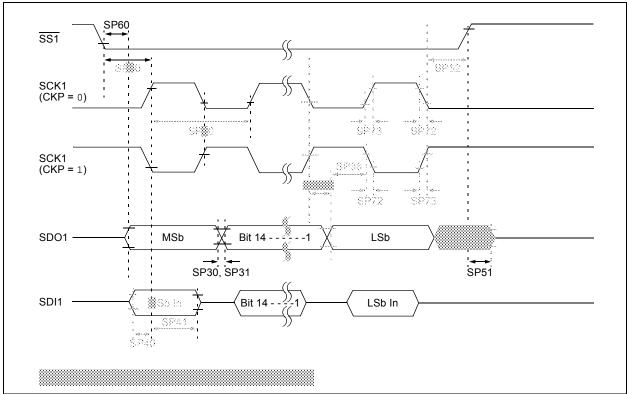

| SCK1                                      | I/O         | ST             | No   | Synchronous serial clock input/output for SPI1.                                  |

| SDI1                                      | I           | ST             | No   | SPI1 data in.                                                                    |

| SDO1                                      | 0           | —              | No   | SPI1 data out.                                                                   |

| SS1                                       | I/O         | ST             | No   | SPI1 slave synchronization or frame pulse I/O.                                   |

| SCK2                                      | I/O         | ST             | Yes  | Synchronous serial clock input/output for SPI2.                                  |

| SDI2                                      | I           | ST             | Yes  | SPI2 data in.                                                                    |

| SDO2                                      | 0           | _              | Yes  | SPI2 data out.                                                                   |

| SS2                                       | I/O         | ST             | Yes  | SPI2 slave synchronization or frame pulse I/O.                                   |

| SCL1                                      | I/O         | ST             | No   | Synchronous serial clock input/output for I2C1.                                  |

| SDA1                                      | I/O         | ST             | No   | Synchronous serial data input/output for I2C1.                                   |

| ASCL1                                     | I/O         | ST             | No   | Alternate synchronous serial clock input/output for I2C1.                        |

| ASDA1                                     | I/O         | ST             | No   | Alternate synchronous serial data input/output for I2C1.                         |

| SCL2                                      | I/O         | ST             | No   | Synchronous serial clock input/output for I2C2.                                  |

| SDA2                                      | I/O         | ST             | No   | Synchronous serial data input/output for I2C2.                                   |

| ASCL2                                     | I/O         | ST             | No   | Alternate synchronous serial clock input/output for I2C2.                        |

| ASDA2                                     | I/O         | ST             | No   | Alternate synchronous serial data input/output for I2C2.                         |

| TMS <sup>(5)</sup>                        | Ι           | ST             | No   | JTAG Test mode select pin.                                                       |

| TCK                                       | Ι           | ST             | No   | JTAG test clock input pin.                                                       |

| TDI                                       | I           | ST             | No   | JTAG test data input pin.                                                        |

| TDO                                       | 0           | _              | No   | JTAG test data output pin.                                                       |

| C1RX <sup>(2)</sup>                       | Ι           | ST             | Yes  | ECAN1 bus receive pin.                                                           |

| C1TX <sup>(2)</sup>                       | 0           | _              | Yes  | ECAN1 bus transmit pin.                                                          |

| FLT1 <sup>(1)</sup> , FLT2 <sup>(1)</sup> | Ι           | ST             | Yes  | PWM Fault Inputs 1 and 2.                                                        |

| FLT3 <sup>(1)</sup> , FLT4 <sup>(1)</sup> | Ι           | ST             | No   | PWM Fault Inputs 3 and 4.                                                        |

| FLT32 <sup>(1,3)</sup>                    | Ι           | ST             | No   | PWM Fault Input 32 (Class B Fault).                                              |

| DTCMP1-DTCMP3 <sup>(1)</sup>              | Ι           | ST             | Yes  | PWM Dead-Time Compensation Inputs 1 through 3.                                   |

| PWM1L-PWM3L <sup>(1)</sup>                | 0           | —              | No   | PWM Low Outputs 1 through 3.                                                     |

| PWM1H-PWM3H <sup>(1)</sup>                | 0           | —              | No   | PWM High Outputs 1 through 3.                                                    |

| SYNCI1 <sup>(1)</sup>                     | Ι           | ST             |      | PWM Synchronization Input 1.                                                     |

| SYNCO1 <sup>(1)</sup>                     | 0           |                | Yes  | PWM Synchronization Output 1.                                                    |

| INDX1 <sup>(1)</sup>                      | Ι           | ST             | Yes  | Quadrature Encoder Index1 pulse input.                                           |

| HOME1 <sup>(1)</sup>                      | Ι           | ST             | Yes  | Quadrature Encoder Home1 pulse input.                                            |

| QEA1 <sup>(1)</sup>                       | Ι           | ST             | Yes  | Quadrature Encoder Phase A input in QEI1 mode. Auxiliary timer                   |

| QEB1 <sup>(1)</sup>                       | ,           | ст             | Vee  | external clock/gate input in Timer mode.                                         |

|                                           | Ι           | ST             | Yes  | Quadrature Encoder Phase B input in QEI1 mode. Auxiliary timer                   |

| CNTCMP1 <sup>(1)</sup>                    | 0           |                | Yes  | external clock/gate input in Timer mode.<br>Quadrature Encoder Compare Output 1. |

|                                           | 0           | <br>ompatible  | 162  |                                                                                  |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Legend:

CMOS = CMOS compatible input or output

Analog = Analog input

ST = Schmitt Trigger input with CMOS levels

O = Output

PPS = Peripheral Pin Select

TTL = TTL input buffer

P = Power I = Input

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

5: There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

## 4.2 Data Address Space

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a separate 16-bit-wide data memory space. The Data Space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory maps, which are presented by device family and memory size, are shown in Figure 4-7 through Figure 4-16.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the Data Space. This arrangement gives a base Data Space address range of 64 Kbytes (32K words).

The base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space, which has a total address range of 16 Mbytes.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices implement up to 52 Kbytes of data memory (4 Kbytes of data memory for Special Function Registers and up to 48 Kbytes of data memory for RAM). If an EA points to a location outside of this area, an all-zero word or byte is returned.

## 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byteaddressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all Data Space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

## 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve Data Space memory usage efficiency, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X instruction set supports both word and byte operations. As a consequence of byte accessibility, all Effective Address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] results in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

A data byte read, reads the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed. If the error occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A Sign-Extend (SE) instruction is provided to allow user applications to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a Zero-Extend (ZE) instruction on the appropriate address.

## 4.2.3 SFR SPACE

The first 4 Kbytes of the Near Data Space, from 0x0000 to 0x0FFF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'.

**Note:** The actual set of peripheral features and interrupts varies by the device. Refer to the corresponding device tables and pinout diagrams for device-specific information.

## 4.2.4 NEAR DATA SPACE

The 8-Kbyte area, between 0x0000 and 0x1FFF, is referred to as the Near Data Space. Locations in this space are directly addressable through a 13-bit absolute address field within all memory direct instructions. Additionally, the whole Data Space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

| TABLE 4   | 4-9:  | INPUT                           |        | JRE 1 T | HROUG  | H INPU    | Т САРТ | URE 4 | REGIST       | ER MA        | Р        |       |              |       |          |          |       |               |

|-----------|-------|---------------------------------|--------|---------|--------|-----------|--------|-------|--------------|--------------|----------|-------|--------------|-------|----------|----------|-------|---------------|

| File Name | Addr. | Bit 15                          | Bit 14 | Bit 13  | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6    | Bit 5 | Bit 4        | Bit 3 | Bit 2    | Bit 1    | Bit 0 | All<br>Resets |

| IC1CON1   | 0140  | _                               | —      | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | -            | —            | ICI<     | :0>   | ICOV         | ICBNE |          | ICM<2:0> |       | 0000          |

| IC1CON2   | 0142  | _                               | _      |         | _      |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |              | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC1BUF    | 0144  |                                 |        |         |        |           |        | Inp   | ut Capture ' | 1 Buffer Reg | gister   |       |              |       |          |          |       | xxxx          |

| IC1TMR    | 0146  |                                 |        |         |        |           |        |       | Input Capt   | ture 1 Time  | r        |       |              |       |          |          |       | 0000          |

| IC2CON1   | 0148  |                                 | _      | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV         | ICBNE |          | ICM<2:0> |       | 0000          |

| IC2CON2   | 014A  |                                 | _      |         |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |              | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC2BUF    | 014C  |                                 |        |         |        |           |        | Inp   | ut Capture 2 | 2 Buffer Reg | gister   |       |              |       |          |          |       | xxxx          |

| IC2TMR    | 014E  |                                 |        |         |        |           |        |       | Input Capt   | ture 2 Time  | r        |       |              |       |          |          |       | 0000          |

| IC3CON1   | 0150  |                                 | —      | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV         | ICBNE |          | ICM<2:0> |       | 0000          |

| IC3CON2   | 0152  |                                 | —      |         |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |              | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC3BUF    | 0154  |                                 |        |         |        |           |        | Inp   | ut Capture 3 | 3 Buffer Reg | gister   |       |              |       |          |          |       | xxxx          |

| IC3TMR    | 0156  |                                 |        |         |        |           |        |       | Input Capt   | ture 3 Time  | r        |       |              |       |          |          |       | 0000          |

| IC4CON1   | 0158  |                                 | —      | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV         | ICBNE |          | ICM<2:0> |       | 0000          |

| IC4CON2   | 015A  | _                               | _      |         | -      |           | -      | _     | IC32         | ICTRIG       | TRIGSTAT | -     | SYNCSEL<4:0> |       |          |          |       | 000D          |

| IC4BUF    | 015C  | Input Capture 4 Buffer Register |        |         |        |           |        |       |              | xxxx         |          |       |              |       |          |          |       |               |

| IC4TMR    | 015E  | Input Capture 4 Timer 0         |        |         |        |           |        |       |              | 0000         |          |       |              |       |          |          |       |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4   | -12:     | PWM RI         | EGISTE      | R MAP      | FOR de      | sPIC33E      | PXXXN   | AC20X/50 | DX AND F | PIC24EP | PXXXM | C20X [ | DEVICE  | S ONI | _Y    |            |       |               |

|-----------|----------|----------------|-------------|------------|-------------|--------------|---------|----------|----------|---------|-------|--------|---------|-------|-------|------------|-------|---------------|

| File Name | Addr.    | Bit 15         | Bit 14      | Bit 13     | Bit 12      | Bit 11       | Bit 10  | Bit 9    | Bit 8    | Bit 7   | Bit 6 | Bit 5  | Bit 4   | Bit 3 | Bit 2 | Bit 1      | Bit 0 | All<br>Resets |

| PTCON     | 0C00     | PTEN           | —           | PTSIDL     | SESTAT      | SEIEN        | EIPU    | SYNCPOL  | SYNCOEN  | SYNCEN  | SY    | NCSRC< | 2:0>    |       | SEV   | /TPS<3:0>  |       | 0000          |

| PTCON2    | 0C02     | _              | —           | _          | _           | _            | —       | —        | —        | —       | _     | —      | _       | —     |       | PCLKDIV<2: | 0>    | 0000          |

| PTPER     | 0C04     |                |             |            |             |              |         |          | PTPER<15 | :0>     |       |        |         |       |       |            |       | 00F8          |

| SEVTCMP   | 0C06     |                |             |            |             |              |         |          | SEVTCMP< | 5:0>    |       |        |         |       |       |            |       | 0000          |

| MDC       | 0C0A     |                |             |            |             |              |         |          | MDC<15:  | )>      |       |        |         |       |       |            |       | 0000          |

| CHOP      | 0C1A     | CHPCLKEN       | _           | _          | _           | _            | _       |          |          |         |       | CHOPCI | _K<9:0> |       |       |            |       | 0000          |

| PWMKEY    | 0C1E     |                |             |            |             |              |         |          | PWMKEY<1 | 5:0>    |       |        |         |       |       |            |       | 0000          |

| Legend: - | – = unir | mplemented, re | ead as '0'. | Reset valu | es are show | vn in hexade | ecimal. |          |          |         |       |        |         |       |       |            |       | -             |

## TABLE 4-13: PWM GENERATOR 1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

|           | 10.   |         |        |         |          |          | I OIL U                                        |        |           |          |        | 1102-   |         |       |          |       |        |               |

|-----------|-------|---------|--------|---------|----------|----------|------------------------------------------------|--------|-----------|----------|--------|---------|---------|-------|----------|-------|--------|---------------|

| File Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12   | Bit 11   | Bit 10                                         | Bit 9  | Bit 8     | Bit 7    | Bit 6  | Bit 5   | Bit 4   | Bit 3 | Bit 2    | Bit 1 | Bit 0  | All<br>Resets |

| PWMCON1   | 0C20  | FLTSTAT | CLSTAT | TRGSTAT | FLTIEN   | CLIEN    | TRGIEN                                         | ITB    | MDCS      | DTC<     | :1:0>  | DTCP    | _       | MTBS  | CAM      | XPRES | IUE    | 0000          |

| IOCON1    | 0C22  | PENH    | PENL   | POLH    | POLL     | PMOD     | <1:0>                                          | OVRENH | OVRENL    | OVRDA    | T<1:0> | FLTDA   | T<1:0>  | CLDA  | T<1:0>   | SWAP  | OSYNC  | C000          |

| FCLCON1   | 0C24  | _       |        | (       | CLSRC<4: | 0>       |                                                | CLPOL  | CLMOD     |          | FL     | TSRC<4: | )>      |       | FLTPOL   | FLTMO | D<1:0> | 0000          |

| PDC1      | 0C26  |         |        |         |          |          | PDC1<15:0><br>PHASE1<15:0>                     |        |           |          |        |         | FFF8    |       |          |       |        |               |

| PHASE1    | 0C28  |         |        |         |          |          | PHASE1<15:0>                                   |        |           |          |        |         | 0000    |       |          |       |        |               |

| DTR1      | 0C2A  | _       | _      |         |          |          | DTR1<13:0>                                     |        |           |          |        |         | 0000    |       |          |       |        |               |

| ALTDTR1   | 0C2C  | _       | _      |         |          |          |                                                |        | А         | LTDTR1<1 | 3:0>   |         |         |       |          |       |        | 0000          |

| TRIG1     | 0C32  |         |        |         |          |          |                                                |        | TRGCMP<18 | 5:0>     |        |         |         |       |          |       |        | 0000          |

| TRGCON1   | 0C34  |         | TRGDI  | V<3:0>  |          | _        | _                                              | _      | _         | _        | _      |         |         | TRG   | STRT<5:0 | >     |        | 0000          |

| LEBCON1   | 0C3A  | PHR     | PHF    | PLR     | PLF      | FLTLEBEN | CLLEBEN                                        | _      | _         | _        | _      | BCH     | BCL     | BPHH  | BPHL     | BPLH  | BPLL   | 0000          |

| LEBDLY1   | 0C3C  | _       | _      | —       | —        |          |                                                |        |           |          | LEB<11 | :0>     |         |       |          |       |        | 0000          |

| AUXCON1   | 0C3E  | —       | —      | _       |          |          | BLANKSEL<3:0> — — CHOPSEL<3:0> CHOPHEN CHOPLEN |        |           |          |        |         | EL<3:0> |       | 0000     |       |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-27: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC204/504 AND PIC24EPXXXGP/MC204 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10     | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|------------|-------|-------|-------|-------|-------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  |        |        |        |            | RP35   | R<5:0>     |       |       | _     | —     |       |       | RP20F | ₹<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      | _      |        | RP37R<5:0> |        |            |       |       |       |       |       |       | RP36F | <5:0>  |       |       | 0000          |

| RPOR2        | 0684  | _      | _      |        |            | RP39   | R<5:0>     |       |       |       | —     |       |       | RP38F | <5:0>  |       |       | 0000          |

| RPOR3        | 0686  | _      | _      |        |            | RP41   | R<5:0>     |       |       |       | —     |       |       | RP40F | <5:0>  |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |            | RP43   | RP43R<5:0> |       |       |       | —     |       |       | RP42F | <5:0>  |       |       | 0000          |

| RPOR5        | 068A  | _      | —      |        |            | RP55   | R<5:0>     |       |       | _     | —     |       |       | RP54F | R<5:0> |       |       | 0000          |

| RPOR6        | 068C  | _      | —      |        |            | RP57   | R<5:0>     |       |       | _     | —     |       |       | RP56F | R<5:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-28: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC206/506 AND PIC24EPXXXGP/MC206 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  | _      | _      |        |        | RP35F  | R<5:0> |       |       | _     | _     |       | •     | RP20F | R<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      |        |        |        | RP37F  | R<5:0> |       |       | _     | _     |       |       | RP36  | R<5:0> |       |       | 0000          |

| RPOR2        | 0684  | _      | —      |        |        | RP39F  | २<5:0> |       |       | _     | _     |       |       | RP38  | R<5:0> |       |       | 0000          |

| RPOR3        | 0686  | _      | —      |        |        | RP41F  | २<5:0> |       |       | _     | _     |       |       | RP40  | R<5:0> |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |        | RP43F  | २<5:0> |       |       | —     | _     |       |       | RP42  | R<5:0> |       |       | 0000          |

| RPOR5        | 068A  | _      | _      |        |        | RP55F  | २<5:0> |       |       | —     | _     |       |       | RP54  | R<5:0> |       |       | 0000          |

| RPOR6        | 068C  | _      | _      |        |        | RP57F  | २<5:0> |       |       | —     | _     |       |       | RP56  | R<5:0> |       |       | 0000          |

| RPOR7        | 068E  | _      | _      |        |        | RP97F  | २<5:0> |       |       | —     | _     | _     | _     | _     | _      | _     | _     | 0000          |

| RPOR8        | 0690  |        | _      |        |        | RP118  | R<5:0> |       |       | _     | _     | —     | _     | —     | _      | —     | _     | 0000          |

| RPOR9        | 0692  | —      | _      | _      | _      | _      | _      | _     | _     | _     | _     |       |       | RP120 | R<5:0> |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer is complete)

- DMA request for each channel can be selected from any supported interrupt source

- Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|-------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0   | 00000000                             | _                                                       | _                                                      |

| IC1 – Input Capture 1         | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2         | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3         | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4         | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1        | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2        | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3        | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4        | 00011010                             | —                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                 | 00000111                             | _                                                       | _                                                      |

| TMR3 – Timer3                 | 00001000                             | —                                                       | _                                                      |

| TMR4 – Timer4                 | 00011011                             | —                                                       | _                                                      |

| TMR5 – Timer5                 | 00011100                             | —                                                       | —                                                      |

| SPI1 Transfer Done            | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |

| SPI2 Transfer Done            | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |

| UART1RX – UART1 Receiver      | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter   | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver      | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter   | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |

| ECAN1 – RX Data Ready         | 00100010                             | 0x0440 (C1RXD)                                          | _                                                      |

| ECAN1 – TX Data Request       | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |

| ADC1 – ADC1 Convert Done      | 00001101                             | 0x0300 (ADC1BUF0)                                       | —                                                      |

#### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

## **REGISTER 8-7:** DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | PAD   | <15:8>            |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | PAE   | )<7:0>            |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

#### bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

## REGISTER 8-8: DMAXCNT: DMA CHANNEL X TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0             | U-0   | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

| —               |       |                  |       | CNT<              | 13:8> <b>(2)</b> |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | CNT<  | <7:0> <b>(2)</b>  |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable b  | oit   | W = Writable b   | bit   | U = Unimplen      | nented bit, rea  | id as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC2R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| ·                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 8                                                                                                                                                                                                                                                                                                                                                                                               |

| R/W-0                        | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                               |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | IC1R<6:0>                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit C                                                                                                                                                                                                                                                                                                                                                                                               |

|                              |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

| e bit                        | W = Writable b                                                                                                                                                         | it                                                                                                                                                                                                                                                                                                                                       | U = Unimplem                                                                                                                                                                                             | nented bit, rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | d as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                     |

| POR                          | '1' = Bit is set                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                          | '0' = Bit is clea                                                                                                                                                                                        | ared                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | x = Bit is unkr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | nown                                                                                                                                                                                                                                                                                                                                                                                                |

| •                            |                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                          | nbers)                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                              |                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |