Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

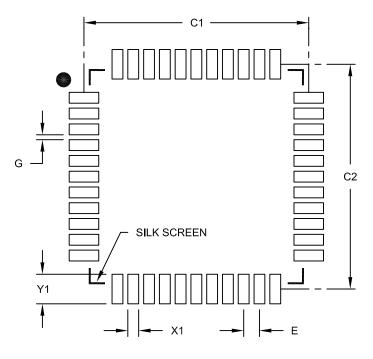

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8×8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gp504t-e-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

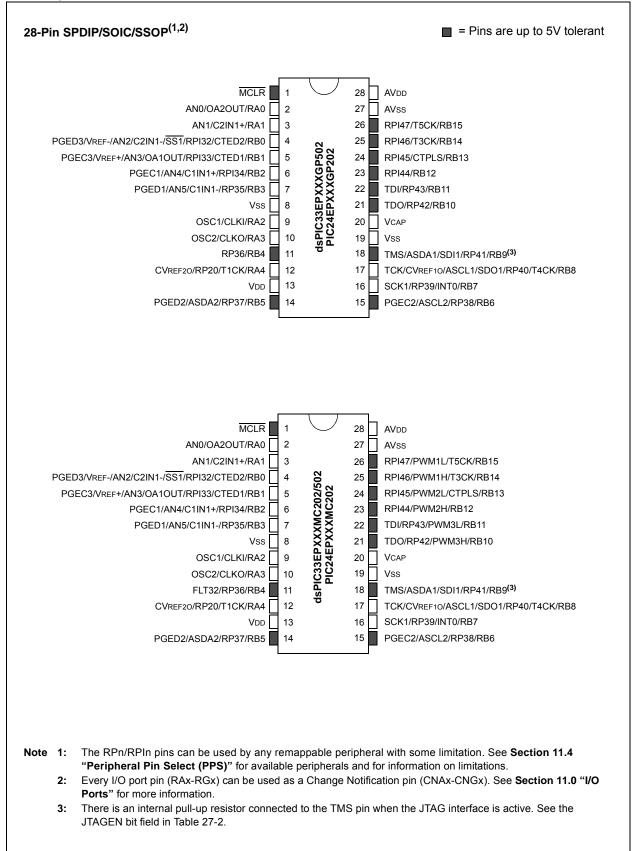

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### **Pin Diagrams**

| TABLE 4 | 4-31: | PER | IPHERA | L PIN S | ELECT | INPUT F | REGISTI | ER MAP | FOR de | sPIC33E | EPXXXG | P50X D | EVICES | SONLY |  |

|---------|-------|-----|--------|---------|-------|---------|---------|--------|--------|---------|--------|--------|--------|-------|--|

|         |       |     |        |         |       |         |         |        |        |         |        |        |        |       |  |

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|------------|--------|-------|-------|-------|-------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | —      |        |        |        | INT1R<6:0> |        |       |       | _     | _     | —     | —     | —          | —     | —     | _     | 0000          |

| RPINR1       | 06A2  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       |       | INT2R<6:0> | •     |       |       | 0000          |

| RPINR3       | 06A6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ٦     | [2CKR<6:0  | >     |       |       | 0000          |

| RPINR7       | 06AE  |        |        |        |        | IC2R<6:0>  |        |       |       | _     |       |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  |        |        |        |        | IC4R<6:0>  |        |       |       | _     |       |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR18      | 06C4  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ι     | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19      | 06C6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22      | 06CC  |        |        |        | S      | CK2INR<6:0 | )>     |       |       | _     |       |       | :     | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23      | 06CE  | _      | _      | _      | —      | —          | _      | _     | —     | —     |       |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26      | 06D4  | —      | _      | _      | -      | _          | _      | —     |       | —     |       |       | (     | C1RXR<6:0  | >     |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-32:** PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|------------|--------|-------|-------|-------|-------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0    | 06A0  | _      |        |        |        | INT1R<6:0> |        |       |       | —     | —     | —     | —     | —          | —     | —     | _     | 0000          |

| RPINR1    | 06A2  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       |       | INT2R<6:0> |       |       |       | 0000          |

| RPINR3    | 06A6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | -     | F2CKR<6:0  | >     |       |       | 0000          |

| RPINR7    | 06AE  |        |        |        |        | IC2R<6:0>  |        |       |       | _     |       |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8    | 06B0  |        |        |        |        | IC4R<6:0>  |        |       |       | _     |       |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11   | 06B6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR12   | 06B8  |        |        |        |        | FLT2R<6:0> | •      |       |       | _     |       |       |       | FLT1R<6:0> | •     |       |       | 0000          |

| RPINR14   | 06BC  |        |        |        | (      | QEB1R<6:0  | >      |       |       | _     |       |       | (     | QEA1R<6:0  | >     |       |       | 0000          |

| RPINR15   | 06BE  |        |        |        | Н      | OME1R<6:0  | )>     |       |       | _     |       |       | I     | NDX1R<6:0  | >     |       |       | 0000          |

| RPINR18   | 06C4  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ι     | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19   | 06C6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22   | 06CC  | _      |        |        | S      | CK2INR<6:( | )>     |       |       | —     |       |       |       | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23   | 06CE  | _      | —      | —      |        | —          | —      |       | —     | —     |       |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26   | 06D4  | _      | _      | _      |        | —          | —      |       | —     | —     |       |       | (     | C1RXR<6:0  | >     |       |       | 0000          |

| RPINR37   | 06EA  | _      |        |        | S      | YNCI1R<6:0 | )>     |       |       | —     | —     | —     | —     | —          |       |       |       | 0000          |

| RPINR38   | 06EC  | _      |        |        | D      | CMP1R<6:   | 0>     |       |       | —     | —     | —     | —     | _          |       |       |       | 0000          |

| RPINR39   | 06EE  | _      |        |        | D      | FCMP3R<6:  | 0>     |       |       | _     |       |       | D     | CMP2R<6:   | 0>    |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### TABLE 4-34: NVM REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3    | Bit 2   | Bit 1   | Bit 0 | All<br>Resets |  |  |  |  |

|-----------|-------|--------|--------|--------|---------|--------|--------|-------|-------|----------|-------|-------|--------|----------|---------|---------|-------|---------------|--|--|--|--|

| NVMCON    | 0728  | WR     | WREN   | WRERR  | NVMSIDL | _      | _      | —     | _     | _        | _     | _     | —      |          | NVMC    | )P<3:0> |       | 0000          |  |  |  |  |

| NVMADRL   | 072A  |        |        |        |         |        |        |       | NVMAD | )R<15:0> |       |       |        |          |         |         | 0000  |               |  |  |  |  |

| NVMADRH   | 072C  | _      | _      | _      | _       | -      | _      | _     | _     |          |       |       | NVMADF | R<23:16> | <23:16> |         |       |               |  |  |  |  |

| NVMKEY    | 072E  |        |        | _      | —       | _      |        | —     | -     |          |       |       | NVMKE  |          | 0000    |         |       |               |  |  |  |  |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-35: SYSTEM CONTROL REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10      | Bit 9     | Bit 8    | Bit 7   | Bit 6  | Bit 5  | Bit 4   | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|-----------|--------|--------|-------------|-----------|----------|---------|--------|--------|---------|-------|--------|-------|-------|---------------|

| RCON      | 0740  | TRAPR  | IOPUWR | _         | _      | VREGSF | _           | СМ        | VREGS    | EXTR    | SWR    | SWDTEN | WDTO    | SLEEP | IDLE   | BOR   | POR   | Note 1        |

| OSCCON    | 0742  | _      | 0      | COSC<2:0> |        | —      |             | NOSC<2:0> |          | CLKLOCK | IOLOCK | LOCK   | _       | CF    | _      | _     | OSWEN | Note 2        |

| CLKDIV    | 0744  | ROI    | [      | OOZE<2:0> |        | DOZEN  | FRCDIV<2:0> |           |          | PLLPOS  | T<1:0> | _      |         | F     | LLPRE< | 4:0>  |       | 0030          |

| PLLFBD    | 0746  | _      | _      | _         | _      | —      |             |           |          |         |        | PLLD   | IV<8:0> |       |        |       |       | 0030          |

| OSCTUN    | 0748  | _      | _      | _         | _      | —      | _           | _         | TUN<5:0> |         |        |        |         |       | 0000   |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration Fuses.

# TABLE 4-36: REFERENCE CLOCK REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| REFOCON   | 074E  | ROON   | —      | ROSSLP | ROSEL  |        | RODI   | V<3:0> |       | _     | _     | —     | _     | _     | —     | _     | -     | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-39: PMD REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   |        |       |       | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  |        | _      | _      | -      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  |       |       | CRCMD  | _     | —     | —      |        | —      | I2C2MD |       | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      |       |       | _      | _     | —     | —      | REFOMD | CTMUMD |        |       | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      |        |       |       | _      |       | —     | _      |        | —      |        |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |       |       |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIND7        | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | —     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-40: PMD REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  | _      | —      | —      | —      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | —     | —     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      | —      |        | _      | _      | PWM3MD | PWM2MD | PWM1MD | —      |       |       | _      | —      |        | —      | -     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | —      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 95

#### TABLE 4-42: OP AMP/COMPARATOR REGISTER MAP

| File Name                | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11                                   | Bit 10  | Bit 9   | Bit 8 | Bit 7 | Bit 6  | Bit 5    | Bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Bit 3   | Bit 2  | Bit 1     | Bit 0 | All<br>Resets |

|--------------------------|-------|--------|--------|--------|--------|------------------------------------------|---------|---------|-------|-------|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|-----------|-------|---------------|

| CMSTAT                   | 0A80  | PSIDL  | _      | -      | —      | C4EVT                                    | C3EVT   | C2EVT   | C1EVT | _     | -      | —        | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | C4OUT   | C3OUT  | C2OUT     | C10UT | 0000          |

| CVRCON                   | 0A82  |        | CVR2OE | _      | _      | _                                        | VREFSEL | _       | _     | CVREN | CVR10E | CVRR     | CVRSS         CVR<3:0>         C           CREF         —         —         CCH<1:0>         C           SELSRCA<3:0>         C         C         C         C           ACNEN         ABEN         AAEN         AANEN         C           CO>         CFLTREN         CFDIV<2:0>         C         C           CREF         —         —         CCH<1:0>         C           ACNEN         ABEN         AAEN         AANEN         C           ACREF         —         —         CCH<1:0>         C           ACNEN         ABEN         ABNEN         AAEN         AANEN         C |         |        |           | 0000  |               |

| CM1CON                   | 0A84  | CON    | COE    | CPOL   | _      | _                                        | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _       | _      | CCH       | <1:0> | 0000          |

| CM1MSKSRC                | 0A86  |        | _      | _      | _      |                                          | SELSR   | CC<3:0> |       |       | SELSRC | B<3:0>   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         | SELSRC | A<3:0>    |       | 0000          |

| CM1MSKCON                | 0A88  | HLMS   | _      | OCEN   | OCNEN  | OBEN                                     | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM1FLTR                  | 0A8A  |        | _      | _      | _      | _                                        | _       | _       | _     | _     | C      | FSEL<2:0 | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CFLTREN | (      | CFDIV<2:0 | >     | 0000          |

| CM2CON                   | 0A8C  | CON    | COE    | CPOL   | _      | _                                        | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | —       | _      | CCH       | <1:0> | 0000          |

| CM2MSKSRC                | 0A8E  |        | _      | _      | _      | - SELSRCC<3:0> SELSRCB<3:0> SELSRCA<3:0> |         |         |       |       |        | 0000     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |        |           |       |               |

| CM2MSKCON                | 0A90  | HLMS   | _      | OCEN   | OCNEN  | OBEN                                     | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM2FLTR                  | 0A92  | _      | _      | _      | _      | _                                        | _       | _       | _     |       | C      | FSEL<2:0 | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CFLTREN | (      | CFDIV<2:0 | >     | 0000          |

| CM3CON <sup>(1)</sup>    | 0A94  | CON    | COE    | CPOL   | _      | _                                        | OPMODE  | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | —       | _      | CCH       | <1:0> | 0000          |

| CM3MSKSRC(1)             | 0A96  | _      | _      | _      | _      |                                          | SELSR   | CC<3:0> |       |       | SELSRC | B<3:0>   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         | SELSRC | A<3:0>    |       | 0000          |

| CM3MSKCON <sup>(1)</sup> | 0A98  | HLMS   | _      | OCEN   | OCNEN  | OBEN                                     | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM3FLTR <sup>(1)</sup>   | 0A9A  | _      | _      | _      | _      | _                                        | _       | _       | _     |       | C      | FSEL<2:0 | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CFLTREN | (      | CFDIV<2:0 | >     | 0000          |

| CM4CON                   | 0A9C  | CON    | COE    | CPOL   | _      | _                                        | _       | CEVT    | COUT  | EVPOL | _<1:0> | _        | CREF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | —       | _      | CCH       | <1:0> | 0000          |

| CM4MSKSRC                | 0A9E  | _      | _      |        |        |                                          | SELSR   | CC<3:0> | -     |       | SELSRC | B<3:0>   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         | SELSRC | A<3:0>    |       | 0000          |

| CM4MSKCON                | 0AA0  | HLMS   | _      | OCEN   | OCNEN  | OBEN                                     | OBNEN   | OAEN    | OANEN | NAGS  | PAGS   | ACEN     | ACNEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ABEN    | ABNEN  | AAEN      | AANEN | 0000          |

| CM4FLTR                  | 0AA2  | _      | _      |        | _      | _                                        | _       | _       | _     | —     | C      | FSEL<2:0 | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CFLTREN | (      | CFDIV<2:0 | >     | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These registers are unavailable on dsPIC33EPXXXGP502/MC502/MC502/MC202 and PIC24EP256GP/MC202 (28-pin) devices.

#### TABLE 4-43: CTMU REGISTER MAP

| File N | lame | Addr. | Bit 15  | Bit 14  | Bit 13   | Bit 12 | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7   | Bit 6   | Bit 5 | Bit 4 | Bit 3   | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------|------|-------|---------|---------|----------|--------|----------|----------|----------|----------|---------|---------|-------|-------|---------|-------|-------|-------|---------------|

| CTMUC  | CON1 | 033A  | CTMUEN  | —       | CTMUSIDL | TGEN   | EDGEN    | EDGSEQEN | IDISSEN  | CTTRIG   | _       | _       | _     | _     | _       | _     | _     | _     | 0000          |

| CTMUC  | CON2 | 033C  | EDG1MOD | EDG1POL |          | EDG1   | SEL<3:0> |          | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |       | EDG2S | EL<3:0> |       | _     | -     | 0000          |

| CTMU   | ICON | 033E  |         |         | ITRIM<5  | 5:0>   |          |          | IRNG     | <1:0>    |         | _       | _     | _     | _       | _     | -     | _     | 0000          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-44: JTAG INTERFACE REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11       | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| JDATAH    | 0FF0 | _      | —      | _      | _      |              |        |       |       |       |       |       |       |       |       |       | xxxx  |               |

| JDATAL    | 0FF2 |        |        |        |        | JDATAL<15:0> |        |       |       |       |       |       |       |       |       |       |       |               |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 97

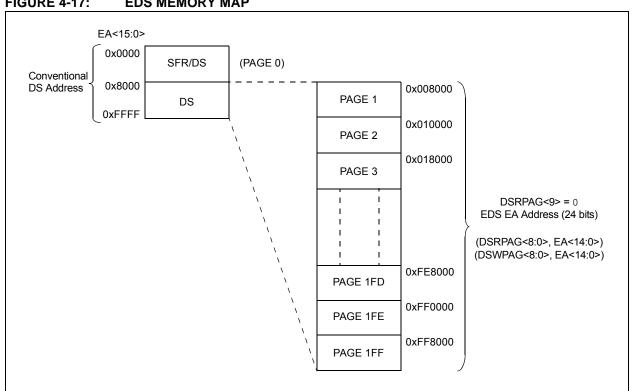

#### 4.4.2 EXTENDED X DATA SPACE

The lower portion of the base address space range, between 0x0000 and 0x7FFF, is always accessible regardless of the contents of the Data Space Page registers. It is indirectly addressable through the register indirect instructions. It can be regarded as being located in the default EDS Page 0 (i.e., EDS address range of 0x000000 to 0x007FFF with the base address bit, EA<15> = 0, for this address range). However, Page 0 cannot be accessed through the upper 32 Kbytes, 0x8000 to 0xFFFF, of base Data Space, in combination with DSRPAG = 0x000 or DSWPAG = 0x000. Consequently, DSRPAG and DSWPAG are initialized to 0x001 at Reset.

- Note 1: DSxPAG should not be used to access Page 0. An EDS access with DSxPAG set to 0x000 will generate an address error trap.

- 2: Clearing the DSxPAG in software has no effect.

The remaining pages, including both EDS and PSV pages, are only accessible using the DSRPAG or DSWPAG registers in combination with the upper 32 Kbytes, 0x8000 to 0xFFFF, of the base address, where base address bit, EA<15> = 1.

For example, when DSRPAG = 0x001 or DSWPAG = 0x001, accesses to the upper 32 Kbytes, 0x8000 to 0xFFFF, of the Data Space will map to the EDS address range of 0x008000 to 0x00FFFF. When DSRPAG = 0x002 or DSWPAG = 0x002, accesses to the upper 32 Kbytes of the Data Space will map to the EDS address range of 0x010000 to 0x017FFF and so on, as shown in the EDS memory map in Figure 4-17.

For more information on the PSV page access using Data Space Page registers, refer to the "**Program Space Visibility from Data Space**" section in "**Program Memory**" (DS70613) of the "*dsPIC33/ PIC24 Family Reference Manual*".

#### FIGURE 4-17: EDS MEMORY MAP

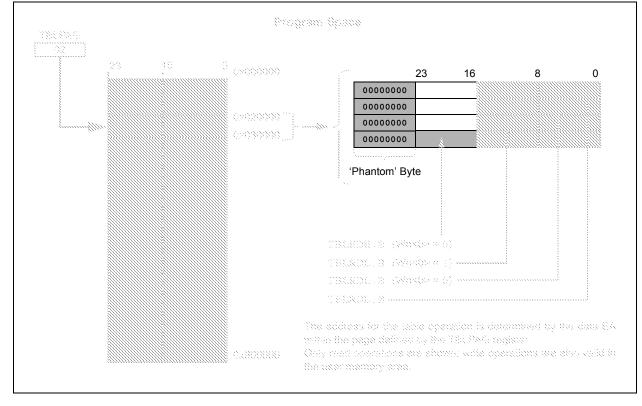

#### 4.8.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the Program Space without going through Data Space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a Program Space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to Data Space addresses. Program memory can thus be regarded as two 16-bit-wide word address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space that contains the least significant data word. TBLRDH and TBLWTH access the space that contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from Program Space. Both function as either byte or word operations.

- TBLRDL (Table Read Low):

- In Word mode, this instruction maps the lower word of the Program Space location (P<15:0>) to a data address (D<15:0>)

- In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High):

- In Word mode, this instruction maps the entire upper word of a program address (P<23:16>) to a data address. The 'phantom' byte (D<15:8>) is always '0'.

- In Byte mode, this instruction maps the upper or lower byte of the program word to D<7:0> of the data address in the TBLRDL instruction. The data is always '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a Program Space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user application and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

# FIGURE 4-23: ACCESSING PROGRAM MEMORY WITH TABLE INSTRUCTIONS

# 5.2 RTSP Operation

RTSP allows the user application to erase a single page of memory and to program two instruction words at a time. See the General Purpose and Motor Control Family tables (Table 1 and Table 2, respectively) for the page sizes of each device.

For more information on erasing and programming Flash memory, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual".

# 5.3 **Programming Operations**

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

For erase and program times, refer to Parameters D137a and D137b (Page Erase Time), and D138a and D138b (Word Write Cycle Time) in Table 30-14 in **Section 30.0 "Electrical Characteristics"**.

Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

#### 5.3.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program two adjacent words (24 bits x 2) of program Flash memory at a time on every other word address boundary (0x000002, 0x000006, 0x00000A, etc.). To do this, it is necessary to erase the page that contains the desired address of the location the user wants to change.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS.

Refer to **Flash Programming**" (DS70609) in the "*dsPIC33/PIC24 Family Reference Manual*" for details and codes examples on programming using RTSP.

# 5.4 Flash Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 5.4.1 KEY RESOURCES

- "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# 5.5 Control Registers

Four SFRs are used to erase and write the program Flash memory: NVMCON, NVMKEY, NVMADRH and NVMADRL.

The NVMCON register (Register 5-1) enables and initiates Flash memory erase and write operations.

NVMKEY (Register 5-4) is a write-only register that is used for write protection. To start a programming or erase sequence, the user application must consecutively write 0x55 and 0xAA to the NVMKEY register.

There are two NVM Address registers: NVMADRH and NVMADRL. These two registers, when concatenated, form the 24-bit Effective Address (EA) of the selected word for programming operations or the selected page for erase operations.

The NVMADRH register is used to hold the upper 8 bits of the EA, while the NVMADRL register is used to hold the lower 16 bits of the EA.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 7-5: | INTCON3: INTERRUPT CONTROL REGISTER 3 |

|---------------|---------------------------------------|

| U-0                                          | U-0                        | U-0                                           | U-0                                     | U-0          | U-0              | U-0    | U-0   |

|----------------------------------------------|----------------------------|-----------------------------------------------|-----------------------------------------|--------------|------------------|--------|-------|

|                                              | —                          | _                                             | —                                       | —            | —                | —      | _     |

| bit 15                                       |                            |                                               |                                         |              |                  | •      | bit 8 |

|                                              |                            |                                               |                                         |              |                  |        |       |

| U-0                                          | U-0                        | R/W-0                                         | R/W-0                                   | U-0          | U-0              | U-0    | U-0   |

| —                                            | —                          | DAE                                           | DOOVR                                   | —            | —                | —      | —     |

| bit 7                                        |                            |                                               |                                         |              |                  |        | bit 0 |

|                                              |                            |                                               |                                         |              |                  |        |       |

| Legend:                                      |                            |                                               |                                         |              |                  |        |       |

| R = Readab                                   | le bit                     | W = Writable                                  | bit                                     | U = Unimplei | mented bit, read | as '0' |       |

| -n = Value at POR '1' = Bit is set           |                            | t                                             | '0' = Bit is cleared x = Bit is unknown |              |                  | nown   |       |

|                                              |                            |                                               |                                         |              |                  |        |       |

| bit 15-6                                     | Unimplemented: Read as '0' |                                               |                                         |              |                  |        |       |

| bit 5                                        | DAE: DMA A                 | DAE: DMA Address Error Soft Trap Status bit   |                                         |              |                  |        |       |

| 1 = DMA address error soft trap has occurred |                            |                                               |                                         |              |                  |        |       |

|                                              | 0 = DMA add                | ress error soft                               | trap has not o                          | ccurred      |                  |        |       |

| bit 4                                        | DOOVR: DO                  | DOOVR: DO Stack Overflow Soft Trap Status bit |                                         |              |                  |        |       |

|                                              | 1 = DO stack               | overflow soft t                               | rap has occurre                         | ed           |                  |        |       |

| I = D0 | Stack Overnow  | 3011 11 ap 11 a3 | occurred     |

|--------|----------------|------------------|--------------|

| 0 = DO | stack overflow | soft trap has    | not occurred |

| bit 3-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

# REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|-----|-----|-----|-----|-----|-------|

| —       | —   | —   | —   | —   | —   | —   | —     |

| bit 15  |     |     |     |     | •   |     | bit 8 |

|         |     |     |     |     |     |     |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

| _       | —   | —   |     | —   | —   | —   | SGHT  |

| bit 7   |     |     |     |     | •   |     | bit 0 |

|         |     |     |     |     |     |     |       |

| Legend: |     |     |     |     |     |     |       |

| 3                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                   |                  |                        |                    |

bit 0

SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

# 15.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 15.1.1 KEY RESOURCES

- "Output Compare" (DS70358) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

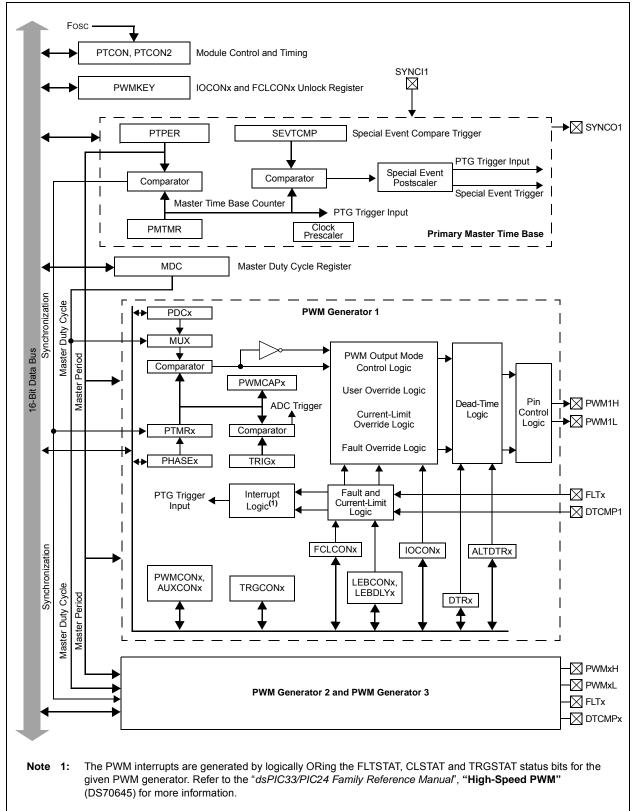

#### FIGURE 16-2: HIGH-SPEED PWMx MODULE REGISTER INTERCONNECTION DIAGRAM

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                         | U-0                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                            | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                               | R/W-0            | R/W-0             | R/W-0         |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------|-------------------|---------------|

| _                           | _                                                                                                                                                                                                          | _                                                                                                                                                                                                                                              | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BLANKSEL3                                                                                           | BLANKSEL2        | BLANKSEL1         | BLANKSEL      |

| bit 15                      | •                                                                                                                                                                                                          | •                                                                                                                                                                                                                                              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •                                                                                                   |                  | •                 | bit 8         |

| U-0                         | U-0                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                               | R/W-0            | R/W-0             | R/W-0         |

|                             |                                                                                                                                                                                                            | CHOPSEL3                                                                                                                                                                                                                                       | CHOPSEL2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CHOPSEL1                                                                                            | CHOPSEL0         | CHOPHEN           | CHOPLEN       |

| bit 7                       |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  | onornen           | bit           |

|                             |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  |                   |               |

| Legend:                     |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  | (0)               |               |

| R = Readab                  |                                                                                                                                                                                                            | W = Writable bit                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                                                                                                   | ented bit, read  |                   |               |

| -n = Value a                | at POR                                                                                                                                                                                                     | '1' = Bit is set                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | '0' = Bit is clea                                                                                   | red              | x = Bit is unkr   | nown          |

| bit 15-12                   | Unimplemen                                                                                                                                                                                                 | ted: Read as '                                                                                                                                                                                                                                 | D'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                     |                  |                   |               |

| bit 11-8                    | -                                                                                                                                                                                                          |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | urce Select bits                                                                                    |                  |                   |               |

|                             | The selected                                                                                                                                                                                               | state blank sig                                                                                                                                                                                                                                | nal will block t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | he current-limit                                                                                    | and/or Fault inp | out signals (if e | nabled via th |

|                             | BCH and BCI                                                                                                                                                                                                | L bits in the LEI                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     | ·                | 5 (               |               |