Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuils                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gp504t-i-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

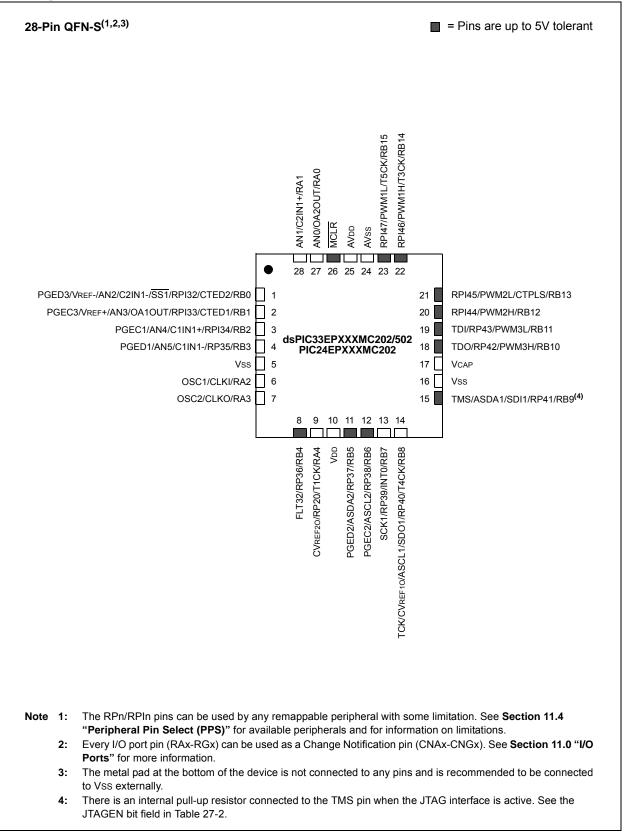

#### Pin Diagrams (Continued)

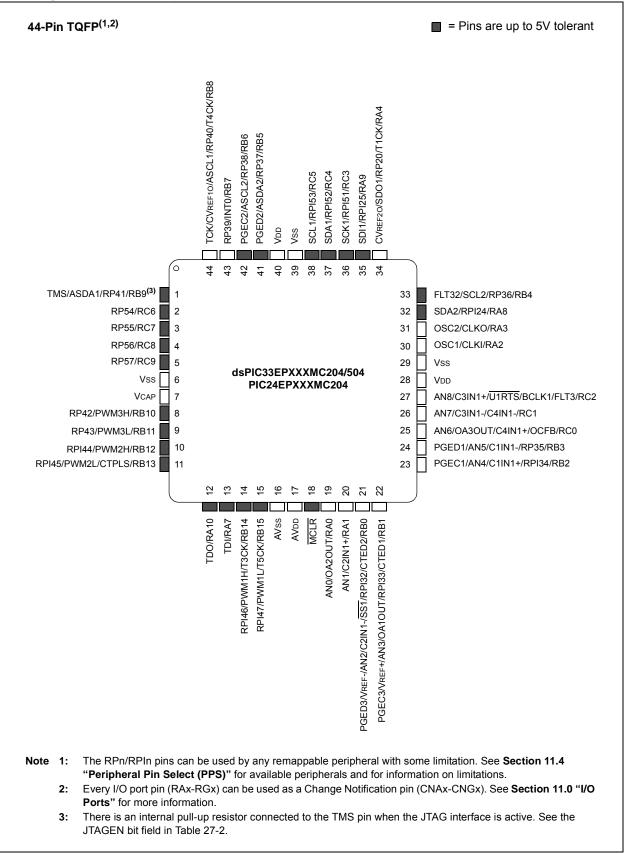

#### Pin Diagrams (Continued)

| TABLE 4   | 4-9:  | INPUT                               |                                     | JRE 1 T | HROUG  | H INPU    | Т САРТ | URE 4 | REGIST       | ER MA        | Р        |       |       |                     |          |          |       |               |

|-----------|-------|-------------------------------------|-------------------------------------|---------|--------|-----------|--------|-------|--------------|--------------|----------|-------|-------|---------------------|----------|----------|-------|---------------|

| File Name | Addr. | Bit 15                              | Bit 14                              | Bit 13  | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3               | Bit 2    | Bit 1    | Bit 0 | All<br>Resets |

| IC1CON1   | 0140  | _                                   | —                                   | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | -            | —            | ICI<     | :0>   | ICOV  | ICOV ICBNE ICM<2:0> |          |          | 0000  |               |

| IC1CON2   | 0142  | _                                   | IC32 ICTRIG TRIGSTAT - SYNCSEL<4:0> |         |        |           |        |       |              | 000D         |          |       |       |                     |          |          |       |               |

| IC1BUF    | 0144  |                                     | Input Capture 1 Buffer Register     |         |        |           |        |       |              |              | xxxx     |       |       |                     |          |          |       |               |

| IC1TMR    | 0146  |                                     | Input Capture 1 Timer 0000          |         |        |           |        |       |              |              |          |       |       |                     |          |          |       |               |

| IC2CON1   | 0148  |                                     | _                                   | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE               |          | ICM<2:0> |       | 0000          |

| IC2CON2   | 014A  | IC32 ICTRIG TRIGSTAT - SYNCSEL<4:0> |                                     |         |        |           |        | 000D  |              |              |          |       |       |                     |          |          |       |               |

| IC2BUF    | 014C  |                                     |                                     |         |        |           |        | Inp   | ut Capture 2 | 2 Buffer Reg | gister   |       |       |                     |          |          |       | xxxx          |

| IC2TMR    | 014E  |                                     |                                     |         |        |           |        |       | Input Capt   | ture 2 Time  | r        |       |       |                     |          |          |       | 0000          |

| IC3CON1   | 0150  |                                     | _                                   | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE               |          | ICM<2:0> |       | 0000          |

| IC3CON2   | 0152  |                                     | _                                   |         |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S                   | YNCSEL<4 | :0>      |       | 000D          |

| IC3BUF    | 0154  |                                     |                                     |         |        |           |        | Inp   | ut Capture 3 | 3 Buffer Reg | gister   |       |       |                     |          |          |       | xxxx          |

| IC3TMR    | 0156  |                                     |                                     |         |        |           |        |       | Input Capt   | ture 3 Time  | r        |       |       |                     |          |          |       | 0000          |

| IC4CON1   | 0158  |                                     | _                                   | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE               |          | ICM<2:0> |       | 0000          |

| IC4CON2   | 015A  | _                                   | _                                   |         | _      |           | -      | _     | IC32         | ICTRIG       | TRIGSTAT | -     |       | S                   | YNCSEL<4 | :0>      |       | 000D          |

| IC4BUF    | 015C  |                                     | Input Capture 4 Buffer Register     |         |        |           |        |       |              |              |          |       | xxxx  |                     |          |          |       |               |

| IC4TMR    | 015E  |                                     |                                     |         |        |           |        |       | Input Capt   | ure 4 Time   | r        |       |       |                     |          |          |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4-29:       PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY |       |        |              |        |        |            |        |       |       |       |            |            |       |            |       |       |       |               |

|---------------------------------------------------------------------------------------------|-------|--------|--------------|--------|--------|------------|--------|-------|-------|-------|------------|------------|-------|------------|-------|-------|-------|---------------|

| File<br>Name                                                                                | Addr. | Bit 15 | Bit 14       | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5      | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| RPINR0                                                                                      | 06A0  | _      |              |        |        | INT1R<6:0> |        |       |       | —     |            |            |       |            |       | _     | 0000  |               |

| RPINR1                                                                                      | 06A2  | _      | _            | _      | _      | _          | _      | _     | _     | _     | INT2R<6:0> |            |       |            |       |       | 0000  |               |

| RPINR3                                                                                      | 06A6  | _      | _            | _      | _      | _          | _      | _     | _     | _     |            |            |       | T2CKR<6:0  | >     |       |       | 0000          |

| RPINR7                                                                                      | 06AE  | _      |              |        |        | IC2R<6:0>  |        | •     |       | _     |            |            |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8                                                                                      | 06B0  | _      |              |        |        | IC4R<6:0>  |        |       |       | _     |            |            |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11                                                                                     | 06B6  | _      | -            | _      | _      | _          | _      | _     | _     | _     |            |            | (     | OCFAR<6:0  | >     |       |       | 0000          |

| RPINR12                                                                                     | 06B8  | _      | FLT2R<6:0>   |        |        |            |        | _     |       |       |            | FLT1R<6:0> | >     |            |       | 0000  |       |               |

| RPINR14                                                                                     | 06BC  | _      | QEB1R<6:0>   |        |        |            |        | _     |       |       | (          | QEA1R<6:0  | >     |            |       | 0000  |       |               |

| RPINR15                                                                                     | 06BE  | _      |              |        | Н      | OME1R<6:0  | )>     |       |       | _     |            |            | 1     | NDX1R<6:0  | >     |       |       | 0000          |

| RPINR18                                                                                     | 06C4  | _      | _            | _      | _      | _          | _      | _     | _     | _     |            |            | I     | U1RXR<6:0  | >     |       |       | 0000          |

| RPINR19                                                                                     | 06C6  | _      | _            | _      | _      | _          | _      | _     | _     | _     |            |            | I     | U2RXR<6:0  | >     |       |       | 0000          |

| RPINR22                                                                                     | 06CC  |        |              |        | S      | CK2INR<6:( | )>     |       |       | _     |            |            |       | SDI2R<6:0> | >     |       |       | 0000          |

| RPINR23                                                                                     | 06CE  |        | _            | _      | _      | _          | _      | _     | _     | _     |            |            |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26                                                                                     | 06D4  |        | _            | _      | _      | _          | _      | _     | _     | _     | _          | _          | _     | _          | _     | _     | _     | 0000          |

| RPINR37                                                                                     | 06EA  | _      |              |        | S      | YNCI1R<6:0 | )>     |       |       | _     | _          | —          | —     | —          | _     | _     | _     | 0000          |

| RPINR38                                                                                     | 06EC  | _      |              |        | D      | FCMP1R<6:  | 0>     |       |       | _     | _          | —          | —     | —          | _     | _     | _     | 0000          |

| RPINR39                                                                                     | 06EE  | _      | DTCMP3R<6:0> |        |        |            | -      |       |       | D     | TCMP2R<6:  | :0>        |       |            | 0000  |       |       |               |

#### TABLE 4-29: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR PIC24EPXXXMC20X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-30: PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6        | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|------------|--------|------------|--------|-------|-------|-------|--------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | —      |        | INT1R<6:0> |        |            |        |       |       | _     | —            | —     | —     | —          | _     | -     | _     | 0000          |

| RPINR1       | 06A2  | _      | _      | _          | _      | _          | _      | _     | _     | _     |              |       |       | INT2R<6:0> |       |       |       | 0000          |

| RPINR3       | 06A6  | _      | _      | _          | _      | _          | _      | _     | _     | _     | T2CKR<6:0>   |       |       |            |       | 0000  |       |               |

| RPINR7       | 06AE  | _      |        |            |        | IC2R<6:0>  |        |       |       | _     |              |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  | _      |        |            |        | IC4R<6:0>  |        |       |       | _     |              |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6  | _      | _      | _          | _      | _          | _      | _     | _     | _     |              |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR18      | 06C4  | _      | _      | _          | _      | _          | _      | _     | _     | _     |              |       | ι     | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19      | 06C6  | _      | _      | _          | _      | _          | _      | _     | _     | _     |              |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22      | 06CC  | —      |        |            | S      | CK2INR<6:0 | )>     |       |       | _     | - SDI2R<6:0> |       |       |            |       | 0000  |       |               |

| RPINR23      | 06CE  | _      | _      | —          | —      | —          | —      | —     | —     | _     |              |       |       | SS2R<6:0>  |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| R/W-0  | U-0   | R/W-0 | R/W-0  | R/W-0               | R-0 | R-0   | R-0   |

|--------|-------|-------|--------|---------------------|-----|-------|-------|

| VAR    | —     | US1   | US0    | EDT                 | DL2 | DL1   | DL0   |

| bit 15 |       | •     |        |                     |     |       | bit 8 |

|        |       |       |        |                     |     |       |       |

| R/W-0  | R/W-0 | R/W-1 | R/W-0  | R/C-0               | R-0 | R/W-0 | R/W-0 |

| SATA   | SATB  | SATDW | ACCSAT | IPL3 <sup>(2)</sup> | SFA | RND   | IF    |

| bit 7  |       | •     |        |                     |     |       | bit 0 |

|        |       |       |        |                     |     |       |       |

|        |       |       |        |                     |     |       |       |

## **REGISTER 7-2:** CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| Legend:           | C = Clearable bit |                      |                    |

|-------------------|-------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1'= Bit is set   | '0' = Bit is cleared | x = Bit is unknown |

bit

| VAR: Variable Exception Processing Latency Control                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------|

| <ol> <li>1 = Variable exception processing is enabled</li> </ol>                                                              |

| 0 = Fixed exception processing is enabled                                                                                     |

| IPL3: CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup>                                                                |

| <ul> <li>1 = CPU Interrupt Priority Level is greater than 7</li> <li>0 = CPU Interrupt Priority Level is 7 or less</li> </ul> |

|                                                                                                                               |

**Note 1:** For complete register details, see Register 3-2.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

|                 | 12. 2007.00    |                                       |              |                   |                  |                 |        |

|-----------------|----------------|---------------------------------------|--------------|-------------------|------------------|-----------------|--------|

| U-0             | U-0            | U-0                                   | U-0          | U-0               | U-0              | U-0             | U-0    |

| —               | —              | —                                     | —            | —                 | —                | —               | —      |

| bit 15          |                |                                       |              |                   |                  |                 | bit 8  |

|                 |                |                                       |              |                   |                  |                 |        |

| U-0             | U-0            | U-0                                   | U-0          | R-0               | R-0              | R-0             | R-0    |

| —               |                | —                                     | —            | RQCOL3            | RQCOL2           | RQCOL1          | RQCOL0 |

| bit 7           |                |                                       |              |                   |                  |                 | bit 0  |

|                 |                |                                       |              |                   |                  |                 |        |

| Legend:         |                |                                       |              |                   |                  |                 |        |

| R = Readable    | bit            | W = Writable                          | bit          | U = Unimpler      | mented bit, read | l as '0'        |        |

| -n = Value at F | POR            | '1' = Bit is set                      |              | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |

|                 |                |                                       |              |                   |                  |                 |        |

| bit 15-4        | Unimplemen     | ted: Read as '                        | כ'           |                   |                  |                 |        |

| bit 3           | RQCOL3: DN     | /IA Channel 3 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |

|                 |                | e and interrupt<br>est collision is d |              | st collision is d | etected          |                 |        |

| <b>h</b> # 0    | •              |                                       |              | est Callisian Fl  | aa hit           |                 |        |

| bit 2           |                | /IA Channel 2 T<br>ce and interrupt   | •            |                   | 0                |                 |        |

|                 |                | e and interrupt<br>est collision is d |              |                   | elecieu          |                 |        |

| bit 1           | RQCOL1: DN     | /IA Channel 1 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |

|                 | 1 = User for   | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

|                 | 0 = No reque   | est collision is d                    | etected      |                   |                  |                 |        |

| bit 0           | RQCOLO: DN     | /IA Channel 0 T                       | ransfer Requ | est Collision F   | lag bit          |                 |        |

|                 | 1 = User force | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

#### REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

| REGISTER     | TU-5: PIVID6 | . PERIPHER       |                           | DISABLE C         | UNIROL RE             | GISIER 6              |                       |

|--------------|--------------|------------------|---------------------------|-------------------|-----------------------|-----------------------|-----------------------|

| U-0          | U-0          | U-0              | U-0                       | U-0               | R/W-0                 | R/W-0                 | R/W-0                 |

| —            | —            | —                | —                         | —                 | PWM3MD <sup>(1)</sup> | PWM2MD <sup>(1)</sup> | PWM1MD <sup>(1)</sup> |

| bit 15       |              |                  |                           |                   |                       |                       | bit 8                 |

|              |              |                  |                           |                   |                       |                       |                       |

| U-0          | U-0          | U-0              | U-0                       | U-0               | U-0                   | U-0                   | U-0                   |

|              |              |                  |                           |                   |                       |                       |                       |

| bit 7        |              |                  |                           |                   |                       |                       | bit 0                 |

|              |              |                  |                           |                   |                       |                       |                       |

| Legend:      |              |                  |                           |                   |                       |                       |                       |

| R = Readab   | le bit       | W = Writable     | bit                       | U = Unimplen      | nented bit, read      | l as '0'              |                       |

| -n = Value a | t POR        | '1' = Bit is set |                           | '0' = Bit is clea | ared                  | x = Bit is unkr       | iown                  |

|              |              |                  |                           |                   |                       |                       |                       |

| bit 15-11    | Unimplement  | ted: Read as '   | כ'                        |                   |                       |                       |                       |

| bit 10       | PWM3MD: P\   | NM3 Module D     | isable bit <sup>(1)</sup> |                   |                       |                       |                       |

|              | 1 = PWM3 mo  | odule is disable | ed                        |                   |                       |                       |                       |

|              | 0 = PWM3 mo  | odule is enable  | d                         |                   |                       |                       |                       |

| bit 9        | PWM2MD: P\   | NM2 Module D     | isable bit <sup>(1)</sup> |                   |                       |                       |                       |

|              | 1 = PWM2 mo  | odule is disable | ed                        |                   |                       |                       |                       |

|              | 0 = PWM2 mo  | odule is enable  | d                         |                   |                       |                       |                       |

| bit 8        | PWM1MD: P\   | NM1 Module D     | isable bit <sup>(1)</sup> |                   |                       |                       |                       |

|              |              | odule is disable |                           |                   |                       |                       |                       |

|              | 0 = PWM1 mo  | odule is enable  | d                         |                   |                       |                       |                       |

| bit 7-0      | Unimplement  | ted: Read as '   | כ'                        |                   |                       |                       |                       |

## REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

Note 1: This bit is available on dsPIC33EPXXXMC50X/20X and PIC24EPXXXMC20X devices only.

## 12.2 Timer1 Control Register

| R/W-0              | U-0                                  | R/W-0                             | U-0                       | U-0              | U-0                      | U-0                | U-0                |

|--------------------|--------------------------------------|-----------------------------------|---------------------------|------------------|--------------------------|--------------------|--------------------|

| TON <sup>(1)</sup> | —                                    | TSIDL                             | —                         | _                | —                        | _                  | _                  |

| bit 15             |                                      |                                   |                           |                  |                          |                    | bit 8              |

|                    |                                      |                                   |                           |                  |                          |                    |                    |

| U-0                | R/W-0                                | R/W-0                             | R/W-0                     | U-0              | R/W-0                    | R/W-0              | U-0                |

|                    | TGATE                                | TCKPS1                            | TCKPS0                    | _                | TSYNC <sup>(1)</sup>     | TCS <sup>(1)</sup> |                    |

| bit 7              |                                      |                                   |                           |                  |                          |                    | bit (              |

| Legend:            |                                      |                                   |                           |                  |                          |                    |                    |

| R = Readable       | e bit                                | W = Writable                      | bit                       | U = Unimplei     | mented bit, read         | l as '0'           |                    |

| -n = Value at      | POR                                  | '1' = Bit is set                  |                           | '0' = Bit is cle | ared                     | x = Bit is unkno   | own                |

|                    |                                      | o                                 |                           |                  |                          |                    |                    |

| bit 15             | <b>TON:</b> Timer1<br>1 = Starts 16- |                                   |                           |                  |                          |                    |                    |

|                    | 0 = Stops 16-                        |                                   |                           |                  |                          |                    |                    |

| bit 14             | Unimplemen                           | ted: Read as '                    | 0'                        |                  |                          |                    |                    |

| bit 13             | TSIDL: Timer                         | 1 Stop in Idle N                  | /lode bit                 |                  |                          |                    |                    |

|                    |                                      | ues module op                     |                           |                  | ldle mode                |                    |                    |

|                    |                                      | s module opera                    |                           | ode              |                          |                    |                    |

| bit 12-7           | -                                    | ted: Read as '                    |                           |                  |                          |                    |                    |

| bit 6              |                                      | r1 Gated Time                     | Accumulation              | h Enable bit     |                          |                    |                    |

|                    | When TCS =<br>This bit is igno       |                                   |                           |                  |                          |                    |                    |

|                    | When TCS =                           |                                   |                           |                  |                          |                    |                    |

|                    |                                      | e accumulatio                     |                           |                  |                          |                    |                    |

|                    |                                      | e accumulatio                     |                           | 0.1.1.1.1.1      |                          |                    |                    |

| bit 5-4            |                                      | : Timer1 Input                    | Clock Prescal             | e Select bits    |                          |                    |                    |

|                    | 11 = 1:256<br>10 = 1:64              |                                   |                           |                  |                          |                    |                    |

|                    | 01 = 1:8                             |                                   |                           |                  |                          |                    |                    |

|                    | 00 = 1:1                             |                                   |                           |                  |                          |                    |                    |

| bit 3              | -                                    | ted: Read as '                    |                           |                  |                          |                    |                    |

| bit 2              |                                      | er1 External Clo                  | ock Input Synd            | chronization S   | elect bit <sup>(1)</sup> |                    |                    |

|                    | When TCS =                           |                                   |                           |                  |                          |                    |                    |

|                    |                                      | izes external c<br>synchronize e> |                           | nut              |                          |                    |                    |

|                    | When TCS =                           | •                                 |                           | iput             |                          |                    |                    |

|                    | This bit is igno                     |                                   |                           |                  |                          |                    |                    |

| bit 1              | TCS: Timer1                          | Clock Source S                    | Select bit <sup>(1)</sup> |                  |                          |                    |                    |

|                    | 1 = External c<br>0 = Internal cl    | clock is from pi<br>ock (FP)      | n, T1CK (on th            | ne rising edge)  | •                        |                    |                    |

| bit 0              | Unimplemen                           | ted: Read as '                    | 0'                        |                  |                          |                    |                    |

|                    | nen Timer1 is er<br>empts by user s  |                                   |                           |                  |                          | SYNC = 1, TON      | <b>\ =</b> 1), any |

#### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

© 2011-2013 Microchip Technology Inc.

## 16.2 PWM Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 16.2.1 KEY RESOURCES

- "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# **19.2** I<sup>2</sup>C Control Registers

#### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0        | U-0                          | R/W-0                                  | R/W-1, HC                  | R/W-0                        | R/W-0            | R/W-0           | R/W-0          |

|--------------|------------------------------|----------------------------------------|----------------------------|------------------------------|------------------|-----------------|----------------|

| I2CEN        | —                            | I2CSIDL                                | SCLREL                     | IPMIEN <sup>(1)</sup>        | A10M             | DISSLW          | SMEN           |

| bit 15       |                              |                                        |                            |                              |                  |                 | bit 8          |

|              |                              |                                        |                            |                              |                  |                 |                |

| R/W-0        | R/W-0                        | R/W-0                                  | R/W-0, HC                  | R/W-0, HC                    | R/W-0, HC        | R/W-0, HC       | R/W-0, HC      |

| GCEN         | STREN                        | ACKDT                                  | ACKEN                      | RCEN                         | PEN              | RSEN            | SEN            |

| bit 7        |                              |                                        |                            |                              |                  |                 | bit 0          |

| Legend:      |                              | HC = Hardware                          | Cloarable bit              |                              |                  |                 |                |

| R = Readab   | le hit                       | W = Writable bi                        |                            | II = I Inimpler              | mented bit, rea  | d as '0'        |                |

| -n = Value a |                              | '1' = Bit is set                       | L .                        | '0' = Bit is cle             |                  | x = Bit is unk  | nown           |

|              |                              |                                        |                            |                              |                  |                 | nown           |

| bit 15       | <b>12CEN:</b> 12Cx           | Enable bit                             |                            |                              |                  |                 |                |

|              |                              | he I2Cx module                         |                            |                              |                  |                 | ;              |

|              | 0 = Disables                 | the I2Cx module;                       | all l <sup>2</sup> C™ pins | are controlled               | by port functior | ıs              |                |

| bit 14       | Unimplemen                   | ted: Read as '0'                       |                            |                              |                  |                 |                |

| bit 13       |                              | x Stop in Idle Mo                      |                            |                              |                  |                 |                |

|              |                              | ues module oper<br>s module operation  |                            |                              | dle mode         |                 |                |

| bit 12       |                              | Lx Release Conf                        |                            | _                            | ( clave)         |                 |                |

|              | 1 = Releases                 |                                        |                            |                              | slave)           |                 |                |

|              |                              | Lx clock low (clo                      | ck stretch)                |                              |                  |                 |                |

|              | If STREN = 1                 | <u>:</u>                               | -                          |                              |                  |                 |                |

|              | •                            | ., software can w                      |                            |                              |                  | ,               |                |

|              |                              | ing of every slav<br>reception. Hardw  |                            |                              |                  |                 | t every slave  |

|              | If STREN = 0                 | -                                      |                            |                              |                  |                 |                |

|              |                              | <u>.</u><br>, software can or          | nly write '1' to re        | elease clock). I             | Hardware is cle  | ar at the begir | ning of every  |

|              | -                            | te transmission.                       |                            |                              | -                | address byte re | eception.      |

| bit 11       |                              | ligent Peripheral                      |                            |                              |                  |                 |                |

|              | 1 = IPMI mod<br>0 = IPMI mod | e is enabled; all                      | addresses are              | Acknowledged                 | 1                |                 |                |

| bit 10       |                              | Slave Address b                        | i+                         |                              |                  |                 |                |

|              |                              | is a 10-bit slave                      |                            |                              |                  |                 |                |

|              |                              | is a 7-bit slave a                     |                            |                              |                  |                 |                |

| bit 9        | DISSLW: Dis                  | able Slew Rate C                       | Control bit                |                              |                  |                 |                |

|              |                              | control is disable                     |                            |                              |                  |                 |                |

|              |                              | control is enable                      |                            |                              |                  |                 |                |

| bit 8        |                              | us Input Levels b                      |                            | 0145                         | <b>c</b>         |                 |                |

|              |                              | /O pin thresholds<br>SMBus input thre  |                            | n SMBus speci                | fication         |                 |                |

| bit 7        |                              | ral Call Enable b                      |                            | ing as I <sup>2</sup> C slav | /e)              |                 |                |

|              | 1 = Enables in               | terrupt when a ge<br>all address disat | neral call addre           | -                            |                  | dule is enabled | for reception) |

|              |                              |                                        |                            |                              |                  |                 |                |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

| U-0                     | U-0                            | U-0                                | R-0     | R-0              | R-0             | R-0              | R-0     |  |

|-------------------------|--------------------------------|------------------------------------|---------|------------------|-----------------|------------------|---------|--|

| _                       | _                              |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1          | FILHIT0 |  |

| bit 15                  | <b>I</b>                       |                                    |         |                  |                 |                  | bit 8   |  |

|                         |                                |                                    |         |                  |                 |                  |         |  |

| U-0                     | R-1                            | R-0                                | R-0     | R-0              | R-0             | R-0              | R-0     |  |

| _                       | ICODE6                         | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1           | ICODE0  |  |

| bit 7                   |                                |                                    |         |                  |                 |                  | bit     |  |

| Logondi                 |                                |                                    |         |                  |                 |                  |         |  |

| Legend:<br>R = Readable | - hit                          | W = Writable                       | hit     | LI – Unimplor    | mented bit, rea | d as '0'         |         |  |

| -n = Value at           |                                | '1' = Bit is set                   |         | '0' = Bit is cle |                 | x = Bit is unkr  |         |  |

|                         | FUR                            |                                    |         |                  | aleu            | x – Dit is uliki |         |  |

| bit 15-13               | Unimplemen                     | ted: Read as '                     | 0'      |                  |                 |                  |         |  |

| bit 12-8                | =                              | Filter Hit Num                     |         |                  |                 |                  |         |  |

|                         |                                | 1 = Reserved                       |         |                  |                 |                  |         |  |

|                         | 01111 <b>= Filte</b>           | er 15                              |         |                  |                 |                  |         |  |

|                         | •                              |                                    |         |                  |                 |                  |         |  |

|                         | •                              |                                    |         |                  |                 |                  |         |  |

|                         |                                | - 1                                |         |                  |                 |                  |         |  |

|                         | 00001 = Filte<br>00000 = Filte |                                    |         |                  |                 |                  |         |  |

| bit 7                   |                                | ted: Read as '                     | 0'      |                  |                 |                  |         |  |

| bit 6-0                 | -                              | : Interrupt Flag                   |         |                  |                 |                  |         |  |

|                         | 1000101-1111111 = Reserved     |                                    |         |                  |                 |                  |         |  |

|                         |                                | IFO almost full                    |         |                  |                 |                  |         |  |

|                         |                                | leceiver overflo                   |         |                  |                 |                  |         |  |

|                         | 1000010 = K<br>1000001 = E     | Vake-up interru<br>rror interrupt  | μ       |                  |                 |                  |         |  |

|                         | 1000000 = N                    |                                    |         |                  |                 |                  |         |  |

|                         | •                              |                                    |         |                  |                 |                  |         |  |

|                         | •                              |                                    |         |                  |                 |                  |         |  |

|                         | •                              |                                    |         |                  |                 |                  |         |  |

|                         |                                | 11111 = Rese                       |         |                  |                 |                  |         |  |

|                         | •                              | B15 buffer inte                    | inupt   |                  |                 |                  |         |  |

|                         | •                              |                                    |         |                  |                 |                  |         |  |

|                         | •                              |                                    |         |                  |                 |                  |         |  |

|                         | 0001001 <b>= R</b>             | B9 buffer inter                    | rupt    |                  |                 |                  |         |  |

|                         |                                | B8 buffer inter                    |         |                  |                 |                  |         |  |

|                         |                                | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                  |         |  |

|                         |                                | RB5 buffer inte                    |         |                  |                 |                  |         |  |

|                         |                                | RB4 buffer inte                    |         |                  |                 |                  |         |  |

|                         | 0000011 <b>= T</b>             | RB3 buffer inte                    | errupt  |                  |                 |                  |         |  |

|                         |                                |                                    |         |                  |                 |                  |         |  |

|                         |                                | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                  |         |  |

#### REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

#### REGISTER 21-16: CxRXFnSID: ECANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

| RW-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x       R/W-x         SID10       SID9       SID8       SID7       SID6       SID5       SID4       SID3         bit 15       bit 15       bit 8       bit 8       bit 8       bit 8       bit 8         R/W-x       R/W-x       R/W-x       U-0       R/W-x       U-0       R/W-x       R/W-x         SID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       bit 0       -       EXIDE       -       EID17       EID16         bit 7       bit 0       -       -       EXIDE       -       bit 0         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |                                                                          |                                    |                     |                  |                  |                 |                    |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------|------------------------------------|---------------------|------------------|------------------|-----------------|--------------------|--|

| bit 15 bit 2 bit 3 bit 8 bit 8 bit 8 bit 7 bit 7 bit 9 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 0 bit 1 bit 9 bit 1 bit 9 bit 1 bit 1 bit 9 bit 1 | R/W-x         | R/W-x                                                                    | R/W-x                              | R/W-x               | R/W-x            | R/W-x            | R/W-x           | R/W-x              |  |

| R/W-x       R/W-x       U-0       R/W-x       U-0       R/W-x       R/W-x         SID2       SID1       SID0       -       EXIDE       -       EID17       EID16         bit 7       bit 0         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses       Ignores EXIDE bit.       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       Ignores Extended Identifier bits       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SID10         | SID9                                                                     | SID8                               | SID7                | SID6             | SID5             | SID4            | SID3               |  |

| SID2       SID1       SID0       —       EXIDE       —       EID17       EID16         bit 7       bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 15        |                                                                          |                                    |                     |                  |                  |                 | bit 8              |  |

| SID2       SID1       SID0       —       EXIDE       —       EID17       EID16         bit 7       bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                                                                          |                                    |                     |                  |                  |                 |                    |  |

| bit 7       bit 0         Legend:       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter       x = Bit is unknown         bit 4       Unimplemented: Read as '0'       bit 3       EXIDE: Extended Identifier Enable bit       If MIDE = 1:         1 = Matches only messages with Extended Identifier addresses       0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses       If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'       bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter       1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-x         | R/W-x                                                                    | R/W-x                              | U-0                 | R/W-x            | U-0              | R/W-x           | R/W-x              |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         If MIDE = 0:       Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SID2          | SID1                                                                     | SID0                               | _                   | EXIDE            |                  | EID17           | EID16              |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses       1f MIDE = 0:         Ignores EXIDE bit.       Implemented: Read as '0'         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         a Hossage address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 7         |                                                                          |                                    |                     |                  |                  |                 | bit 0              |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-5       SID<10:0>: Standard Identifier bits       1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '1' to match filter       0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses       1f MIDE = 0:         Ignores EXIDE bit.       Implemented: Read as '0'         bit 2       Unimplemented: Read as '0'         bit 1-0       EID         a Hossage address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |                                                                          |                                    |                     |                  |                  |                 |                    |  |

| -n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknownbit 15-5SID<10:0>: Standard Identifier bits<br>1 = Message address bit, SIDx, must be '1' to match filter<br>0 = Message address bit, SIDx, must be '0' to match filterbit 4Unimplemented: Read as '0'bit 3EXIDE: Extended Identifier Enable bit<br>If MIDE = 1:<br>1 = Matches only messages with Extended Identifier addresses<br>0 = Matches only messages with Standard Identifier addresses<br>If MIDE = 0:<br>Ignores EXIDE bit.bit 2Unimplemented: Read as '0'bit 4Unimplemented: Read as '0'bit 5I = Matches only messages with Standard Identifier addresses<br>1 = Matches only messages with Standard Identifier addresses<br>If MIDE = 0:<br>Ignores EXIDE bit.bit 2Unimplemented: Read as '0'bit 3EIDbit 4Unimplemented: Read as '0'bit 5Unimplemented: Read as '0'bit 6II = Matches only messages with Standard Identifier addresses<br>I = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Legend:       |                                                                          |                                    |                     |                  |                  |                 |                    |  |

| bit 15-5       SID<10:0>: Standard Identifier bits         1 = Message address bit, SIDx, must be '1' to match filter         0 = Message address bit, SIDx, must be '0' to match filter         bit 4       Unimplemented: Read as '0'         bit 3       EXIDE: Extended Identifier Enable bit         If MIDE = 1:       1 = Matches only messages with Extended Identifier addresses         0 = Matches only messages with Standard Identifier addresses         0 = Matches only messages with Standard Identifier addresses         1 f MIDE = 0:         Ignores EXIDE bit.         bit 2       Unimplemented: Read as '0'         bit 1-0       EID<17:16>: Extended Identifier bits         1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R = Readable  | e bit                                                                    | W = Writable                       | bit                 | U = Unimpler     | nented bit, read | d as '0'        |                    |  |