Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

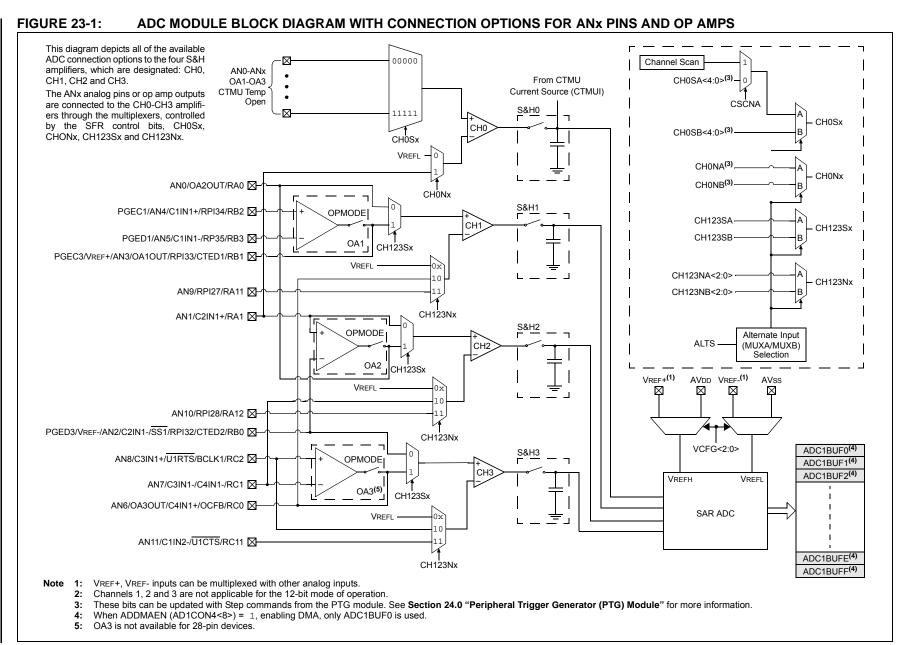

| Data Converters            | A/D 16x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gp506-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

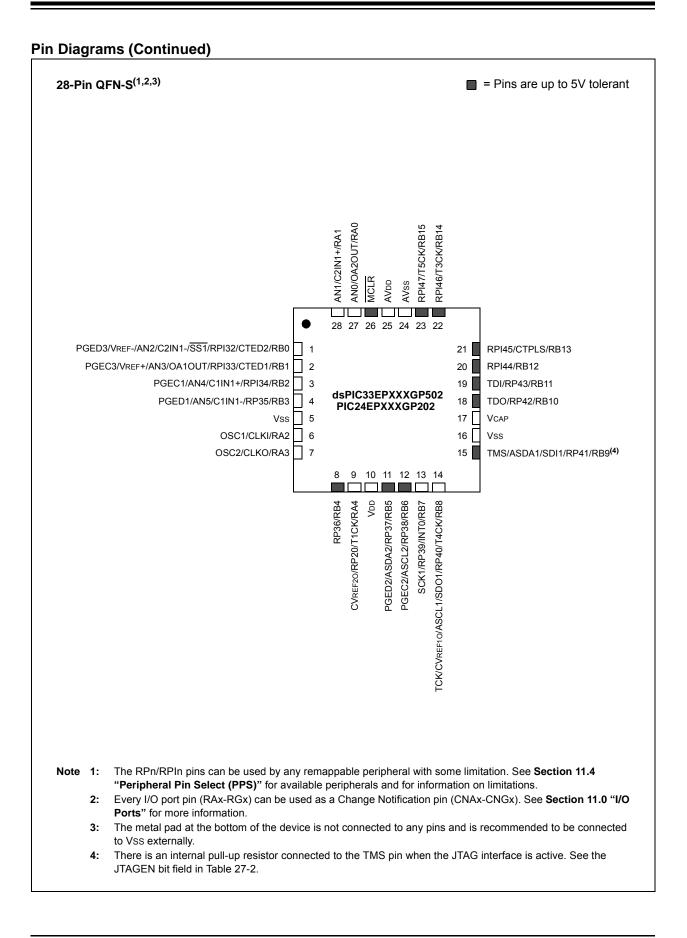

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

### 3.8 Arithmetic Logic Unit (ALU)

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X ALU is 16 bits wide, and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the <u>SR register. The C and DC</u> Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.8.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed, or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

### 3.8.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

## 3.9 DSP Engine (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- · Signed, unsigned or mixed-sign DSP multiply (US)

- · Conventional or convergent rounding (RND)

- · Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

|             | SUMMARY                 |                   |

|-------------|-------------------------|-------------------|

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$           | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

TABLE 3-2: DSP INSTRUCTIONS SUMMARY

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Program Memory" (DS70613) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

## 4.1 Program Address Space

The program address memory space of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in Section 4.8 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space.

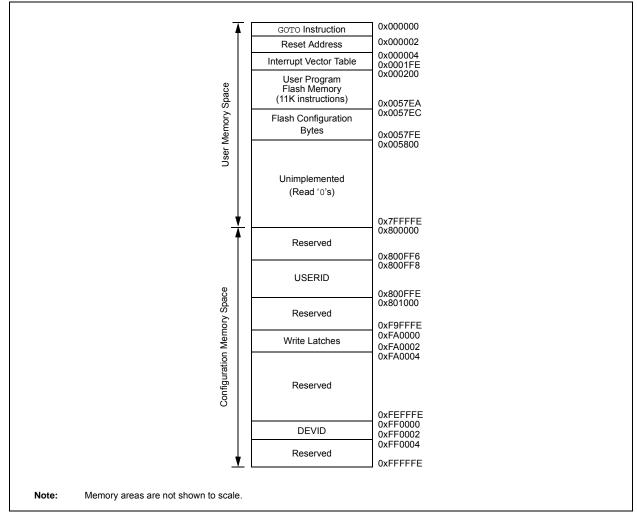

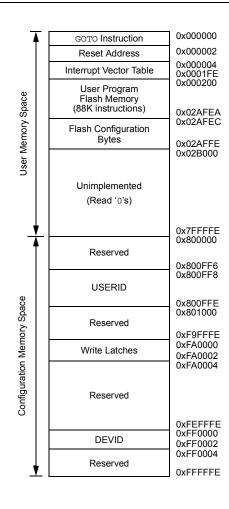

The program memory maps, which are presented by device family and memory size, are shown in Figure 4-1 through Figure 4-5.

# FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EP32GP50X, dsPIC33EP32MC20X/50X AND PIC24EP32GP/MC20X DEVICES

#### FIGURE 4-4: PROGRAM MEMORY MAP FOR dsPIC33EP256GP50X, dsPIC33EP256MC20X/50X AND PIC24EP256GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

# **REGISTER 8-7:** DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | PAD   | <15:8>            |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | PAE   | )<7:0>            |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

#### bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

#### REGISTER 8-8: DMAXCNT: DMA CHANNEL X TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0             | U-0   | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

| —               |       |                  |       | CNT<              | 13:8> <b>(2)</b> |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | CNT<  | <7:0> <b>(2)</b>  |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable b  | oit   | W = Writable b   | bit   | U = Unimplen      | nented bit, rea  | id as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0     | U-0 | U-0   | U-0   | U-0   | U-0   | U-0   | U-0   |

|---------|-----|-------|-------|-------|-------|-------|-------|

| —       | —   | —     | —     | —     | —     | —     | —     |

| bit 15  |     |       |       |       |       |       | bit 8 |

|         |     |       |       |       |       |       |       |

| U-0     | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| —       | —   | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7   |     |       |       |       |       |       | bit 0 |

|         |     |       |       |       |       |       |       |

| Logondi |     |       |       |       |       |       |       |

#### REGISTER 9-4: OSCTUN: FRC OSCILLATOR TUNING REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **TUN<5:0>:** FRC Oscillator Tuning bits 011111 = Maximum frequency deviation of 1.453% (7.477 MHz) 011110 = Center frequency + 1.406% (7.474 MHz) •••• 000001 = Center frequency + 0.047% (7.373 MHz) 000000 = Center frequency (7.37 MHz nominal) 111111 = Center frequency - 0.047% (7.367 MHz) ••• 100001 = Center frequency - 1.453% (7.263 MHz) 100000 = Minimum frequency deviation of -1.5% (7.259 MHz)

### REGISTER 11-15: RPINR37: PERIPHERAL PIN SELECT INPUT REGISTER 37 (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| U-0                | R/W-0                                      | R/W-0                                           | R/W-0                                      | R/W-0                       | R/W-0            | R/W-0           | R/W-0 |

|--------------------|--------------------------------------------|-------------------------------------------------|--------------------------------------------|-----------------------------|------------------|-----------------|-------|

|                    |                                            |                                                 |                                            | SYNCI1R<6:03                | >                |                 |       |

| bit 15             |                                            |                                                 |                                            |                             |                  |                 | bit 8 |

|                    |                                            |                                                 |                                            |                             |                  |                 |       |

| U-0                | U-0                                        | U-0                                             | U-0                                        | U-0                         | U-0              | U-0             | U-0   |

| _                  |                                            |                                                 | —                                          |                             |                  | <u> </u>        | _     |

| bit 7              |                                            |                                                 |                                            |                             |                  |                 | bit 0 |

|                    |                                            |                                                 |                                            |                             |                  |                 |       |

| Legend:            |                                            |                                                 |                                            |                             |                  |                 |       |

| R = Readab         | ole bit                                    | W = Writable                                    | bit                                        | U = Unimplem                | nented bit, read | l as '0'        |       |

| -n = Value a       | it POR                                     | '1' = Bit is set                                |                                            | '0' = Bit is clea           | ared             | x = Bit is unkn | iown  |

|                    |                                            |                                                 |                                            |                             |                  |                 |       |

|                    |                                            |                                                 |                                            |                             |                  |                 |       |

| bit 15             | Unimplemer                                 | nted: Read as '                                 | 0'                                         |                             |                  |                 |       |

| bit 15<br>bit 14-8 | SYNCI1R<6:                                 |                                                 | M Synchroniz                               | zation Input 1 to<br>nbers) | the Correspon    | ding RPn Pin b  | its   |

|                    | SYNCI1R<6:<br>(see Table 11                | <b>0&gt;:</b> Assign PW                         | M Synchroniz selection nur                 |                             | the Correspon    | ding RPn Pin b  | its   |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                             | the Correspon    | ding RPn Pin b  | its   |

|                    | SYNCI1R<6:<br>(see Table 11                | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz selection nur                 |                             | the Correspon    | ding RPn Pin b  | its   |

|                    | SYNCI1R<6:<br>(see Table 11<br>1111001 = I | • <b>0&gt;:</b> Assign PWI<br>I-2 for input pin | M Synchroniz<br>selection nur<br>121<br>P1 |                             | the Correspon    | ding RPn Pin b  | its   |

# 14.2 Input Capture Registers

#### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | —   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 |     | —     |

| bit 15 |     |        |         |         |         |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R/HC/HS-0 | R/HC/HS-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-----------|-----------|-------|-------|-------|

| —     | ICI1  | ICI0  | ICOV      | ICBNE     | ICM2  | ICM1  | ICM0  |

| bit 7 |       |       |           |           |       |       | bit 0 |

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable b  | bit                |

|-------------------|-----------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared      | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture Stop in Idle Control bit                                                                                                              |

|           | 1 = Input capture will Halt in CPU Idle mode                                                                                                                |

|           | 0 = Input capture will continue to operate in CPU Idle mode                                                                                                 |

| bit 12-10 | ICTSEL<2:0>: Input Capture Timer Select bits                                                                                                                |

|           | 111 = Peripheral clock (FP) is the clock source of the ICx                                                                                                  |

|           | 110 = Reserved                                                                                                                                              |

|           | 101 = Reserved                                                                                                                                              |

|           | 100 = T1CLK is the clock source of the ICx (only the synchronous clock is supported)<br>011 = T5CLK is the clock source of the ICx                          |

|           | 010 = T4CLK is the clock source of the ICx                                                                                                                  |

|           | 001 = T2CLK is the clock source of the ICx                                                                                                                  |

|           | 000 = T3CLK is the clock source of the ICx                                                                                                                  |

| bit 9-7   | Unimplemented: Read as '0'                                                                                                                                  |

| bit 6-5   | ICI<1:0>: Number of Captures per Interrupt Select bits (this field is not used if ICM<2:0> = 001 or 111)                                                    |

|           | 11 = Interrupt on every fourth capture event                                                                                                                |

|           | 10 = Interrupt on every third capture event                                                                                                                 |

|           | 01 = Interrupt on every second capture event<br>00 = Interrupt on every capture event                                                                       |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                    |

| bit 4     | 1 = Input capture buffer overflow occurred                                                                                                                  |

|           | 0 = No input capture buffer overflow occurred                                                                                                               |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                                |

|           | 1 = Input capture buffer is not empty, at least one more capture value can be read                                                                          |

|           | 0 = Input capture buffer is empty                                                                                                                           |

| bit 2-0   | ICM<2:0>: Input Capture Mode Select bits                                                                                                                    |

|           | 111 = Input capture functions as interrupt pin only in CPU Sleep and Idle modes (rising edge detect only, all other control bits are not applicable)        |

|           | 110 = Unused (module is disabled)                                                                                                                           |

|           | 101 = Capture mode, every 16th rising edge (Prescaler Capture mode)                                                                                         |

|           | <ul> <li>100 = Capture mode, every 4th rising edge (Prescaler Capture mode)</li> <li>011 = Capture mode, every rising edge (Simple Capture mode)</li> </ul> |

|           | 010 = Capture mode, every falling edge (Simple Capture mode)                                                                                                |

|           | 001 = Capture mode, every edge rising and falling (Edge Detect mode (ICI<1:0>) is not used in this mode)                                                    |

|           | 000 = Input capture module is turned off                                                                                                                    |

### 15.1 Output Compare Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

#### 15.1.1 KEY RESOURCES

- "Output Compare" (DS70358) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER (CONTINUED)

| bit 6-4 | SYNCSRC<2:0>: Synchronous Source Selection bits <sup>(1)</sup><br>111 = Reserved<br>100 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | 100 = Reserved<br>011 = PTGO17 <sup>(2)</sup><br>010 = PTGO16 <sup>(2)</sup><br>001 = Reserved<br>000 = SYNCI1 input from PPS<br>SEVTPS<3:0>: PWMx Special Event Trigger Output Postscaler Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1111 = 1:16 Postscaler generates Special Event Trigger on every sixteenth compare match event</li> <li>.</li> <l< td=""></l<></ul> |

|         | 0000 = 1:1 Postscaler generates Special Event Trigger on every second compare match event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

- **Note 1:** These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user application must program the period register with a value that is slightly larger than the expected period of the external synchronization input signal.

- 2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

#### REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER (CONTINUED)

| bit 7- | 6  | DTC<1:0>: Dead-Time Control bits                                                                                                                                                             |

|--------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |    | 11 = Dead-Time Compensation mode                                                                                                                                                             |

|        |    | 10 = Dead-time function is disabled                                                                                                                                                          |

|        |    | 01 = Negative dead time is actively applied for Complementary Output mode                                                                                                                    |

|        |    | 00 = Positive dead time is actively applied for all output modes                                                                                                                             |

| bit 5  |    | <b>DTCP:</b> Dead-Time Compensation Polarity bit <sup>(3)</sup>                                                                                                                              |

|        |    | When Set to '1':                                                                                                                                                                             |

|        |    | If DTCMPx = 0, PWMxL is shortened and PWMxH is lengthened.<br>If DTCMPx = 1, PWMxH is shortened and PWMxL is lengthened.                                                                     |

|        |    | When Set to '0':                                                                                                                                                                             |

|        |    | If $DTCMPx = 0$ , $PWMxH$ is shortened and $PWMxL$ is lengthened.                                                                                                                            |

|        |    | If DTCMPx = 1, PWMxL is shortened and PWMxH is lengthened.                                                                                                                                   |

| bit 4  |    | Unimplemented: Read as '0'                                                                                                                                                                   |

| bit 3  |    | MTBS: Master Time Base Select bit                                                                                                                                                            |

|        |    | <ul> <li>1 = PWM generator uses the secondary master time base for synchronization and as the clock source<br/>for the PWM generation logic (if secondary time base is available)</li> </ul> |

|        |    | 0 = PWM generator uses the primary master time base for synchronization and as the clock source<br>for the PWM generation logic                                                              |

| bit 2  |    | <b>CAM:</b> Center-Aligned Mode Enable bit <sup>(2,4)</sup>                                                                                                                                  |

|        |    | 1 = Center-Aligned mode is enabled                                                                                                                                                           |

|        |    | 0 = Edge-Aligned mode is enabled                                                                                                                                                             |

| bit 1  |    | XPRES: External PWMx Reset Control bit <sup>(5)</sup>                                                                                                                                        |

|        |    | <ul> <li>1 = Current-limit source resets the time base for this PWM generator if it is in Independent Time Base<br/>mode</li> </ul>                                                          |

|        |    | 0 = External pins do not affect PWMx time base                                                                                                                                               |

| bit 0  |    | IUE: Immediate Update Enable bit <sup>(2)</sup>                                                                                                                                              |

|        |    | 1 = Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are immediate                                                                                                               |

|        |    | <ul> <li>Updates to the active MDC/PDCx/DTRx/ALTDTRx/PHASEx registers are synchronized to the<br/>PWMx period boundary</li> </ul>                                                            |

| Note   | 1: | Software must clear the interrupt status here and in the corresponding IFSx bit in the interrupt controller.                                                                                 |

|        | 2: | These bits should not be changed after the PWMx is enabled (PTEN = 1).                                                                                                                       |

|        | 3: | DTC<1:0> = 11 for DTCP to be effective; otherwise, DTCP is ignored.                                                                                                                          |

|        | 4: | The Independent Time Base (ITB = 1) mode must be enabled to use Center-Aligned mode. If ITB = 0, the CAM bit is ignored.                                                                     |

**5:** To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

# REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER (CONTINUED)

| etching<br>etching                                                                    |

|---------------------------------------------------------------------------------------|

| rating as I <sup>2</sup> C master, applicable during master receive)                  |

| e initiates an Acknowledge sequence.                                                  |

| bit<br>during master receive)                                                         |

| DAx and SCLx pins and transmits ACKDT data bit. Hardware<br>owledge sequence.<br>ress |

| g as I <sup>2</sup> C master)                                                         |

| are is clear at the end of the eighth bit of the master receive                       |

| erating as I <sup>2</sup> C master)                                                   |

| SCLx pins. Hardware is clear at the end of the master Stop                            |

| $\frac{1}{2}$                                                                         |

| it (when operating as I <sup>2</sup> C master)                                        |

| SDAx and SCLx pins. Hardware is clear at the end of the gress                         |

| erating as I <sup>2</sup> C master)                                                   |

| SCLx pins. Hardware is clear at the end of the master Start                           |

|                                                                                       |

**Note 1:** When performing master operations, ensure that the IPMIEN bit is set to '0'.

## 21.2 Modes of Operation

The ECAN module can operate in one of several operation modes selected by the user. These modes include:

- · Initialization mode

- Disable mode

- Normal Operation mode

- · Listen Only mode

- Listen All Messages mode

- Loopback mode

Modes are requested by setting the REQOP<2:0> bits (CxCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CxCTRL1<7:5>). The module does not change the mode and the OPMODEx bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

#### 21.3 ECAN Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 21.3.1 KEY RESOURCES

- "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- · Development Tools

| U-0                     | U-0                                                                | U-0                                | R-0     | R-0              | R-0             | R-0              | R-0     |  |  |

|-------------------------|--------------------------------------------------------------------|------------------------------------|---------|------------------|-----------------|------------------|---------|--|--|

| _                       | _                                                                  |                                    | FILHIT4 | FILHIT3          | FILHIT2         | FILHIT1          | FILHIT0 |  |  |

| bit 15                  | <b>I</b>                                                           |                                    |         |                  |                 |                  | bit 8   |  |  |

|                         |                                                                    |                                    |         |                  |                 |                  |         |  |  |

| U-0                     | R-1                                                                | R-0                                | R-0     | R-0              | R-0             | R-0              | R-0     |  |  |

| _                       | ICODE6                                                             | ICODE5                             | ICODE4  | ICODE3           | ICODE2          | ICODE1           | ICODE0  |  |  |

| bit 7                   |                                                                    |                                    |         |                  |                 |                  | bit     |  |  |

| Logondi                 |                                                                    |                                    |         |                  |                 |                  |         |  |  |

| Legend:<br>R = Readable | - hit                                                              |                                    | hit     | LI – Unimplor    | mented bit, rea | d as '0'         |         |  |  |

| -n = Value at           |                                                                    |                                    |         | '0' = Bit is cle |                 | x = Bit is unkr  |         |  |  |

|                         | FUR                                                                | '1' = Bit is set                   |         |                  |                 | x – Dit is uliki |         |  |  |

| bit 15-13               | Unimplemen                                                         | ted: Read as '                     | 0'      |                  |                 |                  |         |  |  |

| bit 12-8                | =                                                                  | Filter Hit Num                     |         |                  |                 |                  |         |  |  |

|                         |                                                                    | 1 = Reserved                       |         |                  |                 |                  |         |  |  |

|                         | 01111 <b>= Filte</b>                                               | er 15                              |         |                  |                 |                  |         |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                  |         |  |  |

|                         | 00001 = Filte<br>00000 = Filte                                     |                                    |         |                  |                 |                  |         |  |  |

| bit 7                   |                                                                    | ted: Read as '                     | 0'      |                  |                 |                  |         |  |  |

| bit 6-0                 | ICODE<6:0>: Interrupt Flag Code bits                               |                                    |         |                  |                 |                  |         |  |  |

|                         | 1000101-1111111 = Reserved                                         |                                    |         |                  |                 |                  |         |  |  |

|                         |                                                                    | IFO almost full                    |         |                  |                 |                  |         |  |  |

|                         |                                                                    | leceiver overflo                   |         |                  |                 |                  |         |  |  |

|                         | 1000010 = K<br>1000001 = E                                         | Vake-up interru<br>rror interrupt  | μ       |                  |                 |                  |         |  |  |

|                         | 1000000 = N                                                        |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                  |         |  |  |

|                         |                                                                    | 11111 = Rese                       |         |                  |                 |                  |         |  |  |

|                         | •                                                                  | B15 buffer inte                    | inupt   |                  |                 |                  |         |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                  |         |  |  |

|                         | •                                                                  |                                    |         |                  |                 |                  |         |  |  |

|                         | 0001001 <b>= R</b>                                                 | B9 buffer inter                    | rupt    |                  |                 |                  |         |  |  |

|                         |                                                                    | B8 buffer inter                    |         |                  |                 |                  |         |  |  |

|                         |                                                                    | RB7 buffer inte<br>RB6 buffer inte |         |                  |                 |                  |         |  |  |

|                         |                                                                    |                                    |         |                  |                 |                  |         |  |  |

|                         | 0000101 = TRB5 buffer interrupt<br>0000100 = TRB4 buffer interrupt |                                    |         |                  |                 |                  |         |  |  |

|                         | 0000011 <b>= T</b>                                                 | RB3 buffer inte                    | errupt  |                  |                 |                  |         |  |  |

|                         |                                                                    |                                    |         |                  |                 |                  |         |  |  |

|                         |                                                                    | RB2 buffer inte<br>RB1 buffer inte |         |                  |                 |                  |         |  |  |

## REGISTER 21-3: CxVEC: ECANx INTERRUPT CODE REGISTER

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup> (CONTINUED)

| bit 4 | OC1CS: Clock Source for OC1 bit                                                                                                                                                                |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Generates clock pulse when the broadcast command is executed</li> <li>0 = Does not generate clock pulse when the broadcast command is executed</li> </ul>                         |

| bit 3 | OC4TSS: Trigger/Synchronization Source for OC4 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 2 | OC3TSS: Trigger/Synchronization Source for OC3 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 1 | OC2TSS: Trigger/Synchronization Source for OC2 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

| bit 0 | OC1TSS: Trigger/Synchronization Source for OC1 bit                                                                                                                                             |

|       | <ul> <li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> </ul> |

|       |                                                                                                                                                                                                |

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: This register is only used with the PTGCTRL OPTION = 1111 Step command.

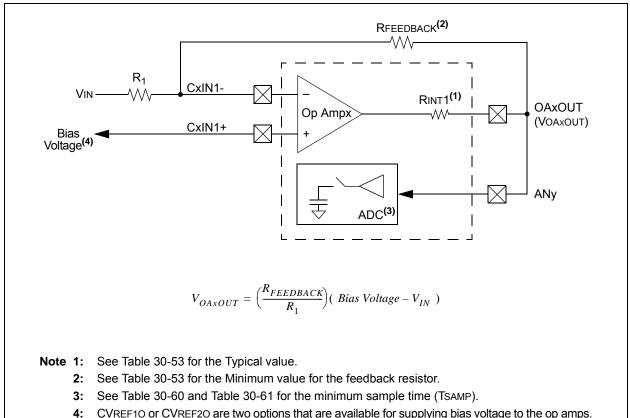

#### 25.1.2 OP AMP CONFIGURATION B

Figure 25-7 shows a typical inverting amplifier circuit with the output of the op amp (OAxOUT) externally routed to a separate analog input pin (ANy) on the device. This op amp configuration is slightly different in terms of the op amp output and the ADC input connection, therefore, RINT1 is not included in the transfer function. However, this configuration requires the designer to externally route the op amp output (OAxOUT) to another analog input pin (ANy). See Table 30-53 in **Section 30.0 "Electrical Characteristics"** for the typical value of RINT1. Table 30-60 and Table 30-61 in **Section 30.0 "Electrical Characteristics"** describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration.

Figure 25-7 also defines the equation to be used to calculate the expected voltage at point VOAxOUT. This is the typical inverting amplifier equation.

## 25.2 Op Amp/Comparator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 25.2.1 KEY RESOURCES

- "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### FIGURE 25-7: OP AMP CONFIGURATION B

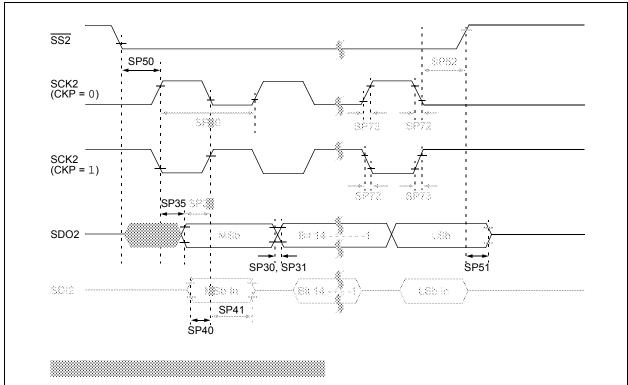

#### FIGURE 30-21: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

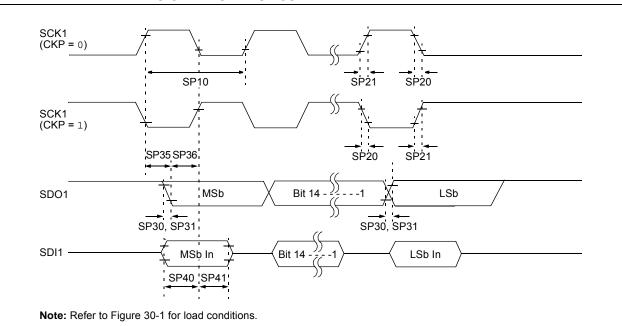

# TABLE 30-44:SPI1 MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                             |

|--------------------|-----------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                                                                                                                                                                                                                                                    | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |

| SP10               | FscP                  | Maximum SCK1 Frequency                        |                                                                                                                                                                                                                                                                                         | —                   | 10   | MHz   | -40°C to +125°C<br>(Note 3) |

| SP20               | TscF                  | SCK1 Output Fall Time                         | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP21               | TscR                  | SCK1 Output Rise Time                         | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP30               | TdoF                  | SDO1 Data Output Fall Time                    | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO32 (Note 4) |

| SP31               | TdoR                  | SDO1 Data Output Rise Time                    | _                                                                                                                                                                                                                                                                                       | —                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge     | _                                                                                                                                                                                                                                                                                       | 6                   | 20   | ns    |                             |

| SP36               | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge  | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                             |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data<br>Input to SCK1 Edge | 30                                                                                                                                                                                                                                                                                      | —                   | _    | ns    |                             |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge     | 30                                                                                                                                                                                                                                                                                      | —                   | —    | ns    |                             |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK1 is 100 ns. The clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPI1 pins.

| Section Name                                                                                              | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Section 16.0 "High-Speed<br>PWM Module<br>(dsPIC33EPXXXMC20X/50X<br>and PIC24EPXXXMC20X<br>Devices Only)" | Figure 16-2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Section 21.0 "Enhanced<br>CAN (ECAN™) Module<br>(dsPIC33EPXXXGP/MC50X<br>Devices Only)"                   | Updated the CANCKS bit value definitions in CiCTRL1: ECAN Control Register 1 (see Register 21-1).                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Section 22.0 "Charge Time<br>Measurement Unit (CTMU)"                                                     | Updated the IRNG<1:0> bit value definitions and added Note 2 in the CTMU Current Control Register (see Register 22-3).                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Section 25.0 "Op amp/<br>Comparator Module"                                                               | Updated the Op amp/Comparator I/O Operating Modes Diagram (see Figure 25-1).<br>Updated the User-programmable Blanking Function Block Diagram (see Figure 25-3).<br>Updated the Digital Filter Interconnect Block Diagram (see Figure 25-4).<br>Added <b>Section 25.1 "Op amp Application Considerations</b> ".<br>Added Note 2 to the Comparator Control Register (see Register 25-2).<br>Updated the bit definitions in the Comparator Mask Gating Control Register (see<br>Register 25-5). |  |  |  |

| Section 27.0 "Special<br>Features"                                                                        | Updated the FICD Configuration Register, updated Note 1, and added Note 3 in the Configuration Byte Register Map (see Table 27-1).<br>Added <b>Section 27.2 "User ID Words"</b> .                                                                                                                                                                                                                                                                                                             |  |  |  |

| Section 30.0 "Electrical<br>Characteristics"                                                              | <ul> <li>Updated the following Absolute Maximum Ratings:</li> <li>Maximum current out of Vss pin</li> <li>Maximum current into VDD pin</li> <li>Added Note 1 to the Operating MIPS vs. Voltage (see Table 30-1).</li> </ul>                                                                                                                                                                                                                                                                   |  |  |  |

|                                                                                                           | Updated all Idle Current (IIDLE) Typical and Maximum DC Characteristics values (see Table 30-7).                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                                                                                                           | Updated all Doze Current (IDOZE) Typical and Maximum DC Characteristics values (see Table 30-9).                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                                                                                                           | Added Note 2, removed Parameter CM24, updated the Typical values Parameters CM10, CM20, CM21, CM32, CM41, CM44, and CM45, and updated the Minimum values for CM40 and CM41, and the Maximum value for CM40 in the AC/DC Characteristics: Op amp/Comparator (see Table 30-14).                                                                                                                                                                                                                 |  |  |  |

|                                                                                                           | Updated Note 2 and the Typical value for Parameter VR310 in the Op amp/<br>Comparator Reference Voltage Settling Time Specifications (see Table 30-15).                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                                                                                           | Added Note 1, removed Parameter VRD312, and added Parameter VRD314 to the Op amp/Comparator Voltage Reference DC Specifications (see Table 30-16).                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                                                                                           | Updated the Minimum, Typical, and Maximum values for Internal LPRC Accuracy (see Table 30-22).                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                                                                                                           | Updated the Minimum, Typical, and Maximum values for Parameter SY37 in the Reset, Watchdog Timer, Oscillator Start-up Timer, Power-up Timer Timing Requirements (see Table 30-24).                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                                                                                           | The Maximum Data Rate values were updated for the SPI2 Maximum Data/Clock Rate Summary (see Table 30-35)                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

## TABLE A-2: MAJOR SECTION UPDATES (CONTINUED)