Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gp506-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.8 Arithmetic Logic Unit (ALU)

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X ALU is 16 bits wide, and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the <u>SR register. The C and DC</u> Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

The core CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.8.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed, or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit signed x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.8.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.9 DSP Engine (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a 40-bit barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The DSP engine can also perform inherent accumulatorto-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- · Signed, unsigned or mixed-sign DSP multiply (US)

- · Conventional or convergent rounding (RND)

- · Automatic saturation on/off for ACCA (SATA)

- Automatic saturation on/off for ACCB (SATB)

- Automatic saturation on/off for writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACCSAT)

|             | SUMMARY                 |                   |

|-------------|-------------------------|-------------------|

| Instruction | Algebraic<br>Operation  | ACC Write<br>Back |

| CLR         | A = 0                   | Yes               |

| ED          | $A = (x - y)^2$         | No                |

| EDAC        | $A = A + (x - y)^2$     | No                |

| MAC         | $A = A + (x \bullet y)$ | Yes               |

| MAC         | $A = A + x^2$           | No                |

| MOVSAC      | No change in A          | Yes               |

| MPY         | $A = x \bullet y$       | No                |

| MPY         | $A = x^2$               | No                |

| MPY.N       | $A = -x \bullet y$      | No                |

| MSC         | $A = A - x \bullet y$   | Yes               |

TABLE 3-2: DSP INSTRUCTIONS SUMMARY

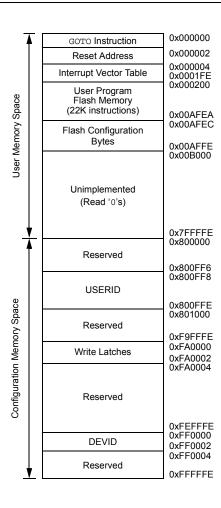

#### FIGURE 4-2: PROGRAM MEMORY MAP FOR dsPIC33EP64GP50X, dsPIC33EP64MC20X/50X AND PIC24EP64GP/MC20X DEVICES

Note: Memory areas are not shown to scale.

| TABLE 4   | 4-9:  | INPUT  |                                     | JRE 1 T | HROUG  | H INPU    | Т САРТ | URE 4 | REGIST       | ER MA        | Р        |       |       |       |          |          |       |               |

|-----------|-------|--------|-------------------------------------|---------|--------|-----------|--------|-------|--------------|--------------|----------|-------|-------|-------|----------|----------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14                              | Bit 13  | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3 | Bit 2    | Bit 1    | Bit 0 | All<br>Resets |

| IC1CON1   | 0140  | _      | —                                   | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | -            | —            | ICI<     | :0>   | ICOV  | ICBNE | ICM<2:0> |          |       | 0000          |

| IC1CON2   | 0142  | _      | _                                   |         | _      |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC1BUF    | 0144  |        |                                     |         |        |           |        | Inp   | ut Capture ' | 1 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC1TMR    | 0146  |        | Input Capture 1 Timer 00            |         |        |           |        |       |              |              |          | 0000  |       |       |          |          |       |               |

| IC2CON1   | 0148  |        | _                                   | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC2CON2   | 014A  |        | IC32 ICTRIG TRIGSTAT - SYNCSEL<4:0> |         |        |           |        |       |              | 000D         |          |       |       |       |          |          |       |               |

| IC2BUF    | 014C  |        |                                     |         |        |           |        | Inp   | ut Capture 2 | 2 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC2TMR    | 014E  |        |                                     |         |        |           |        |       | Input Capt   | ture 2 Time  | r        |       |       |       |          |          |       | 0000          |

| IC3CON1   | 0150  |        | _                                   | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC3CON2   | 0152  |        | _                                   |         |        |           | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC3BUF    | 0154  |        |                                     |         |        |           |        | Inp   | ut Capture 3 | 3 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC3TMR    | 0156  |        |                                     |         |        |           |        |       | Input Capt   | ture 3 Time  | r        |       |       |       |          |          |       | 0000          |

| IC4CON1   | 0158  |        | _                                   | ICSIDL  | 10     | CTSEL<2:0 | >      | —     | _            |              | ICI<1    | :0>   | ICOV  | ICBNE |          | ICM<2:0> |       | 0000          |

| IC4CON2   | 015A  | _      | _                                   |         | -      |           | -      | _     | IC32         | ICTRIG       | TRIGSTAT | -     |       | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC4BUF    | 015C  |        |                                     |         |        |           |        | Inp   | ut Capture 4 | 4 Buffer Reg | gister   |       |       |       |          |          |       | xxxx          |

| IC4TMR    | 015E  |        |                                     |         |        |           |        |       | Input Capt   | ure 4 Time   | r        |       |       |       |          |          |       | 0000          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE 4-2  | TABLE 4-21: ECAN1 REGISTER MAP WHEN WIN (C1CTR1 $<0>$ ) = 0 OR 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY |         |           |         |         |          |            |           |          |              |           |           |         |        |          |          |        |               |

|------------|--------------------------------------------------------------------------------------------------------|---------|-----------|---------|---------|----------|------------|-----------|----------|--------------|-----------|-----------|---------|--------|----------|----------|--------|---------------|

| File Name  | Addr.                                                                                                  | Bit 15  | Bit 14    | Bit 13  | Bit 12  | Bit 11   | Bit 10     | Bit 9     | Bit 8    | Bit 7        | Bit 6     | Bit 5     | Bit 4   | Bit 3  | Bit 2    | Bit 1    | Bit 0  | All<br>Resets |

| C1CTRL1    | 0400                                                                                                   | _       | —         | CSIDL   | ABAT    | CANCKS   | R          | EQOP<2:0  | >        | OPM          | /IODE<2:0 | >         | —       | CANCAP | —        | —        | WIN    | 0480          |

| C1CTRL2    | 0402                                                                                                   | _       | _         | —       | _       | _        | _          | —         | _        | —            | _         | _         |         | D      | NCNT<4:0 | >        |        | 0000          |

| C1VEC      | 0404                                                                                                   | _       | —         | —       |         | F        | ILHIT<4:0> |           |          | — ICODE<6:0> |           |           |         |        | 0040     |          |        |               |

| C1FCTRL    | 0406                                                                                                   | C       | DMABS<2:0 | >       |         | _        | —          | —         | FSA<4:0> |              |           |           |         | 0000   |          |          |        |               |

| C1FIFO     | 0408                                                                                                   |         | —         |         |         | FBP<5:0> |            |           |          | —            | _         | FNRB<5:0> |         |        |          |          | 0000   |               |

| C1INTF     | 040A                                                                                                   |         | —         | TXBO    | TXBP    | RXBP     | TXWAR      | RXWAR     | EWARN    | IVRIF        | WAKIF     | ERRIF     | —       | FIFOIF | RBOVIF   | RBIF     | TBIF   | 0000          |

| C1INTE     | 040C                                                                                                   |         | —         | —       |         | _        | —          | —         | _        | IVRIE        | WAKIE     | ERRIE     | —       | FIFOIE | RBOVIE   | RBIE     | TBIE   | 0000          |

| C1EC       | 040E                                                                                                   |         |           |         | TERRCN  | T<7:0>   |            |           |          | RERRCNT<7:0> |           |           |         |        |          |          | 0000   |               |

| C1CFG1     | 0410                                                                                                   | _       | _         | _       | _       | _        | _          | _         | _        | SJW<1        | :0>       |           |         | BRP    | <5:0>    |          |        | 0000          |

| C1CFG2     | 0412                                                                                                   | _       | WAKFIL    | _       | _       | _        | SI         | =G2PH<2:( | )>       | SEG2PHTS     | SAM       | S         | EG1PH<2 | :0>    | P        | RSEG<2:0 | >      | 0000          |

| C1FEN1     | 0414                                                                                                   | FLTEN15 | FLTEN14   | FLTEN13 | FLTEN12 | FLTEN11  | FLTEN10    | FLTEN9    | FLTEN8   | FLTEN7       | FLTEN6    | FLTEN5    | FLTEN4  | FLTEN3 | FLTEN2   | FLTEN1   | FLTEN0 | FFFF          |

| C1FMSKSEL1 | 0418                                                                                                   | F7MSł   | <<1:0>    | F6MSł   | <<1:0>  | F5MS     | K<1:0>     | F4MS      | K<1:0>   | F3MSK<       | <1:0>     | F2MS      | K<1:0>  | F1MSH  | <<1:0>   | F0MS     | <<1:0> | 0000          |

| C1FMSKSEL2 | 041A                                                                                                   | F15MS   | K<1:0>    | F14MS   | K<1:0>  | F13MS    | K<1:0>     | F12MS     | K<1:0>   | F11MSK       | <1:0>     | F10MS     | K<1:0>  | F9MSk  | <<1:0>   | F8MSI    | <<1:0> | 0000          |

#### TABLE 4-21: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 OR 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-22: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

| File Name | Addr          | Bit 15                      | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8      | Bit 7        | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|---------------|-----------------------------|---------|---------|---------|---------|---------|---------|------------|--------------|---------|---------|---------|---------|---------|---------|---------|---------------|

|           | 0400-<br>041E | See definition when WIN = x |         |         |         |         |         |         |            |              |         |         |         |         |         |         |         |               |

| C1RXFUL1  | 0420          | RXFUL15                     | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9  | RXFUL8     | RXFUL7       | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C1RXFUL2  | 0422          | RXFUL31                     | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24    | RXFUL23      | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C1RXOVF1  | 0428          | RXOVF15                     | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9  | RXOVF8     | RXOVF7       | RXOVF6  | RXOVF5  | RXOVF4  | RXOVF3  | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C1RXOVF2  | 042A          | RXOVF31                     | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24    | RXOVF23      | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 | 0000          |

| C1TR01CON | 0430          | TXEN1                       | TXABT1  | TXLARB1 | TXERR1  | TXREQ1  | RTREN1  | TX1PF   | RI<1:0>    | TXEN0        | TXABAT0 | TXLARB0 | TXERR0  | TXREQ0  | RTREN0  | TX0PF   | RI<1:0> | 0000          |

| C1TR23CON | 0432          | TXEN3                       | TXABT3  | TXLARB3 | TXERR3  | TXREQ3  | RTREN3  | TX3PF   | RI<1:0>    | TXEN2        | TXABAT2 | TXLARB2 | TXERR2  | TXREQ2  | RTREN2  | TX2PF   | RI<1:0> | 0000          |

| C1TR45CON | 0434          | TXEN5                       | TXABT5  | TXLARB5 | TXERR5  | TXREQ5  | RTREN5  | TX5PF   | RI<1:0>    | TXEN4        | TXABAT4 | TXLARB4 | TXERR4  | TXREQ4  | RTREN4  | TX4PF   | RI<1:0> | 0000          |

| C1TR67CON | 0436          | TXEN7                       | TXABT7  | TXLARB7 | TXERR7  | TXREQ7  | RTREN7  | TX7PF   | RI<1:0>    | TXEN6        | TXABAT6 | TXLARB6 | TXERR6  | TXREQ6  | RTREN6  | TX6PF   | RI<1:0> | xxxx          |

| C1RXD     | 0440          |                             |         |         |         |         |         | E       | CAN1 Rece  | eive Data Wo | ord     |         |         |         |         |         |         | xxxx          |

| C1TXD     | 0442          |                             |         |         |         |         |         | E       | CAN1 Trans | smit Data Wo | ord     |         |         |         |         |         |         | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|--------------|----------------------------------------------------------|---------------|-------------------|-----------------|-----------------|-------|

| —            |              |                                                          |               | IC4R<6:0>         |                 |                 |       |

| bit 15       |              |                                                          |               |                   |                 |                 | bit 8 |

|              |              |                                                          |               |                   |                 |                 |       |

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |              |                                                          |               | IC3R<6:0>         |                 |                 |       |

| bit 7        |              |                                                          |               |                   |                 |                 | bit C |

|              |              |                                                          |               |                   |                 |                 |       |

| Legend:      |              |                                                          |               |                   |                 |                 |       |

| R = Readab   | ole bit      | W = Writable I                                           | bit           | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value a | at POR       | '1' = Bit is set                                         |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 0000001 =    | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss | ⊃1            |                   |                 |                 |       |

| bit 7        | Unimpleme    | nted: Read as 'o                                         | )'            |                   |                 |                 |       |

| bit 6-0      | (see Table 1 | Assign Input Ca<br>1-2 for input pin<br>nput tied to RPI | selection nun |                   | onding RPn Pi   | n bits          |       |

#### REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

#### 12.1 Timer1 Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 12.1.1 KEY RESOURCES

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

| U-0    | U-0   | U-0   | U-0   | U-0   | U-0   | R/W-0 | R/W-0 |

|--------|-------|-------|-------|-------|-------|-------|-------|

| —      | —     | —     | —     | —     | —     | AMSK9 | AMSK8 |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| AMSK7  | AMSK6 | AMSK5 | AMSK4 | AMSK3 | AMSK2 | AMSK1 | AMSK0 |

| bit 7  |       |       |       |       |       |       | bit 0 |

#### REGISTER 19-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSK<9:0>: Address Mask Select bits

For 10-Bit Address:

1 = Enables masking for bit Ax of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax; bit match is required in this position

For 7-Bit Address (I2CxMSK<6:0> only):

1 = Enables masking for bit Ax + 1 of incoming message address; bit match is not required in this position

0 = Disables masking for bit Ax + 1; bit match is required in this position

| R-0 | R-0              | R-0                          | R-0                                                | R-0                                                                                            | R-0                                                                                       | R-0                                                                                                                  |  |  |

|-----|------------------|------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|--|

|     |                  | TERR                         | CNT<7:0>                                           |                                                                                                |                                                                                           |                                                                                                                      |  |  |

|     |                  |                              |                                                    |                                                                                                |                                                                                           | bit 8                                                                                                                |  |  |

|     |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |  |  |

| R-0 | R-0              | R-0                          | R-0                                                | R-0                                                                                            | R-0                                                                                       | R-0                                                                                                                  |  |  |

|     |                  | RERR                         | CNT<7:0>                                           |                                                                                                |                                                                                           |                                                                                                                      |  |  |

|     |                  |                              |                                                    |                                                                                                |                                                                                           | bit 0                                                                                                                |  |  |

|     |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |  |  |

|     |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |  |  |

| oit | W = Writable b   | it                           | U = Unimplemented bit, read as '0'                 |                                                                                                |                                                                                           |                                                                                                                      |  |  |

| OR  | '1' = Bit is set |                              | '0' = Bit is cleared x = Bit is unknown            |                                                                                                |                                                                                           |                                                                                                                      |  |  |

|     | R-0              | R-0 R-0<br>it W = Writable b | TERR<br>R-0 R-0 R-0<br>RERR<br>it W = Writable bit | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         RERRCNT<7:0> | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         RERRCNT | TERRCNT<7:0>         R-0       R-0       R-0       R-0         RERRCNT<7:0>       U = Unimplemented bit, read as '0' |  |  |

bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

#### REGISTER 21-9: CxCFG1: ECANx BAUD RATE CONFIGURATION REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SJW1  | SJW0  | BRP5  | BRP4  | BRP3  | BRP2  | BRP1  | BRP0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

| bit 7-6 | SJW<1:0>: Synchronization Jump Width bits    |

|---------|----------------------------------------------|

|         | 11 = Length is 4 x TQ                        |

|         | $10 = \text{Length is } 3 \times \text{Tq}$  |

|         | $01 = \text{Length is } 2 \times \text{T} Q$ |

|         | $00 = \text{Length is } 1 \times \text{Tq}$  |

```

bit 5-0 BRP<5:0>: Baud Rate Prescaler bits

```

```

11 1111 = TQ = 2 x 64 x 1/FCAN

```

•

- 00 0010 = TQ = 2 x 3 x 1/FCAN 00 0001 = TQ = 2 x 2 x 1/FCAN

- 00 0000 = Tq = 2 x 1 x 1/FCAN

#### FIGURE 22-1: CTMU BLOCK DIAGRAM

5: The switch connected to ADC CH0 is closed when IDISSEN (CTMUCON1<9>) = 1, and opened when IDISSEN = 0.

#### 22.1 CTMU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 22.1.1 KEY RESOURCES

- "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

## 23.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- **Note 1:** This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. То complement the information in this data sheet. refer to "Analog-to-Digital Converter (ADC)" (DS70621) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have one ADC module. The ADC module supports up to 16 analog input channels.

On ADC1, the AD12B bit (AD1CON1<10>) allows the ADC module to be configured by the user as either a 10-bit, 4 Sample-and-Hold (S&H) ADC (default configuration) or a 12-bit, 1 S&H ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

## 23.1 Key Features

#### 23.1.1 10-BIT ADC CONFIGURATION

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- · Conversion speeds of up to 1.1 Msps

- · Up to 16 analog input pins

- Connections to three internal op amps

- Connections to the Charge Time Measurement Unit (CTMU) and temperature measurement diode

- Channel selection and triggering can be controlled by the Peripheral Trigger Generator (PTG)

- External voltage reference input pins

- · Simultaneous sampling of:

- Up to four analog input pins

- Three op amp outputs

- Combinations of analog inputs and op amp outputs

- Automatic Channel Scan mode

- Selectable conversion Trigger source

- · Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle modes

#### 23.1.2 12-BIT ADC CONFIGURATION

The 12-bit ADC configuration supports all the features listed above, with the exception of the following:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one S&H amplifier in the 12-bit configuration; therefore, simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 16 analog input pins, designated AN0 through AN15. These analog inputs are shared with op amp inputs and outputs, comparator inputs, and external voltage references. When op amp/comparator functionality is enabled, or an external voltage reference is used, the analog input that shares that pin is no longer available. The actual number of analog input pins, op amps and external voltage reference input configuration depends on the specific device.

A block diagram of the ADC module is shown in Figure 23-1. Figure 23-2 provides a diagram of the ADC conversion clock period.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 24-4: PTGT0LIM: PTG TIMER0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|--------------------------------------|------------------------------------|-------|-------|-------|

|                                    |       |       | PTGT0L                               | _IM<15:8>                          |       |       |       |

| bit 15                             |       |       |                                      |                                    |       |       | bit 8 |

|                                    |       |       |                                      |                                    |       |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                                | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |

|                                    |       |       | PTGT0                                | LIM<7:0>                           |       |       |       |

| bit 7                              |       |       |                                      |                                    |       |       | bit 0 |

|                                    |       |       |                                      |                                    |       |       |       |

| Legend:                            |       |       |                                      |                                    |       |       |       |

| R = Readable bit W = Writable bit  |       |       | bit                                  | U = Unimplemented bit, read as '0' |       |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cleared x = Bit is unkn |                                    | nown  |       |       |

#### bit 15-0 **PTGT0LIM<15:0>:** PTG Timer0 Limit Register bits General Purpose Timer0 Limit register (effective only with a PTGT0 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

## REGISTER 24-5: PTGT1LIM: PTG TIMER1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0   | R/W-0   | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|---------|---------|-------|-------|-------|

|        |       |       | PTGT1LI | M<15:8> |       |       |       |

| bit 15 |       |       |         |         |       |       | bit 8 |

|        |       |       |         |         |       |       |       |

| R/W-0 | R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|---------------|-------|-------|-------|-------|-------|-------|

|       | PTGT1LIM<7:0> |       |       |       |       |       |       |

| bit 7 |               |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 **PTGT1LIM<15:0>:** PTG Timer1 Limit Register bits

General Purpose Timer1 Limit register (effective only with a PTGT1 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

# REGISTER 25-5: CMxMSKCON: COMPARATOR x MASK GATING CONTROL REGISTER (CONTINUED)

bit 3 ABEN: AND Gate B Input Enable bit 1 = MBI is connected to AND gate 0 = MBI is not connected to AND gate bit 2 ABNEN: AND Gate B Input Inverted Enable bit 1 = Inverted MBI is connected to AND gate 0 = Inverted MBI is not connected to AND gate bit 1 AAEN: AND Gate A Input Enable bit 1 = MAI is connected to AND gate 0 = MAI is not connected to AND gate bit 0 AANEN: AND Gate A Input Inverted Enable bit 1 = Inverted MAI is connected to AND gate 0 = Inverted MAI is not connected to AND gate

| U-0                                  | U-0                                                          | U-0              | R/W-0   | R/W-0                              | R/W-0   | R/W-0           | R/W-0         |  |

|--------------------------------------|--------------------------------------------------------------|------------------|---------|------------------------------------|---------|-----------------|---------------|--|

| _                                    | —                                                            | —                | DWIDTH4 | DWIDTH3                            | DWIDTH2 | DWIDTH1         | DWIDTH0       |  |

| bit 15                               |                                                              |                  |         |                                    |         |                 | bit 8         |  |

|                                      |                                                              |                  |         |                                    |         |                 |               |  |

| U-0                                  | U-0                                                          | U-0              | R/W-0   | R/W-0                              | R/W-0   | R/W-0           | R/W-0         |  |

| —                                    | —                                                            | —                | PLEN4   | PLEN3                              | PLEN2   | PLEN1           | PLEN0         |  |

| bit 7                                |                                                              |                  |         |                                    |         |                 | bit 0         |  |

|                                      |                                                              |                  |         |                                    |         |                 |               |  |

| Legend:                              |                                                              |                  |         |                                    |         |                 |               |  |

| R = Readable                         | e bit                                                        | W = Writable     | bit     | U = Unimplemented bit, read as '0' |         |                 |               |  |

| -n = Value at                        | POR                                                          | '1' = Bit is set |         | '0' = Bit is cle                   | ared    | x = Bit is unkr | it is unknown |  |

|                                      |                                                              |                  |         |                                    |         |                 |               |  |

| bit 15-13 Unimplemented: Read as '0' |                                                              |                  |         |                                    |         |                 |               |  |

| bit 12-8                             | 12-8 DWIDTH<4:0>: Data Width Select bits                     |                  |         |                                    |         |                 |               |  |

|                                      | These bits set the width of the data word (DWIDTH<4:0> + 1). |                  |         |                                    |         |                 |               |  |

| bit 7-5                              | Unimplemented: Read as '0'                                   |                  |         |                                    |         |                 |               |  |

|                                      |                                                              |                  |         |                                    |         |                 |               |  |

#### REGISTER 26-2: CRCCON2: CRC CONTROL REGISTER 2

bit 4-0 **PLEN<4:0>:** Polynomial Length Select bits

These bits set the length of the polynomial (Polynomial Length = PLEN<4:0> + 1).

| Bit Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCP                    | General Segment Code-Protect bit<br>1 = User program memory is not code-protected<br>0 = Code protection is enabled for the entire program memory space                                                                                                                                                                                                                                                                                     |

| GWRP                   | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                                                           |

| IESO                   | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Start up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start up device with user-selected oscillator source</li> </ul>                                                                                                                                                                                           |

| PWMLOCK <sup>(1)</sup> | PWM Lock Enable bit<br>1 = Certain PWM registers may only be written after a key sequence<br>0 = PWM registers may be written without a key sequence                                                                                                                                                                                                                                                                                        |

| FNOSC<2:0>             | Oscillator Selection bits<br>111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)<br>110 = Fast RC Oscillator with Divide-by-16 (FRCDIV16)<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved; do not use<br>011 = Primary Oscillator with PLL module (XT + PLL, HS + PLL, EC + PLL)<br>010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator with Divide-by-N with PLL module (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |

| FCKSM<1:0>             | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                                           |

| IOL1WAY                | Peripheral Pin Select Configuration bit<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                                                        |

| OSCIOFNC               | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is the clock output<br>0 = OSC2 is a general purpose digital I/O pin                                                                                                                                                                                                                                                                                                          |

| POSCMD<1:0>            | Primary Oscillator Mode Select bits<br>11 = Primary Oscillator is disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                                                           |

| FWDTEN                 | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled. Clearing the SWDTEN bit in the RCON register will have no effect.)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                                                                                                 |

| WINDIS                 | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                                                                              |

| PLLKEN                 | PLL Lock Enable bit<br>1 = PLL lock is enabled<br>0 = PLL lock is disabled<br>nly available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.                                                                                                                                                                                                                                                                                           |

#### TABLE 27-2: CONFIGURATION BITS DESCRIPTION

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

2: When JTAGEN = 1, an internal pull-up resistor is enabled on the TMS pin. Erased devices default to JTAGEN = 1. Applications requiring I/O pins in a high-impedance state (tri-state) in Reset should use pins other than TMS for this purpose.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| DC CHARACTERISTICS                     |      |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |            |      |         |  |  |

|----------------------------------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|---------|--|--|

| Parameter<br>No.                       | Тур. | Max. | Units                                                                                                                                                                                                                                                                                   | Conditions |      |         |  |  |

| Operating Current (IDD) <sup>(1)</sup> |      |      |                                                                                                                                                                                                                                                                                         |            |      |         |  |  |

| DC20d                                  | 9    | 15   | mA                                                                                                                                                                                                                                                                                      | -40°C      |      |         |  |  |

| DC20a                                  | 9    | 15   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V | 10 MIPS |  |  |

| DC20b                                  | 9    | 15   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V |         |  |  |

| DC20c                                  | 9    | 15   | mA                                                                                                                                                                                                                                                                                      | +125°C     |      |         |  |  |

| DC22d                                  | 16   | 25   | mA                                                                                                                                                                                                                                                                                      | -40°C      |      | 20 MIPS |  |  |

| DC22a                                  | 16   | 25   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3∨ |         |  |  |

| DC22b                                  | 16   | 25   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V |         |  |  |

| DC22c                                  | 16   | 25   | mA                                                                                                                                                                                                                                                                                      | +125°C     |      |         |  |  |

| DC24d                                  | 27   | 40   | mA                                                                                                                                                                                                                                                                                      | -40°C      |      | 40 MIPS |  |  |

| DC24a                                  | 27   | 40   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V |         |  |  |

| DC24b                                  | 27   | 40   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V |         |  |  |

| DC24c                                  | 27   | 40   | mA                                                                                                                                                                                                                                                                                      | +125°C     |      |         |  |  |

| DC25d                                  | 36   | 55   | mA                                                                                                                                                                                                                                                                                      | -40°C      |      | 60 MIPS |  |  |

| DC25a                                  | 36   | 55   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V |         |  |  |

| DC25b                                  | 36   | 55   | mA                                                                                                                                                                                                                                                                                      | +85°C      | 3.3V |         |  |  |

| DC25c                                  | 36   | 55   | mA                                                                                                                                                                                                                                                                                      | +125°C     | 7    |         |  |  |

| DC26d                                  | 41   | 60   | mA                                                                                                                                                                                                                                                                                      | -40°C      |      |         |  |  |

| DC26a                                  | 41   | 60   | mA                                                                                                                                                                                                                                                                                      | +25°C      | 3.3V | 70 MIPS |  |  |

| DC26b                                  | 41   | 60   | mA                                                                                                                                                                                                                                                                                      | +85°C      |      |         |  |  |

#### TABLE 30-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

• Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) {NOP(); } statement

- · JTAG is disabled

| DC CHARACTER  | ISTICS |      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |        |      |  |  |  |

|---------------|--------|------|-------------------------------------------------------|--------|------|--|--|--|

| Parameter No. | Тур.   | Max. | Units Conditions                                      |        |      |  |  |  |

| DC61d         | 8      |      | μΑ                                                    | -40°C  |      |  |  |  |

| DC61a         | 10     | —    | μA                                                    | +25°C  | 3.3V |  |  |  |

| DC61b         | 12     | —    | μA                                                    | +85°C  | 3.3V |  |  |  |

| DC61c         | 13     | —    | μA                                                    | +125°C |      |  |  |  |

#### TABLE 30-9: DC CHARACTERISTICS: WATCHDOG TIMER DELTA CURRENT ( $\Delta$ Iwdt)<sup>(1)</sup>

**Note 1:** The  $\triangle$ IwDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

#### TABLE 30-10: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTER                        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |       |            |    |        |       |                |  |

|-------------------------------------|-------------------------------------------------------|-------|------------|----|--------|-------|----------------|--|

| Parameter No.                       | Doze<br>Ratio                                         | Units | Conditions |    |        |       |                |  |

| Doze Current (IDOZE) <sup>(1)</sup> |                                                       |       |            |    |        |       |                |  |

| DC73a <sup>(2)</sup>                | 35                                                    |       | 1:2        | mA | -40°C  | 3.3V  | Fosc = 140 MHz |  |

| DC73g                               | 20                                                    | 30    | 1:128      | mA | -40 C  |       |                |  |

| DC70a <sup>(2)</sup>                | 35                                                    | _     | 1:2        | mA | +25°C  | 3.3V  | Fosc = 140 MHz |  |

| DC70g                               | 20                                                    | 30    | 1:128      | mA | +25 C  |       |                |  |

| DC71a <sup>(2)</sup>                | 35                                                    | —     | 1:2        | mA | 195%   | 2 2)/ |                |  |

| DC71g                               | 20                                                    | 30    | 1:128      | mA | +85°C  | 3.3V  | Fosc = 140 MHz |  |

| DC72a <sup>(2)</sup>                | 28                                                    | —     | 1:2        | mA | +125°C | 3.3V  | Fosc = 120 MHz |  |

| DC72g                               | 15                                                    | 30    | 1:128      | mA | +125 C |       |                |  |

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) statement

- · JTAG is disabled

- 2: Parameter is characterized but not tested in manufacturing.

| DC CHARACTERISTICS |        |                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |      |      |       |                                                                                                                                               |  |

|--------------------|--------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Symbol Characteristic                   |                                                                                                                                                                                                                                                                                       | Тур. | Max. | Units | Conditions                                                                                                                                    |  |

|                    | liL    | Input Leakage Current <sup>(1,2)</sup>  |                                                                                                                                                                                                                                                                                       |      |      |       |                                                                                                                                               |  |

| DI50               |        | I/O Pins 5V Tolerant <sup>(3)</sup>     | -1                                                                                                                                                                                                                                                                                    | —    | +1   | μA    | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in at high-impedance} \end{split}$                         |  |

| DI51               |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                                                                                                                                                                                                                                                    | _    | +1   | μA    | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ Pin \text{ at high-impedance}, \\ -40^\circC \leq TA \leq +85^\circC \end{array}$ |  |

| DI51a              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                                                                                                                                                                                                                                                    | _    | +1   | μA    | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +85^{\circ}C$                                                 |  |

| DI51b              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                                                                                                                                                                                                                                                    | _    | +1   | μA    | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance,<br>-40°C ≤ TA ≤ +125°C                                                                      |  |

| DI51c              |        | I/O Pins Not 5V Tolerant <sup>(3)</sup> | -1                                                                                                                                                                                                                                                                                    | _    | +1   | μA    | Analog pins shared with<br>external reference pins,<br>$-40^{\circ}C \le TA \le +125^{\circ}C$                                                |  |

| DI55               |        | MCLR                                    | -5                                                                                                                                                                                                                                                                                    | —    | +5   | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                                                                                                      |  |

| DI56               |        | OSC1                                    | -5                                                                                                                                                                                                                                                                                    | —    | +5   | μΑ    | $\label{eq:VSS} \begin{array}{l} VSS \leq VPIN \leq VDD, \\ XT \text{ and } HS \text{ modes} \end{array}$                                     |  |

#### TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

- 4: VIL source < (Vss 0.3). Characterized but not tested.

- **5:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

| AC CHARACTERISTICS |           |                                                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                                                                                                             |  |  |

|--------------------|-----------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-------------------------------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                  | Min.                                                                                                                                                                                                                                                                                    | Тур. <sup>(2)</sup> | Max. | Units | Conditions                                                                                                  |  |  |

| SY00               | Τρυ       | Power-up Period                                                | _                                                                                                                                                                                                                                                                                       | 400                 | 600  | μS    |                                                                                                             |  |  |

| SY10               | Tost      | Oscillator Start-up Time                                       |                                                                                                                                                                                                                                                                                         | 1024 Tosc           |      |       | Tosc = OSC1 period                                                                                          |  |  |

| SY12 Twdt          |           | Watchdog Timer<br>Time-out Period                              | 0.81                                                                                                                                                                                                                                                                                    | 0.98                | 1.22 | ms    | WDTPRE = 0,<br>WDTPOST<3:0> = 0000, using<br>LPRC tolerances indicated in F21<br>(see Table 30-20) at +85°C |  |  |

|                    |           |                                                                | 3.26                                                                                                                                                                                                                                                                                    | 3.91                | 4.88 | ms    | WDTPRE = 1,<br>WDTPOST<3:0> = 0000, using<br>LPRC tolerances indicated in F21<br>(see Table 30-20) at +85°C |  |  |

| SY13               | Tioz      | I/O High-Impedance<br>from MCLR Low or<br>Watchdog Timer Reset | 0.68                                                                                                                                                                                                                                                                                    | 0.72                | 1.2  | μS    |                                                                                                             |  |  |

| SY20               | TMCLR     | MCLR Pulse Width (low)                                         | 2                                                                                                                                                                                                                                                                                       | _                   |      | μS    |                                                                                                             |  |  |