Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 16                                                                         |

| /oltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gp506-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

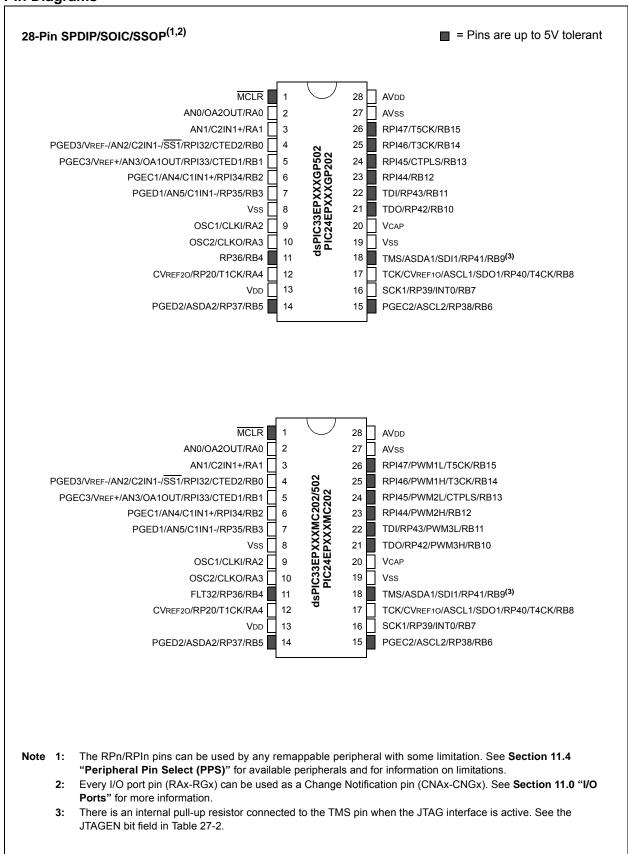

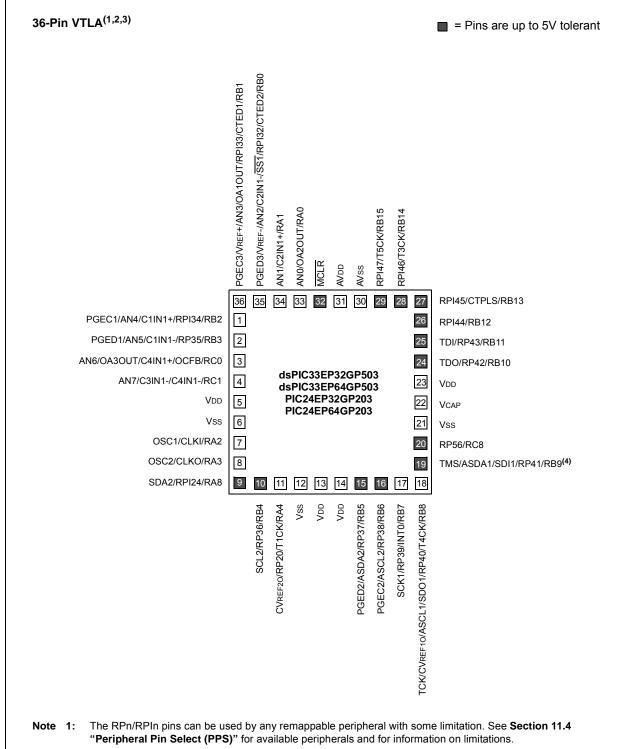

#### Pin Diagrams (Continued)

- 2: Every I/O port pin (RAx-RGx) can be used as a Change Notification pin (CNAx-CNGx). See **Section 11.0 "I/O Ports"** for more information.

- 3: The metal pad at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

- **4:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

#### **Table of Contents**

| 1.0   | Device Overview                                                                                    | 25  |

|-------|----------------------------------------------------------------------------------------------------|-----|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers and Microcontrollers         | 29  |

| 3.0   | CPU                                                                                                | 35  |

| 4.0   | Memory Organization                                                                                | 45  |

| 5.0   | Flash Program Memory                                                                               | 119 |

| 6.0   | Resets                                                                                             | 123 |

| 7.0   | Interrupt Controller                                                                               | 127 |

| 8.0   | Direct Memory Access (DMA)                                                                         | 139 |

| 9.0   | Oscillator Configuration                                                                           | 153 |

| 10.0  | Power-Saving Features                                                                              | 163 |

| 11.0  | I/O Ports                                                                                          | 173 |

| 12.0  | Timer1                                                                                             | 203 |

| 13.0  | Timer2/3 and Timer4/5                                                                              | 207 |

| 14.0  | Input Capture                                                                                      | 213 |

|       | Output Compare                                                                                     |     |

| 16.0  | High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)                     | 225 |

| 17.0  | Quadrature Encoder Interface (QEI) Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only) | 249 |

|       | Serial Peripheral Interface (SPI)                                                                  |     |

| 19.0  | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                                                      | 273 |

| 20.0  | Universal Asynchronous Receiver Transmitter (UART)                                                 | 281 |

| 21.0  | Enhanced CAN (ECAN™) Module (dsPIC33EPXXXGP/MC50X Devices Only)                                    | 287 |

| 22.0  | Charge Time Measurement Unit (CTMU)                                                                | 315 |

| 23.0  | 10-Bit/12-Bit Analog-to-Digital Converter (ADC)                                                    | 321 |

| 24.0  | Peripheral Trigger Generator (PTG) Module                                                          | 337 |

|       | Op Amp/Comparator Module                                                                           |     |

| 26.0  | Programmable Cyclic Redundancy Check (CRC) Generator                                               | 373 |

| 27.0  | Special Features                                                                                   | 379 |

| 28.0  | Instruction Set Summary                                                                            | 387 |

| 29.0  | Development Support                                                                                | 397 |

| 30.0  | Electrical Characteristics                                                                         | 401 |

| 31.0  | High-Temperature Electrical Characteristics                                                        | 467 |

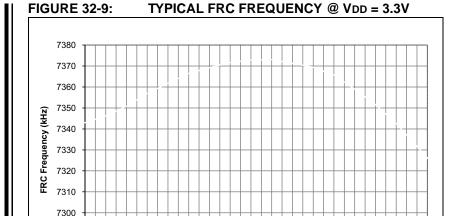

| 32.0  | DC and AC Device Characteristics Graphs                                                            | 475 |

| 33.0  | Packaging Information                                                                              | 479 |

|       | endix A: Revision History                                                                          |     |

| Index | X                                                                                                  | 517 |

| The I | Microchip Web Site                                                                                 | 525 |

| Cust  | omer Change Notification Service                                                                   | 525 |

| Cust  | omer Support                                                                                       | 525 |

| Prod  | uct Identification System                                                                          | 527 |

| Ō          |

|------------|

| 7          |

| 0          |

| Ō          |

| Ō          |

| Ō          |

| Ō          |

| ĆΉ         |

| ₹i         |

|            |

| _          |

| $\tau$     |

| Ö          |

| $\approx$  |

| 'n         |

| മ          |

| ī          |

| 10         |

| $\sim$     |

| CH.        |

| $^{\circ}$ |

|            |

|            |

#### **TABLE 4-8: TIMER1 THROUGH TIMER5 REGISTER MAP**

| SFR<br>Name | Addr. | Bit 15 | Bit 14                                                          | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8       | Bit 7         | Bit 6        | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------|--------|-----------------------------------------------------------------|--------|--------|--------|--------|--------------|-------------|---------------|--------------|-------|--------|-------|-------|-------|-------|---------------|

| TMR1        | 0100  |        |                                                                 |        |        |        |        |              | Timer1      | Register      |              |       |        |       |       |       |       | xxxx          |

| PR1         | 0102  |        |                                                                 |        |        |        |        |              | Period F    | Register 1    |              |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104  | TON    | _                                                               | TSIDL  | _      | _      | _      | _            | _           | _             | TGATE        | TCKPS | S<1:0> | _     | TSYNC | TCS   | _     | 0000          |

| TMR2        | 0106  |        | Timer2 Register xxxx                                            |        |        |        |        |              |             |               |              |       | xxxx   |       |       |       |       |               |

| TMR3HLD     | 0108  |        | Timer3 Holding Register (for 32-bit timer operations only) xxxx |        |        |        |        |              |             |               |              |       | xxxx   |       |       |       |       |               |

| TMR3        | 010A  |        | Timer3 Register xxxx                                            |        |        |        |        |              |             |               |              |       |        |       |       |       |       |               |

| PR2         | 010C  |        | Period Register 2 FFFF                                          |        |        |        |        |              |             |               |              |       | FFFF   |       |       |       |       |               |

| PR3         | 010E  |        | Period Register 3 FFF1                                          |        |        |        |        |              |             |               |              | FFFF  |        |       |       |       |       |               |

| T2CON       | 0110  | TON    | _                                                               | TSIDL  | _      | _      | _      | _            | _           | _             | TGATE        | TCKPS | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T3CON       | 0112  | TON    | _                                                               | TSIDL  | _      | _      | _      | _            | _           | _             | TGATE        | TCKPS | S<1:0> | _     | _     | TCS   | _     | 0000          |

| TMR4        | 0114  |        |                                                                 |        |        |        |        |              | Timer4      | Register      |              |       |        |       |       |       |       | xxxx          |

| TMR5HLD     | 0116  |        |                                                                 |        |        |        | Т      | imer5 Holdir | ng Register | (for 32-bit o | perations on | ly)   |        |       |       |       |       | xxxx          |

| TMR5        | 0118  |        |                                                                 |        |        |        |        |              | Timer5      | Register      |              |       |        |       |       |       |       | xxxx          |

| PR4         | 011A  |        |                                                                 |        |        |        |        |              | Period F    | Register 4    |              |       |        |       |       |       |       | FFFF          |

| PR5         | 011C  |        |                                                                 |        |        |        |        |              | Period F    | Register 5    |              |       |        |       |       |       |       | FFFF          |

| T4CON       | 011E  | TON    | _                                                               | TSIDL  | _      | _      | _      | _            | _           | _             | TGATE        | TCKPS | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T5CON       | 0120  | TON    | 1                                                               | TSIDL  | ı      | -      | _      | _            | _           | _             | TGATE        | TCKPS | S<1:0> | _     | _     | TCS   |       | 0000          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

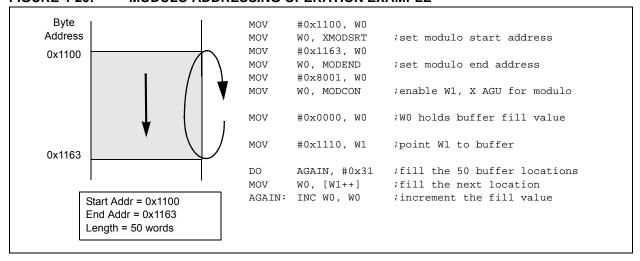

# 4.6 Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X Devices Only)

Modulo Addressing mode is a method of providing an automated means to support circular data buffers using hardware. The objective is to remove the need for software to perform data address boundary checks when executing tightly looped code, as is typical in many DSP algorithms.

Modulo Addressing can operate in either Data or Program Space (since the Data Pointer mechanism is essentially the same for both). One circular buffer can be supported in each of the X (which also provides the pointers into Program Space) and Y Data Spaces. Modulo Addressing can operate on any W Register Pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can be configured to operate in only one direction, as there are certain restrictions on the buffer start address (for incrementing buffers) or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers that have a power-of-two length. As these buffers satisfy the start and end address criteria, they can operate in a bidirectional mode (that is, address boundary checks are performed on both the lower and upper address boundaries).

#### 4.6.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified, and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

**Note:** Y space Modulo Addressing EA calculations assume word-sized data (LSb of every EA is always clear).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

## 4.6.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select the registers that operate with Modulo Addressing:

- If XWM = 1111, X RAGU and X WAGU Modulo Addressing is disabled

- If YWM = 1111, Y AGU Modulo Addressing is disabled

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X Data Space when XWM is set to any value other than '1111' and the XMODEN bit is set (MODCON<15>).

The Y Address Space Pointer W register (YWM), to which Modulo Addressing is to be applied, is stored in MODCON<7:4>. Modulo Addressing is enabled for Y Data Space when YWM is set to any value other than '1111' and the YMODEN bit is set at MODCON<14>.

FIGURE 4-20: MODULO ADDRESSING OPERATION EXAMPLE

#### 6.0 RESETS

Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

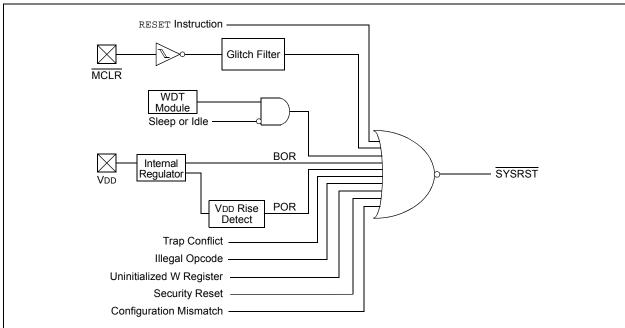

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

POR: Power-on ResetBOR: Brown-out Reset

• MCLR: Master Clear Pin Reset

• SWR: RESET Instruction

· WDTO: Watchdog Timer Time-out Reset

· CM: Configuration Mismatch Reset

TRAPR: Trap Conflict Reset

· IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state and some are unaffected.

**Note:** Refer to the specific peripheral section or **Section 4.0 "Memory Organization"** of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

A POR clears all the bits, except for the POR and BOR bits (RCON<1:0>), that are set. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

For all Resets, the default clock source is determined by the FNOSC<2:0> bits in the FOSCSEL Configuration register. The value of the FNOSC<2:0> bits is loaded into NOSC<2:0> (OSCCON<10:8>) on Reset, which in turn, initializes the system clock.

#### FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

#### REGISTER 8-5: DMAXSTBH: DMA CHANNEL x START ADDRESS REGISTER B (HIGH)

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0     | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |

|-----------|------------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

|           | STB<23:16> |       |       |       |       |       |       |  |  |  |  |  |

| bit 7 bit |            |       |       |       |       |       |       |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 **STB<23:16>:** Secondary Start Address bits (source or destination)

#### REGISTER 8-6: DMAXSTBL: DMA CHANNEL x START ADDRESS REGISTER B (LOW)

| R/W-0  | R/W-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |

|--------|-----------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

|        | STB<15:8> |       |       |       |       |       |       |  |  |  |  |  |

| bit 15 |           |       |       |       |       |       | bit 8 |  |  |  |  |  |

| R/W-0       | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|-------------|----------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|             | STB<7:0> |       |       |       |       |       |       |  |  |  |  |

| bit 7 bit 0 |          |       |       |       |       |       |       |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 **STB<15:0>:** Secondary Start Address bits (source or destination)

#### REGISTER 17-10: INDX1HLD: INDEX COUNTER 1 HOLD REGISTER

| R/W-0        | R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |

|--------------|---------------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

|              | INDXHLD<15:8> |       |       |       |       |       |       |  |  |  |  |  |

| bit 15 bit 8 |               |       |       |       |       |       |       |  |  |  |  |  |

| R/W-0       | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|-------------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|             | INDXHLD<7:0> |       |       |       |       |       |       |  |  |  |  |

| bit 7 bit 0 |              |       |       |       |       |       |       |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 INDXHLD<15:0>: Hold Register for Reading and Writing INDX1CNTH bits

#### REGISTER 17-11: QEI1ICH: QEI1 INITIALIZATION/CAPTURE HIGH WORD REGISTER

| R/W-0  | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |

|--------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

|        | QEIIC<31:24> |       |       |       |       |       |       |  |  |  |  |  |

| bit 15 |              |       |       |       |       |       | bit 8 |  |  |  |  |  |

| R/W-0 | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |  |

|-------|--------------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

|       | QEIIC<23:16> |       |       |       |       |       |       |  |  |  |  |  |

| bit 7 | bit 7 bit 0  |       |       |       |       |       |       |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 QEIIC<31:16>: High Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

#### REGISTER 17-12: QEI1ICL: QEI1 INITIALIZATION/CAPTURE LOW WORD REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|--------|-------|-------|-------|

|        |       |       | QEIIC- | <15:8> |       |       |       |

| bit 15 |       |       |        | bit 8  |       |       |       |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | QEIIC | <7:0> |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 QEIIC<15:0>: Low Word Used to Form 32-Bit Initialization/Capture Register (QEI1IC) bits

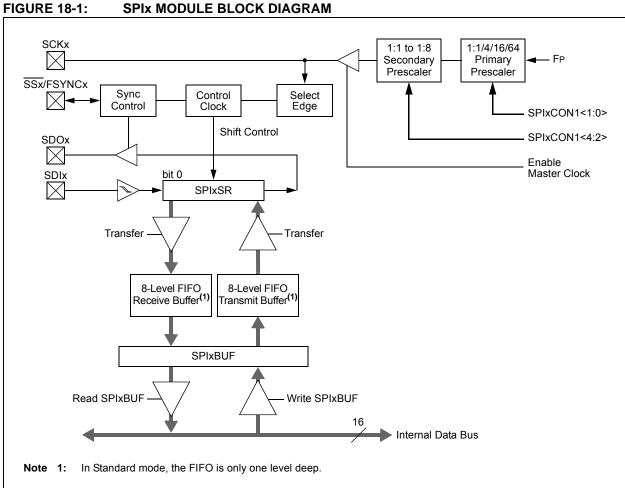

SPIX MODULE BLOCK DIAGRAM

#### REGISTER 21-10: CxCFG2: ECANx BAUD RATE CONFIGURATION REGISTER 2

| U-0    | R/W-x  | U-0 | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   |  |

|--------|--------|-----|-----|-----|---------|---------|---------|--|

| _      | WAKFIL | _   | _   | _   | SEG2PH2 | SEG2PH1 | SEG2PH0 |  |

| bit 15 |        |     |     |     |         |         |         |  |

| R/W-x    | R/W-x | R/W-x   | R/W-x   | R/W-x   | R/W-x  | R/W-x  | R/W-x  |

|----------|-------|---------|---------|---------|--------|--------|--------|

| SEG2PHTS | SAM   | SEG1PH2 | SEG1PH1 | SEG1PH0 | PRSEG2 | PRSEG1 | PRSEG0 |

| bit 7    |       |         |         |         |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 Unimplemented: Read as '0'

bit 14 WAKFIL: Select CAN Bus Line Filter for Wake-up bit

1 = Uses CAN bus line filter for wake-up

0 = CAN bus line filter is not used for wake-up

bit 13-11 **Unimplemented:** Read as '0'

bit 10-8 **SEG2PH<2:0>:** Phase Segment 2 bits

111 = Length is 8 x TQ

•

•

000 = Length is 1 x TQ

bit 7 SEG2PHTS: Phase Segment 2 Time Select bit

1 = Freely programmable

0 = Maximum of SEG1PHx bits or Information Processing Time (IPT), whichever is greater

bit 6 SAM: Sample of the CAN Bus Line bit

1 = Bus line is sampled three times at the sample point

0 = Bus line is sampled once at the sample point

bit 5-3 **SEG1PH<2:0>:** Phase Segment 1 bits

111 = Length is 8 x TQ

.

000 = Length is 1 x TQ

bit 2-0 PRSEG<2:0>: Propagation Time Segment bits

111 = Length is 8 x TQ

•

•

•

000 = Length is  $1 \times TQ$

### REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER<sup>(1,2)</sup> (CONTINUED)

| bit 4 | OC1CS: Clock Source for OC1 bit                                                                                                                                                             |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Generates clock pulse when the broadcast command is executed</li><li>0 = Does not generate clock pulse when the broadcast command is executed</li></ul>                         |

| bit 3 | OC4TSS: Trigger/Synchronization Source for OC4 bit                                                                                                                                          |

|       | 1 = Generates Trigger/Synchronization when the broadcast command is executed 0 = Does not generate Trigger/Synchronization when the broadcast command is executed                           |

| bit 2 | OC3TSS: Trigger/Synchronization Source for OC3 bit                                                                                                                                          |

|       | <ul><li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li><li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li></ul> |

| bit 1 | OC2TSS: Trigger/Synchronization Source for OC2 bit                                                                                                                                          |

|       | <ul><li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li><li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li></ul> |

| bit 0 | OC1TSS: Trigger/Synchronization Source for OC1 bit                                                                                                                                          |

|       | <ul><li>1 = Generates Trigger/Synchronization when the broadcast command is executed</li><li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li></ul> |

|       |                                                                                                                                                                                             |

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: This register is only used with the PTGCTRL OPTION = 1111 Step command.

TABLE 28-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

| Field | Description                                                                                                                                                                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm,Wn | Dividend, Divisor working register pair (direct addressing)                                                                                                                                                                                                 |

| Wm*Wm | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                               |

| Wm*Wn | Multiplicand and Multiplier working register pair for DSP instructions ∈ {W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                                  |

| Wn    | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                                                       |

| Wnd   | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                                                           |

| Wns   | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                                                |

| WREG  | W0 (working register used in file register instructions)                                                                                                                                                                                                    |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                                |

| Wso   | Source W register ∈ { Wns, [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                                       |

| Wx    | X Data Space Prefetch Address register for DSP instructions ∈ {[W8] + = 6, [W8] + = 4, [W8] + = 2, [W8], [W8] - = 6, [W8] - = 4, [W8] - = 2, [W9] + = 6, [W9] + = 4, [W9] + = 2, [W9], [W9] - = 6, [W9] - = 4, [W9] - = 2, [W9 + W12], none}                |

| Wxd   | X Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                    |

| Wy    | Y Data Space Prefetch Address register for DSP instructions ∈ {[W10] + = 6, [W10] + = 4, [W10] + = 2, [W10], [W10] - = 6, [W10] - = 4, [W10] - = 2, [W11] + = 6, [W11] + = 4, [W11] + = 2, [W11], [W11] - = 6, [W11] - = 4, [W11] - = 2, [W11 + W12], none} |

| Wyd   | Y Data Space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                    |

TABLE 30-9: DC CHARACTERISTICS: WATCHDOG TIMER DELTA CURRENT (△IWDT)<sup>(1)</sup>

| DC CHARACTER  | RISTICS | ating Conditions: 3.0V trise stated) therefore $-40^{\circ}C \le TA \le +8$ $-40^{\circ}C \le TA \le +8$ |       |                 |  |  |  |  |

|---------------|---------|----------------------------------------------------------------------------------------------------------|-------|-----------------|--|--|--|--|

| Parameter No. | Тур.    | Max.                                                                                                     | Units | Conditions      |  |  |  |  |

| DC61d         | 8       | _                                                                                                        | μΑ    | -40°C           |  |  |  |  |

| DC61a         | 10      | _                                                                                                        | μΑ    | +25°C           |  |  |  |  |

| DC61b         | 12      | _                                                                                                        | μΑ    | +85°C<br>+125°C |  |  |  |  |

| DC61c         | 13      | _                                                                                                        | μΑ    |                 |  |  |  |  |

Note 1: The ∆IWDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

TABLE 30-10: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTER         | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \leq \text{Ta} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{Ta} \leq +125^{\circ}\text{C}$ for Extended |      |               |       |                            |       |                |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|-------|----------------------------|-------|----------------|

| Parameter No.        | Тур.                                                                                                                                                                                                                                                 | Max. | Doze<br>Ratio | Units |                            | Cond  | ditions        |

| Doze Current (IDC    | )ZE) <sup>(1)</sup>                                                                                                                                                                                                                                  |      |               |       |                            |       |                |

| DC73a <sup>(2)</sup> | 35                                                                                                                                                                                                                                                   | _    | 1:2           | mA    | -40°C                      | 3.3V  | Fosc = 140 MHz |

| DC73g                | 20                                                                                                                                                                                                                                                   | 30   | 1:128         | mA    | -40 C                      | 3.34  |                |

| DC70a <sup>(2)</sup> | 35                                                                                                                                                                                                                                                   | _    | 1:2           | mA    | +25°C                      | 3.3V  | Fosc = 140 MHz |

| DC70g                | 20                                                                                                                                                                                                                                                   | 30   | 1:128         | mA    | +25 C                      | 3.37  |                |

| DC71a <sup>(2)</sup> | 35                                                                                                                                                                                                                                                   | _    | 1:2           | mA    | .05°C                      | 2.2)/ | F000 - 140 MH- |

| DC71g                | 20                                                                                                                                                                                                                                                   | 30   | 1:128         | mA    | +85°C                      | 3.3V  | Fosc = 140 MHz |

| DC72a <sup>(2)</sup> | 28                                                                                                                                                                                                                                                   | _    | 1:2           | mA    | +125°C 3.3V Fosc = 120 MHz |       |                |

| DC72g                | 15                                                                                                                                                                                                                                                   | 30   | 1:128         | mA    | +125 C                     | 3.3V  | Fosc = 120 MHz |

- **Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- · CLKO is configured as an I/O input pin in the Configuration Word

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- · CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) statement

- · JTAG is disabled

- 2: Parameter is characterized but not tested in manufacturing.

## 30.2 AC Characteristics and Timing Parameters

This section defines dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X AC characteristics and timing parameters.

TABLE 30-15: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 3.0V to 3.6V                  |  |  |  |  |

|--------------------|--------------------------------------------------------------|--|--|--|--|

|                    | (unless otherwise stated)                                    |  |  |  |  |

| AC CHARACTERISTICS | Operating temperature -40°C ≤ Ta ≤ +85°C for Industrial      |  |  |  |  |

| AC CHARACTERISTICS | -40°C ≤ Ta ≤ +125°C for Extended                             |  |  |  |  |

|                    | Operating voltage VDD range as described in Section 30.1 "DC |  |  |  |  |

|                    | Characteristics".                                            |  |  |  |  |

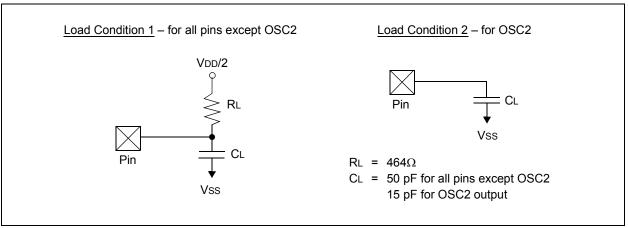

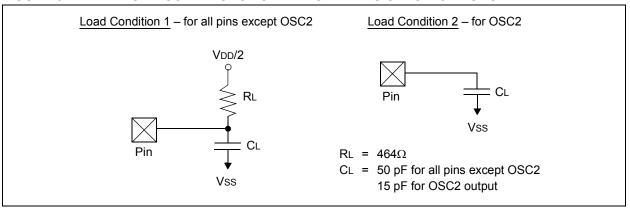

#### FIGURE 30-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 30-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min. | Тур. | Max. | Units | Conditions                                                    |

|--------------|--------|-----------------------|------|------|------|-------|---------------------------------------------------------------|

| DO50         | Cosco  | OSC2 Pin              | _    | _    | 15   | pF    | In XT and HS modes, when external clock is used to drive OSC1 |

| DO56         | Сю     | All I/O Pins and OSC2 | _    | _    | 50   | pF    | EC mode                                                       |

| DO58         | Св     | SCLx, SDAx            | _    | _    | 400  | pF    | In I <sup>2</sup> C™ mode                                     |

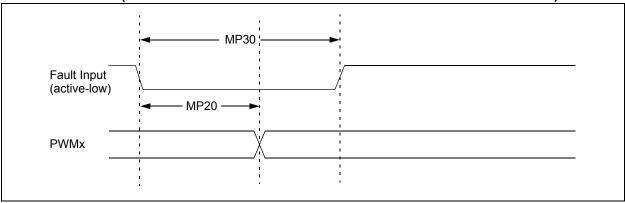

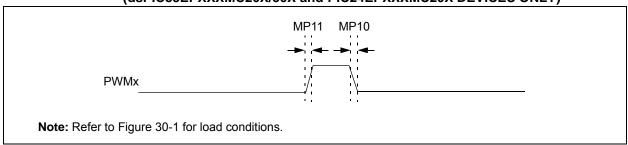

FIGURE 30-9: HIGH-SPEED PWMx MODULE FAULT TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

FIGURE 30-10: HIGH-SPEED PWMx MODULE TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

TABLE 30-29: HIGH-SPEED PWMx MODULE TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| AC CHARACTERISTICS |        |                                  |                                 | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |    |    |                    |  |  |

|--------------------|--------|----------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|--------------------|--|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>    | Min. Typ. Max. Units Conditions |                                                                                                                                                                                                                                                     |    |    |                    |  |  |

| MP10               | TFPWM  | PWMx Output Fall Time            | _                               | _                                                                                                                                                                                                                                                   | _  | ns | See Parameter DO32 |  |  |

| MP11               | TRPWM  | PWMx Output Rise Time            | _                               | _                                                                                                                                                                                                                                                   | _  | ns | See Parameter DO31 |  |  |

| MP20               | TFD    | Fault Input ↓ to PWMx I/O Change |                                 | _                                                                                                                                                                                                                                                   | 15 | ns |                    |  |  |

| MP30               | TFH    | Fault Input Pulse Width          | 15                              | _                                                                                                                                                                                                                                                   | _  | ns |                    |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

TABLE 30-39: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0) TIMING REQUIREMENTS

| AC CHA | AC CHARACTERISTICS    |                                              |              | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industri $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extendition of the condition of the conditio |      |       |                             |  |  |

|--------|-----------------------|----------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-----------------------------|--|--|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                | Min.         | Typ. <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Max. | Units | Conditions                  |  |  |

| SP70   | FscP                  | Maximum SCK2 Input Frequency                 | _            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15   | MHz   | (Note 3)                    |  |  |

| SP72   | TscF                  | SCK2 Input Fall Time                         | _            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _    | ns    | See Parameter DO32 (Note 4) |  |  |

| SP73   | TscR                  | SCK2 Input Rise Time                         | _            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _    | ns    | See Parameter DO31 (Note 4) |  |  |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                   | _            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _    | ns    | See Parameter DO32 (Note 4) |  |  |

| SP31   | TdoR                  | SDO2 Data Output Rise Time                   | _            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _    | ns    | See Parameter DO31 (Note 4) |  |  |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after SCK2 Edge       | _            | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20   | ns    |                             |  |  |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge | 30           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _    | ns    |                             |  |  |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge   | 30           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _    | ns    |                             |  |  |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge    | 30           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _    | ns    |                             |  |  |

| SP50   | TssL2scH,<br>TssL2scL | SS2 ↓ to SCK2 ↑ or SCK2 ↓ Input              | 120          | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _    | ns    |                             |  |  |

| SP51   | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance       | 10           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 50   | ns    | (Note 4)                    |  |  |

| SP52   | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                        | 1.5 Tcy + 40 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _    | ns    | (Note 4)                    |  |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 66.7 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

- 4: Assumes 50 pF load on all SPI2 pins.

## 31.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X AC characteristics and timing parameters for high-temperature devices. However, all AC timing specifications in this section are the same as those in **Section 30.2 "AC Characteristics and Timing Parameters"**, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter OS53 in **Section 30.2** "AC Characteristics and Timing Parameters" is the Industrial and Extended temperature equivalent of HOS53.

TABLE 31-9: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

| AC CHARACTERISTICS | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) |  |  |

|--------------------|-----------------------------------------------------------------------|--|--|

| AC CHARACTERISTICS | Operating temperature -40°C ≤ TA ≤ +150°C                             |  |  |

|                    | Operating voltage VDD range as described in Table 31-1.               |  |  |

#### FIGURE 31-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

TABLE 31-10: PLL CLOCK TIMING SPECIFICATIONS