Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gp506t-e-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33EP64MC506 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70598)

- "Timers" (DS70362)

- "Input Capture" (DS70352)

- "Output Compare" (DS70358)

- "High-Speed PWM" (DS70645)

- "Quadrature Encoder Interface (QEI)" (DS70601)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70582)

- "Serial Peripheral Interface (SPI)" (DS70569)

- "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70330)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "CodeGuard™ Security" (DS70634)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70357)

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Device Configuration" (DS70618)

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

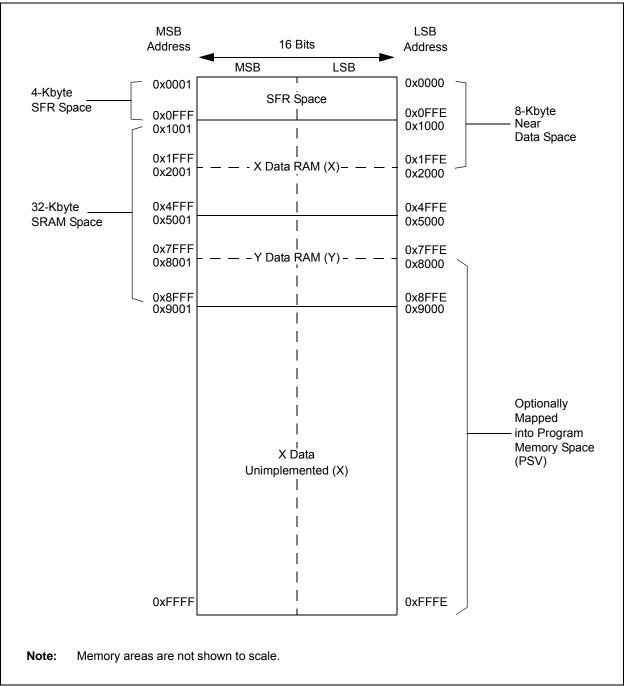

# FIGURE 4-10: DATA MEMORY MAP FOR dsPIC33EP256MC20X/50X AND dsPIC33EP256GP50X DEVICES

## 4.2.5 X AND Y DATA SPACES

# The dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X core has two Data Spaces, X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X Data Space is used by all instructions and supports all addressing modes. X Data Space has separate read and write data buses. The X read data bus is the read data path for all instructions that view Data Space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y Data Space is used in concert with the X Data Space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X Data Space. Modulo Addressing and Bit-Reversed Addressing are not present in PIC24EPXXXGP/MC20X devices.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

## 4.3 Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

## 4.3.1 KEY RESOURCES

- "Program Memory" (DS70613) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

## TABLE 4-19: SPI1 AND SPI2 REGISTER MAP

| SFR Name | Addr. | Bit 15                                        | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8        | Bit 7       | Bit 6      | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------|-----------------------------------------------|--------|---------|--------|--------|--------|------------|--------------|-------------|------------|--------|-------|------------|-------|--------|--------|---------------|

| SPI1STAT | 0240  | SPIEN                                         | _      | SPISIDL | _      | _      | 5      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242  | _                                             | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2 | 0244  | FRMEN                                         | SPIFSD | FRMPOL  | _      | _      |        | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI1BUF  | 0248  |                                               |        |         |        |        |        | SPI1 Tra   | insmit and R | eceive Buff | er Registe | r      |       |            |       |        |        | 0000          |

| SPI2STAT | 0260  | SPIEN                                         | _      | SPISIDL | _      | _      | ŝ      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |       | SISEL<2:0> |       | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262  | _                                             | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE          | SSEN        | CKP        | MSTEN  |       | SPRE<2:0>  |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264  | FRMEN                                         | SPIFSD | FRMPOL  | _      | _      |        | _          | _            | —           | _          | _      | _     | _          | _     | FRMDLY | SPIBEN | 0000          |

| SPI2BUF  | 0268  | 268 SPI2 Transmit and Receive Buffer Register |        |         |        |        |        |            |              |             | 0000       |        |       |            |       |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 4.5.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions. which apply to dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and the DSP accumulator class of instructions, which apply to the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-Bit Literal

- 16-Bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

## 4.5.4 MAC INSTRUCTIONS (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X DEVICES ONLY)

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY. N, MOVSAC and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the Data Pointers through register indirect tables.

The Two-Source Operand Prefetch registers must be members of the set: {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The Effective Addresses generated (before and after modification) must therefore, be valid addresses within X Data Space for W8 and W9, and Y Data Space for W10 and W11.

Note: Register Indirect with Register Offset Addressing mode is available only for W9 (in X space) and W11 (in Y space).

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- · Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

## 4.5.5 OTHER INSTRUCTIONS

Besides the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ULNK, the source of an operand or result is implied by the opcode itself. Certain operations, such as a NOP, do not have any operands.

## 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Flash Programming" (DS70609) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming™ (ICSP™) programming capability

- Run-Time Self-Programming (RTSP)

ICSP allows for a dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X device to be serially programmed while in the end application circuit. This is done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx), and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the device just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (Table Read) and TBLWT (Table Write) instructions. With RTSP, the user application can write program memory data a single program memory word, and erase program memory in blocks or 'pages' of 1024 instructions (3072 bytes) at a time.

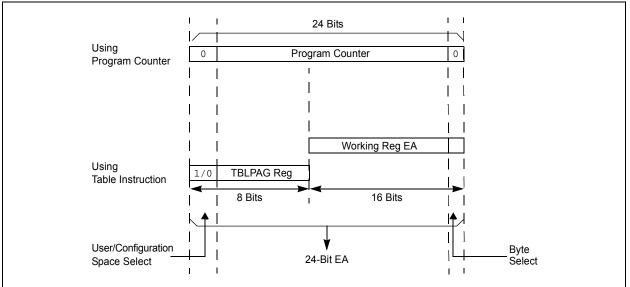

## 5.1 Table Instructions and Flash Programming

Regardless of the method used, all programming of Flash memory is done with the Table Read and Table Write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register, specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

## FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/SO-0 <sup>(1</sup>         | ) R/W-0 <sup>(1)</sup>                     | R/W-0 <sup>(1)</sup>        | R/W-0                         | U-0                     | U-0                     | U-0                     | U-0                    |

|------------------------------|--------------------------------------------|-----------------------------|-------------------------------|-------------------------|-------------------------|-------------------------|------------------------|

| WR                           | WREN                                       | WRERR                       | NVMSIDL <sup>(2)</sup>        | _                       |                         | —                       |                        |

| bit 15                       | I                                          | 1                           | 1                             |                         |                         |                         | bit 8                  |

|                              |                                            |                             |                               |                         |                         |                         |                        |

| U-0                          | U-0                                        | U-0                         | U-0                           | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>   |

| _                            | —                                          | —                           | —                             | NVMOP3 <sup>(3,4)</sup> | NVMOP2 <sup>(3,4)</sup> | NVMOP1 <sup>(3,4)</sup> | NVMOP0 <sup>(3,4</sup> |

| bit 7                        |                                            |                             |                               |                         |                         |                         | bit (                  |

| lagandi                      |                                            | SO - Sottab                 | la Only hit                   |                         |                         |                         |                        |

| L <b>egend:</b><br>R = Reada | ble hit                                    | SO = Settab<br>W = Writable | -                             | II – I Inimplem         | nented bit, read        | ae 'O'                  |                        |

| -n = Value                   |                                            | '1' = Bit is se             |                               | '0' = Bit is clea       |                         | x = Bit is unkr         |                        |

|                              |                                            | 1 - Dit 13 30               |                               |                         |                         |                         | lowin                  |

| bit 15                       | WR: Write Co                               | ontrol bit(1)               |                               |                         |                         |                         |                        |

|                              |                                            |                             | ory program or                | erase operation         | on; the operatio        | n is self-timed         | and the bit is         |

|                              | cleared b                                  | y hardware o                | nce the operati               | on is complete          |                         |                         |                        |

|                              | -                                          |                             | ration is comple              | ete and inactive        | 9                       |                         |                        |

| bit 14                       | WREN: Write                                |                             | n/erase operati               | 000                     |                         |                         |                        |

|                              |                                            |                             | /erase operatio               |                         |                         |                         |                        |

| oit 13                       |                                            |                             | Error Flag bit <sup>(1)</sup> |                         |                         |                         |                        |

|                              | 1 = An impro                               | per program o               | r erase sequend               |                         | rmination has oc        | curred (bit is se       | t automatically        |

|                              |                                            | et attempt of th            | e WR bit)<br>operation com    | olotod pormally         |                         |                         |                        |

| bit 12                       |                                            |                             | le Control bit <sup>(2)</sup> | Sieteu normaliy         |                         |                         |                        |

|                              |                                            |                             | r goes into Star              | ndbv mode duri          | ina Idle mode           |                         |                        |

|                              |                                            |                             | r is active durin             |                         |                         |                         |                        |

| bit 11-4                     | Unimplemen                                 | ted: Read as                | '0'                           |                         |                         |                         |                        |

| bit 3-0                      | NVMOP<3:0>                                 | NVM Operation               | ation Select bits             | <sub>3</sub> (1,3,4)    |                         |                         |                        |

|                              | 1111 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1110 = Rese<br>1101 = Rese                 |                             |                               |                         |                         |                         |                        |

|                              | 1100 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1011 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1010 = Rese<br>0011 = Memo                 |                             | e operation                   |                         |                         |                         |                        |

|                              | 0010 = Rese                                | rved                        | -                             |                         |                         |                         |                        |

|                              |                                            |                             | ord program ope               | eration <sup>(5)</sup>  |                         |                         |                        |

|                              | 0000 <b>= Rese</b>                         | rvea                        |                               |                         |                         |                         |                        |

|                              | These bits can onl                         | -                           |                               |                         |                         |                         |                        |

|                              | If this bit is set, the (TVREG) before Fla |                             |                               |                         | d upon exiting lo       | dle mode, there         | is a delay             |

|                              | All other combinati                        |                             | •                             |                         |                         |                         |                        |

| <b>.</b> .                   |                                            |                             |                               | in ploinenteu.          |                         |                         |                        |

| 4:                           | Execution of the P                         | wrsav instruc               | tion is ianored               | while any of th         | e NVM operatio          | ns are in progr         | ess.                   |

## REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER

|                                                     | Vector  | IRQ        |                   | Inte     | errupt Bit L | ocation      |

|-----------------------------------------------------|---------|------------|-------------------|----------|--------------|--------------|

| Interrupt Source                                    | # #     |            | IVT Address       | Flag     | Enable       | Priority     |

| QEI1 – QEI1 Position Counter Compare <sup>(2)</sup> | 66      | 58         | 0x000088          | IFS3<10> | IEC3<10>     | IPC14<10:8>  |

| Reserved                                            | 67-72   | 59-64      | 0x00008A-0x000094 | _        | _            | _            |

| U1E – UART1 Error Interrupt                         | 73      | 65         | 0x000096          | IFS4<1>  | IEC4<1>      | IPC16<6:4>   |

| U2E – UART2 Error Interrupt                         | 74      | 66         | 0x000098          | IFS4<2>  | IEC4<2>      | IPC16<10:8>  |

| CRC – CRC Generator Interrupt                       | 75      | 67         | 0x00009A          | IFS4<3>  | IEC4<3>      | IPC16<14:12> |

| Reserved                                            | 76-77   | 68-69      | 0x00009C-0x00009E | —        | _            | —            |

| C1TX – CAN1 TX Data Request <sup>(1)</sup>          | 78      | 70         | 0x000A0           | IFS4<6>  | IEC4<6>      | IPC17<10:8>  |

| Reserved                                            | 79-84   | 71-76      | 0x0000A2-0x0000AC | —        | _            | —            |

| CTMU – CTMU Interrupt                               | 85      | 77         | 0x0000AE          | IFS4<13> | IEC4<13>     | IPC19<6:4>   |

| Reserved                                            | 86-101  | 78-93      | 0x0000B0-0x0000CE | —        | _            | —            |

| PWM1 – PWM Generator 1 <sup>(2)</sup>               | 102     | 94         | 0x0000D0          | IFS5<14> | IEC5<14>     | IPC23<10:8>  |

| PWM2 – PWM Generator 2 <sup>(2)</sup>               | 103     | 95         | 0x0000D2          | IFS5<15> | IEC5<15>     | IPC23<14:12> |

| PWM3 – PWM Generator 3 <sup>(2)</sup>               | 104     | 96         | 0x0000D4          | IFS6<0>  | IEC6<0>      | IPC24<2:0>   |

| Reserved                                            | 105-149 | 97-141     | 0x0001D6-0x00012E | —        | _            | —            |

| ICD – ICD Application                               | 150     | 142        | 0x000142          | IFS8<14> | IEC8<14>     | IPC35<10:8>  |

| JTAG – JTAG Programming                             | 151     | 143        | 0x000130          | IFS8<15> | IEC8<15>     | IPC35<14:12> |

| Reserved                                            | 152     | 144        | 0x000134          | —        | _            | _            |

| PTGSTEP – PTG Step                                  | 153     | 145        | 0x000136          | IFS9<1>  | IEC9<1>      | IPC36<6:4>   |

| PTGWDT – PTG Watchdog Time-out                      | 154     | 146        | 0x000138          | IFS9<2>  | IEC9<2>      | IPC36<10:8>  |

| PTG0 – PTG Interrupt 0                              | 155     | 147        | 0x00013A          | IFS9<3>  | IEC9<3>      | IPC36<14:12> |

| PTG1 – PTG Interrupt 1                              | 156     | 148        | 0x00013C          | IFS9<4>  | IEC9<4>      | IPC37<2:0>   |

| PTG2 – PTG Interrupt 2                              | 157     | 149        | 0x00013E          | IFS9<5>  | IEC9<5>      | IPC37<6:4>   |

| PTG3 – PTG Interrupt 3                              | 158     | 150        | 0x000140          | IFS9<6>  | IEC9<6>      | IPC37<10:8>  |

| Reserved                                            | 159-245 | 151-245    | 0x000142-0x0001FE | —        | —            | _            |

|                                                     | Lowe    | est Natura | I Order Priority  |          |              |              |

## TABLE 7-1: INTERRUPT VECTOR DETAILS (CONTINUED)

Note 1: This interrupt source is available on dsPIC33EPXXXGP50X and dsPIC33EPXXXMC50X devices only.

2: This interrupt source is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

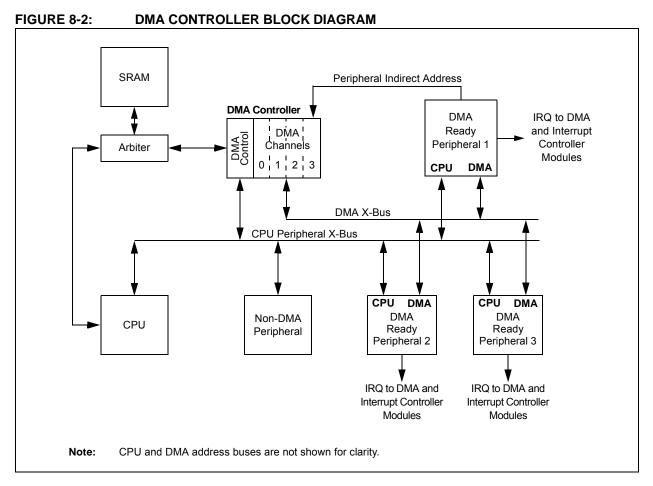

## 8.1 DMA Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

## 8.1.1 KEY RESOURCES

- Section 22. "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## 8.2 DMAC Registers

Each DMAC Channel x (where x = 0 through 3) contains the following registers:

- 16-Bit DMA Channel Control register (DMAxCON)

- 16-Bit DMA Channel IRQ Select register (DMAxREQ)

- 32-Bit DMA RAM Primary Start Address register (DMAxSTA)

- 32-Bit DMA RAM Secondary Start Address register (DMAxSTB)

- 16-Bit DMA Peripheral Address register (DMAxPAD)

- 14-Bit DMA Transfer Count register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADR) are common to all DMAC channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The interrupt flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding interrupt enable control bits (DMAxIE) are located in an IECx register in the interrupt controller, and the corresponding interrupt priority control bits (DMAxIP) are located in an IPCx register in the interrupt controller.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 8-3: DMAXSTAH: DMA CHANNEL X START ADDRESS REGISTER A (HIGH)

| U-0            | U-0   | U-0            | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-------|----------------|-------|--------------|------------------|--------|-------|

| —              | _     | —              | —     | —            | —                | —      | —     |

| bit 15         |       |                |       |              |                  |        | bit 8 |

|                |       |                |       |              |                  |        |       |

| R/W-0          | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

|                |       |                | STA<  | 23:16>       |                  |        |       |

| bit 7          |       |                |       |              |                  |        | bit 0 |

|                |       |                |       |              |                  |        |       |

| Legend:        |       |                |       |              |                  |        |       |

| R = Readable b | oit   | W = Writable b | it    | U = Unimpler | mented bit, read | as '0' |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

## bit 15-8 Unimplemented: Read as '0'

bit 7-0 STA<23:16>: Primary Start Address bits (source or destination)

## REGISTER 8-4: DMAXSTAL: DMA CHANNEL x START ADDRESS REGISTER A (LOW)

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | STA   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STA   | A<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimpler     | mented bit, rea | ad as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unki | nown  |

bit 15-0 STA<15:0>: Primary Start Address bits (source or destination)

NOTES:

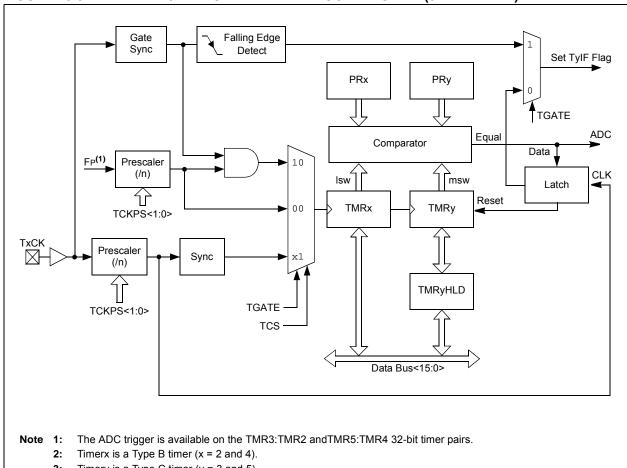

#### **FIGURE 13-3:** TYPE B/TYPE C TIMER PAIR BLOCK DIAGRAM (32-BIT TIMER)

3: Timery is a Type C timer (y = 3 and 5).

#### **Timerx/y Resources** 13.1

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/                                                            |

|       | wwwproducts/Devices.aspx?d                                                           |

|       | DocName=en555464                                                                     |

#### **KEY RESOURCES** 13.1.1

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = No Sync or Trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = CTMU module synchronizes or triggers ICx

- 11011 = ADC1 module synchronizes or triggers  $ICx^{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- 11001 = CMP2 module synchronizes or triggers  $ICx^{(5)}$

- 11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module synchronizes or triggers ICx

- 10010 = IC3 module synchronizes or triggers ICx

- 10001 = IC2 module synchronizes or triggers ICx

- 10000 = IC1 module synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = PTGOx module synchronizes or triggers  $ICx^{(6)}$

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No Sync or Trigger source for ICx

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1

PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

## 16.2 PWM Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en555464                                        |

## 16.2.1 KEY RESOURCES

- "High-Speed PWM" (DS70645) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## REGISTER 16-13: IOCONX: PWMx I/O CONTROL REGISTER<sup>(2)</sup> (CONTINUED)

- bit 1 SWAP: SWAP PWMxH and PWMxL Pins bit

1 = PWMxH output signal is connected to PWMxL pins; PWMxL output signal is connected to PWMxH pins

0 = PWMxH and PWMxL pins are mapped to their respective pins

bit 0 OSYNC: Output Override Synchronization bit

1 = Output overrides via the OVRDAT<1:0> bits are synchronized to the PWMx period boundary

- 0 = Output overrides via the OVDDAT<1:0> bits occur on the next CPU clock boundary

- Note 1: These bits should not be changed after the PWMx module is enabled (PTEN = 1).

- 2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

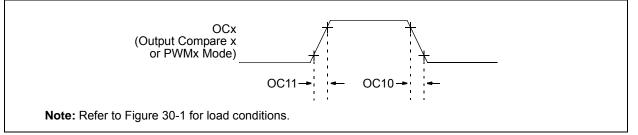

## FIGURE 30-7: OUTPUT COMPARE x MODULE (OCx) TIMING CHARACTERISTICS

## TABLE 30-27: OUTPUT COMPARE x MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |      |       |                    |  |  |

|--------------------|--------|-------------------------------|------------------------------------------------------|------|------|-------|--------------------|--|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min.                                                 | Тур. | Max. | Units | Conditions         |  |  |

| OC10               | TccF   | OCx Output Fall Time          | _                                                    |      | _    | ns    | See Parameter DO32 |  |  |

| OC11               | TccR   | OCx Output Rise Time          | _                                                    | _    | —    | ns    | See Parameter DO31 |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

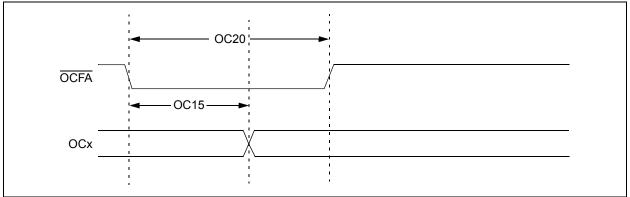

## FIGURE 30-8: OCx/PWMx MODULE TIMING CHARACTERISTICS

## TABLE 30-28: OCx/PWMx MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |          |      |          |       |            |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|----------|-------|------------|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                           | Min.     | Тур. | Max.     | Units | Conditions |

| OC15               | TFD    | Fault Input to PWMx I/O<br>Change                                                                                                                                                                                                                                                       | —        | _    | Tcy + 20 | ns    |            |

| OC20               | TFLT   | Fault Input Pulse Width                                                                                                                                                                                                                                                                 | TCY + 20 |      | —        | ns    |            |

**Note 1:** These parameters are characterized but not tested in manufacturing.

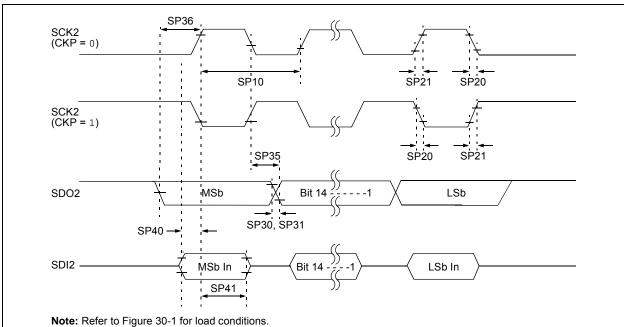

## FIGURE 30-16: SPI2 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1) TIMING CHARACTERISTICS

## TABLE 30-35:SPI2 MASTER MODE (FULL-DUPLEX, CKE = 1, CKP = x, SMP = 1)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                     |      |       |                             |

|--------------------|-----------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-----------------------------|

| Param.             | Symbol                | Characteristic <sup>(1)</sup>                 | Min.                                                                                                                                                                                                                                                                                  | Typ. <sup>(2)</sup> | Max. | Units | Conditions                  |

| SP10               | FscP                  | Maximum SCK2 Frequency                        | _                                                                                                                                                                                                                                                                                     | —                   | 9    | MHz   | (Note 3)                    |

| SP20               | TscF                  | SCK2 Output Fall Time                         | —                                                                                                                                                                                                                                                                                     | —                   |      | ns    | See Parameter DO32 (Note 4) |

| SP21               | TscR                  | SCK2 Output Rise Time                         | —                                                                                                                                                                                                                                                                                     | —                   | —    | ns    | See Parameter DO31 (Note 4) |

| SP30               | TdoF                  | SDO2 Data Output Fall Time                    | —                                                                                                                                                                                                                                                                                     | —                   | —    | ns    | See Parameter DO32 (Note 4) |

| SP31               | TdoR                  | SDO2 Data Output Rise Time                    | —                                                                                                                                                                                                                                                                                     | —                   | _    | ns    | See Parameter DO31 (Note 4) |

| SP35               | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after SCK2 Edge        | —                                                                                                                                                                                                                                                                                     | 6                   | 20   | ns    |                             |

| SP36               | TdoV2sc,<br>TdoV2scL  | SDO2 Data Output Setup to<br>First SCK2 Edge  | 30                                                                                                                                                                                                                                                                                    |                     | —    | ns    |                             |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data<br>Input to SCK2 Edge | 30                                                                                                                                                                                                                                                                                    | —                   |      | ns    |                             |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge     | 30                                                                                                                                                                                                                                                                                    |                     | _    | ns    |                             |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

- **3:** The minimum clock period for SCK2 is 111 ns. The clock generated in Master mode must not violate this specification.

- **4:** Assumes 50 pF load on all SPI2 pins.

## 31.0 HIGH-TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/ MC20X electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 30.0** "**Electrical Characteristics**" for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, Parameter DC10 in **Section 30.0 "Electrical Characteristics"** is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X high-temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

## Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias <sup>(2)</sup>                                     | 40°C to +150°C       |

|-----------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                               | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                                | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(3)</sup>     | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(3)</sup> | 0.3V to 3.6V         |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(3)}$      | 0.3V to 5.5V         |

| Maximum current out of Vss pin                                                    | 60 mA                |

| Maximum current into Vod pin <sup>(4)</sup>                                       | 60 mA                |

| Maximum junction temperature                                                      | +155°C               |

| Maximum current sourced/sunk by any 4x I/O pin                                    | 10 mA                |

| Maximum current sourced/sunk by any 8x I/O pin                                    | 15 mA                |

| Maximum current sunk by all ports combined                                        | 70 mA                |

| Maximum current sourced by all ports combined <sup>(4)</sup>                      | 70 mA                |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: AEC-Q100 reliability testing for devices intended to operate at +150°C is 1,000 hours. Any design in which the total operating time from +125°C to +150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 3: Refer to the "Pin Diagrams" section for 5V tolerant pins.

- 4: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

# 28-Lead Plastic Quad Flat, No Lead Package (MM) - 6x6x0.9mm Body [QFN-S] With 0.40 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |          |      |      |  |  |

|-------------------------|-------------|----------|------|------|--|--|

| Dimension Limits        |             | MIN      | NOM  | MAX  |  |  |

| Number of Pins          | Ν           | 28       |      |      |  |  |

| Pitch                   | е           | 0.65 BSC |      |      |  |  |

| Overall Height          | А           | 0.80     | 0.90 | 1.00 |  |  |

| Standoff                | A1          | 0.00     | 0.02 | 0.05 |  |  |

| Terminal Thickness      | A3          | 0.20 REF |      |      |  |  |

| Overall Width           | Е           | 6.00 BSC |      |      |  |  |

| Exposed Pad Width       | E2          | 3.65     | 3.70 | 4.70 |  |  |

| Overall Length          | D           | 6.00 BSC |      |      |  |  |

| Exposed Pad Length      | D2          | 3.65     | 3.70 | 4.70 |  |  |

| Terminal Width          | b           | 0.23     | 0.30 | 0.35 |  |  |

| Terminal Length         | L           | 0.30     | 0.40 | 0.50 |  |  |

| Terminal-to-Exposed Pad | К           | 0.20     | -    | -    |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

$\label{eq:REF:Reference} \ensuremath{\mathsf{REF:}} \ensuremath{\mathsf{Reference}}\xspace \ensuremath{\mathsf{Dimension}}, \ensuremath{\mathsf{usually}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{toterance}}\xspace, \ensuremath{\mathsf{for}}\xspace \ensuremath{\mathsf{oterance}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{toterance}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{rescale}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{\mathsf{toterance}}\xspace \ensuremath{\mathsf{vithout}}\xspace \ensuremath{$

Microchip Technology Drawing C04-124C Sheet 2 of 2

# 44-Terminal Very Thin Leadless Array Package (TL) – 6x6x0.9 mm Body With Exposed Pad [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL A

|                         | MILLIMETERS         |               |      |       |  |  |

|-------------------------|---------------------|---------------|------|-------|--|--|

| Dimension               | Limits              | MIN           | NOM  | MAX   |  |  |

| Number of Pins          | Ν                   | 44            |      |       |  |  |

| Number of Pins per Side | of Pins per Side ND |               |      | 12    |  |  |

| Number of Pins per Side | NE                  | 10            |      |       |  |  |

| Pitch                   | е                   | 0.50 BSC      |      |       |  |  |

| Overall Height          | Α                   | 0.80          | 0.90 | 1.00  |  |  |

| Standoff                | A1                  | 0.025         | -    | 0.075 |  |  |

| Overall Width           | Е                   | 6.00 BSC      |      |       |  |  |

| Exposed Pad Width       | E2                  | 4.40 4.55 4.7 |      | 4.70  |  |  |

| Overall Length          | D                   | 6.00 BSC      |      |       |  |  |

| Exposed Pad Length      | D2                  | 4.40          | 4.55 | 4.70  |  |  |

| Contact Width           | b                   | 0.20          | 0.25 | 0.30  |  |  |

| Contact Length          | L                   | 0.20          | 0.25 | 0.30  |  |  |

| Contact-to-Exposed Pad  | К                   | 0.20          | -    | -     |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-157C Sheet 2 of 2