Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gp506t-e-pt |

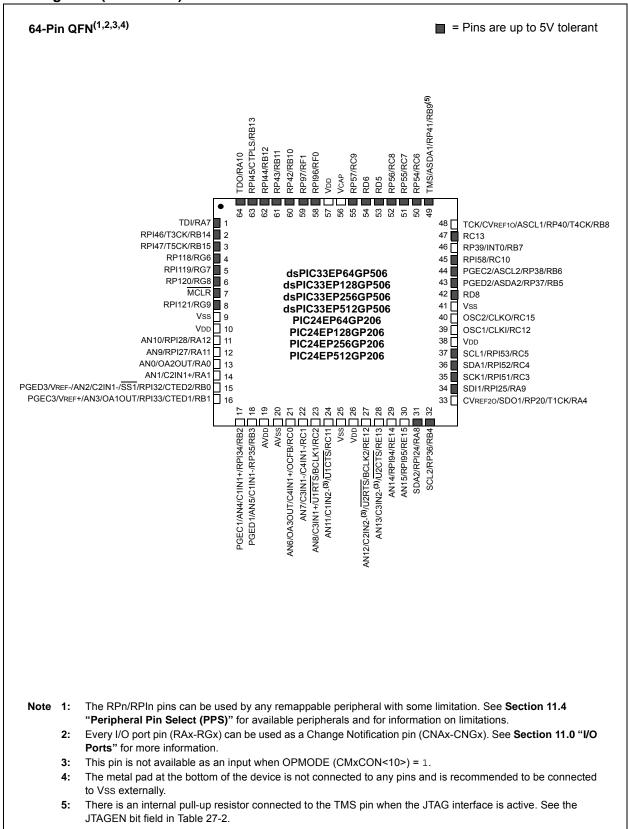

## Pin Diagrams (Continued)

#### 2.7 **Oscillator Value Conditions on Device Start-up**

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz < Fin < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

#### 2.8 Unused I/Os

FIGURE 2-4:

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

#### 2.9 **Application Examples**

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- · DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- Automotive HVAC, cooling fans, fuel pumps

- · Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- · Speech (playback, hands-free kits, answering machines, VoIP)

- · Consumer audio

- · Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- · Data storage device management

- · Smart cards and smart card readers

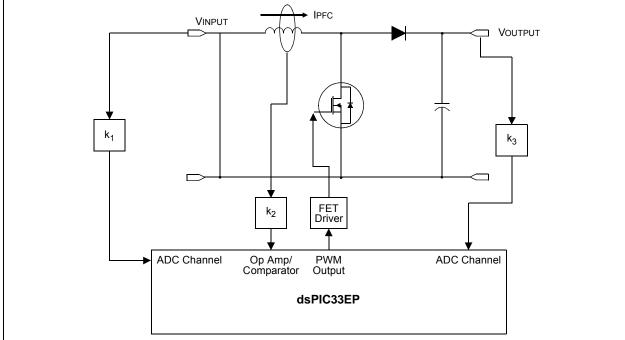

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

**IPFC** VINPUT

**BOOST CONVERTER IMPLEMENTATION**

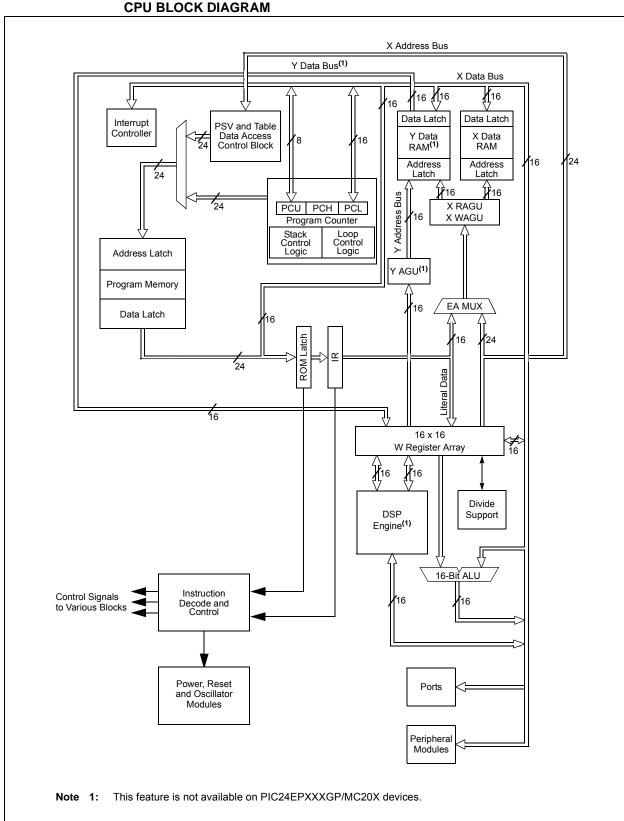

FIGURE 3-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X CPU BLOCK DIAGRAM

#### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Program Memory" (DS70613) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

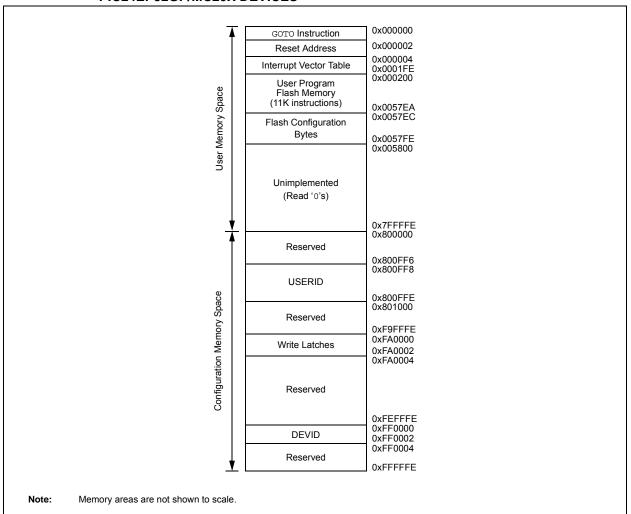

## 4.1 Program Address Space

The program address memory space of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in **Section 4.8 "Interfacing Program and Data Memory Spaces**".

User application access to the program memory space is restricted to the lower half of the address range (0x0000000 to 0x7FFFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space.

The program memory maps, which are presented by device family and memory size, are shown in Figure 4-1 through Figure 4-5.

FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EP32GP50X, dsPIC33EP32MC20X/50X AND PIC24EP32GP/MC20X DEVICES

# 4.4 Special Function Register Maps

## TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND dsPIC33EPXXXGP50X DEVICES ONLY

| IADLL     | ••    | 0, 0 0 |        |        | ·           | 011 00     | .000   | 7070701110 | _0/4/00/1  | 7 ti ti b | 0000  | ,,,,,,, | O. 0071  |          |          | •     |       |               |

|-----------|-------|--------|--------|--------|-------------|------------|--------|------------|------------|-----------|-------|---------|----------|----------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12      | Bit 11     | Bit 10 | Bit 9      | Bit 8      | Bit 7     | Bit 6 | Bit 5   | Bit 4    | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| W0        | 0000  |        |        |        |             |            |        |            | W0 (WRI    | EG)       |       |         |          |          |          |       |       | xxxx          |

| W1        | 0002  |        |        |        |             |            |        |            | W1         |           |       |         |          |          |          |       |       | xxxx          |

| W2        | 0004  |        |        |        |             |            |        |            | W2         |           |       |         |          |          |          |       |       | xxxx          |

| W3        | 0006  |        |        |        |             |            |        |            | W3         |           |       |         |          |          |          |       |       | xxxx          |

| W4        | 8000  |        |        |        |             |            |        |            | W4         |           |       |         |          |          |          |       |       | xxxx          |

| W5        | 000A  |        |        |        |             |            |        |            | W5         |           |       |         |          |          |          |       |       | xxxx          |

| W6        | 000C  |        |        |        |             |            |        |            | W6         |           |       |         |          |          |          |       |       | xxxx          |

| W7        | 000E  |        |        |        |             |            |        |            | W7         |           |       |         |          |          |          |       |       | xxxx          |

| W8        | 0010  |        |        |        |             |            |        |            | W8         |           |       |         |          |          |          |       |       | xxxx          |

| W9        | 0012  |        |        |        |             |            |        |            | W9         |           |       |         |          |          |          |       |       | xxxx          |

| W10       | 0014  |        |        |        |             |            |        |            | W10        |           |       |         |          |          |          |       |       | xxxx          |

| W11       | 0016  |        |        |        |             |            |        |            | W11        |           |       |         |          |          |          |       |       | xxxx          |

| W12       | 0018  |        |        |        |             |            |        |            | W12        |           |       |         |          |          |          |       |       | xxxx          |

| W13       | 001A  |        |        |        |             |            |        |            | W13        |           |       |         |          |          |          |       |       | xxxx          |

| W14       | 001C  |        |        |        |             |            |        |            | W14        |           |       |         |          |          |          |       |       | xxxx          |

| W15       | 001E  |        |        |        |             |            |        |            | W15        |           |       |         |          |          |          |       |       | xxxx          |

| SPLIM     | 0020  |        |        |        |             |            |        |            | SPLIN      | 1         |       |         |          |          |          |       |       | 0000          |

| ACCAL     | 0022  |        |        |        |             |            |        |            | ACCA       | L         |       |         |          |          |          |       |       | 0000          |

| ACCAH     | 0024  |        |        |        |             |            |        |            | ACCA       | Н         |       |         |          |          |          |       |       | 0000          |

| ACCAU     | 0026  |        |        | Sig    | gn Extensio | n of ACCA< | 39>    |            |            |           |       |         | AC       | CAU      |          |       |       | 0000          |

| ACCBL     | 0028  |        |        |        |             |            |        |            | ACCB       | L         |       |         |          |          |          |       |       | 0000          |

| ACCBH     | 002A  |        |        |        |             |            |        |            | ACCBI      | Н         |       |         |          |          |          |       |       | 0000          |

| ACCBU     | 002C  |        |        | Sig    | gn Extensio | n of ACCB< | 39>    |            |            |           |       |         | AC       | CBU      |          |       |       | 0000          |

| PCL       | 002E  |        |        |        |             |            |        | Р          | CL<15:0>   |           |       |         |          |          |          |       | _     | 0000          |

| PCH       | 0030  | _      | _      | _      | _           | _          | _      | _          | _          | _         |       |         |          | PCH<6:0> |          |       | •     | 0000          |

| DSRPAG    | 0032  | _      | _      | _      | _           | _          | _      |            |            |           |       | DSRPAC  | G<9:0>   |          |          |       |       | 0001          |

| DSWPAG    | 0034  | _      | _      | _      | _           | _          | _      | _          |            |           |       | DS      | SWPAG<8: | 0>       |          |       |       | 0001          |

| RCOUNT    | 0036  |        |        |        |             |            | •      | •          | RCOUNT<    | 15:0>     |       |         |          |          |          |       |       | 0000          |

| DCOUNT    | 0038  |        |        |        |             |            |        |            | DCOUNT<    | 15:0>     |       |         |          |          |          |       |       | 0000          |

| DOSTARTL  | 003A  |        |        |        |             |            |        | DOS        | TARTL<15:1 | >         |       |         |          |          |          |       | _     | 0000          |

| DOSTARTH  | 003C  | _      | _      | _      | _           | _          | _      | _          | _          | _         | _     |         |          | DOSTAR   | RTH<5:0> |       | •     | 0000          |

| DOENDL    | 003E  |        |        |        |             |            | •      | DOI        | ENDL<15:1> |           |       |         |          |          |          |       | _     | 0000          |

| DOENDH    | 0040  | _      | _      | _      | _           | _          | _      | _          | _          | _         | _     |         |          | DOEND    | )H<5:0>  |       |       | 0000          |

|           |       |        | D1     |        |             | (a) D      |        |            |            |           |       |         |          |          |          |       |       |               |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-49: PORTD REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|--------|--------|-------|-------|-------|-------|-------|---------------|

| TRISD        | 0E30  | _      | _      | _      | _      | -      | _      | _     | TRISD8 | _     | TRISD6 | TRISD5 | _     |       | _     | _     | -     | 0160          |

| PORTD        | 0E32  | 1      | _      | _      | _      | _      | _      | _     | RD8    |       | RD6    | RD5    | 1     | -     | _     | _     | _     | xxxx          |

| LATD         | 0E34  | 1      | _      | _      | -      | ı      | ı      | -     | LATD8  | _     | LATD6  | LATD5  | -     | ı     | -     | _     | ı     | xxxx          |

| ODCD         | 0E36  | 1      | _      | _      | -      | ı      | ı      | -     | ODCD8  | _     | ODCD6  | ODCD5  | -     | ı     | -     | _     | ı     | 0000          |

| CNEND        | 0E38  | 1      | _      | _      | _      | _      | _      | _     | CNIED8 |       | CNIED6 | CNIED5 | 1     | -     | _     | _     | _     | 0000          |

| CNPUD        | 0E3A  | 1      | _      | _      | -      | ı      | ı      | -     | CNPUD8 | _     | CNPUD6 | CNPUD5 | -     | ı     | -     | _     | ı     | 0000          |

| CNPDD        | 0E3C  | 1      | _      | _      | -      | ı      | ı      | -     | CNPDD8 | _     | CNPDD6 | CNPDD5 | -     | ı     | -     | _     | ı     | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-50: PORTE REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| TRISE        | 0E40  | TRISE15 | TRISE14 | TRISE13 | TRISE12 | _      | -      | -     | _     | -     | -     | _     | -     | _     | _     | _     | _     | F000          |

| PORTE        | 0E42  | RE15    | RE14    | RE13    | RE12    | _      | -      | _     | _     | 1     | _     | _     | _     | _     | _     | _     | _     | xxxx          |

| LATE         | 0E44  | LATE15  | LATE14  | LATE13  | LATE12  | _      | I      | _     | _     |       | _     | _     | _     | _     | _     | _     | _     | xxxx          |

| ODCE         | 0E46  | ODCE15  | ODCE14  | ODCE13  | ODCE12  | -      | _      | _     | _     | 1     | _     | _     | _     | _     | _     |       | _     | 0000          |

| CNENE        | 0E48  | CNIEE15 | CNIEE14 | CNIEE13 | CNIEE12 | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     | 0000          |

| CNPUE        | 0E4A  | CNPUE15 | CNPUE14 | CNPUE13 | CNPUE12 | -      | _      | _     | _     | -     | _     | _     | _     | _     | _     | _     | _     | 0000          |

| CNPDE        | 0E4C  | CNPDE15 | CNPDE14 | CNPDE13 | CNPDE12 | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     | 0000          |

| ANSELE       | 0E4E  | ANSE15  | ANSE14  | ANSE13  | ANSE12  | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | _     | _     | F000          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-51: PORTF REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISF        | 0E50  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | TRISF1 | TRISF0 | 0003          |

| PORTF        | 0E52  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | RF1    | RF0    | xxxx          |

| LATF         | 0E54  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | LATF1  | LATF0  | xxxx          |

| ODCF         | 0E56  | I      | _      | _      | _      | -      | ı      | _     | _     | _     | _     | -     | I     | ı     | _     | ODCF1  | ODCF0  | 0000          |

| CNENF        | 0E58  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | CNIEF1 | CNIEF0 | 0000          |

| CNPUF        | 0E5A  | _      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | _     | _     | _     | CNPUF1 | CNPUF0 | 0000          |

| CNPDF        | 0E5C  | _      | _      | _      | _      | -      | _      | _     | _     | _     | _     | 1     | _     | _     | _     | CNPDF1 | CNPDF0 | 0000          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# REGISTER 8-7: DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-------|--------|-------|-------|-------|

|        |       |       | PAD<  | :15:8> |       |       |       |

| bit 15 |       |       |       |        |       |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

|       |       |       | PAD•  | <7:0> |       |       |       |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

## REGISTER 8-8: DMAXCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0                | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|----------------------|-------|-------|

| _      | _   |       |       | CNT<  | 13:8> <sup>(2)</sup> |       |       |

| bit 15 |     |       |       |       |                      |       | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0               | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|---------------------|-------|-------|-------|

|       |       |       | CNT<  | 7:0> <sup>(2)</sup> |       |       |       |

| bit 7 |       |       |       |                     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

2: The number of DMA transfers = CNT<13:0> + 1.

## REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| _      | _   |       |       | RP43  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| _     | _   |       |       | RP42  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 RP43R<5:0>: Peripheral Output Function is Assigned to RP43 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-6 Unimplemented: Read as '0'

bit 5-0 RP42R<5:0>: Peripheral Output Function is Assigned to RP42 Output Pin bits

(see Table 11-3 for peripheral function numbers)

#### REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| _      | _   |       |       | RP55  | R<5:0> |       |       |

| bit 15 | _   | _     | _     | _     |        | _     | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|--|

| _     | _   |       | RP54R<5:0> |       |       |       |       |  |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **RP55R<5:0>:** Peripheral Output Function is Assigned to RP55 Output Pin bits

(see Table 11-3 for peripheral function numbers)

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 RP54R<5:0>: Peripheral Output Function is Assigned to RP54 Output Pin bits

(see Table 11-3 for peripheral function numbers)

| sPIC33EPXXXG | P50X, dsPIC3 | 3EPXXXMC2 | 0X/50X AND | PIC24EPXX | XGP/MC20X |

|--------------|--------------|-----------|------------|-----------|-----------|

| OTES:        |              |           |            |           |           |

|              |              |           |            |           |           |

|              |              |           |            |           |           |

|              |              |           |            |           |           |

|              |              |           |            |           |           |

|              |              |           |            |           |           |

|              |              |           |            |           |           |

|              |              |           |            |           |           |

|              |              |           |            |           |           |

|              |              |           |            |           |           |

|              |              |           |            |           |           |

|              |              |           |            |           |           |

|              |              |           |            |           |           |

|              |              |           |            |           |           |

|              |              |           |            |           |           |

|              |              |           |            |           |           |

|              |              |           |            |           |           |

#### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

| U-0    | U-0 | U-0                   | R/W-0 | R/W-0  | R/W-0 | R/W-0              | R/W-0 |

|--------|-----|-----------------------|-------|--------|-------|--------------------|-------|

| _      | _   | — DISSCK DISSDO MODE1 |       | MODE16 | SMP   | CKE <sup>(1)</sup> |       |

| bit 15 |     |                       |       |        |       |                    | bit 8 |

| R/W-0               | R/W-0 | R/W-0 | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|---------------------|-------|-------|----------------------|----------------------|----------------------|----------------------|----------------------|

| SSEN <sup>(2)</sup> | CKP   | MSTEN | SPRE2 <sup>(3)</sup> | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |

| bit 7               |       |       |                      |                      |                      |                      | bit 0                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-13 **Unimplemented:** Read as '0'

bit 12 **DISSCK:** Disable SCKx Pin bit (SPIx Master modes only)

1 = Internal SPIx clock is disabled, pin functions as I/O

0 = Internal SPIx clock is enabled

bit 11 DISSDO: Disable SDOx Pin bit

1 = SDOx pin is not used by the module; pin functions as I/O

0 = SDOx pin is controlled by the module

bit 10 MODE16: Word/Byte Communication Select bit

1 = Communication is word-wide (16 bits)

0 = Communication is byte-wide (8 bits)

bit 9 SMP: SPIx Data Input Sample Phase bit

Master mode:

1 = Input data is sampled at end of data output time

0 = Input data is sampled at middle of data output time

Slave mode:

SMP must be cleared when SPIx is used in Slave mode.

bit 8 **CKE:** SPIx Clock Edge Select bit<sup>(1)</sup>

1 = Serial output data changes on transition from active clock state to Idle clock state (refer to bit 6)

0 = Serial output data changes on transition from Idle clock state to active clock state (refer to bit 6)

bit 7 SSEN: Slave Select Enable bit (Slave mode)(2)

$1 = \overline{SSx}$  pin is used for Slave mode

$0 = \overline{SSx}$  pin is not used by the module; pin is controlled by port function

bit 6 **CKP:** Clock Polarity Select bit

${\tt 1}$  = Idle state for clock is a high level; active state is a low level

0 = Idle state for clock is a low level; active state is a high level

bit 5 MSTEN: Master Mode Enable bit

1 = Master mode

0 = Slave mode

Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

2: This bit must be cleared when FRMEN = 1.

3: Do not set both primary and secondary prescalers to the value of 1:1.

DS70000657H-page 274

## 21.2 Modes of Operation

The ECAN module can operate in one of several operation modes selected by the user. These modes include:

- · Initialization mode

- · Disable mode

- · Normal Operation mode

- · Listen Only mode

- · Listen All Messages mode

- · Loopback mode

Modes are requested by setting the REQOP<2:0> bits (CxCTRL1<10:8>). Entry into a mode is Acknowledged by monitoring the OPMODE<2:0> bits (CxCTRL1<7:5>). The module does not change the mode and the OPMODEx bits until a change in mode is acceptable, generally during bus Idle time, which is defined as at least 11 consecutive recessive bits.

#### 21.3 ECAN Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/Devices.aspx?dDocName=en555464

#### 21.3.1 KEY RESOURCES

- "Enhanced Controller Area Network (ECAN™)" (DS70353) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

## 24.3 PTG Control Registers

#### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER

| R/W-0  | U-0 | R/W-0   | R/W-0   | U-0 | R/W-0                 | R/W-0                  | R/W-0   |

|--------|-----|---------|---------|-----|-----------------------|------------------------|---------|

| PTGEN  | _   | PTGSIDL | PTGTOGL | _   | PTGSWT <sup>(2)</sup> | PTGSSEN <sup>(3)</sup> | PTGIVIS |

| bit 15 |     |         |         |     |                       |                        | bit 8   |

| R/W-0   | HS-0        | U-0 | U-0 | U-0 | U-0 | R/V                    | V-0                    |  |  |  |

|---------|-------------|-----|-----|-----|-----|------------------------|------------------------|--|--|--|

| PTGSTRT | PTGWDTO     | _   | _   | _   | _   | PTGITM1 <sup>(1)</sup> | PTGITM0 <sup>(1)</sup> |  |  |  |

| bit 7   | bit 7 bit 0 |     |     |     |     |                        |                        |  |  |  |

| Legend:           | HS = Hardware Settable bit |                                                     |                    |  |  |  |

|-------------------|----------------------------|-----------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit           | W = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared                                | x = Bit is unknown |  |  |  |

bit 15 **PTGEN:** Module Enable bit

1 = PTG module is enabled

0 = PTG module is disabled

bit 14 **Unimplemented:** Read as '0'

bit 13 PTGSIDL: PTG Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 PTGTOGL: PTG TRIG Output Toggle Mode bit

1 = Toggle state of the PTGOx for each execution of the PTGTRIG command

0 = Each execution of the PTGTRIG command will generate a single PTGOx pulse determined by the value in the PTGPWDx bits

bit 11 **Unimplemented:** Read as '0'

bit 10 **PTGSWT:** PTG Software Trigger bit<sup>(2)</sup>

1 = Triggers the PTG module

0 = No action (clearing this bit will have no effect)

bit 9 **PTGSSEN:** PTG Enable Single-Step bit<sup>(3)</sup>

1 = Enables Single-Step mode0 = Disables Single-Step mode

PTGIVIS: PTG Counter/Timer Visibility Control bit

1 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the current values of their corresponding counter/timer registers (PTGSD, PTGCx, PTGTx)

0 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the value previously written to those limit registers

bit 7 PTGSTRT: PTG Start Sequencer bit

1 = Starts to sequentially execute commands (Continuous mode)

0 = Stops executing commands

bit 6 **PTGWDTO:** PTG Watchdog Timer Time-out Status bit

1 = PTG Watchdog Timer has timed out 0 = PTG Watchdog Timer has not timed out.

bit 5-2 **Unimplemented:** Read as '0'

**Note 1:** These bits apply to the PTGWHI and PTGWLO commands only.

2: This bit is only used with the PTGCTRL step command software trigger option.

3: Use of the PTG Single-Step mode is reserved for debugging tools only.

bit 8

TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax             | Description                                    | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|---------|-----------------------------|------------------------------------------------|---------------|-------------------------------|--------------------------|

| 52                 | MUL                  |         |                             | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)       | 1             | 1                             | None                     |

|                    |                      | MUL.SS  | Wb, Ws, Acc <sup>(1)</sup>  | Accumulator = signed(Wb) * signed(Ws)          | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)     | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,Ws,Acc <sup>(1)</sup>    | Accumulator = signed(Wb) * unsigned(Ws)        | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Acc <sup>(1)</sup> | Accumulator = signed(Wb) * unsigned(lit5)      | 1             | 1                             | None                     |

|                    |                      | MUL.US  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)     | 1             | 1                             | None                     |

|                    |                      | MUL.US  | Wb,Ws,Acc <sup>(1)</sup>    | Accumulator = unsigned(Wb) * signed(Ws)        | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(Ws)   | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Acc <sup>(1)</sup> | Accumulator = unsigned(Wb) * unsigned(lit5)    | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,Ws,Acc <sup>(1)</sup>    | Accumulator = unsigned(Wb) * unsigned(Ws)      | 1             | 1                             | None                     |

|                    |                      | MULW.SS | Wb, Ws, Wnd                 | Wnd = signed(Wb) * signed(Ws)                  | 1             | 1                             | None                     |

|                    |                      | MULW.SU | Wb, Ws, Wnd                 | Wnd = signed(Wb) * unsigned(Ws)                | 1             | 1                             | None                     |

|                    |                      | MULW.US | Wb, Ws, Wnd                 | Wnd = unsigned(Wb) * signed(Ws)                | 1             | 1                             | None                     |

|                    |                      | MULW.UU | Wb, Ws, Wnd                 | Wnd = unsigned(Wb) * unsigned(Ws)              | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Wnd                | {Wnd + 1, Wnd} = signed(Wb) * unsigned(lit5)   | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Wnd                | Wnd = signed(Wb) * unsigned(lit5)              | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Wnd                | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(lit5) | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Wnd                | Wnd = unsigned(Wb) * unsigned(lit5)            | 1             | 1                             | None                     |

|                    |                      | MUL     | f                           | W3:W2 = f * WREG                               | 1             | 1                             | None                     |

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

<sup>2:</sup> Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

TABLE 30-22: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                                                                | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                     |      |       |                                                                                                             |  |

|--------------------|-----------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|-------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol    | Characteristic <sup>(1)</sup>                                  | Min.                                                                                                                                                                                                                                             | Typ. <sup>(2)</sup> | Max. | Units | Conditions                                                                                                  |  |

| SY00               | Tpu       | Power-up Period                                                | _                                                                                                                                                                                                                                                | 400                 | 600  | μS    |                                                                                                             |  |

| SY10               | Tost      | Oscillator Start-up Time                                       |                                                                                                                                                                                                                                                  | 1024 Tosc           |      | _     | Tosc = OSC1 period                                                                                          |  |

| SY12               | TWDT      | Watchdog Timer<br>Time-out Period                              | 0.81                                                                                                                                                                                                                                             | 0.98                | 1.22 | ms    | WDTPRE = 0,<br>WDTPOST<3:0> = 0000, using<br>LPRC tolerances indicated in F21<br>(see Table 30-20) at +85°C |  |

|                    |           |                                                                | 3.26                                                                                                                                                                                                                                             | 3.91                | 4.88 | ms    | WDTPRE = 1,<br>WDTPOST<3:0> = 0000, using<br>LPRC tolerances indicated in F21<br>(see Table 30-20) at +85°C |  |

| SY13               | Tioz      | I/O High-Impedance<br>from MCLR Low or<br>Watchdog Timer Reset | 0.68                                                                                                                                                                                                                                             | 0.72                | 1.2  | μS    |                                                                                                             |  |

| SY20               | TMCLR     | MCLR Pulse Width (low)                                         | 2                                                                                                                                                                                                                                                | _                   |      | μS    |                                                                                                             |  |

| SY30               | TBOR      | BOR Pulse Width (low)                                          | 1                                                                                                                                                                                                                                                | _                   | _    | μS    |                                                                                                             |  |

| SY35               | TFSCM     | Fail-Safe Clock Monitor Delay                                  | _                                                                                                                                                                                                                                                | 500                 | 900  | μS    | -40°C to +85°C                                                                                              |  |

| SY36               | TVREG     | Voltage Regulator<br>Standby-to-Active mode<br>Transition Time |                                                                                                                                                                                                                                                  | _                   | 30   | μS    |                                                                                                             |  |

| SY37               | Toscdfrc  | FRC Oscillator Start-up<br>Delay                               | 46                                                                                                                                                                                                                                               | 48                  | 54   | μS    |                                                                                                             |  |

| SY38               | Toscolprc | LPRC Oscillator Start-up<br>Delay                              | _                                                                                                                                                                                                                                                | _                   | 70   | μS    |                                                                                                             |  |

Note 1: These parameters are characterized but not tested in manufacturing.

<sup>2:</sup> Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

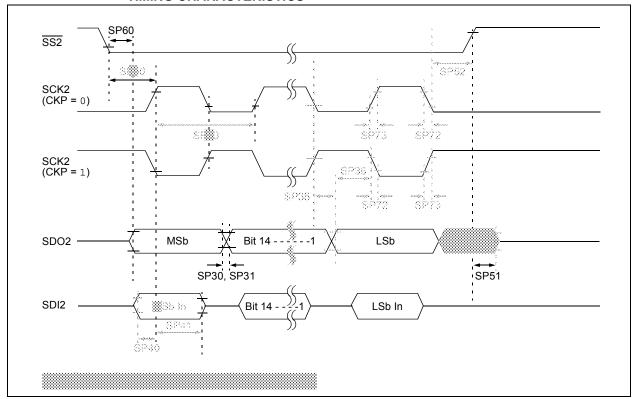

FIGURE 30-18: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

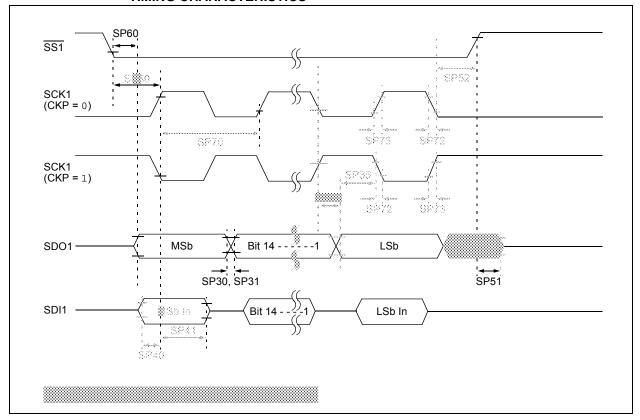

FIGURE 30-27: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0)

TIMING CHARACTERISTICS

#### 33.0 PACKAGING INFORMATION

## 33.1 Package Marking Information

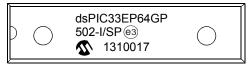

#### 28-Lead SPDIP

#### Example

## 28-Lead SOIC (.300")

## Example

#### 28-Lead SSOP

#### Example

## 28-Lead QFN-S (6x6x0.9 mm)

## Example

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3)

can be found on the outer packaging for this package.

**Note:** In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

## 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units            |          |          | S    |  |

|-------------------------|------------------|----------|----------|------|--|

| Dimension               | Dimension Limits |          |          |      |  |

| Number of Pins          | N                |          | 44       |      |  |

| Pitch                   | е                |          | 0.65 BSC |      |  |

| Overall Height          | Α                | 0.80     | 0.90     | 1.00 |  |

| Standoff                | A1               | 0.00     | 0.02     | 0.05 |  |

| Terminal Thickness      | A3               | 0.20 REF |          |      |  |

| Overall Width           | E                |          | 8.00 BSC |      |  |

| Exposed Pad Width       | E2               | 6.25     | 6.45     | 6.60 |  |

| Overall Length          | D                |          | 8.00 BSC |      |  |

| Exposed Pad Length      | D2               | 6.25     | 6.45     | 6.60 |  |

| Terminal Width          | р                | 0.20     | 0.30     | 0.35 |  |

| Terminal Length         | L                | 0.30     | 0.40     | 0.50 |  |

| Terminal-to-Exposed-Pad | K                | 0.20     | -        | -    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension. usually without tolerance. for information purposes only.

Microchip Technology Drawing C04-103C Sheet 2 of 2

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV == ISO/TS 16949 ==

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2011-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620773949

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.