Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64gp506t-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33EP64MC506 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70598)

- "Timers" (DS70362)

- "Input Capture" (DS70352)

- "Output Compare" (DS70358)

- "High-Speed PWM" (DS70645)

- "Quadrature Encoder Interface (QEI)" (DS70601)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70582)

- "Serial Peripheral Interface (SPI)" (DS70569)

- "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70330)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "CodeGuard™ Security" (DS70634)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70357)

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Device Configuration" (DS70618)

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 3 MHz <  $F_{IN}$  < 5.5 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLFBD, to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration Word.

### 2.8 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state.

Alternatively, connect a 1k to 10k resistor between Vss and unused pins, and drive the output to logic low.

### 2.9 Application Examples

- · Induction heating

- Uninterruptable Power Supplies (UPS)

- DC/AC inverters

- · Compressor motor control

- · Washing machine 3-phase motor control

- BLDC motor control

- · Automotive HVAC, cooling fans, fuel pumps

- Stepper motor control

- · Audio and fluid sensor monitoring

- · Camera lens focus and stability control

- Speech (playback, hands-free kits, answering machines, VoIP)

- Consumer audio

- Industrial and building control (security systems and access control)

- · Barcode reading

- Networking: LAN switches, gateways

- Data storage device management

- · Smart cards and smart card readers

Examples of typical application connections are shown in Figure 2-4 through Figure 2-8.

### FIGURE 2-4: BOOST CONVERTER IMPLEMENTATION

#### **TABLE 4-3**: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| TADLL        | τу.   |        |        |            | VELEN  |        |        |            |        |       |         | DEVICE      |         |         |          |              |         |               |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|---------|-------------|---------|---------|----------|--------------|---------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2    | Bit 1        | Bit 0   | All<br>Resets |

| IFS0         | 0800  |        | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF   | IC2IF       | DMA0IF  | T1IF    | OC1IF    | IC1IF        | INTOIF  | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _       | —           | INT1IF  | CNIF    | CMIF     | MI2C1IF      | SI2C1IF | 0000          |

| IFS2         | 0804  |        | _      | _          | -      |        | _      | —          | _      | _     | IC4IF   | IC3IF       | DMA3IF  | _       | —        | SPI2IF       | SPI2EIF | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      | _      | _          | _      | _     | _       | _           | _       | _       | MI2C2IF  | SI2C2IF      | _       | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | _      | _      | _          | _      | _     | _       | _           | _       | CRCIF   | U2EIF    | U1EIF        | _       | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  |            | _      | _      | _      | _          | —      | _     | _       | _           | _       | _       | —        | —            | —       | 0000          |

| IFS9         | 0812  | _      | _      | _          | _      | _      | _      | _          | —      | _     | PTG3IF  | PTG2IF      | PTG1IF  | PTG0IF  | PTGWDTIF | PTGSTEPIF    | —       | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE   | IC2IE       | DMA0IE  | T1IE    | OC1IE    | IC1IE        | INT0IE  | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _       | _           | INT1IE  | CNIE    | CMIE     | MI2C1IE      | SI2C1IE | 0000          |

| IEC2         | 0824  | _      | _      | _          | _      | _      | _      | _          | _      | _     | IC4IE   | IC3IE       | DMA3IE  | _       | _        | SPI2IE       | SPI2EIE | 0000          |

| IEC3         | 0826  | _      | _      | _          | _      | _      | _      | _          | —      | _     | _       | _           | _       | _       | MI2C2IE  | SI2C2IE      | —       | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | _      | _      | _      | _          | _      | _     | _       | _           | _       | CRCIE   | U2EIE    | U1EIE        | _       | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _      | _      | _      | _          | _      | _     | _       | _           | _       | _       | _        | _            | _       | 0000          |

| IEC9         | 0832  | _      | _      | _          | _      | _      | _      | _          | —      | _     | PTG3IE  | PTG2IE      | PTG1IE  | PTG0IE  | PTGWDTIE | PTGSTEPIE    | _       | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      | (      | OC1IP<2:0  | >      | _     |         | IC1IP<2:0>  |         | —       |          | INT0IP<2:0>  |         | 4444          |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      | (      | OC2IP<2:0  | >      | _     |         | IC2IP<2:0>  |         | _       | C        | 0MA0IP<2:0>  |         | 4444          |

| IPC2         | 0844  | _      | U      | J1RXIP<2:0 | >      | _      | ;      | SPI1IP<2:0 | >      | _     |         | SPI1EIP<2:0 | >       | _       |          | T3IP<2:0>    |         | 4444          |

| IPC3         | 0846  | _      | _      | _          | _      | _      | D      | )MA1IP<2:  | 0>     | _     |         | AD1IP<2:0>  |         | _       | ι        | J1TXIP<2:0>  |         | 0444          |

| IPC4         | 0848  |        |        | CNIP<2:0>  |        |        |        | CMIP<2:0   | >      | _     |         | MI2C1IP<2:0 | >       | _       | S        | SI2C1IP<2:0> |         | 4444          |

| IPC5         | 084A  | _      | _      | _          | _      | _      | _      | _          | _      | _     | _       | —           | _       | _       | I        | INT1IP<2:0>  |         | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      | (      | OC4IP<2:0  | >      | _     |         | OC3IP<2:0>  |         | _       | C        | )ma2IP<2:0>  |         | 4444          |

| IPC7         | 084E  |        | I      | U2TXIP<2:0 | >      |        | L      | J2RXIP<2:  | )>     | _     |         | INT2IP<2:0> |         | _       |          | T5IP<2:0>    |         | 4444          |

| IPC8         | 0850  |        | _      | _          | _      |        | _      | —          | —      | _     |         | SPI2IP<2:0> |         | _       | S        | SPI2EIP<2:0> |         | 0044          |

| IPC9         | 0852  |        | _      | _          |        |        |        | IC4IP<2:0  | >      | _     |         | IC3IP<2:0>  |         | _       | C        | 0MA3IP<2:0>  |         | 0444          |

| IPC12        | 0858  |        | _      | _          |        |        | N      | 112C2IP<2: | 0>     | _     |         | SI2C2IP<2:0 | >       | _       | _        | _            | _       | 0440          |

| IPC16        | 0860  |        |        | CRCIP<2:0> | >      |        |        | U2EIP<2:0  | >      | _     |         | U1EIP<2:0>  |         | _       | _        | _            | _       | 4440          |

| IPC19        | 0866  |        | _      | _          | _      | _      | _      | _          | _      | _     |         | CTMUIP<2:0  | >       | _       | _        | _            | _       | 0040          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >      | _     | _       | _           | _       | _       | _        | _            | _       | 4400          |

| IPC36        | 0888  | _      |        | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>   | _     | P       | TGSTEPIP<2  | :0>     | _       | _        | —            | _       | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | PTG3IP<2:  | )>     | _     |         | PTG2IP<2:0  | >       | _       | F        | PTG1IP<2:0>  |         | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | _      |        |        |            | —      | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR   | OSCFAIL      |         | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      |        |        |            | _      | _     |         | —           | —       | _       | INT2EP   | INT1EP       | INT0EP  | 8000          |

| INTCON3      | 08C4  | _      | _      |            | _      |        |        | _          | _      | _     | _       | DAE         | DOOVR   | _       | _        | —            |         | 0000          |

| INTCON4      | 08C6  |        | _      | _          | _      | _      | _      | —          | _      |       |         |             | SGHT    | 0000    |          |              |         |               |

| INTTREG      | 08C8  | _      |        |            | _      |        | ILR<   | 3:0>       |        |       |         |             | VECN    | UM<7:0> |          |              |         | 0000          |

|              |       |        |        |            |        |        |        |            |        |       |         |             |         |         |          |              |         |               |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

### TABLE 4-34: NVM REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7           | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1   | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|---------|--------|--------|-------|-------|-----------------|-------|-------|-------|-------|-------|---------|-------|---------------|

| NVMCON    | 0728  | WR     | WREN   | WRERR  | NVMSIDL | _      | _      | —     | _     | _               | _     | _     | —     |       | NVMC  | )P<3:0> |       | 0000          |

| NVMADRL   | 072A  |        |        |        |         |        |        |       | NVMAD | )R<15:0>        |       |       |       |       |       |         |       | 0000          |

| NVMADRH   | 072C  | _      | _      | _      | _       | -      | _      | _     | _     | — NVMADR<23:16> |       |       |       |       |       |         |       |               |

| NVMKEY    | 072E  |        |        | _      | —       | _      |        | —     | -     |                 |       |       |       |       |       |         |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-35: SYSTEM CONTROL REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10      | Bit 9     | Bit 8         | Bit 7          | Bit 6  | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|-----------|--------|--------|-------------|-----------|---------------|----------------|--------|--------|-------|-------|--------|-------|-------|---------------|

| RCON      | 0740  | TRAPR  | IOPUWR | _         | _      | VREGSF | _           | СМ        | VREGS         | EXTR           | SWR    | SWDTEN | WDTO  | SLEEP | IDLE   | BOR   | POR   | Note 1        |

| OSCCON    | 0742  | _      | 0      | COSC<2:0> |        | —      |             | NOSC<2:0> |               | CLKLOCK        | IOLOCK | LOCK   | _     | CF    | _      | _     | OSWEN | Note 2        |

| CLKDIV    | 0744  | ROI    | [      | OOZE<2:0> |        | DOZEN  | FRCDIV<2:0> |           |               | PLLPOS         | T<1:0> | _      |       | F     | LLPRE< | 4:0>  |       | 0030          |

| PLLFBD    | 0746  | _      | _      | _         | _      | —      | _           | _         | – PLLDIV<8:0> |                |        |        | 0030  |       |        |       |       |               |

| OSCTUN    | 0748  | _      | _      | _         | _      | —      | _           | _         | _             | — — — TUN<5:0> |        |        |       |       |        |       | 0000  |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values are dependent on the type of Reset.

2: OSCCON register Reset values are dependent on the Configuration Fuses.

### TABLE 4-36: REFERENCE CLOCK REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|---------------|

| REFOCON   | 074E  | ROON   | —      | ROSSLP | ROSEL  | RODIV<3:0> |        |       | _     | _     | —     | _     | _     | —     | _     | -     | 0000  |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-56: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      |        | _      | _     | TRISA8 | _     | —     | —     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 011F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     | RA8    | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     | LATA8  | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     | ODCA8  | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     | CNIEA8 | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     | CNPUA8 | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     | CNPDA8 | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | —      | _     | —      | _     | —     | —     | ANSA4  | —      | —      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-57: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | -       | _       | -       | —       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-58: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      | _      | _      | —      | —     | TRISC8 | _     | _     |       | _     |       | -     | TRISC1 | TRISC0 | 0103          |

| PORTC        | 0E22  |        |        | -      | -      | -      | —      | _     | RC8    | —     | -     |       | _     |       |       | RC1    | RC0    | xxxx          |

| LATC         | 0E24  |        |        | _      | _      | _      | _      | _     | LATC8  | _     | _     | _     | _     | _     | _     | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  |        |        | _      | _      | _      | _      | _     | ODCC8  | _     | _     | _     | _     | _     | _     | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | —      | _      | -      | _      |        | _      | _     | CNIEC8 | —     |       |       | _     |       |       | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  |        |        | _      | _      | _      | _      | _     | CNPUC8 | _     | _     | _     | _     | _     | _     | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  |        |        | _      | _      | _      | _      | _     | CNPDC8 | _     | _     | _     | _     | _     | _     | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | -      | _      | _      | _      | _      | —      | —     | —      | —     |       | _     | _     | _     |       | ANSC1  | ANSC0  | 0003          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer is complete)

- DMA request for each channel can be selected from any supported interrupt source

- Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|-------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0   | 00000000                             | _                                                       | _                                                      |

| IC1 – Input Capture 1         | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2         | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3         | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4         | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1        | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2        | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3        | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4        | 00011010                             | —                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                 | 00000111                             | _                                                       | _                                                      |

| TMR3 – Timer3                 | 00001000                             | —                                                       | _                                                      |

| TMR4 – Timer4                 | 00011011                             | —                                                       | _                                                      |

| TMR5 – Timer5                 | 00011100                             | —                                                       | —                                                      |

| SPI1 Transfer Done            | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |

| SPI2 Transfer Done            | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |

| UART1RX – UART1 Receiver      | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter   | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver      | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter   | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |

| ECAN1 – RX Data Ready         | 00100010                             | 0x0440 (C1RXD)                                          | _                                                      |

| ECAN1 – TX Data Request       | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |

| ADC1 – ADC1 Convert Done      | 00001101                             | 0x0300 (ADC1BUF0)                                       | —                                                      |

### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0                                       | U-0              | U-0             | U-0              | U-0              | U-0             | R/W-0   |

|-----------------|-------------------------------------------|------------------|-----------------|------------------|------------------|-----------------|---------|

| _               | —                                         | —                |                 | —                | —                | —               | PLLDIV8 |

| bit 15          |                                           |                  |                 |                  |                  |                 | bit 8   |

|                 |                                           |                  |                 |                  |                  |                 |         |

| R/W-0           | R/W-0                                     | R/W-1            | R/W-1           | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| PLLDIV7         | PLLDIV6                                   | PLLDIV5          | PLLDIV4         | PLLDIV3          | PLLDIV2          | PLLDIV1         | PLLDIV0 |

| bit 7           |                                           |                  |                 |                  |                  |                 | bit 0   |

|                 |                                           |                  |                 |                  |                  |                 |         |

| Legend:         |                                           |                  |                 |                  |                  |                 |         |

| R = Readable    | bit                                       | W = Writable     | bit             | U = Unimpler     | mented bit, read | as '0'          |         |

| -n = Value at P | OR                                        | '1' = Bit is set |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown    |

|                 |                                           |                  |                 |                  |                  |                 |         |

| bit 15-9        | Unimplemen                                | ted: Read as '   | 0'              |                  |                  |                 |         |

| bit 8-0         | PLLDIV<8:0>                               | : PLL Feedba     | ck Divisor bits | (also denoted    | as 'M', PLL mul  | tiplier)        |         |

|                 | 111111111 =                               | = 513            |                 |                  |                  |                 |         |

|                 | •                                         |                  |                 |                  |                  |                 |         |

|                 | •                                         |                  |                 |                  |                  |                 |         |

|                 | •                                         |                  |                 |                  |                  |                 |         |

|                 | 000110000 =                               | = 50 (default)   |                 |                  |                  |                 |         |

|                 |                                           |                  |                 |                  |                  |                 |         |

|                 | •                                         |                  |                 |                  |                  |                 |         |

|                 | 000000010 =<br>000000001 =<br>000000000 = | = 3              |                 |                  |                  |                 |         |

|                 |                                           |                  |                 |                  |                  |                 |         |

### REGISTER 9-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER

### 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

### 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER     | <u>R 10-2: PMD</u> 2 | 2: PERIPHER                                         | AL MODULE       | DISABLE C         | ONTROL RE       | GISTER 2        |       |

|--------------|----------------------|-----------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|

| U-0          | U-0                  | U-0                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| _            |                      | —                                                   |                 | IC4MD             | IC3MD           | IC2MD           | IC1MD |

| bit 15       |                      |                                                     |                 |                   |                 |                 | bit   |

| U-0          | U-0                  | U-0                                                 | U-0             | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|              |                      |                                                     |                 | OC4MD             | OC3MD           | OC2MD           | OC1MD |

| bit 7        |                      |                                                     |                 |                   |                 |                 | bit   |

|              |                      |                                                     |                 |                   |                 |                 |       |

| Legend:      | 1.1.1                |                                                     |                 |                   |                 |                 |       |

| R = Readab   |                      | W = Writable b                                      | Dit             | •                 | nented bit, rea |                 |       |

| -n = Value a | at POR               | '1' = Bit is set                                    |                 | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

| bit 15-12    | Unimplemen           | ted: Read as '0                                     | ,               |                   |                 |                 |       |

| bit 11       | -                    | t Capture 4 Mod                                     |                 |                   |                 |                 |       |

|              | •                    | ture 4 module is                                    |                 |                   |                 |                 |       |

|              | 0 = Input Cap        | oture 4 module is                                   | s enabled       |                   |                 |                 |       |

| bit 10       | IC3MD: Input         | t Capture 3 Mod                                     | ule Disable bit |                   |                 |                 |       |

|              |                      | oture 3 module is                                   |                 |                   |                 |                 |       |

|              |                      | oture 3 module is                                   |                 |                   |                 |                 |       |

| bit 9        |                      | Capture 2 Mod                                       |                 |                   |                 |                 |       |

|              |                      | oture 2 module is<br>oture 2 module is              |                 |                   |                 |                 |       |

| bit 8        | IC1MD: Input         | t Capture 1 Mod                                     | ule Disable bit |                   |                 |                 |       |

|              | 1 = Input Cap        | oture 1 module is<br>oture 1 module is              | s disabled      |                   |                 |                 |       |

| bit 7-4      |                      | ted: Read as '0                                     |                 |                   |                 |                 |       |

| bit 3        | OC4MD: Out           | put Compare 4                                       | Module Disable  | e bit             |                 |                 |       |

|              |                      | ompare 4 modul                                      |                 |                   |                 |                 |       |

|              | -                    | ompare 4 modu                                       |                 |                   |                 |                 |       |

| bit 2        |                      | put Compare 3                                       |                 | e bit             |                 |                 |       |

|              | •                    | ompare 3 modul                                      |                 |                   |                 |                 |       |

| L:1 4        | -                    | ompare 3 modul                                      |                 | . h.:4            |                 |                 |       |

| bit 1        |                      | put Compare 2                                       |                 |                   |                 |                 |       |

|              | $\perp$ – Output Co  | ompare 2 modu                                       |                 |                   |                 |                 |       |

|              | 0 = Output Co        | ompare 2 modul                                      | le is enabled   |                   |                 |                 |       |

| bit 0        | •                    | ompare 2 modul<br>put Compare 1                     |                 | e bit             |                 |                 |       |

| bit 0        | OC1MD: Out           | ompare 2 modul<br>put Compare 1 l<br>ompare 1 modul | Module Disable  | e bit             |                 |                 |       |

#### ~

### REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER (CONTINUED)

- bit 2 INDEX: Status of INDXx Input Pin After Polarity Control

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 1 QEB: Status of QEBx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1' 0 = Pin is at logic '0'

- bit 0 **QEA:** Status of QEAx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

### 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Serial Peripheral Interface (SPI)" (DS70569) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The SPI module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices can be serial EEPROMs, shift registers, display drivers, ADC Converters, etc. The SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X device family offers two SPI modules on a single device. These modules, which are designated as SPI1 and SPI2, are functionally identical. Each SPI module includes an eight-word FIFO buffer and allows DMA bus connections. When using the SPI module with DMA, FIFO operation can be disabled.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 and SPI2 modules.

The SPI1 module uses dedicated pins which allow for a higher speed when using SPI1. The SPI2 module takes advantage of the Peripheral Pin Select (PPS) feature to allow for greater flexibility in pin configuration of the SPI2 module, but results in a lower maximum speed for SPI2. See **Section 30.0** "**Electrical Characteristics**" for more information.

The SPIx serial interface consists of four pins, as follows:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx/FSYNCx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPIx module can be configured to operate with two, three or four pins. In 3-pin mode, SSx is not used. In 2-pin mode, neither SDOx nor SSx is used.

Figure 18-1 illustrates the block diagram of the SPIx module in Standard and Enhanced modes.

| -             |           |                 |            |                   |                  |                    |                       |

|---------------|-----------|-----------------|------------|-------------------|------------------|--------------------|-----------------------|

| R-0, HSC      | R-0, HSC  | U-0             | U-0        | U-0               | R/C-0, HS        | R-0, HSC           | R-0, HSC              |

| ACKSTAT       | TRSTAT    | —               | —          | —                 | BCL              | GCSTAT             | ADD10                 |

| bit 15        |           |                 |            |                   |                  |                    | bit 8                 |

|               |           |                 |            |                   |                  |                    |                       |

| R/C-0, HS     | R/C-0, HS | R-0, HSC        | R/C-0, HSC | R/C-0, HSC        | R-0, HSC         | R-0, HSC           | R-0, HSC              |

| IWCOL         | I2COV     | D_A             | Р          | S                 | R_W              | RBF                | TBF                   |

| bit 7         |           |                 |            |                   |                  |                    | bit 0                 |

|               |           |                 |            |                   |                  |                    |                       |

| Legend:       |           | C = Clearab     | le bit     | HS = Hardwa       | re Settable bit  | HSC = Hardware S   | ettable/Clearable bit |

| R = Readab    | le bit    | W = Writable    | e bit      | U = Unimplen      | nented bit, read | as '0'             |                       |

| -n = Value at | t POR     | '1' = Bit is se | et         | '0' = Bit is clea | ared             | x = Bit is unknown |                       |

### REGISTER 19-2: I2CxSTAT: I2Cx STATUS REGISTER

| bit 1E    | ACKSTAT: Acknowledge Status bit (when operating as I <sup>2</sup> C™ master, applicable to master transmit operation)                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | 1 = NACK received from slave                                                                                                                                          |

|           | 0 = ACK received from slave                                                                                                                                           |

|           | Hardware is set or clear at the end of slave Acknowledge.                                                                                                             |

| bit 14    | <b>TRSTAT:</b> Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                                               |

|           | 1 = Master transmit is in progress (8 bits + ACK)                                                                                                                     |

|           | 0 = Master transmit is not in progress                                                                                                                                |

|           | Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.                                                           |

| bit 13-11 | Unimplemented: Read as '0'                                                                                                                                            |

| bit 10    | BCL: Master Bus Collision Detect bit                                                                                                                                  |

|           | <ul> <li>1 = A bus collision has been detected during a master operation</li> <li>0 = No bus collision detected</li> </ul>                                            |

|           | Hardware is set at detection of a bus collision.                                                                                                                      |

| bit 9     | GCSTAT: General Call Status bit                                                                                                                                       |

|           | 1 = General call address was received                                                                                                                                 |

|           | 0 = General call address was not received                                                                                                                             |

|           | Hardware is set when address matches general call address. Hardware is clear at Stop detection.                                                                       |

| bit 8     | ADD10: 10-Bit Address Status bit                                                                                                                                      |

|           | 1 = 10-bit address was matched                                                                                                                                        |

|           | <ul> <li>0 = 10-bit address was not matched</li> <li>Hardware is set at the match of the 2nd byte of the matched 10-bit address. Hardware is clear at Stop</li> </ul> |

|           | detection.                                                                                                                                                            |

| bit 7     | IWCOL: I2Cx Write Collision Detect bit                                                                                                                                |

|           | 1 = An attempt to write to the I2CxTRN register failed because the I <sup>2</sup> C module is busy                                                                    |

|           | 0 = No collision                                                                                                                                                      |

| L:1 0     | Hardware is set at the occurrence of a write to I2CxTRN while busy (cleared by software).                                                                             |

| bit 6     | <b>I2COV:</b> I2Cx Receive Overflow Flag bit                                                                                                                          |

|           | <ul> <li>1 = A byte was received while the I2CxRCV register was still holding the previous byte</li> <li>0 = No overflow</li> </ul>                                   |

|           | Hardware is set at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                                                   |

| bit 5     | <b>D_A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                                                                               |

|           | 1 = Indicates that the last byte received was data                                                                                                                    |

|           | 0 = Indicates that the last byte received was a device address                                                                                                        |

|           | Hardware is clear at a device address match. Hardware is set by reception of a slave byte.                                                                            |

| bit 4     | P: Stop bit                                                                                                                                                           |

|           | <ol> <li>I = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last</li> </ol>                                                  |

|           | Hardware is set or clear when a Start, Repeated Start or Stop is detected.                                                                                            |

|           |                                                                                                                                                                       |

|           |                                                                                                                                                                       |

### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled; if 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4 | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Receiver is active                                                                                                                                                                                                           |

| bit 3 | <b>PERR:</b> Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character (character at the top of the receive FIFO) 0 = Parity error has not been detected                                                                                                  |

| bit 2 | <pre>FERR: Framing Error Status bit (read-only) 1 = Framing error has been detected for the current character (character at the top of the receive FIFO) 0 = Framing error has not been detected</pre>                                                                                           |

| bit 1 | <ul> <li>OERR: Receive Buffer Overrun Error Status bit (clear/read-only)</li> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed; clearing a previously set OERR bit (1 → 0 transition) resets the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | <ul> <li>URXDA: UARTx Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                |

**Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

### 22.2 CTMU Control Registers

| REGISTER                                                                          | 22-1: CTM                                                                                                                                                           | UCON1: CTMU      | J CONTROL | . REGISTER        | 1        |                        |        |  |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|-------------------|----------|------------------------|--------|--|

| R/W-0                                                                             | U-0                                                                                                                                                                 | R/W-0            | R/W-0     | R/W-0             | R/W-0    | R/W-0                  | R/W-0  |  |

| CTMUEN                                                                            | _                                                                                                                                                                   | CTMUSIDL         | TGEN      | EDGEN             | EDGSEQEN | IDISSEN <sup>(1)</sup> | CTTRIG |  |

| bit 15                                                                            |                                                                                                                                                                     |                  |           |                   |          |                        | bit 8  |  |

|                                                                                   |                                                                                                                                                                     |                  |           |                   |          |                        |        |  |

| U-0                                                                               | U-0                                                                                                                                                                 | U-0              | U-0       | U-0               | U-0      | U-0                    | U-0    |  |

| _                                                                                 |                                                                                                                                                                     | —                | _         |                   | <u> </u> |                        | _      |  |

| bit 7                                                                             |                                                                                                                                                                     |                  |           |                   |          |                        | bit 0  |  |

|                                                                                   |                                                                                                                                                                     |                  |           |                   |          |                        |        |  |

| Legend:                                                                           |                                                                                                                                                                     |                  |           |                   |          |                        |        |  |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'                |                                                                                                                                                                     |                  |           |                   |          |                        |        |  |

| -n = Value at POR                                                                 |                                                                                                                                                                     | '1' = Bit is set |           | '0' = Bit is clea | ared     | x = Bit is unknown     |        |  |

| bit 15 CTMUEN: CTMU Enable bit<br>1 = Module is enabled<br>0 = Module is disabled |                                                                                                                                                                     |                  |           |                   |          |                        |        |  |

| bit 14                                                                            | Unimplemented: Read as '0'                                                                                                                                          |                  |           |                   |          |                        |        |  |

| bit 13                                                                            | bit 13 <b>CTMUSIDL:</b> CTMU Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode<br>0 = Continues module operation in Idle mode |                  |           |                   |          |                        |        |  |

| bit 12                                                                            | TGEN: Time                                                                                                                                                          | Generation Ena   | ble bit   |                   |          |                        |        |  |

### REGISTER 22-1: CTMUCON1: CTMU CONTROL REGISTER 1

|         | <ul> <li>1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.)</li> <li>0 = Software is used to trigger edges (manual set of EDGxSTAT)</li> </ul> |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 10  | EDGSEQEN: Edge Sequence Enable bit                                                                                                                             |

|         | <ul> <li>1 = Edge 1 event must occur before Edge 2 event can occur</li> <li>0 = No edge sequence is needed</li> </ul>                                          |

| bit 9   | IDISSEN: Analog Current Source Control bit <sup>(1)</sup>                                                                                                      |

|         | <ul> <li>1 = Analog current source output is grounded</li> <li>0 = Analog current source output is not grounded</li> </ul>                                     |

| bit 8   | CTTRIG: ADC Trigger Control bit                                                                                                                                |

|         | 1 = CTMU triggers ADC start of conversion                                                                                                                      |

|         | 0 = CTMU does not trigger ADC start of conversion                                                                                                              |

| bit 7-0 | Unimplemented: Read as '0'                                                                                                                                     |

1 = Enables edge delay generation0 = Disables edge delay generation

**EDGEN:** Edge Enable bit

bit 11

**Note 1:** The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

### 25.1.2 OP AMP CONFIGURATION B

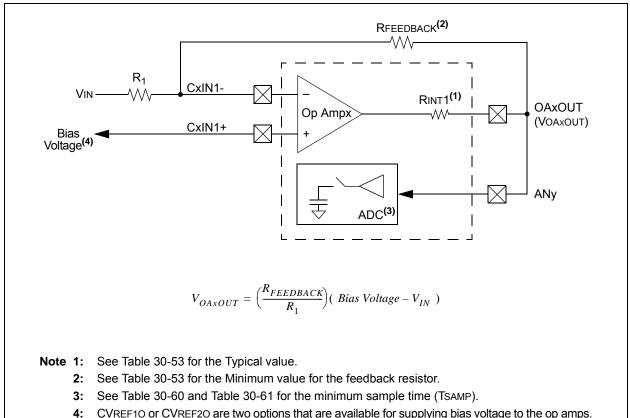

Figure 25-7 shows a typical inverting amplifier circuit with the output of the op amp (OAxOUT) externally routed to a separate analog input pin (ANy) on the device. This op amp configuration is slightly different in terms of the op amp output and the ADC input connection, therefore, RINT1 is not included in the transfer function. However, this configuration requires the designer to externally route the op amp output (OAxOUT) to another analog input pin (ANy). See Table 30-53 in **Section 30.0 "Electrical Characteristics"** for the typical value of RINT1. Table 30-60 and Table 30-61 in **Section 30.0 "Electrical Characteristics"** describe the minimum sample time (TSAMP) requirements for the ADC module in this configuration.

Figure 25-7 also defines the equation to be used to calculate the expected voltage at point VOAxOUT. This is the typical inverting amplifier equation.

### 25.2 Op Amp/Comparator Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|

|       | product page using the link above, enter    |  |  |  |  |

|       | this URL in your browser:                   |  |  |  |  |

|       | http://www.microchip.com/wwwproducts/       |  |  |  |  |

|       | Devices.aspx?dDocName=en555464              |  |  |  |  |

### 25.2.1 KEY RESOURCES

- "Op Amp/Comparator" (DS70357) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- · Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

### FIGURE 25-7: OP AMP CONFIGURATION B

### REGISTER 25-2: CMxCON: COMPARATOR x CONTROL REGISTER (x = 1, 2 OR 3) (CONTINUED)

| bit 7-6 | EVPOL<1:0>: Trigger/Event/Interrupt Polarity Select bits                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|         | <ul> <li>11 = Trigger/event/interrupt generated on any change of the comparator output (while CEVT = 0)</li> <li>10 = Trigger/event/interrupt generated only on high-to-low transition of the polarity selected comparator output (while CEVT = 0)</li> </ul> |  |  |  |  |  |  |  |

|         | If CPOL = 1 (inverted polarity):<br>Low-to-high transition of the comparator output.                                                                                                                                                                          |  |  |  |  |  |  |  |

|         | If CPOL = 0 (non-inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                      |  |  |  |  |  |  |  |

|         | 01 = Trigger/event/interrupt generated only on low-to-high transition of the polarity-selected comparator output (while CEVT = 0)                                                                                                                             |  |  |  |  |  |  |  |

|         | If CPOL = 1 (inverted polarity):<br>High-to-low transition of the comparator output.                                                                                                                                                                          |  |  |  |  |  |  |  |

|         | If CPOL = 0 (non-inverted polarity):<br>Low-to-high transition of the comparator output                                                                                                                                                                       |  |  |  |  |  |  |  |

|         | 00 = Trigger/event/interrupt generation is disabled                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| bit 5   | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| bit 4   | CREF: Comparator Reference Select bit (VIN+ input) <sup>(1)</sup>                                                                                                                                                                                             |  |  |  |  |  |  |  |

|         | <ul> <li>1 = VIN+ input connects to internal CVREFIN voltage<sup>(2)</sup></li> <li>0 = VIN+ input connects to CxIN1+ pin</li> </ul>                                                                                                                          |  |  |  |  |  |  |  |

| bit 3-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| bit 1-0 | CCH<1:0>: Op Amp/Comparator Channel Select bits <sup>(1)</sup>                                                                                                                                                                                                |  |  |  |  |  |  |  |

|         | <ul> <li>11 = Unimplemented</li> <li>10 = Unimplemented</li> <li>01 = Inverting input of the comparator connects to the CxIN2- pin<sup>(2)</sup></li> <li>00 = Inverting input of the op amp/comparator connects to the CxIN1- pin</li> </ul>                 |  |  |  |  |  |  |  |

|         |                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

- **Note 1:** Inputs that are selected and not available will be tied to Vss. See the "**Pin Diagrams**" section for available inputs for each package.

- 2: This output is not available when OPMODE (CMxCON<10>) = 1.

# REGISTER 25-5: CMxMSKCON: COMPARATOR x MASK GATING CONTROL REGISTER (CONTINUED)

bit 3 ABEN: AND Gate B Input Enable bit 1 = MBI is connected to AND gate 0 = MBI is not connected to AND gate bit 2 ABNEN: AND Gate B Input Inverted Enable bit 1 = Inverted MBI is connected to AND gate 0 = Inverted MBI is not connected to AND gate bit 1 AAEN: AND Gate A Input Enable bit 1 = MAI is connected to AND gate 0 = MAI is not connected to AND gate bit 0 AANEN: AND Gate A Input Inverted Enable bit 1 = Inverted MAI is connected to AND gate 0 = Inverted MAI is not connected to AND gate

| DC CHARACTERISTICS |        |                                                                       | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                                 |                       |    |                                                                                                                                      |  |  |  |

|--------------------|--------|-----------------------------------------------------------------------|-------------------------------------------------------|---------------------------------|-----------------------|----|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No.       | Symbol | Characteristic                                                        | Min.                                                  | Min. Typ. Max. Units Conditions |                       |    |                                                                                                                                      |  |  |  |

| DI60a              | licl   | Input Low Injection Current                                           | 0                                                     |                                 | <sub>-5</sub> (4,7)   | mA | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR, VCAP<br>and RB7                                                                       |  |  |  |

| DI60b              | Іісн   | Input High Injection Current                                          | 0                                                     |                                 | +5 <sup>(5,6,7)</sup> | mA | All pins except VDD, VSS,<br>AVDD, AVSS, MCLR, VCAP,<br>RB7 and all 5V tolerant<br>pins <sup>(6)</sup>                               |  |  |  |

| DI60c              | ∑lict  | Total Input Injection Current<br>(sum of all I/O and control<br>pins) | -20 <sup>(8)</sup>                                    | _                               | +20 <sup>(8)</sup>    | mA | Absolute instantaneous sum<br>of all $\pm$ input injection cur-<br>rents from all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT |  |  |  |

### TABLE 30-11: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current can be measured at different input voltages.

2: Negative current is defined as current sourced by the pin.

3: See the "Pin Diagrams" section for the 5V tolerant I/O pins.

4: VIL source < (Vss – 0.3). Characterized but not tested.

5: Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

6: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

7: Non-zero injection currents can affect the ADC results by approximately 4-6 counts.

8: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

# FIGURE 30-11: TIMERQ (QEI MODULE) EXTERNAL CLOCK TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

### TABLE 30-30: QEI MODULE EXTERNAL CLOCK TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)