Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc202-i-mm |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 2: dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X MOTOR CONTROL FAMILIES (CONTINUED)

|                   |                                |                               | (00          |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

|-------------------|--------------------------------|-------------------------------|--------------|----------------------|---------------|----------------|------------------------------------------------|------------------------------|--------|--------------------|------------------|------------------------------------|--------------------------------|----------------------|------------------------------|---------------------|------|-----|----------|-----------|-----------------------|

|                   | <i>•</i>                       | (se                           |              |                      | -             | Re             | mappa                                          | ble P                        | eriphe | erals              |                  |                                    |                                |                      | ~                            |                     |      |     |          |           |                       |

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbytes) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM <sup>(4)</sup><br>(Channels) | Quadrature Encoder Interface | UART   | SPI <sup>(2)</sup> | ECAN™ Technology | External Interrupts <sup>(3)</sup> | I <sup>2</sup> C <sup>TM</sup> | <b>CRC Generator</b> | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | ЪТG | I/O Pins | Pins      | Packages              |

| dsPIC33EP32MC504  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC504  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> , |

| dsPIC33EP128MC504 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,         |

| dsPIC33EP256MC504 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          | 40        | UQFN                  |

| dsPIC33EP512MC504 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP64MC506  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

| dsPIC33EP128MC506 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 16                           | 3/4                 | Voo  | Voo | 53       | 64        | TQFP,                 |

| dsPIC33EP256MC506 | 1024                           | 256                           | 32           | 3                    | 4             | 4              | 0                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2                              | 1                    | 10                           | 3/4                 | Yes  | Yes | 55       | 04        | QFN                   |

| dsPIC33EP512MC506 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |                                |                      |                              |                     |      |     |          |           |                       |

Note 1:

On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details.

2:

Only SPI2 is remappable.

3: INT0 is not remappable.

4: Only the PWM Faults are remappable.

5: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

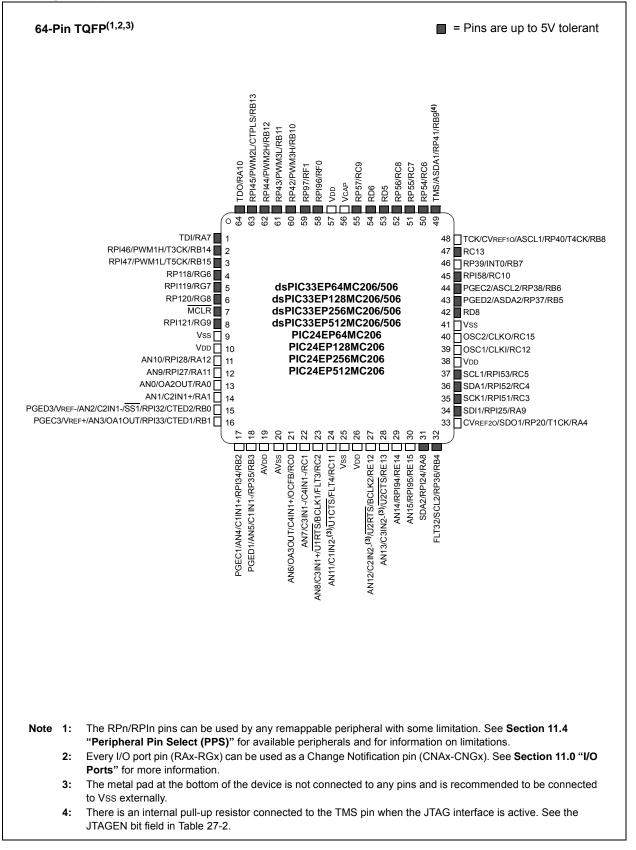

#### Pin Diagrams (Continued)

#### **TABLE 4-3**: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| TADLL        | τу.   |        |        |            | VELEN  |        |        |            |        |       |         | DEVICE      |         |               |          |              |         |               |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|---------|-------------|---------|---------------|----------|--------------|---------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3         | Bit 2    | Bit 1        | Bit 0   | All<br>Resets |

| IFS0         | 0800  |        | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF   | IC2IF       | DMA0IF  | T1IF          | OC1IF    | IC1IF        | INTOIF  | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _       | —           | INT1IF  | CNIF          | CMIF     | MI2C1IF      | SI2C1IF | 0000          |

| IFS2         | 0804  |        | _      | _          | -      |        | _      | —          | _      | _     | IC4IF   | IC3IF       | DMA3IF  | _             | —        | SPI2IF       | SPI2EIF | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      | _      | _          | _      | _     | _       | _           | _       | _             | MI2C2IF  | SI2C2IF      | _       | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | _      | _      | _          | _      | _     | _       | _           | _       | CRCIF         | U2EIF    | U1EIF        | _       | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  | _          | _      | _      | _      | —          | —      | _     | _       | _           | _       | _             | —        | —            | —       | 0000          |

| IFS9         | 0812  | _      | _      | _          | _      | _      | _      | —          | —      | _     | PTG3IF  | PTG2IF      | PTG1IF  | PTG0IF        | PTGWDTIF | PTGSTEPIF    | —       | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE   | IC2IE       | DMA0IE  | T1IE          | OC1IE    | IC1IE        | INT0IE  | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _       | _           | INT1IE  | CNIE          | CMIE     | MI2C1IE      | SI2C1IE | 0000          |

| IEC2         | 0824  | _      | _      | _          | _      | _      | _      | _          | _      | _     | IC4IE   | IC3IE       | DMA3IE  | _             | _        | SPI2IE       | SPI2EIE | 0000          |

| IEC3         | 0826  | _      | _      | _          | _      | _      | _      | —          | —      | _     | _       | _           | _       | _             | MI2C2IE  | SI2C2IE      | —       | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | _      | _      | _      | _          | _      | _     | _       | _           | _       | CRCIE         | U2EIE    | U1EIE        | _       | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _      | _      | _      | _          | _      | _     | _       | _           | _       | _             | _        | _            | _       | 0000          |

| IEC9         | 0832  | _      | _      | _          | _      | _      | _      | —          | —      | _     | PTG3IE  | PTG2IE      | PTG1IE  | PTG0IE        | PTGWDTIE | PTGSTEPIE    | —       | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      | (      | OC1IP<2:0  | >      | _     |         | IC1IP<2:0>  |         | —             |          | INT0IP<2:0>  |         | 4444          |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      | (      | OC2IP<2:0  | >      | _     |         | IC2IP<2:0>  |         | — DMA0IP<2:0> |          |              | 4444    |               |

| IPC2         | 0844  | _      | U      | J1RXIP<2:0 | >      | _      | ;      | SPI1IP<2:0 | >      | _     |         | SPI1EIP<2:0 | >       | _             |          | T3IP<2:0>    |         | 4444          |

| IPC3         | 0846  | _      | _      | _          | _      | _      | D      | )MA1IP<2:  | 0>     | _     |         | AD1IP<2:0>  |         | _             | ι        | U1TXIP<2:0>  |         |               |

| IPC4         | 0848  |        |        | CNIP<2:0>  |        |        |        | CMIP<2:0   | >      | _     |         | MI2C1IP<2:0 | >       | _             | S        | SI2C1IP<2:0> |         | 4444          |

| IPC5         | 084A  | _      | _      | _          | _      | _      | _      | _          | _      | _     | _       | —           | _       | _             | I        | INT1IP<2:0>  |         | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      | (      | OC4IP<2:0  | >      | _     |         | OC3IP<2:0>  |         | _             | C        | )ma2IP<2:0>  |         | 4444          |

| IPC7         | 084E  |        | I      | U2TXIP<2:0 | >      |        | L      | J2RXIP<2:  | )>     | _     |         | INT2IP<2:0> |         | _             |          | T5IP<2:0>    |         | 4444          |

| IPC8         | 0850  |        | _      | _          | _      |        | _      | —          | —      | _     |         | SPI2IP<2:0> |         | _             | S        | SPI2EIP<2:0> |         | 0044          |

| IPC9         | 0852  |        | _      | _          | _      |        |        | IC4IP<2:0  | >      | _     |         | IC3IP<2:0>  |         | _             | C        | 0MA3IP<2:0>  |         | 0444          |

| IPC12        | 0858  |        | _      | _          | _      |        | N      | 112C2IP<2: | 0>     | _     |         | SI2C2IP<2:0 | >       | _             | _        | _            | _       | 0440          |

| IPC16        | 0860  |        |        | CRCIP<2:0> | >      |        |        | U2EIP<2:0  | >      | _     |         | U1EIP<2:0>  |         | _             | _        | _            | _       | 4440          |

| IPC19        | 0866  |        | _      | _          | _      | _      | _      | _          | _      | _     |         | CTMUIP<2:0  | >       | _             | _        | _            | _       | 0040          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >      | _     | _       | _           | _       | _             | _        | _            | _       | 4400          |

| IPC36        | 0888  | _      |        | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>   | _     | P       | TGSTEPIP<2  | :0>     | _             | _        | —            | _       | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | PTG3IP<2:  | )>     | _     |         | PTG2IP<2:0  | >       | _             | F        | PTG1IP<2:0>  |         | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | _      |        |        |            | —      | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR       | STKERR   | OSCFAIL      |         | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      |        |        |            | _      | _     |         | —           | —       | _             | INT2EP   | INT1EP       | INT0EP  | 8000          |

| INTCON3      | 08C4  | _      | _      |            | _      |        |        | _          | _      | _     | _       | DAE         | DOOVR   | _             | _        | —            |         | 0000          |

| INTCON4      | 08C6  |        | _      | _          | _      | _      | _      | —          | _      | _     | _       | _           | _       | _             | _        |              | SGHT    | 0000          |

| INTTREG      | 08C8  | _      |        |            | _      |        | ILR<   | 3:0>       |        |       |         |             | VECN    | UM<7:0>       |          |              |         | 0000          |

|              |       |        |        |            |        |        |        |            |        |       |         |             |         |               |          |              |         |               |

- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

| U-0                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                               | U-0                                                                                              | U-0                               | U-0                      | U-0                         | U-0  |  |  |  |  |  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|-----------------------------|------|--|--|--|--|--|

|                                              | _                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                 | _                                                                                                | _                                 | _                        | _                           | _    |  |  |  |  |  |

| bit 15                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                   |                                                                                                  |                                   |                          |                             | bit  |  |  |  |  |  |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                   |                                                                                                  |                                   |                          |                             |      |  |  |  |  |  |

| U-0                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                               | R/W-0                                                                                            | R/W-0                             | U-0                      | U-0                         | U-0  |  |  |  |  |  |

| _                                            | -                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                 | DMA0MD <sup>(1)</sup><br>DMA1MD <sup>(1)</sup><br>DMA2MD <sup>(1)</sup><br>DMA3MD <sup>(1)</sup> | PTGMD                             | _                        | _                           | _    |  |  |  |  |  |

| bit 7                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                   |                                                                                                  |                                   |                          |                             | bit  |  |  |  |  |  |

| <b>Legend:</b><br>R = Readab<br>-n = Value a |                                                                                                                                                                                                                                                                                                                                                                                                                                       | W = Writable<br>'1' = Bit is set                  |                                                                                                  | U = Unimplen<br>'0' = Bit is clea | nented bit, read<br>ared | l as '0'<br>x = Bit is unkn | iown |  |  |  |  |  |

| bit 15-5<br>bit 4                            | Unimplemented: Read as '0'<br>DMA0MD: DMA0 Module Disable bit <sup>(1)</sup><br>1 = DMA0 module is disabled<br>0 = DMA0 module is enabled<br>DMA1MD: DMA1 Module Disable bit <sup>(1)</sup><br>1 = DMA1 module is disabled<br>0 = DMA1 module is enabled<br>DMA2MD: DMA2 Module Disable bit <sup>(1)</sup><br>1 = DMA2 module is disabled<br>0 = DMA2 module is disabled<br>0 = DMA2 module is disabled<br>0 = DMA3 module is enabled |                                                   |                                                                                                  |                                   |                          |                             |      |  |  |  |  |  |

| bit 3                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                       | Module Disat<br>ule is disabled<br>ule is enabled | ole bit                                                                                          |                                   |                          |                             |      |  |  |  |  |  |

| bit 2-0                                      | Unimplement                                                                                                                                                                                                                                                                                                                                                                                                                           | ted: Read as '                                    | 0'                                                                                               |                                   |                          |                             |      |  |  |  |  |  |

| Note 1: T                                    | his single bit ena                                                                                                                                                                                                                                                                                                                                                                                                                    | ables and disal                                   | oles all four DM                                                                                 | A channels.                       |                          |                             |      |  |  |  |  |  |

#### REGISTER 10-6: PMD7: PERIPHERAL MODULE DISABLE CONTROL REGISTER 7

| U-0           | U-0        | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|---------------|------------|------------------|----------------|-------------------|------------------|-----------------|-------|

| _             | —          |                  |                | RP39              | R<5:0>           |                 |       |

| bit 15        |            |                  |                |                   |                  |                 | bit 8 |

|               |            |                  |                |                   |                  |                 |       |

| U-0           | U-0        | R/W-0            | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| —             | —          |                  |                | RP38              | R<5:0>           |                 |       |

| bit 7         |            |                  |                |                   |                  |                 | bit 0 |

|               |            |                  |                |                   |                  |                 |       |

| Legend:       |            |                  |                |                   |                  |                 |       |

| R = Readable  | e bit      | W = Writable     | bit            | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at | POR        | '1' = Bit is set |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|               |            |                  |                |                   |                  |                 |       |

| bit 15-14     | Unimplemer | nted: Read as '  | 0'             |                   |                  |                 |       |

| bit 13-8      | RP39R<5:0> | : Peripheral Ou  | Itput Function | n is Assigned to  | RP39 Output F    | Pin bits        |       |

#### REGISTER 11-20: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

|         | (see Table 11-3 for peripheral function numbers)                           |

|---------|----------------------------------------------------------------------------|

| bit 7-6 | Unimplemented: Read as '0'                                                 |

| bit 5-0 | RP38R<5:0>: Peripheral Output Function is Assigned to RP38 Output Pin bits |

|         | (see Table 11-3 for peripheral function numbers)                           |

#### REGISTER 11-21: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP41  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP40  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP41R<5:0>:** Peripheral Output Function is Assigned to RP41 Output Pin bits (see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP40R<5:0>:** Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 11-3 for peripheral function numbers)

NOTES:

#### 12.1 Timer1 Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 12.1.1 KEY RESOURCES

- "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### **REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is cleared only by software

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

- 2: Each Output Compare x module (OCx) has one PTG clock source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

- PTGO4 = OC1 PTGO5 = OC2

- PTGO6 = OC3 PTGO7 = OC4

## 16.3 PWMx Control Registers

#### REGISTER 16-1: PTCON: PWMx TIME BASE CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | HS/HC-0 | R/W-0 | R/W-0               | R/W-0                  | R/W-0                  |

|--------|-----|--------|---------|-------|---------------------|------------------------|------------------------|

| PTEN   | —   | PTSIDL | SESTAT  | SEIEN | EIPU <sup>(1)</sup> | SYNCPOL <sup>(1)</sup> | SYNCOEN <sup>(1)</sup> |

| bit 15 |     |        |         |       |                     |                        | bit 8                  |

| R/W-0                 | R/W-0                   | R/W-0                   | R/W-0                   | R/W-0                  | R/W-0                  | R/W-0                  | R/W-0                  |

|-----------------------|-------------------------|-------------------------|-------------------------|------------------------|------------------------|------------------------|------------------------|

| SYNCEN <sup>(1)</sup> | SYNCSRC2 <sup>(1)</sup> | SYNCSRC1 <sup>(1)</sup> | SYNCSRC0 <sup>(1)</sup> | SEVTPS3 <sup>(1)</sup> | SEVTPS2 <sup>(1)</sup> | SEVTPS1 <sup>(1)</sup> | SEVTPS0 <sup>(1)</sup> |

| bit 7                 | •                       |                         |                         |                        |                        |                        | bit 0                  |

| Legend:           | HC = Hardware Clearable bit HS = Hardware Settable bit |                                    | t                  |

|-------------------|--------------------------------------------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit                                       | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set                                       | '0' = Bit is cleared               | x = Bit is unknown |

| bit 15  | PTEN: PWMx Module Enable bit                                                                                                                            |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = PWMx module is enabled</li> <li>0 = PWMx module is disabled</li> </ul>                                                                     |

| bit 14  | Unimplemented: Read as '0'                                                                                                                              |

| bit 13  | PTSIDL: PWMx Time Base Stop in Idle Mode bit                                                                                                            |

|         | <ul> <li>1 = PWMx time base halts in CPU Idle mode</li> <li>0 = PWMx time base runs in CPU Idle mode</li> </ul>                                         |

| bit 12  | SESTAT: Special Event Interrupt Status bit                                                                                                              |

|         | <ul> <li>1 = Special event interrupt is pending</li> <li>0 = Special event interrupt is not pending</li> </ul>                                          |

| bit 11  | SEIEN: Special Event Interrupt Enable bit                                                                                                               |

|         | 1 = Special event interrupt is enabled                                                                                                                  |

|         | 0 = Special event interrupt is disabled                                                                                                                 |

| bit 10  | EIPU: Enable Immediate Period Updates bit <sup>(1)</sup>                                                                                                |

|         | <ul> <li>1 = Active Period register is updated immediately</li> <li>0 = Active Period register updates occur on PWMx cycle boundaries</li> </ul>        |

| bit 9   | SYNCPOL: Synchronize Input and Output Polarity bit <sup>(1)</sup>                                                                                       |

|         | 1 = SYNCI1/SYNCO1 polarity is inverted (active-low)                                                                                                     |

|         | 0 = SYNCI1/SYNCO1 is active-high                                                                                                                        |

| bit 8   | SYNCOEN: Primary Time Base Sync Enable bit <sup>(1)</sup>                                                                                               |

|         | 1 = SYNCO1 output is enabled                                                                                                                            |

| L:1 7   | 0 = SYNCO1 output is disabled                                                                                                                           |

| bit 7   | SYNCEN: External Time Base Synchronization Enable bit <sup>(1)</sup>                                                                                    |

|         | <ul> <li>1 = External synchronization of primary time base is enabled</li> <li>0 = External synchronization of primary time base is disabled</li> </ul> |

|         |                                                                                                                                                         |

| Note 1: | These bits should be changed only when PTEN = 0. In addition, when using the SYNCI1 feature, the user                                                   |

|         | application must program the period register with a value that is slightly larger than the expected period of                                           |

the external synchronization input signal.

2: See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.

#### 17.2 QEI Control Registers

|  | REGISTER 17-1: | QEI1CON: QEI1 CONTROL REGISTER |

|--|----------------|--------------------------------|

|--|----------------|--------------------------------|

| U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         —       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------|---------------------|

| bit 15       bit 2         U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       -       intdividue       W= Writable bit       U = Unimplemented bit, read as '0'       bit 15       GEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to         bit 13       GEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD-2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       100 = Modulo Count mode for position counter         100 = Next index event after home event initializes position counter with contents of QEI1IC register       100 = Next index input event initializes position counter with contents of QEI1IC register       100 = Index input event dees not affect position coun                                                                                                                                                                                                  | R/W-0        | U-0                                                                                              | R/W-0                                                                                                          | R/W-0                                                                                        | R/W-0                                                                                          | R/W-0                                                      | R/W-0                             | R/W-0               |

| U-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0       R/W-0         -       INTDIV2 <sup>(3)</sup> INTDIV1 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 0       Dit 7       Dit 7       Dit 7       Dit 7       Dit 7         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       Dit 7         en value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN:       Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0         0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to       Dit 13       QEISDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation in Idle mode       0 = Continues module operation in Idle mode       Di Continues module operation on In Idle mode         Dit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         100 = Modulo Count mode for position counter       101 = Resets the position counter       101 = Resets the position counter with contents of QEI1IC register         101 = Resets the position counter when the position counter with contents of QEI1IC register       000 = Index input e                                                                                                                                                                                                                                          | QEIEN        | _                                                                                                | QEISIDL                                                                                                        | PIMOD2 <sup>(1)</sup>                                                                        | PIMOD1 <sup>(1)</sup>                                                                          | PIMOD0 <sup>(1)</sup>                                      | IMV1 <sup>(2)</sup>               | IMV0 <sup>(2)</sup> |

| -       INTDIV2 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 7       bit 0         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit 0         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       Bit is cleared       x = Bit is unknown         bit 13       QEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation unter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         10 = Resets the position counter when the position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event frees the position counter       110 = Resets the position counter         11 = Reserved       11 = First index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event free home event initializes position counter with contents of QEI1IC register                                                                                                                                          | bit 15       |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   | bit 8               |

| -       INTDIV2 <sup>(3)</sup> INTDIV0 <sup>(3)</sup> CNTPOL       GATEN       CCM1       CCM0         bit 7       bit 7       bit 0         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'       bit 0         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       Bit is cleared       x = Bit is unknown         bit 13       QEISDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation unter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         10 = Resets the position counter when the position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event frees the position counter       110 = Resets the position counter         11 = Reserved       11 = First index event after home event initializes position counter with contents of QEI1IC register         10 = Next index input event free home event initializes position counter with contents of QEI1IC register                                                                                                                                          |              |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |

| bit 7       bit 0         Legend:       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Module counters are enabled         0 = Module counters are disabled, but SFRs can be read or written to       0 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'       0 = Continues module operation when device enters Idle mode         0 = Continues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD-2:0-: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Resets the position counter         101 = Resets the position counter when the position counter with contents of QEI1IC register         101 = Nexet input event after home event initializes position counter with contents of QEI1IC register         010 = Next index input event resets the position counter         011 = Every index input event resets the position counter         012 = Nease B match occurs when QEB = 1         0 = Phase B match occurs when QEB = 0         bit 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1 <t< td=""><td>U-0</td><td></td><td></td><td></td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td><td>R/W-0</td></t<>                                                                       | U-0          |                                                                                                  |                                                                                                                |                                                                                              | R/W-0                                                                                          | R/W-0                                                      | R/W-0                             | R/W-0               |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0         0 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to       0         bit 14       Unimplemented: Read as '0'       0         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         11 = Reserved       111 = Reserved         110 = Modulo Count mode for position counter       101 = Resets the position counter when the position counter equals QEI1GEC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       100 = Second index event after home event initializes position counter with contents of QEI1IC register         101 = First index vent after home event initializes position counter with contents of QEI1IC register       001 = Every index input event resets the position counter         010 = Next index input event does not affect position counter       001 = Every index input event after home event initializes position counter with contents of QEI1IC register                                                                                                                                |              | INTDIV2 <sup>(3)</sup>                                                                           | INTDIV1 <sup>(3)</sup>                                                                                         | INTDIV0 <sup>(3)</sup>                                                                       | CNTPOL                                                                                         | GATEN                                                      | CCM1                              |                     |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is cleared       x = Bit is unknown         bit 15       QEISIDL: QEI Stop in Idle Mode bit       1 = Module counters are disabled, but SFRs can be read or written to       bit 14         Unimplemented: Read as '0'       East as '0'       East as '0'       East as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI1IC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter         101 = Reserved       III = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes position counter with contents of QEI1IC register         102 = Mext index input event does not affect position counter       01 = Phase                                                                                              | bit 7        |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   | bit 0               |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         In = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is cleared       x = Bit is unknown         bit 15       QEISIDL: QEI Stop in Idle Mode bit       1 = Module counters are disabled, but SFRs can be read or written to       bit 14         Unimplemented: Read as '0'       East as '0'       East as '0'       East as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit       1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI1IC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter         101 = Reserved       III = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes position counter with contents of QEI1IC register         102 = Mext index input event does not affect position counter       01 = Phase                                                                                              | Logondy      |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                |                                                            |                                   |                     |

| n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is unknown         bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit       1 = Module counters are enabled       0 = Bit is unknown         bit 14       Unimplemented: Read as '0'       0'       0'       Bit is cleared       0 = Continues module operation when device enters ldle mode       0 = Continues module operation in ldle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       10 = Second index event after home event initializes position counter with contents of QEI11C register         100 = Second index event after home event initializes position counter with contents of QEI11C register       10 = Next index input event resets the position counter with contents of QEI11C register         101 = Every index input event resets the position counter       00 = Index input event does not affect position counter         001 = Every index input event genst bit <sup>(2)</sup> 1 = Phase B match occurs when QEB = 1         011 = Phase B match occurs when QEB = 1       0 = Phase B match occurs when QEA = 1         015 = Phase A match occurs when QEA = 1       0 = Phase A match occurs when QEA = 1         015 = Phase A match occurs when QEA =                                                                                                  |              | lo hit                                                                                           |                                                                                                                | hit                                                                                          | II – Unimplor                                                                                  | monted bit read                                            | ac '0'                            |                     |

| bit 15       QEIEN: Quadrature Encoder Interface Module Counter Enable bit         1 = Module counters are enabled       0 = Module counters are disabled, but SFRs can be read or written to         bit 14       Unimplemented: Read as '0'         bit 13       QEISIDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         11 = Discontinues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation in Idle mode       0 = Continues module operation in Idle mode         0 = Continues module operation counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved         110 = Modulo Count mode for position counter       100 = Second index event after home event initializes position counter with contents of QEI1IC register         011 = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event resets the position counter         001 = Nevery index input eve                                                                                                  |              |                                                                                                  |                                                                                                                |                                                                                              | •                                                                                              |                                                            |                                   |                     |

| <ul> <li>1 = Module counters are enabled</li> <li>0 = Module counters are disabled, but SFRs can be read or written to</li> <li>bit 14</li> <li>Unimplemented: Read as '0'</li> <li>bit 13</li> <li>QEISIDL: QEI Stop in Idle Mode bit</li> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>0 = Continues module operation counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>110 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event initializes the position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>011 = Every index input event resets the position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index Match Value for Phase B bit<sup>(2)</sup></li> <li>1 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul> | -n = value a | PUR                                                                                              | I = Bit is set                                                                                                 |                                                                                              | 0 = Bit is cle                                                                                 | ared                                                       | x = Bit is unkr                   | lown                |

| bit 13       QEISDL: QEI Stop in Idle Mode bit         1 = Discontinues module operation when device enters Idle mode       0 = Continues module operation in Idle mode         bit 12-10       PIMOD<2:0>: Position Counter Initialization Mode Select bits <sup>(1)</sup> 111 = Reserved       110 = Modulo Count mode for position counter         100 = Modulo Count mode for position counter       101 = Resets the position counter when the position counter equals QEI1GEC register         100 = Second index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter with contents of QEI1IC register         011 = First index event after home event initializes position counter with contents of QEI1IC register       010 = Next index input event initializes the position counter with contents of QEI1IC register         011 = Every index input event resets the position counter       001 = Every index input event for position counter         001 = Index input event does not affect position counter       000 = Index input event does not affect position counter         001 = Phase B match occurs when QEB = 1       0 = Phase B match occurs when QEB = 0         0it 8       IMV0: Index Match Value for Phase A bit <sup>(2)</sup> 1 = Phase A match occurs when QEA = 1       0 = Phase A match occurs when QEA = 0         0it 7       Unimplemented: Read as '0'                                                                                                                                                                                   | bit 15       | 1 = Module co                                                                                    | ounters are ena                                                                                                | abled                                                                                        |                                                                                                |                                                            |                                   |                     |

| <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> <li>bit 12-10</li> <li>PIMOD&lt;2:0&gt;: Position Counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>10 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event operation when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> <li>Unimplemented: Read as '0'</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                  | bit 14       | Unimplemen                                                                                       | ted: Read as '                                                                                                 | 0'                                                                                           |                                                                                                |                                                            |                                   |                     |

| <ul> <li>0 = Continues module operation in Idle mode</li> <li>bit 12-10</li> <li>PIMOD&lt;2:0&gt;: Position Counter Initialization Mode Select bits<sup>(1)</sup></li> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event resets the position counter with contents of QEI1IC register</li> <li>001 = Every index input event resets the position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event QEB = 1</li> <li>0 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>bit 8</li> <li>IMV0: Index Match Value for Phase A bit<sup>(2)</sup></li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>bit 7</li> </ul>                                                                                                                                                                                                                                                                                                                                  | bit 13       | QEISIDL: QE                                                                                      | I Stop in Idle M                                                                                               | lode bit                                                                                     |                                                                                                |                                                            |                                   |                     |

| <ul> <li>111 = Reserved</li> <li>10 = Modulo Count mode for position counter</li> <li>101 = Resets the position counter when the position counter equals QEI1GEC register</li> <li>100 = Second index event after home event initializes position counter with contents of QEI1IC register</li> <li>011 = First index event after home event initializes position counter with contents of QEI1IC register</li> <li>010 = Next index input event initializes the position counter with contents of QEI1IC register</li> <li>011 = Every index input event resets the position counter with contents of QEI1IC register</li> <li>000 = Index input event does not affect position counter</li> <li>000 = Index input event does not affect position counter</li> <li>011 = Phase B match occurs when QEB = 1</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>0 = Phase B match occurs when QEB = 0</li> <li>1 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 1</li> <li>0 = Phase A match occurs when QEA = 0</li> <li>0 = Phase A match occurs when QEA = 0</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |                                                                                                  |                                                                                                                |                                                                                              |                                                                                                | dle mode                                                   |                                   |                     |