#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 6x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc202-i-sp |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

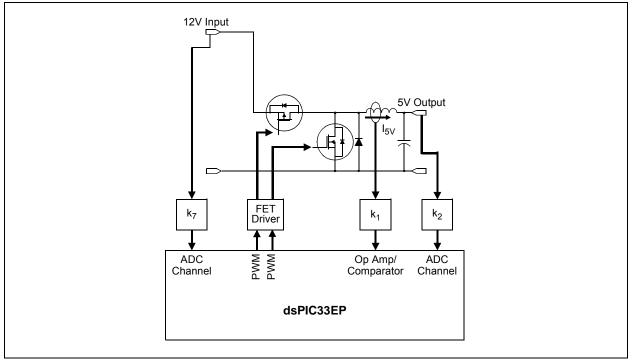

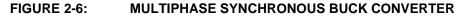

### FIGURE 2-5: SINGLE-PHASE SYNCHRONOUS BUCK CONVERTER

| TABLE 4   | 4-9:  | -9: INPUT CAPTURE 1 THROUGH INPUT CAPTURE 4 REGISTER MAP |                                                 |        |        |               |        |       |              |              |          |       |                     |       |          |          |       |               |

|-----------|-------|----------------------------------------------------------|-------------------------------------------------|--------|--------|---------------|--------|-------|--------------|--------------|----------|-------|---------------------|-------|----------|----------|-------|---------------|

| File Name | Addr. | Bit 15                                                   | Bit 14                                          | Bit 13 | Bit 12 | Bit 11        | Bit 10 | Bit 9 | Bit 8        | Bit 7        | Bit 6    | Bit 5 | Bit 4               | Bit 3 | Bit 2    | Bit 1    | Bit 0 | All<br>Resets |

| IC1CON1   | 0140  | _                                                        | —                                               | ICSIDL | 10     | ICTSEL<2:0> — |        |       | -            | —            | ICI<     | :0>   | ICOV ICBNE ICM<2:0> |       |          |          | 0000  |               |

| IC1CON2   | 0142  | _                                                        | <u>− − − − − − − − − − − − − − − − − − − </u>   |        |        |               |        |       |              |              |          | 000D  |                     |       |          |          |       |               |

| IC1BUF    | 0144  |                                                          | Input Capture 1 Buffer Register x               |        |        |               |        |       |              |              |          |       |                     | xxxx  |          |          |       |               |

| IC1TMR    | 0146  |                                                          | Input Capture 1 Timer 0                         |        |        |               |        |       |              |              |          |       |                     | 0000  |          |          |       |               |

| IC2CON1   | 0148  |                                                          | ICSIDL ICTSEL<2:0> ICI<1:0> ICOV ICBNE ICM<2:0> |        |        |               |        |       |              | 0000         |          |       |                     |       |          |          |       |               |

| IC2CON2   | 014A  |                                                          | IC32 ICTRIG TRIGSTAT SYNCSEL<4:0>               |        |        |               |        |       |              |              |          |       | 000D                |       |          |          |       |               |

| IC2BUF    | 014C  |                                                          |                                                 |        |        |               |        | Inp   | ut Capture 2 | 2 Buffer Reg | gister   |       |                     |       |          |          |       | xxxx          |

| IC2TMR    | 014E  |                                                          |                                                 |        |        |               |        |       | Input Capt   | ture 2 Time  | r        |       |                     |       |          |          |       | 0000          |

| IC3CON1   | 0150  |                                                          | _                                               | ICSIDL | 10     | CTSEL<2:0     | >      | —     | _            |              | ICI<1    | :0>   | ICOV                | ICBNE |          | ICM<2:0> |       | 0000          |

| IC3CON2   | 0152  |                                                          | _                                               |        |        |               | —      | —     | IC32         | ICTRIG       | TRIGSTAT |       |                     | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC3BUF    | 0154  |                                                          |                                                 |        |        |               |        | Inp   | ut Capture 3 | 3 Buffer Reg | gister   |       |                     |       |          |          |       | xxxx          |

| IC3TMR    | 0156  |                                                          |                                                 |        |        |               |        |       | Input Capt   | ture 3 Time  | r        |       |                     |       |          |          |       | 0000          |

| IC4CON1   | 0158  |                                                          | _                                               | ICSIDL | 10     | CTSEL<2:0     | >      | —     | _            |              | ICI<1    | :0>   | ICOV                | ICBNE |          | ICM<2:0> |       | 0000          |

| IC4CON2   | 015A  | _                                                        | _                                               |        | _      |               | -      | _     | IC32         | ICTRIG       | TRIGSTAT | -     |                     | S     | YNCSEL<4 | :0>      |       | 000D          |

| IC4BUF    | 015C  |                                                          |                                                 |        |        |               |        | Inp   | ut Capture 4 | 4 Buffer Reg | gister   |       |                     |       |          |          |       | xxxx          |

| IC4TMR    | 015E  |                                                          |                                                 |        |        |               |        |       | Input Capt   | ure 4 Time   | r        |       |                     |       |          |          |       | 0000          |

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4         | _E 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY |        |                   |          |            |            |          |          |             |        |        |            |          |        |        |        |        |               |

|-----------------|---------------------------------------------------------------------------------------|--------|-------------------|----------|------------|------------|----------|----------|-------------|--------|--------|------------|----------|--------|--------|--------|--------|---------------|

| File Name       | Addr.                                                                                 | Bit 15 | Bit 14            | Bit 13   | Bit 12     | Bit 11     | Bit 10   | Bit 9    | Bit 8       | Bit 7  | Bit 6  | Bit 5      | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| QEI1CON         | 01C0                                                                                  | QEIEN  | —                 | QEISIDL  |            | PIMOD<2:0> |          | IMV      | <1:0>       | -      |        | INTDIV<2:0 | >        | CNTPOL | GATEN  | CCM    | <1:0>  | 0000          |

| QEI1IOC         | 01C2                                                                                  | QCAPEN | FLTREN            |          | QFDIV<2:0> |            | OUTFN    | NC<1:0>  | SWPAB       | HOMPOL | IDXPOL | QEBPOL     | QEAPOL   | HOME   | INDEX  | QEB    | QEA    | 000x          |

| <b>QEI1STAT</b> | 01C4                                                                                  | _      | _                 | PCHEQIRQ | PCHEQIEN   | PCLEQIRQ   | PCLEQIEN | POSOVIRQ | POSOVIEN    | PCIIRQ | PCIIEN | VELOVIRQ   | VELOVIEN | HOMIRQ | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS1CNTL        | 01C6                                                                                  |        | POSCNT<15:0> 00   |          |            |            |          |          |             |        |        |            |          | 0000   |        |        |        |               |

| POS1CNTH        | 01C8                                                                                  |        | POSCNT<31:16> 00  |          |            |            |          |          |             |        |        |            |          | 0000   |        |        |        |               |

| POS1HLD         | 01CA                                                                                  |        |                   |          |            |            |          |          | POSHLD<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| VEL1CNT         | 01CC                                                                                  |        |                   |          |            |            |          |          | VELCNT<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| INT1TMRL        | 01CE                                                                                  |        |                   |          |            |            |          |          | INTTMR<15:  | 0>     |        |            |          |        |        |        |        | 0000          |

| INT1TMRH        | 01D0                                                                                  |        | INTTMR<31:16> 0   |          |            |            |          |          |             |        |        | 0000       |          |        |        |        |        |               |

| INT1HLDL        | 01D2                                                                                  |        |                   |          |            |            |          |          | INTHLD<15:  | )>     |        |            |          |        |        |        |        | 0000          |

| INT1HLDH        | 01D4                                                                                  |        |                   |          |            |            |          |          | INTHLD<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

| INDX1CNTL       | 01D6                                                                                  |        |                   |          |            |            |          |          | INDXCNT<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| INDX1CNTH       | 01D8                                                                                  |        |                   |          |            |            |          |          | NDXCNT<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| INDX1HLD        | 01DA                                                                                  |        |                   |          |            |            |          |          | INDXHLD<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| QEI1GECL        | 01DC                                                                                  |        |                   |          |            |            |          |          | QEIGEC<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1ICL</b>  | 01DC                                                                                  |        |                   |          |            |            |          |          | QEIIC<15:0  | >      |        |            |          |        |        |        |        | 0000          |

| QEI1GECH        | 01DE                                                                                  |        |                   |          |            |            |          |          | QEIGEC<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| QEI1ICH         | 01DE                                                                                  |        | QEIIC<31:16> 0000 |          |            |            |          |          |             |        |        |            | 0000     |        |        |        |        |               |

| QEI1LECL        | 01E0                                                                                  |        |                   |          |            |            |          |          | QEILEC<15:  | )>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1LECH</b> | 01E2                                                                                  |        |                   |          |            |            |          |          | QEILEC<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

TABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| <b>TABLE 4-33</b> : | PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY |

|---------------------|-----------------------------------------------------------------------------|

|---------------------|-----------------------------------------------------------------------------|

| File<br>Name | Addr. | Bit 15 | Bit 14       | Bit 13       | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6        | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------------|--------------|--------|------------|--------|-------|-------|-------|--------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | _      |              | INT1R<6:0>   |        |            |        |       |       |       | _            | _     | _     | _          |       | _     | _     | 0000          |

| RPINR1       | 06A2  |        | —            | —            | -      |            | -      | -     | -     | -     | INT2R<6:0>   |       |       |            |       |       | 0000  |               |

| RPINR3       | 06A6  | -      | _            | _            | _      | _          | _      | _     | _     | _     | T2CKR<6:0>   |       |       |            |       |       | 0000  |               |

| RPINR7       | 06AE  | _      |              | IC2R<6:0>    |        |            |        |       |       | —     |              |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  | _      |              | IC4R<6:0>    |        |            |        |       |       | —     |              |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6  | _      | _            | _            | —      | _          | _      | _     | _     | —     |              |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR12      | 06B8  | _      |              | FLT2R<6:0>   |        |            |        |       |       | —     | FLT1R<6:0>   |       |       |            |       |       | 0000  |               |

| RPINR14      | 06BC  | _      |              |              | (      | QEB1R<6:0  | >      |       |       | —     | QEA1R<6:0>   |       |       |            |       |       | 0000  |               |

| RPINR15      | 06BE  | _      |              |              | Н      | OME1R<6:0  | )>     |       |       | —     | INDX1R<6:0>  |       |       |            |       |       | 0000  |               |

| RPINR18      | 06C4  | _      | _            | _            | —      | —          | _      | _     | _     | —     | U1RXR<6:0>   |       |       |            |       |       | 0000  |               |

| RPINR19      | 06C6  | _      | _            | _            | _      | _          | _      | _     | _     | —     |              |       | ι     | J2RXR<6:0> | >     |       |       | 0000          |

| RPINR22      | 06CC  | _      |              | •            | S      | CK2INR<6:0 | )>     |       |       | _     |              |       |       | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23      | 06CE  | _      | _            |              | _      | _          | _      | _     | _     | _     |              |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR37      | 06EA  | _      | SYNCI1R<6:0> |              |        |            |        | _     | _     | _     | _            | _     | _     | _          | _     | 0000  |       |               |

| RPINR38      | 06EC  | _      |              | DTCMP1R<6:0> |        |            |        |       |       | _     | _            | _     | _     |            | _     | _     | _     | 0000          |

| RPINR39      | 06EE  | _      |              |              | DT     | CMP3R<6:   | 0>     |       |       | —     | DTCMP2R<6:0> |       |       |            |       |       | 0000  |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

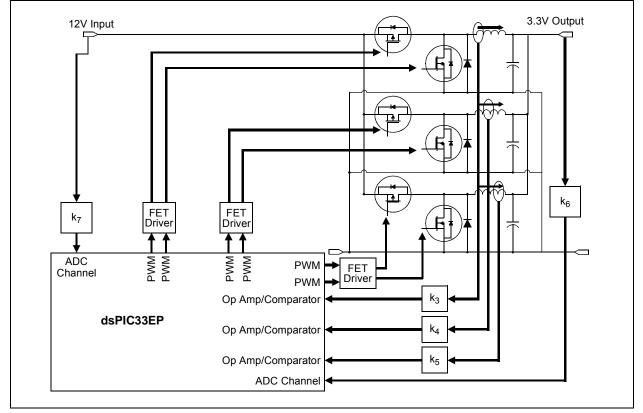

## 4.4.4 SOFTWARE STACK

The W15 register serves as a dedicated Software Stack Pointer (SSP) and is automatically modified by exception processing, subroutine calls and returns; however, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies reading, writing and manipulating of the Stack Pointer (for example, creating stack frames).

| Note: | To protect against misaligned stack               |

|-------|---------------------------------------------------|

|       | accesses, W15<0> is fixed to '0' by the hardware. |

W15 is initialized to 0x1000 during all Resets. This address ensures that the SSP points to valid RAM in all dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices, and permits stack availability for non-maskable trap exceptions. These can occur before the SSP is initialized by the user software. You can reprogram the SSP during initialization to any location within Data Space.

The Software Stack Pointer always points to the first available free word and fills the software stack working from lower toward higher addresses. Figure 4-19 illustrates how it pre-decrements for a stack pop (read) and post-increments for a stack push (writes).

When the PC is pushed onto the stack, PC<15:0> are pushed onto the first available stack word, then PC<22:16> are pushed into the second available stack location. For a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, as shown in Figure 4-19. During exception processing, the MSB of the PC is concatenated with the lower 8 bits of the CPU STATUS Register, SR. This allows the contents of SRL to be preserved automatically during interrupt processing.

- **Note 1:** To maintain system Stack Pointer (W15) coherency, W15 is never subject to (EDS) paging, and is therefore restricted to an address range of 0x0000 to 0xFFFF. The same applies to the W14 when used as a Stack Frame Pointer (SFA = 1).

- 2: As the stack can be placed in, and can access X and Y spaces, care must be taken regarding its use, particularly with regard to local automatic variables in a C development environment

FIGURE 4-19: CALL STACK FRAME

## REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

| bit 4 | MATHERR: Math Error Status bit                                                                        |

|-------|-------------------------------------------------------------------------------------------------------|

|       | 1 = Math error trap has occurred                                                                      |

|       | 0 = Math error trap has not occurred                                                                  |

| bit 3 | ADDRERR: Address Error Trap Status bit                                                                |

|       | <ul><li>1 = Address error trap has occurred</li><li>0 = Address error trap has not occurred</li></ul> |

| bit 2 | STKERR: Stack Error Trap Status bit                                                                   |

|       | 1 = Stack error trap has occurred                                                                     |

|       | 0 = Stack error trap has not occurred                                                                 |

| bit 1 | <b>OSCFAIL:</b> Oscillator Failure Trap Status bit                                                    |

|       | 1 = Oscillator failure trap has occurred                                                              |

|       | 0 = Oscillator failure trap has not occurred                                                          |

| bit 0 | Unimplemented: Read as '0'                                                                            |

Note 1: These bits are available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| REGISTER 7-5: | INTCON3: INTERRUPT CONTROL REGISTER 3 |

|---------------|---------------------------------------|

| U-0          | U-0          | U-0             | U-0              | U-0              | U-0              | U-0                | U-0   |  |

|--------------|--------------|-----------------|------------------|------------------|------------------|--------------------|-------|--|

|              | —            | _               | —                | —                | —                | —                  | _     |  |

| bit 15       |              |                 |                  |                  |                  |                    | bit 8 |  |

|              |              |                 |                  |                  |                  |                    |       |  |

| U-0          | U-0          | R/W-0           | R/W-0            | U-0              | U-0              | U-0                | U-0   |  |

| —            | —            | DAE             | DOOVR            | —                | —                | —                  | —     |  |

| bit 7        |              |                 |                  |                  |                  |                    | bit 0 |  |

|              |              |                 |                  |                  |                  |                    |       |  |

| Legend:      |              |                 |                  |                  |                  |                    |       |  |

| R = Readab   | le bit       | W = Writable    | bit              | U = Unimplei     | mented bit, read | as '0'             |       |  |

| -n = Value a | It POR       | '1' = Bit is se | t                | '0' = Bit is cle | eared            | x = Bit is unknown |       |  |

|              |              |                 |                  |                  |                  |                    |       |  |

| bit 15-6     | Unimplemen   | ted: Read as    | '0'              |                  |                  |                    |       |  |

| bit 5        | DAE: DMA A   | ddress Error S  | Soft Trap Status | s bit            |                  |                    |       |  |

|              | 1 = DMA add  | ress error soft | trap has occur   | red              |                  |                    |       |  |

|              | 0 = DMA add  | ress error soft | trap has not o   | ccurred          |                  |                    |       |  |

| bit 4        | DOOVR: DO    | Stack Overflov  | v Soft Trap Sta  | tus bit          |                  |                    |       |  |

|              | 1 = DO stack | overflow soft t | rap has occurre  | ed               |                  |                    |       |  |

| I = D0 | Stack Overnow  | 3011 11 ap 11 a3 | occurred     |

|--------|----------------|------------------|--------------|

| 0 = DO | stack overflow | soft trap has    | not occurred |

| bit 3-0 | Unimplemented: Read as '0' |

|---------|----------------------------|

|---------|----------------------------|

## REGISTER 7-6: INTCON4: INTERRUPT CONTROL REGISTER 4

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|-----|-----|-----|-----|-----|-----|-------|

| —       | —   | —   | —   | —   | —   | —   | —     |

| bit 15  |     |     |     |     | •   |     | bit 8 |

|         |     |     |     |     |     |     |       |

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 |

| _       | —   | —   |     | —   | —   | —   | SGHT  |

| bit 7   |     |     |     |     | •   |     | bit 0 |

|         |     |     |     |     |     |     |       |

| Legend: |     |     |     |     |     |     |       |

| 3                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

|                   |                  |                        |                    |

bit 0

SGHT: Software Generated Hard Trap Status bit

1 = Software generated hard trap has occurred

0 = Software generated hard trap has not occurred

| U-0                                                                | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|--------------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------------|---------------|-------------------|---------------|-----------------|--------|

| —                                                                  |                                          |                                                                              |               | SCK2INR<6:0       | >             |                 |        |

| bit 15                                                             |                                          |                                                                              |               |                   |               |                 | bit 8  |

|                                                                    |                                          |                                                                              |               |                   | 5444.6        | <b>D</b> 444 A  | 5444.6 |

| U-0                                                                | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|                                                                    |                                          |                                                                              |               | SDI2R<6:0>        |               |                 |        |

| bit 7                                                              |                                          |                                                                              |               |                   |               |                 | bit 0  |

|                                                                    |                                          |                                                                              |               |                   |               |                 |        |

| Legend:                                                            |                                          |                                                                              |               |                   |               |                 |        |

| R = Readable bitW = Writable bitU = Unimplemented bit, read as '0' |                                          |                                                                              |               |                   |               |                 |        |

| -n = Value a                                                       | t POR                                    | '1' = Bit is set                                                             |               | '0' = Bit is clea | ared          | x = Bit is unkr | nown   |

|                                                                    |                                          | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss                     | P1            |                   |               |                 |        |

| bit 7                                                              | Unimpleme                                | nted: Read as 'o                                                             | כי            |                   |               |                 |        |

| bit 6-0                                                            | (see Table 1 <sup>^</sup><br>1111001 = I | : Assign SPI2 D<br>1-2 for input pin<br>nput tied to RPI<br>nput tied to CMI | selection num | ,                 | esponding RPi | ר Pin bits      |        |

## REGISTER 11-12: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0 | R/W-0      | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|-----|------------|------------|-------|-------|-------|-------|--|--|

| —      | —   |            | RP43R<5:0> |       |       |       |       |  |  |

| bit 15 |     |            |            |       |       |       | bit 8 |  |  |

|        |     |            |            |       |       |       |       |  |  |

| U-0    | U-0 | R/W-0      | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

| —      | —   | RP42R<5:0> |            |       |       |       |       |  |  |

## REGISTER 11-22: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4

|   | bit | 7 |

|---|-----|---|

| 1 |     |   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP43R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP43 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP42R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP42 Output Pin bits (see Table 11-3 for peripheral function numbers) |

## REGISTER 11-23: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | RP55  | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|

| —     | —   |       | RP54R<5:0> |       |       |       |       |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP55R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP55 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP54R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP54 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 0

## REGISTER 18-1: SPIx STAT: SPIx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

- 1 = Transmit not yet started, SPIxTXB is full

- 0 = Transmit started, SPIxTXB is empty

### Standard Buffer mode:

Automatically set in hardware when core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when SPIx module transfers data from SPIxTXB to SPIxSR.

## Enhanced Buffer mode:

Automatically set in hardware when the CPU writes to the SPIxBUF location, loading the last available buffer location. Automatically cleared in hardware when a buffer location is available for a CPU write operation.

### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive is complete, SPIxRXB is full

0 = Receive is incomplete, SPIxRXB is empty

### Standard Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when the core reads the SPIxBUF location, reading SPIxRXB.

### Enhanced Buffer mode:

Automatically set in hardware when SPIx transfers data from SPIxSR to the buffer, filling the last unread buffer location. Automatically cleared in hardware when a buffer location is available for a transfer from SPIxSR.

## 19.0 INTER-INTEGRATED CIRCUIT<sup>™</sup> (I<sup>2</sup>C<sup>™</sup>)

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70330) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

- 3: There are minimum bit rates of approximately FCY/512. As a result, high processor speeds may not support 100 Kbit/second operation. See timing specifications, IM10 and IM11, and the "Baud Rate Generator" in the "dsPIC33/PIC24 Family Reference Manual".

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X family of devices contains two Inter-Integrated Circuit (I<sup>2</sup>C) modules: I2C1 and I2C2.

The  $l^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard, with a 16-bit interface.

The  $I^2C$  module has a 2-pin interface:

- · The SCLx pin is clock

- The SDAx pin is data

The I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both Master and Slave modes of operation

- I<sup>2</sup>C Slave mode supports 7 and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7 and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation, detects bus collision and arbitrates accordingly

- Intelligent Platform Management Interface (IPMI)

support

- System Management Bus (SMBus) support

| U-0          | U-0                                | R-0                        | R-0            | R-0               | R-0              | R-0             | R-0   |  |  |  |  |

|--------------|------------------------------------|----------------------------|----------------|-------------------|------------------|-----------------|-------|--|--|--|--|

| _            |                                    | FBP5                       | FBP4           | FBP3              | FBP2             | FBP1            | FBP0  |  |  |  |  |

| bit 15       |                                    |                            |                |                   |                  |                 | bit 8 |  |  |  |  |

|              |                                    |                            |                |                   |                  |                 |       |  |  |  |  |

| U-0          | U-0                                | R-0                        | R-0            | R-0               | R-0              | R-0             | R-0   |  |  |  |  |

|              |                                    | FNRB5                      | FNRB4          | FNRB3             | FNRB2            | FNRB1           | FNRB0 |  |  |  |  |

| bit 7        |                                    |                            |                |                   |                  |                 | bit ( |  |  |  |  |

| Legend:      |                                    |                            |                |                   |                  |                 |       |  |  |  |  |

| R = Readab   | le bit                             | W = Writable               | bit            | U = Unimplen      | nented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value a | t POR                              | '1' = Bit is set           |                | '0' = Bit is clea |                  | x = Bit is unkr | iown  |  |  |  |  |

|              |                                    |                            |                |                   |                  |                 |       |  |  |  |  |

| bit 15-14    | Unimpleme                          | ented: Read as '           | 0'             |                   |                  |                 |       |  |  |  |  |

| bit 13-8     | FBP<5:0>: FIFO Buffer Pointer bits |                            |                |                   |                  |                 |       |  |  |  |  |

|              |                                    | 011111 = RB31 buffer       |                |                   |                  |                 |       |  |  |  |  |

|              | 011110 <b>= F</b>                  | RB30 buffer                |                |                   |                  |                 |       |  |  |  |  |

|              | •                                  |                            |                |                   |                  |                 |       |  |  |  |  |

|              | •                                  |                            |                |                   |                  |                 |       |  |  |  |  |

|              | •                                  | TRB1 buffer                |                |                   |                  |                 |       |  |  |  |  |

|              |                                    | TRB0 buffer                |                |                   |                  |                 |       |  |  |  |  |

| bit 7-6      | Unimpleme                          | ented: Read as '           | 0'             |                   |                  |                 |       |  |  |  |  |

| bit 5-0      | FNRB<5:0                           | >: FIFO Next Rea           | ad Buffer Poir | iter bits         |                  |                 |       |  |  |  |  |

|              | 011111 <b>= F</b>                  | RB31 buffer                |                |                   |                  |                 |       |  |  |  |  |

|              | 011110 <b>= F</b>                  | RB30 buffer                |                |                   |                  |                 |       |  |  |  |  |

|              | •                                  |                            |                |                   |                  |                 |       |  |  |  |  |

|              | •                                  |                            |                |                   |                  |                 |       |  |  |  |  |

|              | •                                  |                            |                |                   |                  |                 |       |  |  |  |  |

|              |                                    |                            |                |                   |                  |                 |       |  |  |  |  |

|              |                                    | FRB1 buffer<br>FRB0 buffer |                |                   |                  |                 |       |  |  |  |  |

## REGISTER 21-5: CxFIFO: ECANx FIFO STATUS REGISTER

| PTG Output<br>Number | PTG Output Description                                  |

|----------------------|---------------------------------------------------------|

| PTGO0                | Trigger/Synchronization Source for OC1                  |

| PTGO1                | Trigger/Synchronization Source for OC2                  |

| PTGO2                | Trigger/Synchronization Source for OC3                  |

| PTGO3                | Trigger/Synchronization Source for OC4                  |

| PTGO4                | Clock Source for OC1                                    |

| PTGO5                | Clock Source for OC2                                    |

| PTGO6                | Clock Source for OC3                                    |

| PTGO7                | Clock Source for OC4                                    |

| PTGO8                | Trigger/Synchronization Source for IC1                  |

| PTGO9                | Trigger/Synchronization Source for IC2                  |

| PTGO10               | Trigger/Synchronization Source for IC3                  |

| PTGO11               | Trigger/Synchronization Source for IC4                  |

| PTGO12               | Sample Trigger for ADC                                  |

| PTGO13               | Sample Trigger for ADC                                  |

| PTGO14               | Sample Trigger for ADC                                  |

| PTGO15               | Sample Trigger for ADC                                  |

| PTGO16               | PWM Time Base Synchronous Source for PWM <sup>(1)</sup> |

| PTGO17               | PWM Time Base Synchronous Source for PWM <sup>(1)</sup> |

| PTGO18               | Mask Input Select for Op Amp/Comparator                 |

| PTGO19               | Mask Input Select for Op Amp/Comparator                 |

| PTGO20               | Reserved                                                |

| PTGO21               | Reserved                                                |

| PTGO22               | Reserved                                                |

| PTGO23               | Reserved                                                |

| PTGO24               | Reserved                                                |

| PTGO25               | Reserved                                                |

| PTGO26               | Reserved                                                |

| PTGO27               | Reserved                                                |

| PTGO28               | Reserved                                                |

| PTGO29               | Reserved                                                |

| PTGO30               | PTG Output to PPS Input Selection                       |

| PTGO31               | PTG Output to PPS Input Selection                       |

## TABLE 24-2: PTG OUTPUT DESCRIPTIONS

Note 1: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

| U-0          | U-0                                                    | U-0                                                                                 | U-0              | U-0              | U-0              | U-0            | U-0    |  |  |  |  |

|--------------|--------------------------------------------------------|-------------------------------------------------------------------------------------|------------------|------------------|------------------|----------------|--------|--|--|--|--|

|              | —                                                      | —                                                                                   | _                | —                |                  | —              | _      |  |  |  |  |

| bit 15       |                                                        |                                                                                     |                  |                  |                  |                | bit    |  |  |  |  |

|              |                                                        |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

| U-0          | R/W-0                                                  | R/W-0                                                                               | R/W-0            | R/W-0            | R/W-0            | R/W-0          | R/W-0  |  |  |  |  |

|              | CFSEL2                                                 | CFSEL1                                                                              | CFSEL0           | CFLTREN          | CFDIV2           | CFDIV1         | CFDIV0 |  |  |  |  |

| bit 7        |                                                        |                                                                                     |                  |                  |                  |                | bit    |  |  |  |  |

| Legend:      |                                                        |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

| R = Readab   | le bit                                                 | W = Writable                                                                        | bit              | U = Unimpler     | mented bit, read | as '0'         |        |  |  |  |  |

| -n = Value a |                                                        | '1' = Bit is set                                                                    |                  | '0' = Bit is cle |                  | x = Bit is unk | nown   |  |  |  |  |

|              |                                                        |                                                                                     |                  |                  |                  |                | -      |  |  |  |  |

| bit 15-7     | Unimplemen                                             | ted: Read as                                                                        | ʻ0'              |                  |                  |                |        |  |  |  |  |

| bit 6-4      | CFSEL<2:0>                                             | : Comparator                                                                        | Filter Input Clo | ock Select bits  |                  |                |        |  |  |  |  |

|              |                                                        | CFSEL<2:0>: Comparator Filter Input Clock Select bits<br>111 = T5CLK <sup>(1)</sup> |                  |                  |                  |                |        |  |  |  |  |

|              |                                                        | $110 = T4CLK^{(2)}$                                                                 |                  |                  |                  |                |        |  |  |  |  |

|              | 101 = T3CLK                                            | $101 = T3CLK^{(1)}$                                                                 |                  |                  |                  |                |        |  |  |  |  |

|              | $100 = T2CLK^{(2)}$                                    |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

|              |                                                        | 011 = Reserved                                                                      |                  |                  |                  |                |        |  |  |  |  |

|              | 010 = SYNC                                             | 01 <sup>(3)</sup>                                                                   |                  |                  |                  |                |        |  |  |  |  |

|              |                                                        | $001 = Fosc^{(4)}$                                                                  |                  |                  |                  |                |        |  |  |  |  |

|              | 000 = FP <sup>(4)</sup>                                |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

| bit 3        | CFLTREN: Comparator Filter Enable bit                  |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

|              | 1 = Digital filter is enabled                          |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

|              | •                                                      | er is disabled                                                                      |                  |                  |                  |                |        |  |  |  |  |

| bit 2-0      | CFDIV<2:0>: Comparator Filter Clock Divide Select bits |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

|              | 111 = Clock Divide 1:128                               |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

|              | 110 = Clock Divide 1:64                                |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

|              | 101 = Clock Divide 1:32                                |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

|              | 100 = Clock                                            | 100 = Clock Divide 1:16                                                             |                  |                  |                  |                |        |  |  |  |  |

|              |                                                        | 011 = Clock Divide 1:8                                                              |                  |                  |                  |                |        |  |  |  |  |

|              | 010 = Clock Divide 1:4                                 |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

|              | 001 = Clock Divide 1:2                                 |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

|              | 000 = Clock                                            | Divide 1:1                                                                          |                  |                  |                  |                |        |  |  |  |  |

| Note 1: S    | See the Type C Ti                                      | mer Block Diag                                                                      | gram (Figure 1   | 3-2).            |                  |                |        |  |  |  |  |

|              | See the Type B Timer Block Diagram (Figure 13-1).      |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

| •            |                                                        |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

## REGISTER 25-6: CMxFLTR: COMPARATOR x FILTER CONTROL REGISTER

- 3: See the High-Speed PWMx Module Register Interconnection Diagram (Figure 16-2).

- 4: See the Oscillator System Diagram (Figure 9-1).

## dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 26-3: CRCXORH: CRC XOR POLYNOMIAL HIGH REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0            | R/W-0 | R/W-0           | R/W-0 |  |  |

|------------------------------------|-------|-------|------------------------------------|------------------|-------|-----------------|-------|--|--|

| X<31:24>                           |       |       |                                    |                  |       |                 |       |  |  |

| bit 15 bi                          |       |       |                                    |                  |       |                 |       |  |  |

|                                    |       |       |                                    |                  |       |                 |       |  |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0            | R/W-0 | R/W-0           | R/W-0 |  |  |

|                                    |       |       | X<2                                | 23:16>           |       |                 |       |  |  |

| bit 7 bit 0                        |       |       |                                    |                  |       |                 |       |  |  |

|                                    |       |       |                                    |                  |       |                 |       |  |  |

| Legend:                            |       |       |                                    |                  |       |                 |       |  |  |

| R = Readable bit W = Writable bit  |       |       | U = Unimplemented bit, read as '0' |                  |       |                 |       |  |  |

| -n = Value at POR '1' = Bit is set |       |       |                                    | '0' = Bit is cle | ared  | x = Bit is unkr | nown  |  |  |

|                                    | -     |       |                                    |                  |       |                 | -     |  |  |

bit 15-0 X<31:16>: XOR of Polynomial Term X<sup>n</sup> Enable bits

### REGISTER 26-4: CRCXORL: CRC XOR POLYNOMIAL LOW REGISTER

| R/W-0                             | R/W-0                              | R/W-0 | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | R/W-0 |

|-----------------------------------|------------------------------------|-------|------------------------------------|-------------------|-------|-----------------|-------|

|                                   |                                    |       | Х<                                 | 15:8>             |       |                 |       |

| bit 15                            |                                    |       |                                    |                   |       |                 | bit 8 |

| R/W-0                             | R/W-0                              | R/W-0 | R/W-0                              | R/W-0             | R/W-0 | R/W-0           | U-0   |

|                                   |                                    |       | X<7:1>                             |                   |       |                 | _     |

| bit 7                             |                                    |       |                                    |                   |       |                 | bit 0 |

| Legend:                           |                                    |       |                                    |                   |       |                 |       |

| R = Readable bit W = Writable bit |                                    |       | U = Unimplemented bit, read as '0' |                   |       |                 |       |

| -n = Value at P                   | -n = Value at POR '1' = Bit is set |       |                                    | '0' = Bit is clea | ared  | x = Bit is unkr | nown  |

bit 15-1X<15:1>: XOR of Polynomial Term X<sup>n</sup> Enable bitsbit 0Unimplemented: Read as '0'

## FIGURE 30-29: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

| DC CHARACTERISTICS                 |       |                                                          | $\begin{array}{l} \mbox{Standard Operating Conditions:3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |       |      |                                   |                                   |  |

|------------------------------------|-------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-----------------------------------|-----------------------------------|--|

| Param<br>No. Symbol Characteristic |       |                                                          | Min.                                                                                                                                                                                                                                                                                   | Тур.  | Max. | Units                             | Conditions                        |  |

| CTMU Current Source                |       |                                                          |                                                                                                                                                                                                                                                                                        |       |      |                                   |                                   |  |

| CTMUI1                             | Ιουτ1 | Base Range <sup>(1)</sup>                                | 0.29                                                                                                                                                                                                                                                                                   |       | 0.77 | μA                                | CTMUICON<9:8> = 01                |  |

| CTMUI2                             | IOUT2 | 10x Range <sup>(1)</sup>                                 | 3.85                                                                                                                                                                                                                                                                                   |       | 7.7  | μA                                | CTMUICON<9:8> = 10                |  |

| CTMUI3                             | Ιουτ3 | 100x Range <sup>(1)</sup>                                | 38.5                                                                                                                                                                                                                                                                                   | _     | 77   | μA                                | CTMUICON<9:8> = 11                |  |

| CTMUI4                             | IOUT4 | 1000x Range <sup>(1)</sup>                               | 385                                                                                                                                                                                                                                                                                    | _     | 770  | μA                                | CTMUICON<9:8> = 00                |  |

| CTMUFV1                            | VF    | Temperature Diode Forward Voltage <sup>(1,2)</sup>       | _                                                                                                                                                                                                                                                                                      | 0.598 | _    | V                                 | TA = +25°C,<br>CTMUICON<9:8> = 01 |  |

|                                    |       | _                                                        | 0.658                                                                                                                                                                                                                                                                                  | _     | V    | TA = +25°C,<br>CTMUICON<9:8> = 10 |                                   |  |

|                                    |       |                                                          | _                                                                                                                                                                                                                                                                                      | 0.721 | _    | V                                 | TA = +25°C,<br>CTMUICON<9:8> = 11 |  |

| CTMUFV2                            | VFVR  | /FVR Temperature Diode Rate of Change <sup>(1,2,3)</sup> | _                                                                                                                                                                                                                                                                                      | -1.92 | _    | mV/ºC                             | CTMUICON<9:8> = 01                |  |

|                                    |       |                                                          | _                                                                                                                                                                                                                                                                                      | -1.74 | _    | mV/ºC                             | CTMUICON<9:8> = 10                |  |

|                                    |       |                                                          |                                                                                                                                                                                                                                                                                        | -1.56 | _    | mV/ºC                             | CTMUICON<9:8> = 11                |  |

## TABLE 30-56: CTMU CURRENT SOURCE SPECIFICATIONS

Note 1: Nominal value at center point of current trim range (CTMUICON<15:10> = 000000).

2: Parameters are characterized but not tested in manufacturing.

**3:** Measurements taken with the following conditions:

- VREF+ = AVDD = 3.3V

- ADC configured for 10-bit mode

- ADC module configured for conversion speed of 500 ksps

- All PMDx bits are cleared (PMDx = 0)

- Executing a while(1) statement

- · Device operating from the FRC with no PLL

# 32.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

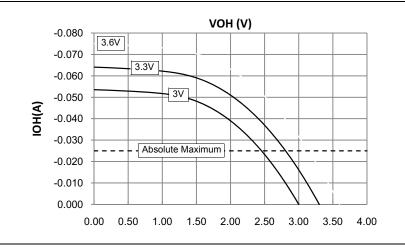

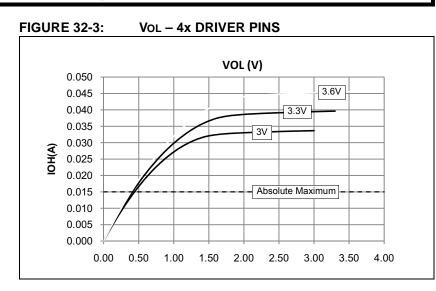

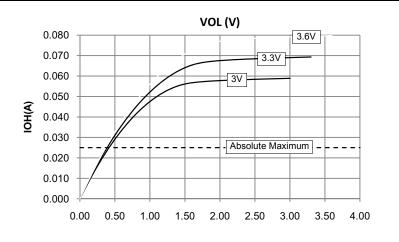

**Note:** The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

**FIGURE 32-1: VOH – 4x DRIVER PINS** VOH (V) -0.050 -0.045 3.6V -0.040 3.3V -0.035 3V -0.030 IOH(A) -0.025 -0.020 Absolute Maximum -0.015 -0.010 -0.005 0.000 0.50 1.00 2.00 2.50 3.00 3.50 0.00 1.50 4.00

## FIGURE 32-2: VOH – 8x DRIVER PINS

## FIGURE 32-4: Vol – 8x DRIVER PINS

NOTES:

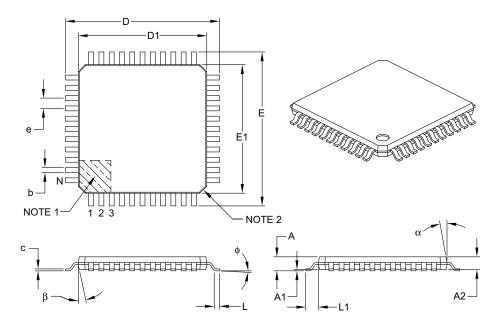

## 44-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units       |           | MILLIMETERS | 6    |  |  |  |

|--------------------------|-------------|-----------|-------------|------|--|--|--|

| Dimens                   | sion Limits | MIN       | NOM         | MAX  |  |  |  |

| Number of Leads          | Ν           |           | 44          |      |  |  |  |

| Lead Pitch               | е           |           | 0.80 BSC    |      |  |  |  |

| Overall Height           | А           | -         | -           | 1.20 |  |  |  |

| Molded Package Thickness | A2          | 0.95      | 1.00        | 1.05 |  |  |  |

| Standoff                 | A1          | 0.05      | -           | 0.15 |  |  |  |

| Foot Length              | L           | 0.45      | 0.60        | 0.75 |  |  |  |

| Footprint                | L1 1.00 REF |           |             |      |  |  |  |

| Foot Angle               | φ           | 0°        | 3.5°        | 7°   |  |  |  |

| Overall Width            | E           | 12.00 BSC |             |      |  |  |  |

| Overall Length           | D           | 12.00 BSC |             |      |  |  |  |

| Molded Package Width     | E1          | 10.00 BSC |             |      |  |  |  |

| Molded Package Length    | D1          | 10.00 BSC |             |      |  |  |  |

| Lead Thickness           | с           | 0.09      | -           | 0.20 |  |  |  |

| Lead Width               | b           | 0.30      | 0.37        | 0.45 |  |  |  |

| Mold Draft Angle Top     | α           | 11°       | 12°         | 13°  |  |  |  |

| Mold Draft Angle Bottom  | β           | 11°       | 12°         | 13°  |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-076B