Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

⊡XFI

| Product Status             | Obsolete                                                                         |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 4K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc202t-e-mm |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

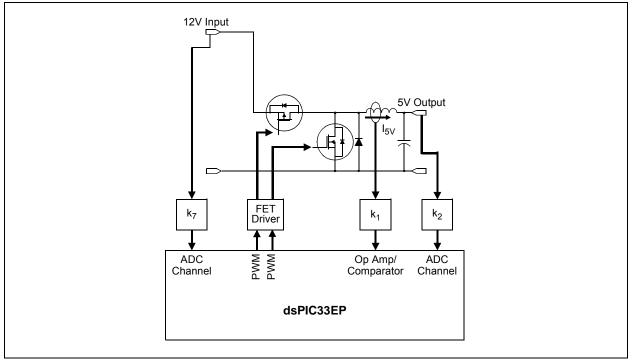

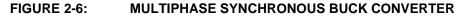

#### FIGURE 2-5: SINGLE-PHASE SYNCHRONOUS BUCK CONVERTER

## 3.7 CPU Control Registers

| REGISTER               | 3-1: SR: Cl                                          | PU STATUS I                            | REGISTER                    |                          |                    |                   |               |

|------------------------|------------------------------------------------------|----------------------------------------|-----------------------------|--------------------------|--------------------|-------------------|---------------|

| R/W-0                  | R/W-0                                                | R/W-0                                  | R/W-0                       | R/C-0                    | R/C-0              | R-0               | R/W-0         |

| 0A <sup>(1)</sup>      | OB <sup>(1)</sup>                                    | SA <sup>(1,4)</sup>                    | SB <sup>(1,4)</sup>         | OAB <sup>(1)</sup>       | SAB <sup>(1)</sup> | DA <sup>(1)</sup> | DC            |

| bit 15                 |                                                      |                                        |                             |                          |                    |                   | bit 8         |

| R/W-0 <sup>(2,3)</sup> | R/W-0 <sup>(2,3)</sup>                               | R/W-0 <sup>(2,3)</sup>                 | R-0                         | R/W-0                    | R/W-0              | R/W-0             | R/W-0         |

| IPL2                   | IPL1                                                 | IPL0                                   | RA                          | N                        | OV                 | Z                 | С             |

| bit 7                  | ·                                                    | •                                      |                             | •                        |                    |                   | bit (         |

| Legend:                |                                                      | C = Clearable                          | e bit                       |                          |                    |                   |               |

| R = Readab             | le bit                                               | W = Writable                           | bit                         | U = Unimpler             | nented bit, read   | l as '0'          |               |

| -n = Value a           | t POR                                                | '1'= Bit is set                        |                             | '0' = Bit is cle         | ared               | x = Bit is unkr   | iown          |

|                        |                                                      |                                        |                             |                          |                    |                   |               |

| bit 15                 | OA: Accumul                                          | ator A Overflov                        | v Status bit <sup>(1)</sup> |                          |                    |                   |               |

|                        | 1 = Accumula                                         | ator A has over                        | flowed                      |                          |                    |                   |               |

|                        | 0 = Accumula                                         | ator A has not o                       | verflowed                   |                          |                    |                   |               |

| bit 14                 | OB: Accumul                                          | ator B Overflov                        | v Status bit <sup>(1)</sup> |                          |                    |                   |               |

|                        | 1 = Accumula                                         | ator B has over                        | flowed                      |                          |                    |                   |               |

|                        |                                                      | ator B has not c                       |                             |                          |                    |                   |               |

| bit 13                 | SA: Accumul                                          | ator A Saturatio                       | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |

|                        |                                                      | ator A is saturat<br>ator A is not sat |                             | en saturated at          | some time          |                   |               |

| bit 12                 | SB: Accumul                                          | ator B Saturatio                       | on 'Sticky' Sta             | tus bit <sup>(1,4)</sup> |                    |                   |               |

|                        | 1 = Accumula                                         | ator B is saturat<br>ator B is not sat | ted or has bee              |                          | some time          |                   |               |

| bit 11                 |                                                      | B Combined A                           |                             | vorflow Status           | ы#(1)              |                   |               |

|                        |                                                      | ators A or B have                      |                             | vernow Status            | DIL                |                   |               |

|                        |                                                      | ccumulators A                          |                             | erflowed                 |                    |                   |               |

| bit 10                 |                                                      | B Combined Ad                          |                             |                          | (1)                |                   |               |

|                        |                                                      |                                        |                             |                          | urated at some     | time              |               |

|                        | 0 = Neither A                                        | ccumulators A                          | or B are satur              | ated                     |                    |                   |               |

| bit 9                  | DA: DO Loop                                          | Active bit <sup>(1)</sup>              |                             |                          |                    |                   |               |

|                        | 1 = DO <b>loop is</b>                                | s in progress                          |                             |                          |                    |                   |               |

|                        | 0 = DO <b>loop</b> is                                | s not in progres                       | S                           |                          |                    |                   |               |

| bit 8                  | DC: MCU AL                                           | U Half Carry/Bo                        | orrow bit                   |                          |                    |                   |               |

|                        |                                                      | out from the 4th sult occurred         | low-order bit (             | for byte-sized c         | lata) or 8th low-  | order bit (for wo | rd-sized data |

|                        | 0 = No carry                                         |                                        |                             | oit (for byte-siz        | ed data) or 8th    | low-order bit (f  | or word-size  |

|                        | his bit is available                                 |                                        |                             |                          |                    |                   | -             |

| L                      | he IPL<2:0> bits<br>evel. The value ir<br>PL<3> = 1. |                                        |                             |                          |                    |                   |               |

#### REGISTER 3-1: SR: CPU STATUS REGISTER

- 3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- **4:** A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

## 4.4 Special Function Register Maps

## TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND dsPIC33EPXXXGP50X DEVICES ONLY

|           |       | 0.00   |        |        |              | 011 401    |        |       | 20/00/      |        |       |        |         |          |          | -     | r     |               |

|-----------|-------|--------|--------|--------|--------------|------------|--------|-------|-------------|--------|-------|--------|---------|----------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12       | Bit 11     | Bit 10 | Bit 9 | Bit 8       | Bit 7  | Bit 6 | Bit 5  | Bit 4   | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| W0        | 0000  |        |        |        |              |            |        |       | W0 (WR      | EG)    |       |        |         |          |          |       |       | xxxx          |

| W1        | 0002  |        |        |        |              |            |        |       | W1          |        |       |        |         |          |          |       |       | xxxx          |

| W2        | 0004  |        |        |        |              |            |        |       | W2          |        |       |        |         |          |          |       |       | xxxx          |

| W3        | 0006  |        |        |        |              |            |        |       | W3          |        |       |        |         |          |          |       |       | xxxx          |

| W4        | 8000  |        |        |        |              |            |        |       | W4          |        |       |        |         |          |          |       |       | xxxx          |

| W5        | 000A  |        |        |        |              |            |        |       | W5          |        |       |        |         |          |          |       |       | xxxx          |

| W6        | 000C  |        |        |        |              |            |        |       | W6          |        |       |        |         |          |          |       |       | xxxx          |

| W7        | 000E  |        |        |        |              |            |        |       | W7          |        |       |        |         |          |          |       |       | xxxx          |

| W8        | 0010  |        |        |        |              |            |        |       | W8          |        |       |        |         |          |          |       |       | xxxx          |

| W9        | 0012  |        |        |        |              |            |        |       | W9          |        |       |        |         |          |          |       |       | xxxx          |

| W10       | 0014  |        |        |        |              |            |        |       | W10         |        |       |        |         |          |          |       |       | xxxx          |

| W11       | 0016  |        |        |        |              |            |        |       | W11         |        |       |        |         |          |          |       |       | xxxx          |

| W12       | 0018  |        |        |        |              |            |        |       | W12         |        |       |        |         |          |          |       |       | xxxx          |

| W13       | 001A  |        |        |        |              |            |        |       | W13         |        |       |        |         |          |          |       |       | xxxx          |

| W14       | 001C  |        |        |        |              |            |        |       | W14         |        |       |        |         |          |          |       |       | xxxx          |

| W15       | 001E  |        |        |        |              |            |        |       | W15         |        |       |        |         |          |          |       |       | xxxx          |

| SPLIM     | 0020  |        |        |        |              |            |        |       | SPLI        | N      |       |        |         |          |          |       |       | 0000          |

| ACCAL     | 0022  |        |        |        |              |            |        |       | ACCA        | L      |       |        |         |          |          |       |       | 0000          |

| ACCAH     | 0024  |        |        |        |              |            |        |       | ACCA        | H      |       |        |         |          |          |       |       | 0000          |

| ACCAU     | 0026  |        |        | Si     | gn Extensior | n of ACCA< | 39>    |       |             |        |       |        | ACO     | CAU      |          |       |       | 0000          |

| ACCBL     | 0028  |        |        |        |              |            |        |       | ACCB        | L      |       |        |         |          |          |       |       | 0000          |

| ACCBH     | 002A  |        |        |        |              |            |        |       | ACCB        | Н      |       |        |         |          |          |       |       | 0000          |

| ACCBU     | 002C  |        |        | Si     | gn Extensior | n of ACCB< | 39>    |       |             |        |       |        | ACO     | CBU      |          |       |       | 0000          |

| PCL       | 002E  |        |        |        |              |            |        | F     | PCL<15:0>   |        |       |        |         |          |          |       | —     | 0000          |

| PCH       | 0030  | _      | _      | _      | —            | _          | _      | —     | _           | _      |       |        |         | PCH<6:0> |          |       |       | 0000          |

| DSRPAG    | 0032  | _      | _      | _      | —            | _          | _      |       |             |        |       | DSRPAC | 6<9:0>  |          |          |       |       | 0001          |

| DSWPAG    | 0034  | _      |        | _      | —            |            | _      | _     |             |        |       | DS     | WPAG<8: | 0>       |          |       |       | 0001          |

| RCOUNT    | 0036  |        |        |        |              |            |        |       | RCOUNT<     | :15:0> |       |        |         |          |          |       |       | 0000          |

| DCOUNT    | 0038  |        |        |        |              |            |        |       | DCOUNT<     | :15:0> |       |        |         |          |          |       |       | 0000          |

| DOSTARTL  | 003A  |        |        |        |              |            |        | DOS   | STARTL<15:1 | >      |       |        |         |          |          |       |       | 0000          |

| DOSTARTH  | 003C  | _      | —      | —      | _            | —          | —      | _     | _           | _      | —     |        |         | DOSTAF   | RTH<5:0> |       |       | 0000          |

| DOENDL    | 003E  |        |        |        |              |            |        | DO    | ENDL<15:1>  | >      |       |        |         |          |          |       |       | 0000          |

| DOENDH    | 0040  | _      | —      | —      | —            | —          | —      | _     | —           | —      | —     |        |         | DOEND    | )H<5:0>  |       |       | 0000          |

|           |       |        |        |        |              |            |        |       |             |        |       |        |         |          |          |       |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-6: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|---------|--------|------------|-------|----------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | )>      | —       |        | ICDIP<2:0  | >     | _        | —       | —           | _       | —       | _      | -           |        | 4400          |

| IPC36        | 0888  | -      | l      | PTG0IP<2:0 | )>      | _       | PT     | GWDTIP<    | 2:0>  | _        | P       | TGSTEPIP<2  | :0>     | —       | —      |             |        | 4440          |

| IPC37        | 088A  |        | _      | _          | _       | _       | F      | PTG3IP<2:0 | )>    | _        |         | PTG2IP<2:0> | >       | _       | F      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | —       | _      |            |       | —        | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | _      | —          | —       | —       | _      |            |       | —        | _       | DAE         | DOOVR   | _       | —      |             |        | 0000          |

| INTCON4      | 08C6  | -      | _      | —          | _       | _       | _      |            | _     | _        | _       | —           | —       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | -      | —      | —          | _       |         | ILR<   | 3:0>       |       |          |         |             | VECNU   | M<7:0>  |        |             |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

|                 |       |        |          |         |         |         |            |         |          |         |        |       |       |        |          |          |        | All    |

|-----------------|-------|--------|----------|---------|---------|---------|------------|---------|----------|---------|--------|-------|-------|--------|----------|----------|--------|--------|

| File Name       | Addr. | Bit 15 | Bit 14   | Bit 13  | Bit 12  | Bit 11  | Bit 10     | Bit 9   | Bit 8    | Bit 7   | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1    | Bit 0  | Resets |

| PTGCST          | 0AC0  | PTGEN  | —        | PTGSIDL | PTGTOGL |         | PTGSWT     | PTGSSEN | PTGIVIS  | PTGSTRT | PTGWTO | _     | _     | —      | —        | PTGIT    | M<1:0> | 0000   |

| PTGCON          | 0AC2  | F      | PTGCLK<2 | :0>     |         | F       | PTGDIV<4:0 | >       |          |         | PTGPWD | <3:0> |       | _      | P        | TGWDT<2: | 0>     | 0000   |

| PTGBTE          | 0AC4  |        | ADC      | TS<4:1> |         | IC4TSS  | IC3TSS     | IC2TSS  | IC1TSS   | OC4CS   | OC3CS  | OC2CS | OC1CS | OC4TSS | OC3TSS   | OC2TSS   | OC1TSS | 0000   |

| PTGHOLD         | 0AC6  |        |          |         |         |         |            |         | PTGHOLD  | <15:0>  |        |       |       |        |          |          |        | 0000   |

| <b>PTGT0LIM</b> | 0AC8  |        |          |         |         |         |            |         | PTGT0LIM | <15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGT1LIM        | 0ACA  |        |          |         |         |         |            |         | PTGT1LIM | <15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGSDLIM        | 0ACC  |        |          |         |         |         |            |         | PTGSDLIN | l<15:0> |        |       |       |        |          |          |        | 0000   |

| <b>PTGC0LIM</b> | 0ACE  |        |          |         |         |         |            |         | PTGC0LIN | <15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGC1LIM        | 0AD0  |        |          |         |         |         |            |         | PTGC1LIN | <15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGADJ          | 0AD2  |        |          |         |         |         |            |         | PTGADJ<  | :15:0>  |        |       |       |        |          |          |        | 0000   |

| PTGL0           | 0AD4  |        |          |         |         |         |            |         | PTGL0<   | 15:0>   |        |       |       |        |          |          |        | 0000   |

| PTGQPTR         | 0AD6  | —      | —        | —       | —       | _       | —          | —       | _        | —       | —      | -     |       | P      | TGQPTR<4 | 4:0>     |        | 0000   |

| PTGQUE0         | 0AD8  |        |          |         | STEP    | 1<7:0>  |            |         |          |         |        |       | STEPO | )<7:0> |          |          |        | 0000   |

| PTGQUE1         | 0ADA  |        |          |         | STEP    | '3<7:0> |            |         |          |         |        |       | STEP2 | 2<7:0> |          |          |        | 0000   |

| PTGQUE2         | 0ADC  |        |          |         | STEP    | 25<7:0> |            |         |          |         |        |       | STEP4 | <7:0>  |          |          |        | 0000   |

| PTGQUE3         | 0ADE  |        |          |         | STEP    | 7<7:0>  |            |         |          |         |        |       | STEP6 | 6<7:0> |          |          |        | 0000   |

| PTGQUE4         | 0AE0  |        |          |         | STEP    | 9<7:0>  |            |         |          |         |        |       | STEP8 | 8<7:0> |          |          |        | 0000   |

| PTGQUE5         | 0AE2  |        |          |         | STEP    | 11<7:0> |            |         |          |         |        |       | STEP1 | 0<7:0> |          |          |        | 0000   |

| PTGQUE6         | 0AE4  |        |          |         | STEP    | 13<7:0> |            |         |          |         |        |       | STEP1 | 2<7:0> |          |          |        | 0000   |

| PTGQUE7         | 0AE6  |        |          |         | STEP    | 15<7:0> |            |         |          |         |        |       | STEP1 | 4<7:0> |          |          |        | 0000   |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 78

Allocating different Page registers for read and write access allows the architecture to support data movement between different pages in data memory. This is accomplished by setting the DSRPAG register value to the page from which you want to read, and configuring the DSWPAG register to the page to which it needs to be written. Data can also be moved from different PSV to EDS pages, by configuring the DSRPAG and DSWPAG registers to address PSV and EDS space, respectively. The data can be moved between pages by a single instruction.

When an EDS or PSV page overflow or underflow occurs, EA<15> is cleared as a result of the register indirect EA calculation. An overflow or underflow of the EA in the EDS or PSV pages can occur at the page boundaries when:

- The initial address prior to modification addresses an EDS or PSV page

- The EA calculation uses Pre-Modified or Post-Modified Register Indirect Addressing; however, this does not include Register Offset Addressing

In general, when an overflow is detected, the DSxPAG register is incremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. When an underflow is detected, the DSxPAG register is decremented and the EA<15> bit is set to keep the base address within the EDS or PSV window. This creates a linear EDS and PSV address space, but only when using Register Indirect Addressing modes.

Exceptions to the operation described above arise when entering and exiting the boundaries of Page 0, EDS and PSV spaces. Table 4-61 lists the effects of overflow and underflow scenarios at different boundaries.

In the following cases, when overflow or underflow occurs, the EA<15> bit is set and the DSxPAG is not modified; therefore, the EA will wrap to the beginning of the current page:

- · Register Indirect with Register Offset Addressing

- Modulo Addressing

- · Bit-Reversed Addressing

|             | -                   | SV SI ACE BOON |              |                        |                |              |                        |

|-------------|---------------------|----------------|--------------|------------------------|----------------|--------------|------------------------|

| 0/11        |                     |                | Before       |                        |                | After        |                        |

| O/U,<br>R/W | Operation           | DSxPAG         | DS<br>EA<15> | Page<br>Description    | DSxPAG         | DS<br>EA<15> | Page<br>Description    |

| O,<br>Read  |                     | DSRPAG = 0x1FF | 1            | EDS: Last page         | DSRPAG = 0x1FF | 0            | See Note 1             |

| O,<br>Read  | [++Wn]              | DSRPAG = 0x2FF | 1            | PSV: Last lsw<br>page  | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page |

| O,<br>Read  | <b>Or</b><br>[Wn++] | DSRPAG = 0x3FF | 1            | PSV: Last MSB<br>page  | DSRPAG = 0x3FF | 0            | See Note 1             |

| O,<br>Write |                     | DSWPAG = 0x1FF | 1            | EDS: Last page         | DSWPAG = 0x1FF | 0            | See Note 1             |

| U,<br>Read  |                     | DSRPAG = 0x001 | 1            | PSV page               | DSRPAG = 0x001 | 0            | See Note 1             |

| U,<br>Read  | [Wn]<br>Or<br>[Wn]  | DSRPAG = 0x200 | 1            | PSV: First Isw<br>page | DSRPAG = 0x200 | 0            | See Note 1             |

| U,<br>Read  | [ //11 - ]          | DSRPAG = 0x300 | 1            | PSV: First MSB<br>page | DSRPAG = 0x2FF | 1            | PSV: Last Isw<br>page  |

# TABLE 4-61: OVERFLOW AND UNDERFLOW SCENARIOS AT PAGE 0, EDS and PSV SPACE BOUNDARIES<sup>(2,3,4)</sup>

Legend: O = Overflow, U = Underflow, R = Read, W = Write

Note 1: The Register Indirect Addressing now addresses a location in the base Data Space (0x0000-0x8000).

2: An EDS access with DSxPAG = 0x000 will generate an address error trap.

- **3:** Only reads from PS are supported using DSRPAG. An attempt to write to PS using DSWPAG will generate an address error trap.

- 4: Pseudo-Linear Addressing is not supported for large offsets.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0             | U-0   | U-0              | U-0   | U-0              | U-0              | U-0             | U-0   |

|-----------------|-------|------------------|-------|------------------|------------------|-----------------|-------|

| —               | —     | —                | —     | —                | —                | —               | —     |

| bit 15          |       |                  |       |                  | •                |                 | bit 8 |

|                 |       |                  |       |                  |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | STB<  | 23:16>           |                  |                 |       |

| bit 7           |       |                  |       |                  |                  |                 | bit 0 |

|                 |       |                  |       |                  |                  |                 |       |

| Legend:         |       |                  |       |                  |                  |                 |       |

| R = Readable    | bit   | W = Writable     | bit   | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

|                 |       |                  |       |                  |                  |                 |       |

## REGISTER 8-5: DMAXSTBH: DMA CHANNEL X START ADDRESS REGISTER B (HIGH)

bit 15-8 Unimplemented: Read as '0'

bit 7-0 STB<23:16>: Secondary Start Address bits (source or destination)

## REGISTER 8-6: DMAXSTBL: DMA CHANNEL X START ADDRESS REGISTER B (LOW)

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|

|                 |       |                  | STB   | <15:8>            |                 |                 |       |

| bit 15          |       |                  |       |                   |                 |                 | bit 8 |

|                 |       |                  |       |                   |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STE   | 3<7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                   |                 |                 | bit 0 |

| Legend:         |       |                  |       |                   |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is clea | ared            | x = Bit is unkı | nown  |

bit 15-0 **STB<15:0>:** Secondary Start Address bits (source or destination)

| U-0          | U-0                         | U-0                                          | U-0            | U-0              | U-0              | U-0             | U-0   |

|--------------|-----------------------------|----------------------------------------------|----------------|------------------|------------------|-----------------|-------|

| -            | —                           | —                                            | —              | —                | —                | —               | —     |

| bit 15       |                             |                                              |                |                  |                  |                 | bit 8 |

| U-0          | U-0                         | U-0                                          | U-0            | R-1              | R-1              | R-1             | R-1   |

| _            | _                           | _                                            | _              |                  | LSTC             | H<3:0>          |       |

| bit 7        |                             |                                              |                |                  |                  |                 | bit 0 |

| Legend:      |                             |                                              |                |                  |                  |                 |       |

| R = Readat   | ole bit                     | W = Writable                                 | bit            | U = Unimpler     | mented bit, read | 1 as '0'        |       |

| -n = Value a | at POR                      | '1' = Bit is set                             |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|              |                             |                                              |                |                  |                  |                 |       |

| bit 15-4     | Unimplemen                  | ted: Read as '                               | 0'             |                  |                  |                 |       |

| bit 3-0      | LSTCH<3:0>                  | : Last DMAC C                                | hannel Active  | e Status bits    |                  |                 |       |

|              | 1111 = No DI<br>1110 = Rese | MA transfer has<br>rved                      | s occurred sir | nce system Res   | set              |                 |       |

|              | •                           |                                              |                |                  |                  |                 |       |

|              | •                           |                                              |                |                  |                  |                 |       |

|              | •                           |                                              |                |                  |                  |                 |       |

|              |                             | rved<br>data transfer wa<br>data transfer wa |                |                  |                  |                 |       |

|              |                             | data transfer wa                             |                |                  |                  |                 |       |

## REGISTER 8-13: DMALCA: DMA LAST CHANNEL ACTIVE STATUS REGISTER

0001 = Last data transfer was handled by Channel 0 0000 = Last data transfer was handled by Channel 0

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment          | Peripheral Pir<br>Select Input<br>Register Value |     | Pin Assignment |

|--------------------------------------------------|------------------|-------------------------|--------------------------------------------------|-----|----------------|

| 000 0000                                         | I                | Vss                     | 010 1101                                         |     | RPI45          |

| 000 0001                                         | I                | C1OUT <sup>(1)</sup>    | 010 1110                                         | I   | RPI46          |

| 000 0010                                         | I                | C2OUT <sup>(1)</sup>    | 010 1111                                         | I   | RPI47          |

| 000 0011                                         | I                | C3OUT <sup>(1)</sup>    | 011 0000                                         | _   | _              |

| 000 0100                                         | I                | C4OUT <sup>(1)</sup>    | 011 0001                                         |     | _              |

| 000 0101                                         | —                | _                       | 011 0010                                         | _   | _              |

| 000 0110                                         | I                | PTGO30 <sup>(1)</sup>   | 011 0011                                         | I   | RPI51          |

| 000 0111                                         | I                | PTGO31 <sup>(1)</sup>   | 011 0100                                         | I   | RPI52          |

| 000 1000                                         | I                | FINDX1 <sup>(1,2)</sup> | 011 0101                                         | I   | RPI53          |

| 000 1001                                         | I                | FHOME1 <sup>(1,2)</sup> | 011 0110                                         | I/O | RP54           |

| 000 1010                                         | _                | _                       | 011 0111                                         | I/O | RP55           |

| 000 1011                                         | —                | _                       | 011 1000                                         | I/O | RP56           |

| 000 1100                                         | —                | —                       | 011 1001                                         | I/O | RP57           |

| 000 1101                                         | _                |                         | 011 1010                                         | I   | RPI58          |

| 000 1110                                         | —                | —                       | 011 1011                                         | _   | —              |

| 000 1111                                         | —                | —                       | 011 1100                                         | _   | —              |

| 001 0000                                         | —                | —                       | 011 1101                                         | —   | _              |

| 001 0001                                         | —                | —                       | 011 1110                                         | _   | —              |

| 001 0010                                         | —                | —                       | 011 1111                                         | —   | —              |

| 001 0011                                         | —                | —                       | 100 0000                                         | —   | _              |

| 001 0100                                         | I/O              | RP20                    | 100 0001                                         |     | —              |

| 001 0101                                         | —                | —                       | 100 0010                                         | —   | —              |

| 001 0110                                         | —                | —                       | 100 0011                                         | _   | —              |

| 001 0111                                         | —                | —                       | 100 0100                                         |     | —              |

| 001 1000                                         | I                | RPI24                   | 100 0101                                         | _   | —              |

| 001 1001                                         | I                | RPI25                   | 100 0110                                         | _   | —              |

| 001 1010                                         | —                | —                       | 100 0111                                         |     | —              |

| 001 1011                                         | I                | RPI27                   | 100 1000                                         | _   | _              |

| 001 1100                                         | I                | RPI28                   | 100 1001                                         | _   |                |

| 001 1101                                         | —                | _                       | 100 1010                                         | _   | _              |

| 001 1110                                         | —                |                         | 100 1011                                         | _   |                |

| 001 1111                                         | —                |                         | 100 1100                                         | —   | _              |

| 010 0000                                         | I                | RPI32                   | 100 1101                                         | —   | _              |

| 010 0001                                         | I                | RPI33                   | 100 1110                                         | _   | _              |

| 010 0010                                         | I                | RPI34                   | 100 1111                                         | _   |                |

| 010 0011                                         | I/O              | RP35                    | 101 0000                                         | _   | <u> </u>       |

| 010 0100                                         | I/O              | RP36                    | 101 0001                                         | —   | _              |

| 010 0101                                         | I/O              | RP37                    | 101 0010                                         | —   | _              |

| 010 0110                                         | I/O              | RP38                    | 101 0011                                         | —   | _              |

| 010 0111                                         | I/O              | RP39                    | 101 0100                                         | _   | _              |

## TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

# 12.0 TIMER1

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

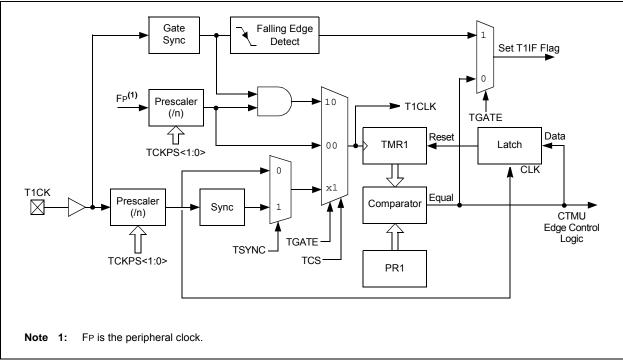

The Timer1 module is a 16-bit timer that can operate as a free-running interval timer/counter.

The Timer1 module has the following unique features over other timers:

- Can be operated in Asynchronous Counter mode from an external clock source

- The external clock input (T1CK) can optionally be synchronized to the internal device clock and the clock synchronization is performed after the prescaler

- A block diagram of Timer1 is shown in Figure 12-1.

The Timer1 module can operate in one of the following modes:

- Timer mode

- · Gated Timer mode

- Synchronous Counter mode

- · Asynchronous Counter mode

In Timer and Gated Timer modes, the input clock is derived from the internal instruction cycle clock (FCY). In Synchronous and Asynchronous Counter modes, the input clock is derived from the external clock input at the T1CK pin.

The Timer modes are determined by the following bits:

- Timer Clock Source Control bit (TCS): T1CON<1>

- Timer Synchronization Control bit (TSYNC): T1CON<2>

- Timer Gate Control bit (TGATE): T1CON<6>

Timer control bit setting for different operating modes are given in the Table 12-1.

| Mode                    | TCS | TGATE | TSYNC |

|-------------------------|-----|-------|-------|

| Timer                   | 0   | 0     | х     |

| Gated Timer             | 0   | 1     | x     |

| Synchronous<br>Counter  | 1   | х     | 1     |

| Asynchronous<br>Counter | 1   | x     | 0     |

### TABLE 12-1: TIMER MODE SETTINGS

## FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

## 14.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70352) in the "dsPIC33/dsPIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

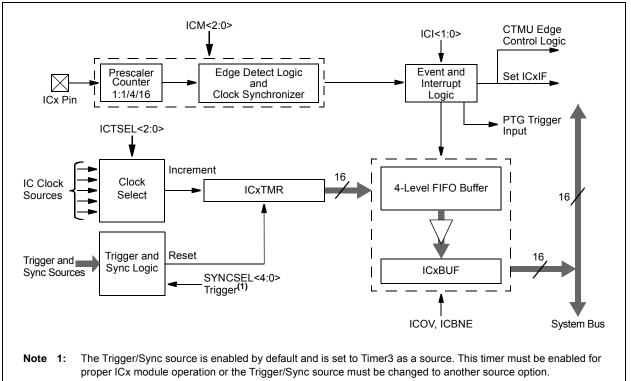

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices support four input capture channels.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 19 user-selectable Trigger/Sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to six clock sources available for each module, driving a separate internal 16-bit counter

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                         | U-0                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                            | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                               | R/W-0            | R/W-0             | R/W-0         |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------|-------------------|---------------|

| _                           | _                                                                                                                                                                                                          | _                                                                                                                                                                                                                                              | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BLANKSEL3                                                                                           | BLANKSEL2        | BLANKSEL1         | BLANKSEL      |

| bit 15                      | •                                                                                                                                                                                                          | •                                                                                                                                                                                                                                              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •                                                                                                   |                  | •                 | bit 8         |

| U-0                         | U-0                                                                                                                                                                                                        | R/W-0                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                               | R/W-0            | R/W-0             | R/W-0         |

|                             |                                                                                                                                                                                                            | CHOPSEL3                                                                                                                                                                                                                                       | CHOPSEL2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CHOPSEL1                                                                                            | CHOPSEL0         | CHOPHEN           | CHOPLEN       |

| bit 7                       |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  | onornen           | bit           |

|                             |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  |                   |               |

| Legend:                     |                                                                                                                                                                                                            |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  | (0)               |               |

| R = Readab                  |                                                                                                                                                                                                            | W = Writable                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -                                                                                                   | ented bit, read  |                   |               |

| -n = Value a                | at POR                                                                                                                                                                                                     | '1' = Bit is set                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | '0' = Bit is clea                                                                                   | red              | x = Bit is unkr   | nown          |

| bit 15-12                   | Unimplemen                                                                                                                                                                                                 | ted: Read as '                                                                                                                                                                                                                                 | D'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                     |                  |                   |               |

| bit 11-8                    | -                                                                                                                                                                                                          |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | urce Select bits                                                                                    |                  |                   |               |

|                             | The selected                                                                                                                                                                                               | state blank sig                                                                                                                                                                                                                                | nal will block t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | he current-limit                                                                                    | and/or Fault inp | out signals (if e | nabled via th |

|                             | BCH and BCI                                                                                                                                                                                                | L bits in the LEI                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     | ·                | 5 (               |               |

|                             | 1001 <b>= Rese</b>                                                                                                                                                                                         | rved                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  |                   |               |

|                             | •                                                                                                                                                                                                          |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                     |                  |                   |               |