#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 70 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

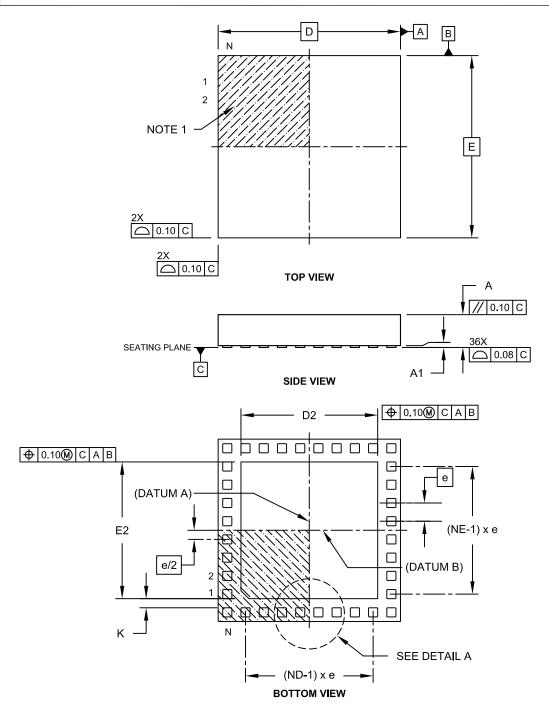

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc202t-i-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

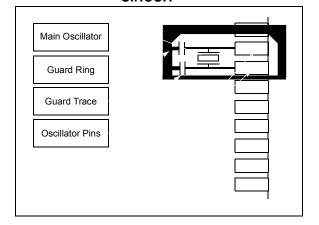

#### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| R/W-0               | U-0                          | R/W-0                                                    | R/W-0                   | R/W-0                       | R-0                       | R-0                | R-0                |

|---------------------|------------------------------|----------------------------------------------------------|-------------------------|-----------------------------|---------------------------|--------------------|--------------------|

| VAR                 | —                            | US1 <sup>(1)</sup>                                       | US0 <sup>(1)</sup>      | EDT <sup>(1,2)</sup>        | DL2 <sup>(1)</sup>        | DL1 <sup>(1)</sup> | DL0 <sup>(1)</sup> |

| bit 15              |                              |                                                          |                         |                             |                           |                    | bit                |

| R/W-0               | R/W-0                        | R/W-1                                                    | R/W-0                   | R/C-0                       | R-0                       | R/W-0              | R/W-0              |

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup>          | SATDW <sup>(1)</sup>                                     | ACCSAT <sup>(1)</sup>   | IPL3(3)                     | SFA                       | RND <sup>(1)</sup> | IF(1)              |

| bit 7               | I                            |                                                          |                         |                             | I                         | 1                  | bit                |

| Legend:             |                              | C = Clearable                                            | e bit                   |                             |                           |                    |                    |

| R = Readabl         | e bit                        | W = Writable                                             | bit                     | U = Unimpler                | mented bit, read          | d as '0'           |                    |

| -n = Value at       | POR                          | '1' = Bit is set                                         | t                       | '0' = Bit is cle            | ared                      | x = Bit is unkr    | nown               |

| bit 15              | 1 = Variable                 | le Exception Pro<br>exception proce                      | essing latency          | is enabled                  |                           |                    |                    |

| bit 14              |                              | nted: Read as '                                          |                         |                             |                           |                    |                    |

| bit 13-12           | -                            | SP Multiply Uns                                          |                         | Control bits <sup>(1)</sup> |                           |                    |                    |

|                     | 01 = DSP er<br>00 = DSP er   | ngine multiplies<br>ngine multiplies<br>ngine multiplies | are unsigned are signed |                             |                           |                    |                    |

| bit 11              | •                            | O Loop Terminatives executing Dot<br>t                   |                         |                             | iteration                 |                    |                    |

| bit 10-8            |                              | Loop Nesting<br>oops are active                          |                         | (1)                         |                           |                    |                    |

|                     | •                            |                                                          |                         |                             |                           |                    |                    |

|                     | •                            |                                                          |                         |                             |                           |                    |                    |

|                     | 001 = 1 DO k<br>000 = 0 DO k | oop is active<br>oops are active                         |                         |                             |                           |                    |                    |

| bit 7               | SATA: ACCA                   | A Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |

|                     |                              | ator A saturatio<br>ator A saturatio                     |                         |                             |                           |                    |                    |

| bit 6               | SATB: ACCE                   | B Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |

|                     |                              | ator B saturatio<br>ator B saturatio                     |                         |                             |                           |                    |                    |

| bit 5               | SATDW: Dat                   | ta Space Write                                           | from DSP Engi           | ne Saturation               | Enable bit <sup>(1)</sup> |                    |                    |

|                     |                              | ace write satura<br>ace write satura                     |                         | I                           |                           |                    |                    |

| bit 4               |                              | cumulator Satu                                           |                         | elect bit <sup>(1)</sup>    |                           |                    |                    |

|                     |                              | uration (super s<br>uration (normal                      | ,                       |                             |                           |                    |                    |

| bit 3               |                              | nterrupt Priority                                        |                         |                             |                           |                    |                    |

|                     |                              | errupt Priority Le<br>errupt Priority Le                 |                         |                             |                           |                    |                    |

|                     | nis bit is availabl          |                                                          | PXXXMC20X/              | 50X and dsPl                | C33EPXXXGP                | 50X devices on     | ly.                |

| 2: Th               | nis bit is always            | reau as 0.                                               |                         |                             |                           |                    |                    |

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER

**3:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

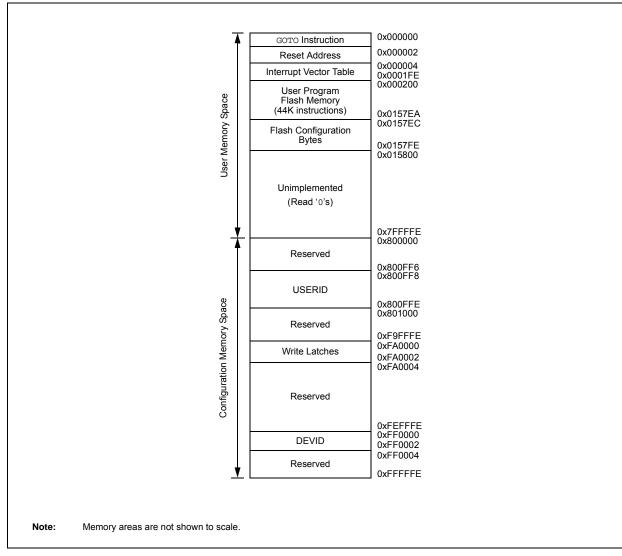

#### FIGURE 4-3: PROGRAM MEMORY MAP FOR dsPIC33EP128GP50X, dsPIC33EP128MC20X/50X AND PIC24EP128GP/MC20X DEVICES

| TABLE 4         | -16:  | QEI1   | REGR                                                                                                                              |        | P FOR d | SPIC33E | PXXXMO | 20X/50) | ( AND PI    | C24EP) |       | 20X DE | VICES O | NLY   | 1     |       |       | r             |

|-----------------|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------|--------|---------|---------|--------|---------|-------------|--------|-------|--------|---------|-------|-------|-------|-------|---------------|

| File Name       | Addr. | Bit 15 | Bit 14                                                                                                                            | Bit 13 | Bit 12  | Bit 11  | Bit 10 | Bit 9   | Bit 8       | Bit 7  | Bit 6 | Bit 5  | Bit 4   | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| QEI1CON         | 01C0  | QEIEN  |                                                                                                                                   |        |         |         |        |         |             |        |       |        |         | 0000  |       |       |       |               |

| QEI1IOC         | 01C2  | QCAPEN | EN FLTREN QFDIV<2:0> OUTFNC<1:0> SWPAB HOMPOL IDXPOL QEBPOL QEAPOL HOME INDEX QEB QEA 000x                                        |        |         |         |        |         |             |        |       |        |         |       |       |       |       |               |

| <b>QEI1STAT</b> | 01C4  | _      | - PCHEQIRQ PCHEQIEN PCLEQIRQ PCLEQIRQ POLEQIEN POSOVIRQ POSOVIEN PCIIRQ PCIIEN VELOVIRQ VELOVIEN HOMIRQ HOMIEN IDXIRQ IDXIEN 0000 |        |         |         |        |         |             |        |       |        | 0000    |       |       |       |       |               |

| POS1CNTL        | 01C6  |        |                                                                                                                                   |        |         |         |        |         | POSCNT<15   | :0>    |       |        |         |       |       |       |       | 0000          |

| POS1CNTH        | 01C8  |        |                                                                                                                                   |        |         |         |        | ł       | POSCNT<31:  | 16>    |       |        |         |       |       |       |       | 0000          |

| POS1HLD         | 01CA  |        |                                                                                                                                   |        |         |         |        |         | POSHLD<15   | 0>     |       |        |         |       |       |       |       | 0000          |

| VEL1CNT         | 01CC  |        |                                                                                                                                   |        |         |         |        |         | VELCNT<15   | 0>     |       |        |         |       |       |       |       | 0000          |

| INT1TMRL        | 01CE  |        |                                                                                                                                   |        |         |         |        |         | INTTMR<15:  | 0>     |       |        |         |       |       |       |       | 0000          |

| INT1TMRH        | 01D0  |        |                                                                                                                                   |        |         |         |        |         | INTTMR<31:  | 6>     |       |        |         |       |       |       |       | 0000          |

| INT1HLDL        | 01D2  |        |                                                                                                                                   |        |         |         |        |         | INTHLD<15:  | )>     |       |        |         |       |       |       |       | 0000          |

| INT1HLDH        | 01D4  |        |                                                                                                                                   |        |         |         |        |         | INTHLD<31:1 | 6>     |       |        |         |       |       |       |       | 0000          |

| INDX1CNTL       | 01D6  |        |                                                                                                                                   |        |         |         |        |         | INDXCNT<15  | :0>    |       |        |         |       |       |       |       | 0000          |

| INDX1CNTH       | 01D8  |        |                                                                                                                                   |        |         |         |        |         | NDXCNT<31:  | 16>    |       |        |         |       |       |       |       | 0000          |

| INDX1HLD        | 01DA  |        |                                                                                                                                   |        |         |         |        |         | INDXHLD<15  | :0>    |       |        |         |       |       |       |       | 0000          |

| QEI1GECL        | 01DC  |        |                                                                                                                                   |        |         |         |        |         | QEIGEC<15   | 0>     |       |        |         |       |       |       |       | 0000          |

| <b>QEI1ICL</b>  | 01DC  |        |                                                                                                                                   |        |         |         |        |         | QEIIC<15:0  | >      |       |        |         |       |       |       |       | 0000          |

| QEI1GECH        | 01DE  |        |                                                                                                                                   |        |         |         |        |         | QEIGEC<31:  | 16>    |       |        |         |       |       |       |       | 0000          |

| QEI1ICH         | 01DE  |        | QEIIC<31:16> 0000                                                                                                                 |        |         |         |        |         |             |        |       |        |         |       |       |       |       |               |

| QEI1LECL        | 01E0  |        | QEILEC<15:0> 0000                                                                                                                 |        |         |         |        |         |             |        |       |        |         |       |       |       |       |               |

| <b>QEI1LECH</b> | 01E2  |        |                                                                                                                                   |        |         |         |        |         | QEILEC<31:1 | 6>     |       |        |         |       |       |       |       | 0000          |

TABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-46: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|---------|---------|---------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      |        | TRISA12 | TRISA11 | TRISA10 | TRISA9 | TRISA8 | TRISA7 | _     |       | TRISA4 | _     |       | TRISA1 | TRISA0 | 1F93          |

| PORTA        | 0E02  | _      | _      | -      | RA12    | RA11    | RA10    | RA9    | RA8    | RA7    | _     |       | RA4    | _     | -     | RA1    | RA0    | 0000          |

| LATA         | 0E04  |        | _      | _      | LATA12  | LATA11  | LATA10  | LATA9  | LATA8  | LATA7  |       | _     | LATA4  |       | _     | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  |        | _      | _      | ODCA12  | ODCA11  | ODCA10  | ODCA9  | ODCA8  | ODCA7  |       | _     | ODCA4  |       | _     | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  |        | _      | _      | CNIEA12 | CNIEA11 | CNIEA10 | CNIEA9 | CNIEA8 | CNIEA7 |       | _     | CNIEA4 |       | _     | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  |        | _      | _      | CNPUA12 | CNPUA11 | CNPUA10 | CNPUA9 | CNPUA8 | CNPUA7 |       | _     | CNPUA4 |       | _     | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  |        | _      | _      | CNPDA12 | CNPDA11 | CNPDA10 | CNPDA9 | CNPDA8 | CNPDA7 |       | _     | CNPDA4 |       | _     | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | _      | _      | ANSA12  | ANSA11  |         | _      | -      | _      | _     | _     | ANSA4  | _     | _     | ANSA1  | ANSA0  | 1813          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-47: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | —       | _       | -       | _       | _      | ANSB8  | _      | _      | -      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-48: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|--------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISC        | 0E20  | TRISC15 | _      | TRISC13 | TRISC12 | TRISC11 | TRISC10 | TRISC9 | TRISC8 | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | BFFF          |

| PORTC        | 0E22  | RC15    | _      | RC13    | RC12    | RC11    | RC10    | RC9    | RC8    | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | xxxx          |

| LATC         | 0E24  | LATC15  | _      | LATC13  | LATC12  | LATC11  | LATC10  | LATC9  | LATC8  | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  | ODCC15  | -      | ODCC13  | ODCC12  | ODCC11  | ODCC10  | ODCC9  | ODCC8  | ODCC7  | ODCC6  | ODCC5  | ODCC4  | ODCC3  | ODCC2  | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | CNIEC15 | —      | CNIEC13 | CNIEC12 | CNIEC11 | CNIEC10 | CNIEC9 | CNIEC8 | CNIEC7 | CNIEC6 | CNIEC5 | CNIEC4 | CNIEC3 | CNIEC2 | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  | CNPUC15 | —      | CNPUC13 | CNPUC12 | CNPUC11 | CNPUC10 | CNPUC9 | CNPUC8 | CNPUC7 | CNPUC6 | CNPUC5 | CNPUC4 | CNPUC3 | CNPUC2 | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  | CNPDC15 | —      | CNPDC13 | CNPDC12 | CNPDC11 | CNPDC10 | CNPDC9 | CNPDC8 | CNPDC7 | CNPDC6 | CNPDC5 | CNPDC4 | CNPDC3 | CNPDC2 | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | _       | _      | _       | _       | ANSC11  | _       | _      | _      | _      | _      | _      | _      | _      | ANSC2  | ANSC1  | ANSC0  | 0807          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

In addition, DMA transfers can be triggered by timers as well as external interrupts. Each DMA channel is unidirectional. Two DMA channels must be allocated to read and write to a peripheral. If more than one channel receives a request to transfer data, a simple fixed priority scheme based on channel number, dictates which channel completes the transfer and which channel, or channels, are left pending. Each DMA channel moves a block of data, after which, it generates an interrupt to the CPU to indicate that the block is available for processing.

The DMA Controller provides these functional capabilities:

- Four DMA channels

- Register Indirect with Post-Increment Addressing mode

- Register Indirect without Post-Increment Addressing mode

- Peripheral Indirect Addressing mode (peripheral generates destination address)

- CPU interrupt after half or full block transfer complete

- Byte or word transfers

- · Fixed priority channel arbitration

- Manual (software) or automatic (peripheral DMA requests) transfer initiation

- One-Shot or Auto-Repeat Block Transfer modes

- Ping-Pong mode (automatic switch between two SRAM start addresses after each block transfer is complete)

- DMA request for each channel can be selected from any supported interrupt source

- Debug support features

The peripherals that can utilize DMA are listed in Table 8-1.

| Peripheral to DMA Association | DMAxREQ Register<br>IRQSEL<7:0> Bits | DMAxPAD Register<br>(Values to Read from<br>Peripheral) | DMAxPAD Register<br>(Values to Write to<br>Peripheral) |

|-------------------------------|--------------------------------------|---------------------------------------------------------|--------------------------------------------------------|

| INT0 – External Interrupt 0   | 00000000                             | _                                                       | _                                                      |

| IC1 – Input Capture 1         | 0000001                              | 0x0144 (IC1BUF)                                         | —                                                      |

| IC2 – Input Capture 2         | 00000101                             | 0x014C (IC2BUF)                                         | —                                                      |

| IC3 – Input Capture 3         | 00100101                             | 0x0154 (IC3BUF)                                         | —                                                      |

| IC4 – Input Capture 4         | 00100110                             | 0x015C (IC4BUF)                                         | —                                                      |

| OC1 – Output Compare 1        | 0000010                              | _                                                       | 0x0906 (OC1R)<br>0x0904 (OC1RS)                        |

| OC2 – Output Compare 2        | 00000110                             | _                                                       | 0x0910 (OC2R)<br>0x090E (OC2RS)                        |

| OC3 – Output Compare 3        | 00011001                             | _                                                       | 0x091A (OC3R)<br>0x0918 (OC3RS)                        |

| OC4 – Output Compare 4        | 00011010                             | _                                                       | 0x0924 (OC4R)<br>0x0922 (OC4RS)                        |

| TMR2 – Timer2                 | 00000111                             | —                                                       | _                                                      |

| TMR3 – Timer3                 | 00001000                             | —                                                       | _                                                      |

| TMR4 – Timer4                 | 00011011                             | —                                                       | _                                                      |

| TMR5 – Timer5                 | 00011100                             | —                                                       | —                                                      |

| SPI1 Transfer Done            | 00001010                             | 0x0248 (SPI1BUF)                                        | 0x0248 (SPI1BUF)                                       |

| SPI2 Transfer Done            | 00100001                             | 0x0268 (SPI2BUF)                                        | 0x0268 (SPI2BUF)                                       |

| UART1RX – UART1 Receiver      | 00001011                             | 0x0226 (U1RXREG)                                        | —                                                      |

| UART1TX – UART1 Transmitter   | 00001100                             | —                                                       | 0x0224 (U1TXREG)                                       |

| UART2RX – UART2 Receiver      | 00011110                             | 0x0236 (U2RXREG)                                        |                                                        |

| UART2TX – UART2 Transmitter   | 00011111                             | —                                                       | 0x0234 (U2TXREG)                                       |

| ECAN1 – RX Data Ready         | 00100010                             | 0x0440 (C1RXD)                                          | _                                                      |

| ECAN1 – TX Data Request       | 01000110                             | —                                                       | 0x0442 (C1TXD)                                         |

| ADC1 – ADC1 Convert Done      | 00001101                             | 0x0300 (ADC1BUF0)                                       | —                                                      |

#### TABLE 8-1: DMA CHANNEL TO PERIPHERAL ASSOCIATIONS

| R/W-0                 | R/W-0                                         | R/W-0                                                | R/W-0                                         | R/W-0                              | U-0              | U-0             | U-0     |

|-----------------------|-----------------------------------------------|------------------------------------------------------|-----------------------------------------------|------------------------------------|------------------|-----------------|---------|

| CHEN                  | SIZE                                          | DIR                                                  | HALF                                          | NULLW                              |                  |                 |         |

| bit 15                |                                               |                                                      |                                               |                                    |                  |                 | bit     |

| U-0                   | U-0                                           | R/W-0                                                | R/W-0                                         | U-0                                | U-0              | R/W-0           | R/W-0   |

|                       | 0-0                                           | AMODE1                                               | AMODE0                                        | 0-0                                | 0-0              | MODE1           | MODE0   |

| bit 7                 |                                               | AWODET                                               | 7 WIODE0                                      |                                    |                  | MODET           | bit     |

| Lovende               |                                               |                                                      |                                               |                                    |                  |                 |         |

| Legend:<br>R = Readab | lo hit                                        | M - Mritabla                                         | hit.                                          |                                    | monted bit rec   | ud aa '0'       |         |

|                       |                                               | W = Writable                                         |                                               | -                                  | mented bit, rea  |                 |         |

| -n = Value a          | IT POR                                        | '1' = Bit is set                                     |                                               | '0' = Bit is cle                   | ared             | x = Bit is unkr | nown    |

| bit 15                | CHEN: DMA                                     | Channel Enabl                                        | e bit                                         |                                    |                  |                 |         |

|                       | 1 = Channel<br>0 = Channel                    |                                                      |                                               |                                    |                  |                 |         |

| bit 14                |                                               | ata Transfer S                                       | ze hit                                        |                                    |                  |                 |         |

|                       | 1 = Byte                                      |                                                      |                                               |                                    |                  |                 |         |

|                       | 0 = Word                                      |                                                      |                                               |                                    |                  |                 |         |

| bit 13                | DIR: DMA Tra                                  | ansfer Directior                                     | n bit (source/d                               | estination bus                     | select)          |                 |         |

|                       |                                               | om RAM addre<br>om peripheral a                      |                                               | •                                  |                  |                 |         |

| bit 12                |                                               | Block Transfer                                       |                                               |                                    |                  |                 |         |

|                       | 1 = Initiates i                               | nterrupt when                                        | half of the data                              | a has been mo                      |                  |                 |         |

| bit 11                |                                               | Data Periphera                                       |                                               |                                    |                  |                 |         |

|                       |                                               | write to periph                                      |                                               |                                    | e (DIR bit must  | also be clear)  |         |

| bit 10-6              | Unimplemen                                    | ted: Read as '                                       | 0'                                            |                                    |                  |                 |         |

| bit 5-4               | AMODE<1:0                                     | -: DMA Chann                                         | el Addressing                                 | Mode Select b                      | oits             |                 |         |

|                       | 11 = Reserve<br>10 = Periphe<br>01 = Register |                                                      | ressing mode<br>ut Post-Increm                | nent mode                          |                  |                 |         |

| bit 3-2               | Unimplemen                                    | ted: Read as '                                       | 0'                                            |                                    |                  |                 |         |

| bit 1-0               | -                                             | DMA Channel                                          |                                               | de Select bits                     |                  |                 |         |

|                       | 11 = One-Sho<br>10 = Continue                 | ot, Ping-Pong r<br>ous, Ping-Pong<br>ot, Ping-Pong r | nodes are ena<br>modes are e<br>nodes are dis | abled (one bloc<br>nabled<br>abled | ck transfer fror | n/to each DMA t | ouffer) |

#### REGISTER 8-1: DMAXCON: DMA CHANNEL X CONTROL REGISTER

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                 | 12. 2007.00    |                                       |              |                   |                  |                 |        |

|-----------------|----------------|---------------------------------------|--------------|-------------------|------------------|-----------------|--------|

| U-0             | U-0            | U-0                                   | U-0          | U-0               | U-0              | U-0             | U-0    |

| —               | —              | —                                     | —            | —                 | —                | —               | —      |

| bit 15          |                |                                       |              |                   |                  |                 | bit 8  |

|                 |                |                                       |              |                   |                  |                 |        |

| U-0             | U-0            | U-0                                   | U-0          | R-0               | R-0              | R-0             | R-0    |

| —               |                | —                                     | —            | RQCOL3            | RQCOL2           | RQCOL1          | RQCOL0 |

| bit 7           |                |                                       |              |                   |                  |                 | bit 0  |

|                 |                |                                       |              |                   |                  |                 |        |

| Legend:         |                |                                       |              |                   |                  |                 |        |

| R = Readable    | bit            | W = Writable                          | bit          | U = Unimpler      | mented bit, read | l as '0'        |        |

| -n = Value at F | POR            | '1' = Bit is set                      |              | '0' = Bit is cle  | ared             | x = Bit is unkr | nown   |

|                 |                |                                       |              |                   |                  |                 |        |

| bit 15-4        | Unimplemen     | ted: Read as '                        | כ'           |                   |                  |                 |        |

| bit 3           | RQCOL3: DN     | /IA Channel 3 T                       | ransfer Requ | est Collision F   | ag bit           |                 |        |

|                 |                | e and interrupt<br>est collision is d |              | st collision is d | etected          |                 |        |

| <b>h</b> # 0    | •              |                                       |              | est Callisian Fl  | aa hit           |                 |        |

| bit 2           |                | /IA Channel 2 T<br>ce and interrupt   | •            |                   | 0                |                 |        |

|                 |                | e and interrupt<br>est collision is d |              |                   | elecieu          |                 |        |

| bit 1           | RQCOL1: DN     | /IA Channel 1 T                       | ransfer Requ | est Collision Fl  | ag bit           |                 |        |

|                 | 1 = User for   | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

|                 | 0 = No reque   | est collision is d                    | etected      |                   |                  |                 |        |

| bit 0           | RQCOLO: DN     | /IA Channel 0 T                       | ransfer Requ | est Collision F   | lag bit          |                 |        |

|                 | 1 = User force | e and interrupt                       | -based reque | st collision is d | etected          |                 |        |

#### REGISTER 8-12: DMARQC: DMA REQUEST COLLISION STATUS REGISTER

0 = No request collision is detected

NOTES:

#### REGISTER 11-7: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

|                   | R/W-0                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|-------------------|--------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------|----------------------------|-----------------|-----------------|-----------------|

| _                 |                                            |                                                                            |                                              | FLT2R<6:0>                 |                 |                 |                 |

| bit 15            |                                            |                                                                            |                                              |                            |                 |                 | bit 8           |

|                   | <b>D</b> 444 A                             | <b>D</b> 444 0                                                             | <b>D</b> 444 A                               | Date                       | <b>D</b> 444 0  | DAVA            | <b>D</b> # 44 0 |

| U-0               | R/W-0                                      | R/W-0                                                                      | R/W-0                                        | R/W-0                      | R/W-0           | R/W-0           | R/W-0           |

|                   |                                            |                                                                            |                                              | FLT1R<6:0>                 |                 |                 |                 |

| bit 7             |                                            |                                                                            |                                              |                            |                 |                 | bit C           |

| Legend:           |                                            |                                                                            |                                              |                            |                 |                 |                 |

| R = Readabl       | le bit                                     | W = Writable                                                               | bit                                          | U = Unimplen               | nented bit, rea | ad as '0'       |                 |

| -n = Value at     | t POR                                      | '1' = Bit is set                                                           |                                              | '0' = Bit is clea          | ared            | x = Bit is unkr | nown            |

| bit 14-8          | <b>FLT2R&lt;6:0&gt;</b><br>(see Table 11   | -2 for input pin                                                           | Fault 2 (FLT2)                               | ) to the Corresp<br>nbers) | onding RPn F    | Pin bits        |                 |

| bit 14-8          | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I                                                             | Fault 2 (FLT2)<br>selection nur<br>121       |                            | onding RPn F    | Pin bits        |                 |

| bit 14-8          | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I<br>I-2 for input pin<br>nput tied to RPI                    | Fault 2 (FLT2)<br>selection nur<br>121<br>P1 |                            | onding RPn F    | Pin bits        |                 |

| bit 14-8<br>bit 7 | FLT2R<6:0><br>(see Table 11<br>1111001 = h | : Assign PWM I<br>I-2 for input pin<br>nput tied to RPI<br>nput tied to CM | Fault 2 (FLT2<br>selection nur<br>121<br>P1  |                            | onding RPn F    | Pin bits        |                 |

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|--------------|------------------------------------------|------------------------------------------------------------------------------|---------------|-------------------|---------------|-----------------|--------|

| —            |                                          |                                                                              |               | SCK2INR<6:0       | >             |                 |        |

| bit 15       |                                          |                                                                              |               |                   |               |                 | bit 8  |

|              |                                          |                                                                              |               |                   | 5444.6        | <b>D</b> 444 A  | 5444.6 |

| U-0          | R/W-0                                    | R/W-0                                                                        | R/W-0         | R/W-0             | R/W-0         | R/W-0           | R/W-0  |

|              |                                          |                                                                              |               | SDI2R<6:0>        |               |                 |        |

| bit 7        |                                          |                                                                              |               |                   |               |                 | bit 0  |

|              |                                          |                                                                              |               |                   |               |                 |        |

| Legend:      |                                          |                                                                              |               |                   |               |                 |        |

| R = Readab   |                                          | W = Writable                                                                 |               | U = Unimplen      |               |                 |        |

| -n = Value a | t POR                                    | '1' = Bit is set                                                             |               | '0' = Bit is clea | ared          | x = Bit is unkr | nown   |

|              |                                          | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss                     | P1            |                   |               |                 |        |

| bit 7        | Unimpleme                                | nted: Read as 'o                                                             | כי            |                   |               |                 |        |

| bit 6-0      | (see Table 1 <sup>^</sup><br>1111001 = I | : Assign SPI2 D<br>1-2 for input pin<br>nput tied to RPI<br>nput tied to CMI | selection num | ,                 | esponding RPi | ר Pin bits      |        |

## REGISTER 11-12: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| U-0    | U-0      | U-0 | U-0   | U-0   | U-0   | U-0   | R/W-0 |

|--------|----------|-----|-------|-------|-------|-------|-------|

| —      | _        | -   | —     | —     | —     | —     | IC32  |

| bit 15 |          |     |       |       |       |       | bit 8 |

|        |          |     |       |       |       |       |       |

| R/W-0  | R/W/HS-0 | U-0 | R/W-0 | R/W-1 | R/W-1 | R/W-0 | R/W-1 |

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2

| Dit 7             |                      |                        |                    | DILU |

|-------------------|----------------------|------------------------|--------------------|------|

|                   |                      |                        |                    |      |

| Legend:           | HS = Hardware Settab | le bit                 |                    |      |

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, | read as '0'        |      |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared   | x = Bit is unknown |      |

SYNCSEL4<sup>(4)</sup> SYNCSEL3<sup>(4)</sup> SYNCSEL2<sup>(4)</sup> SYNCSEL1<sup>(4)</sup> SYNCSEL0<sup>(4)</sup>

hit A

| bit 15-9 | Unimplemented: Read as '0' |  |

|----------|----------------------------|--|

TRIGSTAT<sup>(3)</sup>

ICTRIG<sup>(2)</sup>

hit 7

| bit 10-0 | Ommplemented. Read as 0                      |

|----------|----------------------------------------------|

| bit 8    | IC32: Input Capture 32-Bit Timer Mode Select |

- IC32: Input Capture 32-Bit Timer Mode Select bit (Cascade mode)

- 1 = Odd IC and Even IC form a single 32-bit input capture module<sup>(1)</sup>

- 0 = Cascade module operation is disabled

#### bit 7 **ICTRIG:** Input Capture Trigger Operation Select bit<sup>(2)</sup>

- 1 = Input source used to trigger the input capture timer (Trigger mode)

- 0 = Input source used to synchronize the input capture timer to a timer of another module (Synchronization mode)

#### bit 6 **TRIGSTAT:** Timer Trigger Status bit<sup>(3)</sup>

- 1 = ICxTMR has been triggered and is running

- 0 = ICxTMR has not been triggered and is being held clear

#### bit 5 Unimplemented: Read as '0'

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- 6: Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1 PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

DS70000657H-page 216

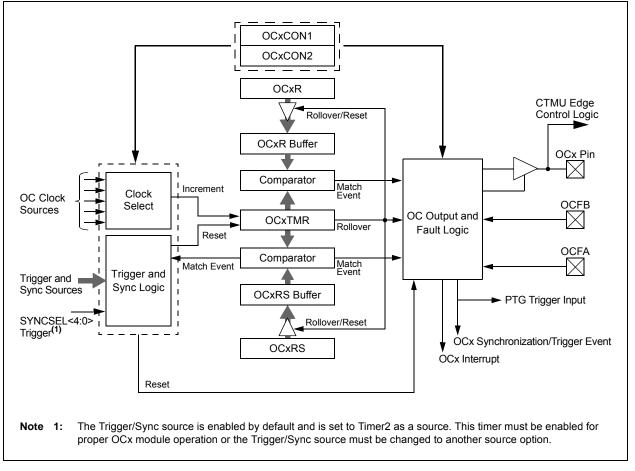

# 15.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The output compare module can select one of seven available clock sources for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The output compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events and trigger DMA data transfers.

Note: See "Output Compare" (DS70358) in the "dsPIC33/PIC24 Family Reference Manual" for OCxR and OCxRS register restrictions.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                | U-0   | U-0          | U-0                                     | R/W-0  | R/W-0                              | R/W-0  | R/W-0 |

|------------------------------------|-------|--------------|-----------------------------------------|--------|------------------------------------|--------|-------|

| —                                  | -     | —            | —                                       |        | LEB                                | <11:8> |       |

| bit 15                             |       |              |                                         |        |                                    |        | bit 8 |

|                                    |       |              |                                         |        |                                    |        |       |

| R/W-0                              | R/W-0 | R/W-0        | R/W-0                                   | R/W-0  | R/W-0                              | R/W-0  | R/W-0 |

|                                    |       |              | LEE                                     | 3<7:0> |                                    |        |       |

| bit 7                              |       |              |                                         |        |                                    |        | bit 0 |

|                                    |       |              |                                         |        |                                    |        |       |

| Legend:                            |       |              |                                         |        |                                    |        |       |

| R = Readable bit V                 |       | W = Writable | W = Writable bit                        |        | U = Unimplemented bit, read as '0' |        |       |

| -n = Value at POR '1' = Bit is set |       |              | '0' = Bit is cleared x = Bit is unknown |        |                                    | nown   |       |

## REGISTER 16-17: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER

bit 15-12 Unimplemented: Read as '0'

bit 11-0 LEB<11:0>: Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits

| R-0                                                     | R-0 | R-0                          | R-0                                                | R-0                                                              | R-0                                                         | R-0                                                                              |

|---------------------------------------------------------|-----|------------------------------|----------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------|

|                                                         |     | TERR                         | CNT<7:0>                                           |                                                                  |                                                             |                                                                                  |

|                                                         |     |                              |                                                    |                                                                  |                                                             | bit 8                                                                            |

|                                                         |     |                              |                                                    |                                                                  |                                                             |                                                                                  |

| R-0                                                     | R-0 | R-0                          | R-0                                                | R-0                                                              | R-0                                                         | R-0                                                                              |

|                                                         |     | RERR                         | CNT<7:0>                                           |                                                                  |                                                             |                                                                                  |

|                                                         |     |                              |                                                    |                                                                  |                                                             | bit 0                                                                            |

|                                                         |     |                              |                                                    |                                                                  |                                                             |                                                                                  |

|                                                         |     |                              |                                                    |                                                                  |                                                             |                                                                                  |

| R = Readable bit W = Writable bit                       |     | it                           | U = Unimpleme                                      | ented bit, rea                                                   | ad as '0'                                                   |                                                                                  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared |     |                              | x = Bit is unkr                                    | nown                                                             |                                                             |                                                                                  |

|                                                         | R-0 | R-0 R-0<br>it W = Writable b | TERR<br>R-0 R-0 R-0<br>RERR<br>it W = Writable bit | TERRCNT<7:0>     R-0   R-0   R-0     RERRCNT<7:0>   RERRCNT<7:0> | TERRCNT<7:0>     R-0   R-0   R-0     RERRCNT<7:0>   RERRCNT | TERRCNT<7:0>   R-0 R-0 R-0 R-0   RERRCNT<7:0> U = Unimplemented bit, read as '0' |

bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

#### REGISTER 21-9: CxCFG1: ECANx BAUD RATE CONFIGURATION REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SJW1  | SJW0  | BRP5  | BRP4  | BRP3  | BRP2  | BRP1  | BRP0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

| bit 7-6 | SJW<1:0>: Synchronization Jump Width bits    |

|---------|----------------------------------------------|

|         | 11 = Length is 4 x TQ                        |

|         | $10 = \text{Length is } 3 \times \text{Tq}$  |

|         | $01 = \text{Length is } 2 \times \text{T} Q$ |

|         | $00 = \text{Length is } 1 \times \text{Tq}$  |

```

bit 5-0 BRP<5:0>: Baud Rate Prescaler bits

```

```

11 1111 = TQ = 2 x 64 x 1/FCAN

```

•

- 00 0010 = TQ = 2 x 3 x 1/FCAN 00 0001 = TQ = 2 x 2 x 1/FCAN

- 00 0000 = Tq = 2 x 1 x 1/FCAN

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| R/W-0                                        | R/W-0                                                                                                                        | R/W-0                                                                                                                                            | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0 |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------|-------|--|

| F15MSK<1:0>                                  |                                                                                                                              | F14MS                                                                                                                                            | F14MSK<1:0>                                                                                                                                          |                                                                                                                           | SK<1:0>                                                                 | F12MSK<1:0>                  |       |  |

| bit 15                                       |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit 8 |  |

| R/W-0                                        | R/W-0                                                                                                                        | R/W-0                                                                                                                                            | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0 |  |

|                                              | F11MSK<1:0>                                                                                                                  |                                                                                                                                                  | F10MSK<1:0>                                                                                                                                          |                                                                                                                           | F9MSK<1:0>                                                              |                              | <1:0> |  |

| bit 7                                        |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit C |  |

|                                              |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |       |  |

| Legend:                                      |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |       |  |

| R = Readabl                                  | le bit                                                                                                                       | W = Writable bit                                                                                                                                 |                                                                                                                                                      | U = Unimplem                                                                                                              | l as '0'                                                                |                              |       |  |

| -n = Value at                                | t POR                                                                                                                        | '1' = Bit is set                                                                                                                                 |                                                                                                                                                      | '0' = Bit is clea                                                                                                         | ared                                                                    | x = Bit is unknown           |       |  |

|                                              |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |       |  |

|                                              |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |       |  |

| bit 15-14                                    |                                                                                                                              | 0>: Mask Sourc                                                                                                                                   | e for Filter 15                                                                                                                                      | bits                                                                                                                      |                                                                         |                              |       |  |

| bit 15-14                                    | 11 = Reserv                                                                                                                  | ed                                                                                                                                               |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |       |  |

| bit 15-14                                    | 11 = Reserv<br>10 = Accepta                                                                                                  | ed<br>ance Mask 2 reg                                                                                                                            | gisters contair                                                                                                                                      | n mask                                                                                                                    |                                                                         |                              |       |  |

| bit 15-14                                    | 11 = Reserv<br>10 = Accept<br>01 = Accept                                                                                    | ed                                                                                                                                               | gisters contair<br>gisters contair                                                                                                                   | n mask<br>n mask                                                                                                          |                                                                         |                              |       |  |