Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 25                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

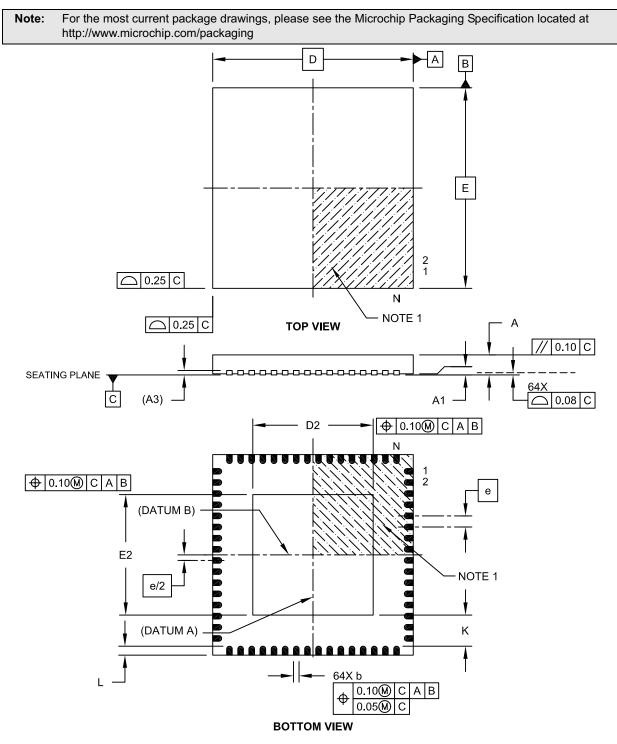

| Package / Case             | 36-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 36-VTLA (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc203-e-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

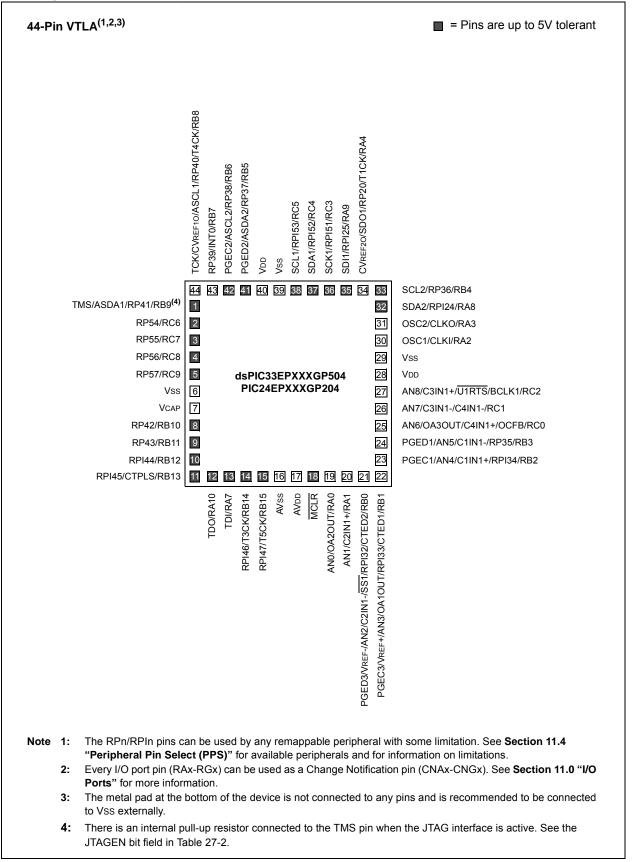

#### **Pin Diagrams (Continued)**

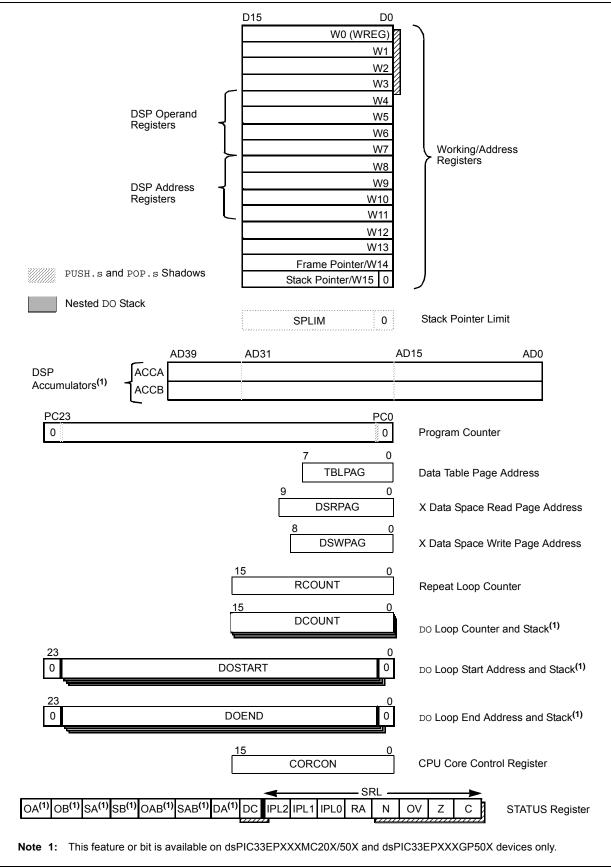

## 4.4 Special Function Register Maps

## TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND dsPIC33EPXXXGP50X DEVICES ONLY

|           |       | 0.00   |              |        |              |            |        |       | 20/0/00/    |        |       |        |         |          |          | -     | r     |               |

|-----------|-------|--------|--------------|--------|--------------|------------|--------|-------|-------------|--------|-------|--------|---------|----------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14       | Bit 13 | Bit 12       | Bit 11     | Bit 10 | Bit 9 | Bit 8       | Bit 7  | Bit 6 | Bit 5  | Bit 4   | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| W0        | 0000  |        |              |        |              |            |        |       | W0 (WR      | EG)    |       |        |         |          |          |       |       | xxxx          |

| W1        | 0002  |        |              |        |              |            |        |       | W1          |        |       |        |         |          |          |       |       | xxxx          |

| W2        | 0004  |        |              |        |              |            |        |       | W2          |        |       |        |         |          |          |       |       | xxxx          |

| W3        | 0006  |        |              |        |              |            |        |       | W3          |        |       |        |         |          |          |       |       | xxxx          |

| W4        | 8000  |        |              |        |              |            |        |       | W4          |        |       |        |         |          |          |       |       | xxxx          |

| W5        | 000A  |        |              |        |              |            |        |       | W5          |        |       |        |         |          |          |       |       | xxxx          |

| W6        | 000C  |        | W6           |        |              |            |        |       |             |        |       |        | xxxx    |          |          |       |       |               |

| W7        | 000E  |        | W7           |        |              |            |        |       |             |        |       |        | xxxx    |          |          |       |       |               |

| W8        | 0010  |        | W8           |        |              |            |        |       |             |        |       |        | xxxx    |          |          |       |       |               |

| W9        | 0012  |        |              |        |              |            |        |       | W9          |        |       |        |         |          |          |       |       | xxxx          |

| W10       | 0014  |        |              |        |              |            |        |       | W10         |        |       |        |         |          |          |       |       | xxxx          |

| W11       | 0016  |        |              |        |              |            |        |       | W11         |        |       |        |         |          |          |       |       | xxxx          |

| W12       | 0018  |        |              |        |              |            |        |       | W12         |        |       |        |         |          |          |       |       | xxxx          |

| W13       | 001A  |        |              |        |              |            |        |       | W13         |        |       |        |         |          |          |       |       | xxxx          |

| W14       | 001C  |        |              |        |              |            |        |       | W14         |        |       |        |         |          |          |       |       | xxxx          |

| W15       | 001E  |        |              |        |              |            |        |       | W15         |        |       |        |         |          |          |       |       | xxxx          |

| SPLIM     | 0020  |        |              |        |              |            |        |       | SPLI        | N      |       |        |         |          |          |       |       | 0000          |

| ACCAL     | 0022  |        |              |        |              |            |        |       | ACCA        | L      |       |        |         |          |          |       |       | 0000          |

| ACCAH     | 0024  |        |              |        |              |            |        |       | ACCA        | H      |       |        |         |          |          |       |       | 0000          |

| ACCAU     | 0026  |        |              | Si     | gn Extensior | n of ACCA< | 39>    |       |             |        |       |        | ACO     | CAU      |          |       |       | 0000          |

| ACCBL     | 0028  |        |              |        |              |            |        |       | ACCB        | L      |       |        |         |          |          |       |       | 0000          |

| ACCBH     | 002A  |        |              |        |              |            |        |       | ACCB        | Н      |       |        |         |          |          |       |       | 0000          |

| ACCBU     | 002C  |        |              | Si     | gn Extensior | n of ACCB< | 39>    |       |             |        |       |        | ACO     | CBU      |          |       |       | 0000          |

| PCL       | 002E  |        |              |        |              |            |        | F     | PCL<15:0>   |        |       |        |         |          |          |       |       | 0000          |

| PCH       | 0030  | _      | _            | _      | —            | _          | _      | —     | _           | _      |       |        |         | PCH<6:0> |          |       |       | 0000          |

| DSRPAG    | 0032  | _      | _            | _      | —            | _          | _      |       |             |        |       | DSRPAC | 6<9:0>  |          |          |       |       | 0001          |

| DSWPAG    | 0034  | _      |              | _      | —            |            | _      | _     |             |        |       | DS     | WPAG<8: | 0>       |          |       |       | 0001          |

| RCOUNT    | 0036  |        | RCOUNT<15:0> |        |              |            |        |       |             |        |       |        | 0000    |          |          |       |       |               |

| DCOUNT    | 0038  |        |              |        |              |            |        |       | DCOUNT<     | :15:0> |       |        |         |          |          |       |       | 0000          |

| DOSTARTL  | 003A  |        |              |        |              |            |        | DOS   | STARTL<15:1 | >      |       |        |         |          |          |       |       | 0000          |

| DOSTARTH  | 003C  | _      | —            | —      | _            | —          | —      | _     | _           | _      | —     |        |         | DOSTAF   | RTH<5:0> |       |       | 0000          |

| DOENDL    | 003E  |        |              |        |              |            |        | DO    | ENDL<15:1>  | >      |       |        |         |          |          |       |       | 0000          |

| DOENDH    | 0040  | _      | —            | —      | —            | —          | —      | _     | —           | —      | —     |        |         | DOEND    | )H<5:0>  |       |       | 0000          |

|           |       |        |              |        |              |            |        |       |             |        |       |        |         |          |          |       |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| IABLE 4-2  | ABLE 4-21: ECAN1 REGISTER MAP WHEN WIN (C1CTRE1<0>) = 0 OR 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY |         |           |         |         |         |            |           |        |          |           |        |         |           |          |          |        |               |

|------------|----------------------------------------------------------------------------------------------------|---------|-----------|---------|---------|---------|------------|-----------|--------|----------|-----------|--------|---------|-----------|----------|----------|--------|---------------|

| File Name  | Addr.                                                                                              | Bit 15  | Bit 14    | Bit 13  | Bit 12  | Bit 11  | Bit 10     | Bit 9     | Bit 8  | Bit 7    | Bit 6     | Bit 5  | Bit 4   | Bit 3     | Bit 2    | Bit 1    | Bit 0  | All<br>Resets |

| C1CTRL1    | 0400                                                                                               | _       | —         | CSIDL   | ABAT    | CANCKS  | R          | EQOP<2:0  | >      | OPM      | /IODE<2:0 | >      | —       | CANCAP    | —        | —        | WIN    | 0480          |

| C1CTRL2    | 0402                                                                                               | _       | _         | —       | _       | _       | _          | —         | _      | —        | _         | _      |         | D         | NCNT<4:0 | >        |        | 0000          |

| C1VEC      | 0404                                                                                               | _       | —         | —       |         | F       | ILHIT<4:0> |           |        | —        |           |        | •       | ICODE<6:0 | >        |          |        | 0040          |

| C1FCTRL    | 0406                                                                                               | C       | DMABS<2:0 | >       |         | _       | —          | —         | —      | _        | _         | _      |         |           | FSA<4:0> |          |        | 0000          |

| C1FIFO     | 0408                                                                                               |         | —         |         |         | FBP<    | 5:0>       |           |        | _        | _         |        |         | FNRB      | <5:0>    |          |        | 0000          |

| C1INTF     | 040A                                                                                               |         | —         | TXBO    | TXBP    | RXBP    | TXWAR      | RXWAR     | EWARN  | IVRIF    | WAKIF     | ERRIF  | _       | FIFOIF    | RBOVIF   | RBIF     | TBIF   | 0000          |

| C1INTE     | 040C                                                                                               |         | —         | —       |         | _       | —          | —         | —      | IVRIE    | WAKIE     | ERRIE  | _       | FIFOIE    | RBOVIE   | RBIE     | TBIE   | 0000          |

| C1EC       | 040E                                                                                               |         |           |         | TERRCN  | T<7:0>  |            |           |        |          |           |        | RERRCN  | NT<7:0>   |          |          |        | 0000          |

| C1CFG1     | 0410                                                                                               | _       | _         | _       | _       | _       | _          | _         | _      | SJW<1    | :0>       |        |         | BRP       | <5:0>    |          |        | 0000          |

| C1CFG2     | 0412                                                                                               | _       | WAKFIL    | _       | _       | _       | SI         | =G2PH<2:( | )>     | SEG2PHTS | SAM       | S      | EG1PH<2 | :0>       | P        | RSEG<2:0 | >      | 0000          |

| C1FEN1     | 0414                                                                                               | FLTEN15 | FLTEN14   | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10    | FLTEN9    | FLTEN8 | FLTEN7   | FLTEN6    | FLTEN5 | FLTEN4  | FLTEN3    | FLTEN2   | FLTEN1   | FLTEN0 | FFFF          |

| C1FMSKSEL1 | 0418                                                                                               | F7MSł   | <<1:0>    | F6MSł   | <<1:0>  | F5MS    | K<1:0>     | F4MS      | K<1:0> | F3MSK<   | <1:0>     | F2MS   | K<1:0>  | F1MSH     | <<1:0>   | F0MS     | <<1:0> | 0000          |

| C1FMSKSEL2 | 041A                                                                                               | F15MS   | K<1:0>    | F14MS   | K<1:0>  | F13MS   | K<1:0>     | F12MS     | K<1:0> | F11MSK   | <1:0>     | F10MS  | K<1:0>  | F9MSk     | <<1:0>   | F8MSI    | <<1:0> | 0000          |

#### TABLE 4-21: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 OR 1 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-22: ECAN1 REGISTER MAP WHEN WIN (C1CTRL1<0>) = 0 FOR dsPIC33EPXXXMC/GP50X DEVICES ONLY

| File Name | Addr          | Bit 15  | Bit 14                        | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9   | Bit 8         | Bit 7        | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|---------------|---------|-------------------------------|---------|---------|---------|---------|---------|---------------|--------------|---------|---------|---------|---------|---------|---------|---------|---------------|

|           | 0400-<br>041E |         |                               |         |         |         |         | S       | ee definition | when WIN     | = x     |         |         |         |         |         |         |               |

| C1RXFUL1  | 0420          | RXFUL15 | RXFUL14                       | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9  | RXFUL8        | RXFUL7       | RXFUL6  | RXFUL5  | RXFUL4  | RXFUL3  | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C1RXFUL2  | 0422          | RXFUL31 | RXFUL30                       | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24       | RXFUL23      | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C1RXOVF1  | 0428          | RXOVF15 | RXOVF14                       | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9  | RXOVF8        | RXOVF7       | RXOVF6  | RXOVF5  | RXOVF4  | RXOVF3  | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C1RXOVF2  | 042A          | RXOVF31 | RXOVF30                       | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24       | RXOVF23      | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 | 0000          |

| C1TR01CON | 0430          | TXEN1   | TXABT1                        | TXLARB1 | TXERR1  | TXREQ1  | RTREN1  | TX1PF   | RI<1:0>       | TXEN0        | TXABAT0 | TXLARB0 | TXERR0  | TXREQ0  | RTREN0  | TX0PF   | RI<1:0> | 0000          |

| C1TR23CON | 0432          | TXEN3   | TXABT3                        | TXLARB3 | TXERR3  | TXREQ3  | RTREN3  | TX3PF   | RI<1:0>       | TXEN2        | TXABAT2 | TXLARB2 | TXERR2  | TXREQ2  | RTREN2  | TX2PF   | RI<1:0> | 0000          |

| C1TR45CON | 0434          | TXEN5   | TXABT5                        | TXLARB5 | TXERR5  | TXREQ5  | RTREN5  | TX5PF   | RI<1:0>       | TXEN4        | TXABAT4 | TXLARB4 | TXERR4  | TXREQ4  | RTREN4  | TX4PF   | RI<1:0> | 0000          |

| C1TR67CON | 0436          | TXEN7   | TXABT7                        | TXLARB7 | TXERR7  | TXREQ7  | RTREN7  | TX7PF   | RI<1:0>       | TXEN6        | TXABAT6 | TXLARB6 | TXERR6  | TXREQ6  | RTREN6  | TX6PF   | RI<1:0> | xxxx          |

| C1RXD     | 0440          |         |                               |         |         |         |         | E       | CAN1 Rece     | eive Data Wo | ord     |         |         |         |         |         |         | xxxx          |

| C1TXD     | 0442          |         | ECAN1 Transmit Data Word xxxx |         |         |         |         |         |               |              |         | xxxx    |         |         |         |         |         |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 11.0 I/O PORTS

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "I/O Ports" (DS70598) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Many of the device pins are shared among the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

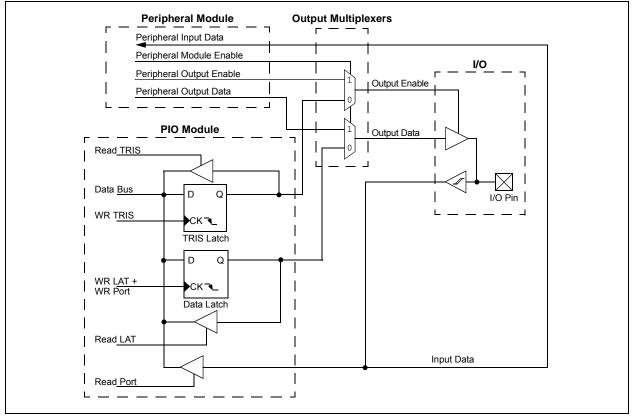

# 11.1 Parallel I/O (PIO) Ports

Generally, a parallel I/O port that shares a pin with a peripheral is subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through," in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin can be read, but the output driver for the parallel port bit is disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin can be driven by a port.

All port pins have eight registers directly associated with their operation as digital I/O. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the Latch register (LATx) read the latch. Writes to the Latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

Any bit and its associated data and control registers that are not valid for a particular device is disabled. This means the corresponding LATx and TRISx registers and the port pin are read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs.

## 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital-only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $I^2C^{TM}$  and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0      | R/W-0                                                                    | R/W-0                                                | R/W-0                           | U-0               | U-0              | U-0                    | R/W-0        |

|------------|--------------------------------------------------------------------------|------------------------------------------------------|---------------------------------|-------------------|------------------|------------------------|--------------|

| FLTMD      | FLTOUT                                                                   | FLTTRIEN                                             | OCINV                           | —                 | _                | —                      | OC32         |

| bit 15     | ·                                                                        |                                                      |                                 |                   | ·                |                        | bit          |

|            |                                                                          |                                                      |                                 |                   |                  |                        |              |

| R/W-0      | R/W-0, HS                                                                | R/W-0                                                | R/W-0                           | R/W-1             | R/W-1            | R/W-0                  | R/W-0        |

| OCTRIC     | G TRIGSTAT                                                               | OCTRIS                                               | SYNCSEL4                        | SYNCSEL3          | SYNCSEL2         | SYNCSEL1               | SYNCSEL      |

| bit 7      |                                                                          |                                                      |                                 |                   |                  |                        | bit          |

| Legend:    |                                                                          | HS = Hardwa                                          | re Settable bit                 |                   |                  |                        |              |

| R = Reada  | able bit                                                                 | W = Writable                                         | bit                             | U = Unimplem      | nented bit, read | l as '0'               |              |

| -n = Value | at POR                                                                   | '1' = Bit is set                                     |                                 | '0' = Bit is clea | ared             | x = Bit is unkn        | iown         |

|            |                                                                          |                                                      |                                 |                   |                  |                        |              |

| bit 15     | 1 = Fault mo<br>cleared i                                                | t Mode Select b<br>ode is maintain<br>n software and | ed until the Fa<br>a new PWM pe | eriod starts      |                  |                        |              |

|            |                                                                          | de is maintaine                                      | d until the Faul                | t source is rem   | loved and a ne   | w PWM period           | starts       |

| bit 14     | FLTOUT: Fau                                                              |                                                      | . –                             |                   |                  |                        |              |

|            |                                                                          | tput is driven hi<br>tput is driven lo               |                                 |                   |                  |                        |              |

| bit 13     |                                                                          | ault Output Sta                                      |                                 |                   |                  |                        |              |

|            |                                                                          | is tri-stated on                                     |                                 | 'n                |                  |                        |              |

|            | •                                                                        | I/O state is defi                                    |                                 |                   | ault condition   |                        |              |

| bit 12     | OCINV: Outp                                                              | ut Compare x I                                       | nvert bit                       |                   |                  |                        |              |

|            |                                                                          | out is inverted<br>out is not invert                 | ed                              |                   |                  |                        |              |

| bit 11-9   | Unimplemen                                                               | ted: Read as '                                       | כי                              |                   |                  |                        |              |

| bit 8      | OC32: Casca                                                              | ide Two OCx M                                        | odules Enable                   | bit (32-bit oper  | ration)          |                        |              |

|            |                                                                          | module operate module operate                        |                                 |                   |                  |                        |              |

| bit 7      |                                                                          | tput Compare x                                       |                                 | Select bit        |                  |                        |              |

|            |                                                                          | OCx from the s                                       |                                 |                   | CSELx bits       |                        |              |

|            |                                                                          | nizes OCx with                                       |                                 |                   |                  | S                      |              |

| bit 6      | TRIGSTAT: T                                                              | imer Trigger St                                      | atus bit                        |                   |                  |                        |              |

|            |                                                                          | urce has been <sup>.</sup><br>urce has not be        |                                 |                   | d clear          |                        |              |

| bit 5      |                                                                          | put Compare x                                        |                                 | •                 |                  |                        |              |

|            | 1 = OCx is tr                                                            | • •                                                  | ·                               |                   |                  |                        |              |

|            | 0 = Output C                                                             | ompare x mod                                         | ule drives the C                | OCx pin           |                  |                        |              |

| Note 1:    | Do not use the O                                                         | Cx module as i                                       | ts own Svnchro                  | nization or Tric  | aaer source.     |                        |              |

|            | When the OCy m                                                           |                                                      | -                               |                   |                  | module uses t          | he OCv       |

|            | module as a Trigg                                                        |                                                      |                                 |                   |                  |                        |              |

| 3:         | Each Output Con<br><b>"Peripheral Trig</b><br>PTGO0 = OC1<br>PTGO1 = OC2 |                                                      |                                 |                   |                  | n source. See <b>S</b> | Section 24.0 |

|            | PTGO2 = OC3 $PTGO3 = OC4$                                                |                                                      |                                 |                   |                  |                        |              |

### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

|                                                                                                          | lled low externally in order to clear and disable the fault<br>egister requires unlock sequence                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0x0000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |

| -                                                                                                        | d polarity using the IOCON1 register<br>gister requires unlock sequence                                                                                                                                                                                                                           |

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0xF000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |

| R/W-0         | R/W-0                                  | R/W-0                                 | R/W-0            | R/W-0              | R/W-0           | R/W-0           | R/W-0    |  |  |  |  |  |

|---------------|----------------------------------------|---------------------------------------|------------------|--------------------|-----------------|-----------------|----------|--|--|--|--|--|

| EDG1MOD       | EDG1POL                                | EDG1SEL3                              | EDG1SEL2         | EDG1SEL1           | EDG1SEL0        | EDG2STAT        | EDG1STAT |  |  |  |  |  |

| bit 15        |                                        | 1                                     |                  | 11                 |                 |                 | bit 8    |  |  |  |  |  |

|               |                                        |                                       |                  |                    |                 |                 |          |  |  |  |  |  |

| R/W-0         | R/W-0                                  | R/W-0                                 | R/W-0            | R/W-0              | R/W-0           | U-0             | U-0      |  |  |  |  |  |

| EDG2MOD       | EDG2POL                                | EDG2SEL3                              | EDG2SEL2         | EDG2SEL1           | EDG2SEL0        | —               | _        |  |  |  |  |  |

| bit 7         |                                        |                                       |                  | 1 1                |                 | 1               | bit (    |  |  |  |  |  |

|               |                                        |                                       |                  |                    |                 |                 |          |  |  |  |  |  |

| Legend:       |                                        |                                       |                  |                    |                 |                 |          |  |  |  |  |  |

| R = Readabl   | le bit                                 | W = Writable                          | oit              | U = Unimplem       | ented bit, read | l as '0'        |          |  |  |  |  |  |

| -n = Value at | POR                                    | '1' = Bit is set                      |                  | '0' = Bit is clea  | red             | x = Bit is unkr | nown     |  |  |  |  |  |

|               |                                        |                                       |                  |                    |                 |                 |          |  |  |  |  |  |

| bit 15        | EDG1MOD: E                             | Edge 1 Edge Sa                        | ampling Mode     | Selection bit      |                 |                 |          |  |  |  |  |  |

|               | 1 = Edge 1 is                          | s edge-sensitive                      | 9                |                    |                 |                 |          |  |  |  |  |  |

|               | •                                      | s level-sensitive                     |                  |                    |                 |                 |          |  |  |  |  |  |

| bit 14        |                                        | dge 1 Polarity                        |                  |                    |                 |                 |          |  |  |  |  |  |

|               |                                        | s programmed f                        |                  |                    |                 |                 |          |  |  |  |  |  |

| L:1 40 40     | •                                      | s programmed f                        | •                | •                  |                 |                 |          |  |  |  |  |  |

| bit 13-10     |                                        | :0>: Edge 1 So                        | urce Select bits | 5                  |                 |                 |          |  |  |  |  |  |

|               | 1xxx = Reserved<br>01xx = Reserved     |                                       |                  |                    |                 |                 |          |  |  |  |  |  |

|               | 0011 = CTED1 pin                       |                                       |                  |                    |                 |                 |          |  |  |  |  |  |

|               | 0010 = CTED2 pin                       |                                       |                  |                    |                 |                 |          |  |  |  |  |  |

|               | 0001 = OC1                             |                                       |                  |                    |                 |                 |          |  |  |  |  |  |

| hit O         | 0000 = Timer                           |                                       | :+               |                    |                 |                 |          |  |  |  |  |  |

| bit 9         |                                        | Edge 2 Status b                       |                  | vritten to control | the odge cou    | reo             |          |  |  |  |  |  |

|               | 1 = Edge 2 h                           |                                       |                  |                    | the edge sou    | ice.            |          |  |  |  |  |  |

|               |                                        | as not occurred                       | ł                |                    |                 |                 |          |  |  |  |  |  |

| bit 8         | EDG1STAT: E                            | Edge 1 Status b                       | it               |                    |                 |                 |          |  |  |  |  |  |

|               |                                        |                                       | 1 and can be v   | vritten to control | the edge sou    | rce.            |          |  |  |  |  |  |

|               | 1 = Edge 1 h                           |                                       |                  |                    |                 |                 |          |  |  |  |  |  |

|               | -                                      | as not occurred                       |                  |                    |                 |                 |          |  |  |  |  |  |

| bit 7         |                                        | Edge 2 Edge Sa                        |                  | Selection bit      |                 |                 |          |  |  |  |  |  |

|               |                                        | s edge-sensitive<br>s level-sensitive |                  |                    |                 |                 |          |  |  |  |  |  |

| bit 6         | •                                      | dge 2 Polarity                        |                  |                    |                 |                 |          |  |  |  |  |  |

| Sit 0         |                                        | s programmed f                        |                  | dae response       |                 |                 |          |  |  |  |  |  |

|               |                                        | s programmed f                        |                  |                    |                 |                 |          |  |  |  |  |  |

| bit 5-2       | EDG2SEL<3                              | :0>: Edge 2 So                        | urce Select bits | 3                  |                 |                 |          |  |  |  |  |  |

|               | 1111 <b>= Rese</b>                     | rved                                  |                  |                    |                 |                 |          |  |  |  |  |  |

|               | 01xx = Rese                            |                                       |                  |                    |                 |                 |          |  |  |  |  |  |

|               | 0100 = CMP <sup>2</sup><br>0011 = CTEE |                                       |                  |                    |                 |                 |          |  |  |  |  |  |

|               | 0010 = CTEE                            |                                       |                  |                    |                 |                 |          |  |  |  |  |  |

|               |                                        | Ji pili                               |                  |                    |                 |                 |          |  |  |  |  |  |

|               | 0001 = OC1                             | module                                |                  |                    |                 |                 |          |  |  |  |  |  |

|               |                                        | module                                |                  |                    |                 |                 |          |  |  |  |  |  |

#### REGISTER 22-2: CTMUCON2: CTMU CONTROL REGISTER 2

# 23.4 ADC Control Registers

#### REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1

| R/W-0         | U-0                                | R/W-0                               | R/W-0               | U-0               | R/W-0            | R/W-0                               | R/W-0               |  |  |  |

|---------------|------------------------------------|-------------------------------------|---------------------|-------------------|------------------|-------------------------------------|---------------------|--|--|--|

| ADON          | —                                  | ADSIDL                              | ADDMABM             |                   | AD12B            | FORM1                               | FORM0               |  |  |  |

| bit 15        | •                                  |                                     |                     |                   |                  |                                     | bit 8               |  |  |  |

| R/W-0         | R/W-0                              | R/W-0                               | R/W-0               | R/W-0             | R/W-0            | R/W-0, HC, HS                       | R/C-0. HC. HS       |  |  |  |

| SSRC2         | SSRC1                              | SSRC0                               | SSRCG               | SIMSAM            | ASAM             | SAMP                                | DONE <sup>(3)</sup> |  |  |  |

| bit 7         |                                    |                                     |                     |                   |                  |                                     | bit (               |  |  |  |

| Legend:       |                                    | HC - Hardwar                        | e Clearable bit     | HS - Hardwa       | re Settable bit  | C = Clearable bi                    | +                   |  |  |  |

| R = Readable  | a hit                              | W = Writable b                      |                     |                   | nented bit, read |                                     | L                   |  |  |  |

| -n = Value at |                                    | '1' = Bit is set                    | nt -                | '0' = Bit is clea |                  | x = Bit is unknov                   | vp.                 |  |  |  |

|               | FUR                                | I - DILIS SEL                       |                     |                   | aieu             |                                     |                     |  |  |  |

| bit 15        | ADON: ADO                          | C1 Operating M                      | ode bit             |                   |                  |                                     |                     |  |  |  |

|               | 1 = ADC mo<br>0 = ADC is 0         | odule is operatir<br>off            | ng                  |                   |                  |                                     |                     |  |  |  |

| bit 14        | Unimpleme                          | nted: Read as                       | <b>'</b> 0 <b>'</b> |                   |                  |                                     |                     |  |  |  |

| bit 13        | ADSIDL: ADC1 Stop in Idle Mode bit |                                     |                     |                   |                  |                                     |                     |  |  |  |

|               | 1 = Disconti                       | nues module oj                      | peration when o     | device enters     | ldle mode        |                                     |                     |  |  |  |

|               | 0 = Continu                        | es module oper                      | ation in Idle mo    | ode               |                  |                                     |                     |  |  |  |

| bit 12        |                                    | : DMA Buffer B                      |                     |                   |                  |                                     |                     |  |  |  |

|               |                                    |                                     |                     |                   |                  | rovides an addre                    | ess to the DM       |  |  |  |

|               |                                    |                                     |                     |                   |                  | nd-alone buffer<br>des a Scatter/Ga | ther address t      |  |  |  |

|               |                                    |                                     |                     |                   |                  | size of the DMA b                   |                     |  |  |  |

| bit 11        |                                    | nted: Read as                       |                     |                   |                  |                                     |                     |  |  |  |

| bit 10        | AD12B: AD                          | C1 10-Bit or 12                     | -Bit Operation I    | Mode bit          |                  |                                     |                     |  |  |  |

|               |                                    | -channel ADC                        | -                   |                   |                  |                                     |                     |  |  |  |

|               | 0 = 10-bit, 4                      | -channel ADC                        | operation           |                   |                  |                                     |                     |  |  |  |

| bit 9-8       | FORM<1:0>                          | Data Output I                       | Format bits         |                   |                  |                                     |                     |  |  |  |

|               | For 10-Bit C                       |                                     |                     |                   |                  |                                     |                     |  |  |  |

|               |                                    | l fractional (Dou<br>nal (Dou⊤ = dd |                     |                   | 0, where s = .I  | NOT.d<9>)                           |                     |  |  |  |

|               |                                    | l integer (DOUT                     |                     |                   | where $s = .NC$  | (<9>)                               |                     |  |  |  |

|               |                                    | r (Dout = 0000                      |                     |                   |                  |                                     |                     |  |  |  |

|               | For 12-Bit C                       | peration:                           |                     |                   |                  |                                     |                     |  |  |  |

|               | •                                  | fractional (Dou                     |                     |                   | 0, where s = .I  | NOT.d<11>)                          |                     |  |  |  |

|               |                                    |                                     |                     |                   |                  |                                     |                     |  |  |  |

|               |                                    | nal (Dout = dd<br>I integer (Dout   |                     |                   |                  | (<11>)                              |                     |  |  |  |

- 2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 3: Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

## 24.2 PTG Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 24.2.1 KEY RESOURCES

- "Peripheral Trigger Generator" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# 26.3 Programmable CRC Registers

#### REGISTER 26-1: CRCCON1: CRC CONTROL REGISTER 1

| R/W-0                            | U-0                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                  | R-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R-0                                                                                      | R-0                                                | R-0             | R-0            |

|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------|----------------|

| CRCEN                            | —                                                                                                                                                                                                                                                             | CSIDL                                                                                                                                                                                                                                                                  | VWORD4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VWORD3                                                                                   | VWORD2                                             | VWORD1          | VWORD0         |

| bit 15                           | ·                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                          |                                                    |                 | bit 8          |

| R-0                              | R-1                                                                                                                                                                                                                                                           | R/W-0                                                                                                                                                                                                                                                                  | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                    | U-0                                                | U-0             | U-0            |

| CRCFUL                           | CRCMPT                                                                                                                                                                                                                                                        | CRCISEL                                                                                                                                                                                                                                                                | CRCGO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LENDIAN                                                                                  | _                                                  | _               | _              |

| bit 7                            | •                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                          |                                                    |                 | bit (          |

| Legend:                          |                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                          |                                                    |                 |                |

| R = Readable                     | e bit                                                                                                                                                                                                                                                         | W = Writable                                                                                                                                                                                                                                                           | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U = Unimplen                                                                             | nented bit, read                                   | d as '0'        |                |

| -n = Value at                    | POR                                                                                                                                                                                                                                                           | '1' = Bit is set                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | '0' = Bit is cle                                                                         | ared                                               | x = Bit is unkr | nown           |

| bit 15                           | 0 = CRC mo                                                                                                                                                                                                                                                    | dule is enabled                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | chines, pointer                                                                          | s and CRCWD                                        | AT/CRCDAT a     | re reset, othe |