Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I²C, IrDA, LINbus, QEI, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 25                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 8x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

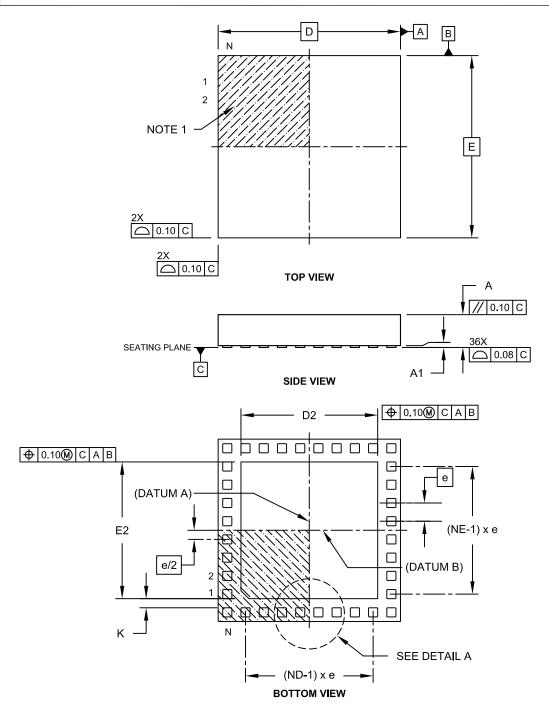

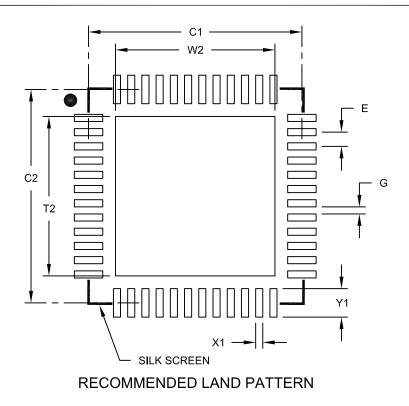

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 36-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 36-VTLA (5x5)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc203-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 2: dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X MOTOR CONTROL FAMILIES

| FA                | MIL                            | ES                            |              |                      |               |                |                                                |                              |        |                    |                  |                                    | _    | _                    | _                            | _                   |      |     | _        | _         |                                |

|-------------------|--------------------------------|-------------------------------|--------------|----------------------|---------------|----------------|------------------------------------------------|------------------------------|--------|--------------------|------------------|------------------------------------|------|----------------------|------------------------------|---------------------|------|-----|----------|-----------|--------------------------------|

|                   | ()                             | es)                           |              |                      |               | Rei            | mappa                                          | ble P                        | eriphe | erals              |                  |                                    |      |                      | -                            |                     |      |     |          |           |                                |

| Device            | Page Erase Size (Instructions) | Program Flash Memory (Kbytes) | RAM (Kbytes) | 16-Bit/32-Bit Timers | Input Capture | Output Compare | Motor Control PWM <sup>(4)</sup><br>(Channels) | Quadrature Encoder Interface | UART   | SPI <sup>(2)</sup> | ECAN™ Technology | External Interrupts <sup>(3)</sup> | I²C™ | <b>CRC Generator</b> | 10-Bit/12-Bit ADC (Channels) | Op Amps/Comparators | CTMU | PTG | I/O Pins | Pins      | Packages                       |

| PIC24EP32MC202    | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP64MC202    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | SPDIP,                         |

| PIC24EP128MC202   | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| PIC24EP256MC202   | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | QFN-S                          |

| PIC24EP512MC202   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP32MC203    | 512                            | 32                            | 4            | -                    |               |                | <u> </u>                                       | ,                            | 6      | 6                  |                  | <u> </u>                           | 6    |                      | _                            |                     | v    | ~   | 0-       |           | ) (T) A                        |

| PIC24EP64MC203    | 1024                           | 64                            | 8            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| PIC24EP32MC204    | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      | 1   |          |           |                                |

| PIC24EP64MC204    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> ,          |

| PIC24EP128MC204   | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| PIC24EP256MC204   | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          | 40        | UQFN                           |

| PIC24EP512MC204   | 1024                           | 512                           | 48           | -                    |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP64MC206    | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| PIC24EP128MC206   | 1024                           | 128                           | 16           | F                    | 4             |                | 6                                              | 4                            | 2      | 2                  |                  | 2                                  | 2    | 1                    | 10                           | 2/4                 | Vaa  | Vaa | 50       | 64        | TQFP,                          |

| PIC24EP256MC206   | 1024                           | 256                           | 32           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 16                           | 3/4                 | Yes  | Yes | 53       | 64        | QFN                            |

| PIC24EP512MC206   | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC202  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC202  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | SPDIP,                         |

| dsPIC33EP128MC202 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 6                            | 2/3 <b>(1)</b>      | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| dsPIC33EP256MC202 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | QFN-S                          |

| dsPIC33EP512MC202 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC203  | 512                            | 32                            | 4            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  |                  | 3                                  | 2    | 1                    | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| dsPIC33EP64MC203  | 1024                           | 64                            | 8            | э                    | 4             | 4              | 0                                              | -                            | 2      | 2                  |                  | ა                                  | 2    | I                    | 0                            | 3/4                 | res  | tes | 25       | 30        | VILA                           |

| dsPIC33EP32MC204  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC204  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | VTLA <sup>(5)</sup> ,          |

| dsPIC33EP128MC204 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | —                | 3                                  | 2    | 1                    | 9                            | 3/4                 | Yes  | Yes | 35       | 44/<br>48 | TQFP,<br>QFN,                  |

| dsPIC33EP256MC204 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | UQFN                           |

| dsPIC33EP512MC204 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC206  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP128MC206 | 1024                           | 128                           | 16           | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | _                | 3                                  | 2    | 1                    | 16                           | 3/4                 | Yes  | Yes | 53       | 64        | TQFP,                          |

| dsPIC33EP256MC206 | 1024                           | 256                           | 32           | 5                    | +             | 1              | 0                                              | 1                            | 2      | 2                  |                  | 5                                  | 2    | · ·                  | 10                           | 5/4                 | 165  | 163 | 55       | 04        | QFN                            |

| dsPIC33EP512MC206 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC502  | 512                            | 32                            | 4            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP64MC502  | 1024                           | 64                            | 8            |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | SPDIP,<br>SOIC,                |

| dsPIC33EP128MC502 | 1024                           | 128                           | 16           | 16 5<br>32           |               | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2    | 1                    | 6                            | 2/3(1)              | Yes  | Yes | 21       | 28        | SOIC,<br>SSOP <sup>(5)</sup> , |

| dsPIC33EP256MC502 | 1024                           | 256                           | 32           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           | QFN-S                          |

| dsPIC33EP512MC502 | 1024                           | 512                           | 48           |                      |               |                |                                                |                              |        |                    |                  |                                    |      |                      |                              |                     |      |     |          |           |                                |

| dsPIC33EP32MC503  | 512                            | 32                            | 4            | 5                    | 4             | 4              | 6                                              | 1                            | 2      | 2                  | 1                | 3                                  | 2    | 1                    | 8                            | 3/4                 | Yes  | Yes | 25       | 36        | VTLA                           |

| dsPIC33EP64MC503  | 1024                           | 64                            | 8            | ~                    |               |                |                                                |                              | _      | _                  |                  |                                    | _    |                      | Ĵ                            | <i></i>             |      |     |          |           |                                |

Note 1: On 28-pin devices, Comparator 4 does not have external connections. Refer to Section 25.0 "Op Amp/Comparator Module" for details. 2: Only SPI2 is remappable.

**3:** INTO is not remappable.

4: Only the PWM Faults are remappable.

5: The SSOP and VTLA packages are not available for devices with 512 Kbytes of memory.

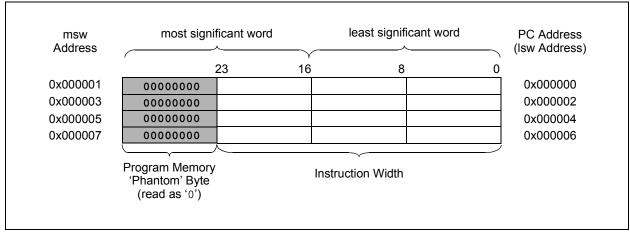

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-6).

Program memory addresses are always word-aligned on the lower word and addresses are incremented, or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

#### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices reserve the addresses between 0x000000 and 0x000200 for hardcoded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-6: PROGRAM MEMORY ORGANIZATION

#### 4.2.5 X AND Y DATA SPACES

# The dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X core has two Data Spaces, X and Y. These Data Spaces can be considered either separate (for some DSP instructions) or as one unified linear address range (for MCU instructions). The Data Spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms, such as Finite Impulse Response (FIR) filtering and Fast Fourier Transform (FFT).

The X Data Space is used by all instructions and supports all addressing modes. X Data Space has separate read and write data buses. The X read data bus is the read data path for all instructions that view Data Space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y Data Space is used in concert with the X Data Space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths.

Both the X and Y Data Spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X Data Space. Modulo Addressing and Bit-Reversed Addressing are not present in PIC24EPXXXGP/MC20X devices.

All data memory writes, including in DSP instructions, view Data Space as combined X and Y address space. The boundary between the X and Y Data Spaces is device-dependent and is not user-programmable.

#### 4.3 Memory Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 4.3.1 KEY RESOURCES

- "Program Memory" (DS70613) in the "dsPIC33/ PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

#### TABLE 4-39: PMD REGISTER MAP FOR dsPIC33EPXXXGP50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   |        |       |       | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  |        | _      | _      | -      | IC4MD  | IC3MD  | IC2MD | IC1MD | _      | _     | _     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  |       |       | CRCMD  | _     | —     | —      |        | —      | I2C2MD |       | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      |       |       | _      | _     | —     | —      | REFOMD | CTMUMD |        |       | 0000          |

| PMD6         | 076A  | _      |        | _      | _      | _      |        |       |       | _      |       | —     | _      |        | —      |        |       | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |       |       |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIND7        | 0700  | _      | _      | _      | _      | _      | _      | _     | _     | _      | —     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |       |       |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-40: PMD REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|---------------|

| PMD1         | 0760  | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | QEI1MD | PWMMD  | _      | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | —      | C1MD   | AD1MD | 0000          |

| PMD2         | 0762  | _      | —      | —      | —      | IC4MD  | IC3MD  | IC2MD  | IC1MD  | _      | —     | —     | _      | OC4MD  | OC3MD  | OC2MD  | OC1MD | 0000          |

| PMD3         | 0764  | _      | _      | _      | _      | _      | CMPMD  | _      | _      | CRCMD  | _     | _     | _      | _      | _      | I2C2MD | _     | 0000          |

| PMD4         | 0766  | _      | _      | _      | _      | _      | _      | _      | _      | _      | _     | _     | _      | REFOMD | CTMUMD | _      | _     | 0000          |

| PMD6         | 076A  | _      | —      |        | _      | _      | PWM3MD | PWM2MD | PWM1MD | —      |       |       | _      | —      |        | —      | -     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA0MD |        |        |        |       |               |

| PMD7         | 076C  |        |        |        |        |        |        |        |        |        |       |       | DMA1MD | PTGMD  |        |        |       | 0000          |

| FIVID7       | 0700  | _      | _      | _      | _      | _      | _      | _      | _      | —      | _     | _     | DMA2MD | FIGND  | _      | _      | _     | 0000          |

|              |       |        |        |        |        |        |        |        |        |        |       |       | DMA3MD |        |        |        |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

DS70000657H-page 95

#### TABLE 4-56: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | _      | _      | _      |        | _      | _     | TRISA8 | _     | —     | —     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 011F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     | RA8    | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     | LATA8  | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     | ODCA8  | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     | CNIEA8 | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     | CNPUA8 | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     | CNPDA8 | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | —      | _     | —      | _     | —     | —     | ANSA4  | —      | —      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-57: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | -       | _       | -       | —       | -      | ANSB8  | _      | _      | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-58: PORTC REGISTER MAP FOR PIC24EPXXXGP/MC203 AND dsPIC33EPXXXGP/MC203/503 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|-------|-------|-------|--------|--------|---------------|

| TRISC        | 0E20  | _      | _      | _      | _      | _      | —      | —     | TRISC8 | _     | -     |       | _     |       | -     | TRISC1 | TRISC0 | 0103          |

| PORTC        | 0E22  |        |        | -      | -      | -      | —      | _     | RC8    | —     | -     |       | _     |       |       | RC1    | RC0    | xxxx          |

| LATC         | 0E24  |        |        | _      | _      | _      | _      | _     | LATC8  | _     | _     | _     | _     | _     | _     | LATC1  | LATC0  | xxxx          |

| ODCC         | 0E26  |        |        | _      | _      | _      | _      | _     | ODCC8  | _     | _     | _     | _     | _     | _     | ODCC1  | ODCC0  | 0000          |

| CNENC        | 0E28  | _      | _      | -      | _      |        | _      | _     | CNIEC8 | —     |       |       | _     |       |       | CNIEC1 | CNIEC0 | 0000          |

| CNPUC        | 0E2A  |        |        | _      | _      | _      | _      | _     | CNPUC8 | _     | _     | _     | _     | _     | _     | CNPUC1 | CNPUC0 | 0000          |

| CNPDC        | 0E2C  |        |        | _      | _      | _      | _      | _     | CNPDC8 | _     | _     | _     | _     | _     | _     | CNPDC1 | CNPDC0 | 0000          |

| ANSELC       | 0E2E  | -      | _      | _      | _      | _      | —      | —     | _      | —     |       | _     | _     | _     |       | ANSC1  | ANSC0  | 0003          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0         | R/W-0                                  | U-0                                    | U-0           | R/W-0                 | U-0               | R/W-0            | R/W-0         |

|---------------|----------------------------------------|----------------------------------------|---------------|-----------------------|-------------------|------------------|---------------|

| TRAPF         | R IOPUWR                               | —                                      | _             | VREGSF                | —                 | CM               | VREGS         |

| bit 15        |                                        |                                        |               |                       |                   |                  | bit 8         |

|               |                                        | DANIO                                  | DAMO          | DAMA                  | DAMO              |                  |               |

| R/W-0         |                                        | R/W-0                                  | R/W-0         | R/W-0                 | R/W-0             | R/W-1            | R/W-1         |

| EXTR<br>bit 7 | SWR                                    | SWDTEN <sup>(2)</sup>                  | WDTO          | SLEEP                 | IDLE              | BOR              | POR           |

|               |                                        |                                        |               |                       |                   |                  | bit (         |

| Legend:       |                                        |                                        |               |                       |                   |                  |               |

| R = Reada     | able bit                               | W = Writable I                         | oit           | U = Unimpler          | mented bit, read  | d as '0'         |               |

| -n = Value    | at POR                                 | '1' = Bit is set                       |               | '0' = Bit is cle      | ared              | x = Bit is unkı  | nown          |

|               |                                        |                                        |               |                       |                   |                  |               |

| bit 15        | •                                      | Reset Flag bit                         |               |                       |                   |                  |               |

|               |                                        | onflict Reset ha<br>onflict Reset ha   |               | d                     |                   |                  |               |

| bit 14        | •                                      | gal Opcode or                          |               |                       | et Flag bit       |                  |               |

|               |                                        | I opcode detec                         |               |                       | •                 | lized W registe  | er used as ar |

|               |                                        | Pointer caused                         |               |                       |                   |                  |               |

|               | -                                      | l opcode or Uni                        |               | egister Reset h       | as not occurred   | d                |               |

| bit 13-12     | -                                      | ted: Read as '                         |               |                       | . 1.9             |                  |               |

| bit 11        |                                        | ash Voltage Reg<br>Itage regulator i   |               |                       | p bit             |                  |               |

|               |                                        | ltage regulator (                      |               | •                     | ing Sleep         |                  |               |

| bit 10        |                                        | ted: Read as '                         | -             | ,,                    | <b>5 F</b>        |                  |               |

| bit 9         | CM: Configur                           | ation Mismatch                         | Flag bit      |                       |                   |                  |               |

|               | 1 = A Configu                          | uration Mismatc<br>uration Mismatc     | h Reset has   |                       |                   |                  |               |

| bit 8         | VREGS: Volta                           | age Regulator S                        | Standby Durir | ng Sleep bit          |                   |                  |               |

|               | •                                      | egulator is active<br>egulator goes in | •             | •                     | еер               |                  |               |

| bit 7         | EXTR: Extern                           | nal Reset (MCL                         | R) Pin bit    |                       |                   |                  |               |

|               |                                        | Clear (pin) Res<br>Clear (pin) Res     |               |                       |                   |                  |               |

| bit 6         | SWR: Softwa                            | re RESET (Instr                        | uction) Flag  | bit                   |                   |                  |               |

|               |                                        | instruction has instruction has        |               |                       |                   |                  |               |

| bit 5         | SWDTEN: So                             | oftware Enable/                        | Disable of W  | DT bit <sup>(2)</sup> |                   |                  |               |

|               | 1 = WDT is e<br>0 = WDT is di          |                                        |               |                       |                   |                  |               |

| bit 4         | WDTO: Watc                             | hdog Timer Tim                         | e-out Flag bi | it                    |                   |                  |               |

|               |                                        | e-out has occur<br>e-out has not oc    |               |                       |                   |                  |               |

| Note 1:       | All of the Reset sta cause a device Re |                                        | set or cleare | d in software. S      | Setting one of th | ese bits in soft | ware does not |

| 2:            | If the FWDTEN Co<br>SWDTEN bit settir  | onfiguration bit i                     | s '1' (unprog | rammed), the V        | VDT is always e   | enabled, regard  | lless of the  |

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

| U-0             | U-0                                                                                          | U-0                                                                                                                                                                     | U-0                                                                             | R-0               | R-0              | R-0             | R-0     |

|-----------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------|------------------|-----------------|---------|

|                 | —                                                                                            |                                                                                                                                                                         |                                                                                 | ILR3              | ILR2             | ILR1            | ILR0    |

| bit 15          |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 | bit 8   |

| R-0             | R-0                                                                                          | R-0                                                                                                                                                                     | R-0                                                                             | R-0               | R-0              | R-0             | R-0     |

| VECNUM7         | VECNUM6                                                                                      | VECNUM5                                                                                                                                                                 | VECNUM4                                                                         | VECNUM3           | VECNUM2          | VECNUM1         | VECNUM0 |

| bit 7           |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 | bit C   |

| Legend:         |                                                                                              |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |

| R = Readable    | bit                                                                                          | W = Writable                                                                                                                                                            | bit                                                                             | U = Unimplen      | nented bit, read | as '0'          |         |

| -n = Value at I | POR                                                                                          | '1' = Bit is set                                                                                                                                                        |                                                                                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |

| bit 15-12       | Unimplemen                                                                                   | ted: Read as '                                                                                                                                                          | 0'                                                                              |                   |                  |                 |         |

| bit 11-8        | -                                                                                            | w CPU Interru                                                                                                                                                           |                                                                                 | el bits           |                  |                 |         |

|                 |                                                                                              | Interrupt Priorit                                                                                                                                                       | -                                                                               |                   |                  |                 |         |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |

|                 |                                                                                              | Interrupt Priori<br>Interrupt Priori                                                                                                                                    |                                                                                 |                   |                  |                 |         |

| bit 7-0         | VECNUM<7:0                                                                                   | >: Vector Nun                                                                                                                                                           | nber of Pendin                                                                  | g Interrupt bits  |                  |                 |         |

|                 | 11111111 = 2                                                                                 | 255, Reserved                                                                                                                                                           | ; do not use                                                                    |                   |                  |                 |         |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |

|                 | •                                                                                            |                                                                                                                                                                         |                                                                                 |                   |                  |                 |         |

|                 | 00001000 = 8<br>00000111 = 7<br>00000110 = 8<br>00000101 = 8<br>00000100 = 7<br>00000011 = 3 | 9, IC1 – Input (<br>8, INT0 – Exter<br>7, Reserved; d<br>6, Generic soft<br>5, DMAC error<br>4, Math error tr<br>3, Stack error t<br>2, Generic hard<br>1, Address erro | rnal Interrupt C<br>o not use<br>error trap<br>trap<br>rap<br>d trap<br>or trap | )                 |                  |                 |         |

#### REGISTER 7-7: INTTREG: INTERRUPT CONTROL AND STATUS REGISTER

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|                               |     |                |     |                   | UNIRUL RE       |                 |       |

|-------------------------------|-----|----------------|-----|-------------------|-----------------|-----------------|-------|

| U-0                           | U-0 | U-0            | U-0 | U-0               | R/W-0           | U-0             | U-0   |

| —                             | _   | —              | —   | —                 | CMPMD           | —               | —     |

| bit 15                        |     |                |     |                   |                 |                 | bit 8 |

|                               |     |                |     |                   |                 |                 |       |

| R/W-0                         | U-0 | U-0            | U-0 | U-0               | U-0             | R/W-0           | U-0   |

| CRCMD                         | —   | —              | _   | —                 | —               | I2C2MD          | —     |

| bit 7                         |     |                |     |                   |                 |                 | bit C |

|                               |     |                |     |                   |                 |                 |       |

| Legend:                       |     |                |     |                   |                 |                 |       |

| R = Readable                  | bit | W = Writable I | bit | U = Unimplem      | ented bit, read | l as '0'        |       |

| n = Value at POR '1' = Bit is |     |                |     | '0' = Bit is clea | ared            | x = Bit is unkn | own   |

#### REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| bit 10  | CMPMD: Comparator Module Disable bit |

|---------|--------------------------------------|

|         | 1 = Comparator module is disabled    |

|         | 0 = Comparator module is enabled     |

| bit 9-8 | Unimplemented: Read as '0'           |

| bit 7   | CRCMD: CRC Module Disable bit        |

|         | 1 = CRC module is disabled           |

|         | 0 = CRC module is enabled            |

| bit 6-2 | Unimplemented: Read as '0'           |

| bit 1   | I2C2MD: I2C2 Module Disable bit      |

|         | 1 = I2C2 module is disabled          |

|         | 0 = I2C2 module is enabled           |

| bit 0   | Unimplemented: Read as '0'           |

|         |                                      |

#### REGISTER 10-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

|        | -   |     |     |        |        |     |       |

|--------|-----|-----|-----|--------|--------|-----|-------|

| U-0    | U-0 | U-0 | U-0 | U-0    | U-0    | U-0 | U-0   |

| —      | —   |     |     | —      | —      | —   | —     |

| bit 15 |     |     |     |        |        |     | bit 8 |

|        |     |     |     |        |        |     |       |

| U-0    | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | U-0 | U-0   |

| —      | —   | —   | —   | REFOMD | CTMUMD | —   | —     |

| bit 7  |     |     |     |        |        |     | bit 0 |

|        |     |     |     |        |        |     |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 3    | <b>REFOMD:</b> Reference Clock Module Disable bit          |

|          | <ol> <li>1 = Reference clock module is disabled</li> </ol> |

|          | 0 = Reference clock module is enabled                      |

| bit 2    | CTMUMD: CTMU Module Disable bit                            |

|          | 1 = CTMU module is disabled                                |

|          | 0 = CTMU module is enabled                                 |

| bit 1-0  | Unimplemented: Read as '0'                                 |

$\ensuremath{\textcircled{}^\circ}$  2011-2013 Microchip Technology Inc.

#### REGISTER 11-8: RPINR14: PERIPHERAL PIN SELECT INPUT REGISTER 14 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|---------------------------|----------------------------------------------------------------------------------------------------|----------------------------|-------------------|-----------------|-----------------|-------|

| —            |                           |                                                                                                    |                            | QEB1R<6:0>        |                 |                 |       |

| bit 15       |                           |                                                                                                    |                            |                   |                 |                 | bit 8 |

|              |                           |                                                                                                    |                            |                   |                 |                 |       |

| U-0          | R/W-0                     | R/W-0                                                                                              | R/W-0                      | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |                           |                                                                                                    |                            | QEA1R<6:0>        |                 |                 |       |

| bit 7        |                           |                                                                                                    |                            |                   |                 |                 | bit 0 |

|              |                           |                                                                                                    |                            |                   |                 |                 |       |

| Legend:      |                           |                                                                                                    |                            |                   |                 |                 |       |

| R = Readat   | ole bit                   | W = Writable                                                                                       | bit                        | U = Unimplen      | nented bit, rea | ad as '0'       |       |

| -n = Value a | at POR                    | '1' = Bit is set                                                                                   |                            | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 1111001 =                 | 1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss                    | 121<br>P1                  |                   |                 |                 |       |

| bit 7        | Unimpleme                 | nted: Read as '                                                                                    | 0'                         |                   |                 |                 |       |

| bit 6-0      | (see Table 1<br>1111001 = | >: Assign A (QE<br>1-2 for input pin<br>Input tied to RPI<br>Input tied to CM<br>Input tied to Vss | selection nun<br>121<br>P1 |                   | n Pin bits      |                 |       |

#### **REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is cleared only by software

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

- 2: Each Output Compare x module (OCx) has one PTG clock source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

- PTGO4 = OC1 PTGO5 = OC2

- PTGO6 = OC3 PTGO7 = OC4

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0                                                                  | U-0   | U-0              | U-0   | R/W-0                                   | R/W-0 | R/W-0  | R/W-0 |

|----------------------------------------------------------------------|-------|------------------|-------|-----------------------------------------|-------|--------|-------|

| —                                                                    | -     | —                | —     |                                         | LEB   | <11:8> |       |

| bit 15                                                               |       |                  |       |                                         |       |        | bit 8 |

|                                                                      |       |                  |       |                                         |       |        |       |

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0  | R/W-0 |

|                                                                      |       |                  | LEE   | 3<7:0>                                  |       |        |       |

| bit 7                                                                |       |                  |       |                                         |       |        | bit 0 |

|                                                                      |       |                  |       |                                         |       |        |       |

| Legend:                                                              |       |                  |       |                                         |       |        |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       |                                         |       |        |       |

| -n = Value at F                                                      | POR   | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |        |       |

#### REGISTER 16-17: LEBDLYx: PWMx LEADING-EDGE BLANKING DELAY REGISTER

bit 15-12 Unimplemented: Read as '0'

bit 11-0 LEB<11:0>: Leading-Edge Blanking Delay for Current-Limit and Fault Inputs bits

#### REGISTER 17-2: QEI1IOC: QEI1 I/O CONTROL REGISTER (CONTINUED)

- bit 2 INDEX: Status of INDXx Input Pin After Polarity Control

- 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

- bit 1 QEB: Status of QEBx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1' 0 = Pin is at logic '0'

- bit 0 **QEA:** Status of QEAx Input Pin After Polarity Control And SWPAB Pin Swapping 1 = Pin is at logic '1'

- 0 = Pin is at logic '0'

# **19.2** I<sup>2</sup>C Control Registers

#### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0            | U-0                             | R/W-0                                    | R/W-1, HC            | R/W-0                        | R/W-0             | R/W-0           | R/W-0          |

|------------------|---------------------------------|------------------------------------------|----------------------|------------------------------|-------------------|-----------------|----------------|

| I2CEN            | —                               | I2CSIDL                                  | SCLREL               | IPMIEN <sup>(1)</sup>        | A10M              | DISSLW          | SMEN           |

| bit 15           |                                 |                                          |                      |                              |                   |                 | bit 8          |

|                  |                                 |                                          |                      |                              |                   |                 |                |

| R/W-0            | R/W-0                           | R/W-0                                    | R/W-0, HC            | R/W-0, HC                    | R/W-0, HC         | R/W-0, HC       | R/W-0, HC      |

| GCEN             | STREN                           | ACKDT                                    | ACKEN                | RCEN                         | PEN               | RSEN            | SEN            |

| bit 7            |                                 |                                          |                      |                              |                   |                 | bit 0          |

| Legend:          |                                 | HC = Hardware                            | Clearable bit        |                              |                   |                 |                |

| R = Readab       | le bit                          | W = Writable bi                          |                      | U = Unimpler                 | mented bit, rea   | d as '0'        |                |

| -n = Value a     | It POR                          | '1' = Bit is set                         |                      | '0' = Bit is cle             |                   | x = Bit is unk  | nown           |

|                  |                                 |                                          |                      |                              |                   |                 |                |

| bit 15           | I2CEN: I2Cx                     | Enable bit                               |                      |                              |                   |                 |                |

|                  |                                 | the I2Cx module                          |                      |                              |                   |                 | ;              |

| L:1 4 4          |                                 | the I2Cx module                          | ; all I-C ™ pins a   | are controlled               | by port function  | IS              |                |

| bit 14<br>bit 13 | -                               | ited: Read as '0'                        | do bit               |                              |                   |                 |                |

| DIC 13           |                                 | Stop in Idle Mo<br>ues module oper       |                      | rice enters an l             | dle mode          |                 |                |

|                  |                                 | s module operati                         |                      |                              |                   |                 |                |

| bit 12           | SCLREL: SC                      | Lx Release Con                           | rol bit (when op     | perating as I <sup>2</sup> C | slave)            |                 |                |

|                  | 1 = Releases                    |                                          |                      |                              |                   |                 |                |

|                  |                                 | Lx clock low (clo                        | ck stretch)          |                              |                   |                 |                |

|                  | If STREN = 1<br>Bit is R/W (i e | <u>.:</u><br>e., software can w          | rite '0' to initiate | e stretch and w              | rite '1' to relea | se clock) Harr  | lware is clear |

|                  | at the beginn                   | ing of every slav<br>reception. Hardv    | ve data byte tra     | ansmission. Ha               | ardware is clea   | r at the end o  |                |

|                  | If STREN = 0                    |                                          |                      |                              |                   |                 |                |

|                  |                                 | ., software can or                       |                      |                              |                   |                 |                |

| hit 11           | -                               | te transmission.<br>Iligent Peripheral   |                      |                              | -                 | address byte re | eception.      |

| bit 11           |                                 | le is enabled; all                       |                      |                              |                   |                 |                |

|                  | $0 = IPMI \mod$                 |                                          |                      | , lon no me agea             |                   |                 |                |

| bit 10           | A10M: 10-Bit                    | Slave Address b                          | oit                  |                              |                   |                 |                |

|                  |                                 | is a 10-bit slave                        |                      |                              |                   |                 |                |

|                  |                                 | is a 7-bit slave a                       |                      |                              |                   |                 |                |

| bit 9            |                                 | able Slew Rate (                         |                      |                              |                   |                 |                |

|                  |                                 | control is disable<br>control is enable  |                      |                              |                   |                 |                |

| bit 8            |                                 | us Input Levels b                        |                      |                              |                   |                 |                |

|                  |                                 | /O pin thresholds                        |                      | SMBus speci                  | fication          |                 |                |

|                  |                                 | SMBus input thre                         |                      | ,                            |                   |                 |                |

| bit 7            | GCEN: Gene                      | eral Call Enable b                       | it (when operat      | ing as I <sup>2</sup> C slav | /e)               |                 |                |

|                  |                                 | nterrupt when a ge<br>call address disal |                      | ss is received ir            | n I2CxRSR (mo     | dule is enabled | for reception) |

|                  |                                 |                                          |                      |                              |                   |                 |                |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

| REGISTER 24-6: | PTGSDLIM: PTG STEP DELAY LIMIT REGISTER <sup>(1,2)</sup> |

|----------------|----------------------------------------------------------|

|                |                                                          |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|------------------|-----------------|-------|

|                 |       |                  | PTGSD | LIM<15:8>         |                  |                 |       |

| bit 15          |       |                  |       |                   |                  |                 | bit 8 |

|                 |       |                  |       |                   |                  |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|                 |       |                  | PTGSE | )LIM<7:0>         |                  |                 |       |

| bit 7           |       |                  |       |                   |                  |                 | bit 0 |

|                 |       |                  |       |                   |                  |                 |       |

| Legend:         |       |                  |       |                   |                  |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimplen      | nented bit, read | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

bit 15-0 **PTGSDLIM<15:0>:** PTG Step Delay Limit Register bits Holds a PTG Step delay value representing the number of additional PTG clocks between the start of a Step command and the completion of a Step command.

**Note 1:** A base Step delay of one PTG clock is added to any value written to the PTGSDLIM register (Step Delay = (PTGSDLIM) + 1).

2: This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

#### REGISTER 24-7: PTGC0LIM: PTG COUNTER 0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|-----------------|-----------------|-------|