Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

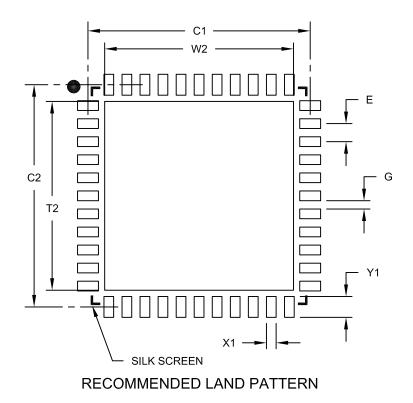

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc204-e-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for ICSP and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Voltage Input High (VIH) and Voltage Input Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> PICkit<sup>™</sup> 3, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on MPLAB ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) DS51749

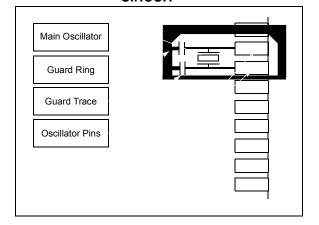

### 2.6 External Oscillator Pins

Many DSCs have options for at least two oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator. For details, see **Section 9.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

### TABLE 4-52: PORTG REGISTER MAP FOR PIC24EPXXXGP/MC206 AND dsPIC33EPXXXGP/MC206/506 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| TRISG        | 0E60  | _      | -      | _      | _      | -      | -      | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _     | _     | _     | _     | _     | -     | 03C0          |

| PORTG        | 0E62  |        |        | -      | _      | _      | _      | RG9    | RG8    | RG7    | RG6    | _     | _     | _     | _     | _     | _     | xxxx          |

| LATG         | 0E64  |        |        | -      | _      | _      | _      | LATG9  | LATG8  | LATG7  | LATG6  | _     | _     | _     | _     | _     | _     | xxxx          |

| ODCG         | 0E66  |        |        | -      | _      | _      | _      | ODCG9  | ODCG8  | ODCG7  | ODCG6  | _     | _     | _     | _     | _     | _     | 0000          |

| CNENG        | 0E68  |        |        | -      | _      | _      | _      | CNIEG9 | CNIEG8 | CNIEG7 | CNIEG6 | _     | _     | _     | _     | _     | _     | 0000          |

| CNPUG        | 0E6A  |        |        | -      | _      | _      | _      | CNPUG9 | CNPUG8 | CNPUG7 | CNPUG6 | _     | _     | _     | _     | _     | _     | 0000          |

| CNPDG        | 0E6C  | _      | -      | _      | _      |        |        | CNPDG9 | CNPDG8 | CNPDG7 | CNPDG6 | _     | _     | -     | _     | _     |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

| bit 3 | <b>SLEEP:</b> Wake-up from Sleep Flag bit<br>1 = Device has been in Sleep mode<br>0 = Device has not been in Sleep mode |

|-------|-------------------------------------------------------------------------------------------------------------------------|

| bit 2 | IDLE: Wake-up from Idle Flag bit                                                                                        |

|       | <ol> <li>Device was in Idle mode</li> <li>Device was not in Idle mode</li> </ol>                                        |

| bit 1 | <b>BOR:</b> Brown-out Reset Flag bit<br>1 = A Brown-out Reset has occurred<br>0 = A Brown-out Reset has not occurred    |

| bit 0 | <b>POR:</b> Power-on Reset Flag bit<br>1 = A Power-on Reset has occurred<br>0 = A Power-on Reset has not occurred       |

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

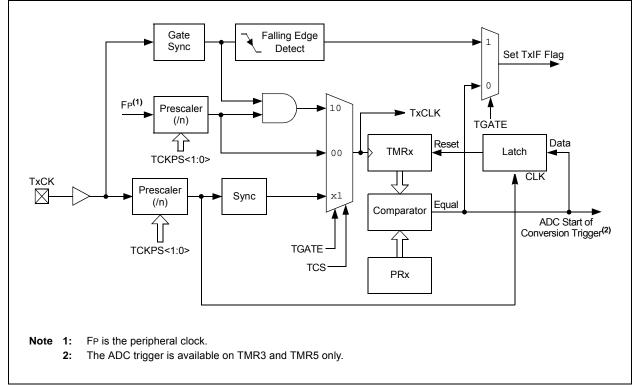

### FIGURE 13-2: TYPE C TIMER BLOCK DIAGRAM (x = 3 AND 5)

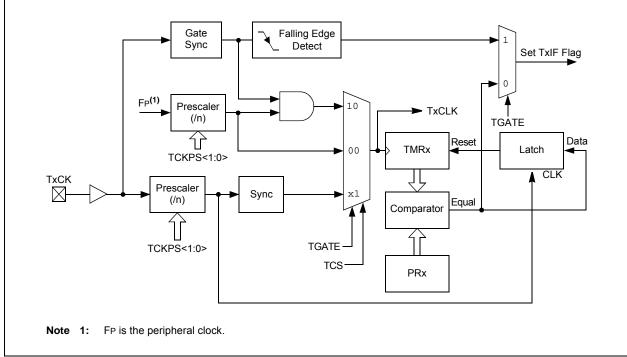

# FIGURE 13-1:TYPE B TIMER BLOCK DIAGRAM (x = 2 AND 4)

### REGISTER 16-8: PDCx: PWMx GENERATOR DUTY CYCLE REGISTER

| R/W-0                                                                 | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|-----------------------------------------------------------------------|-------|-------|-------|------------------------------------|-------|-------|-------|--|--|

|                                                                       |       |       | PDC   | <15:8>                             |       |       |       |  |  |

| bit 15                                                                |       |       |       |                                    |       |       | bit 8 |  |  |

|                                                                       |       |       |       |                                    |       |       |       |  |  |

| R/W-0                                                                 | R/W-0 | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0 | R/W-0 |  |  |

|                                                                       |       |       | PDC   | x<7:0>                             |       |       |       |  |  |

| bit 7                                                                 |       |       |       |                                    |       |       | bit 0 |  |  |

|                                                                       |       |       |       |                                    |       |       |       |  |  |

| Legend:                                                               |       |       |       |                                    |       |       |       |  |  |

| R = Readable bit W = Writable bit                                     |       |       | oit   | U = Unimplemented bit, read as '0' |       |       |       |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is un |       |       |       | x = Bit is unkr                    | nown  |       |       |  |  |

bit 15-0 **PDCx<15:0>:** PWMx Generator # Duty Cycle Value bits

### REGISTER 16-9: PHASEx: PWMx PRIMARY PHASE-SHIFT REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |  |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|--------------------|-------|--|--|

|                                   |       |                  | PHAS  | Ex<15:8>                           |       |                    |       |  |  |

| bit 15                            |       |                  |       |                                    |       |                    | bit 8 |  |  |

|                                   |       |                  |       |                                    |       |                    |       |  |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |  |  |

|                                   |       |                  | PHAS  | SEx<7:0>                           |       |                    |       |  |  |

| bit 7                             |       |                  |       |                                    |       |                    | bit 0 |  |  |

|                                   |       |                  |       |                                    |       |                    |       |  |  |

| Legend:                           |       |                  |       |                                    |       |                    |       |  |  |

| R = Readable bit W = Writable bit |       |                  | pit   | U = Unimplemented bit, read as '0' |       |                    |       |  |  |

| -n = Value at P                   | POR   | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unknown |       |  |  |

bit 15-0 PHASEx<15:0>: PWMx Phase-Shift Value or Independent Time Base Period for the PWM Generator bits

Note 1: If ITB (PWMCONx<9>) = 0, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCON<11:10>) = 00, 01 or 10), PHASEx<15:0> = Phase-shift value for PWMxH and PWMxL outputs

If ITB (PWMCONx<9>) = 1, the following applies based on the mode of operation: Complementary, Redundant and Push-Pull Output mode (PMOD<1:0> (IOCONx<11:10>) = 00, 01 or 10), PHASEx<15:0> = Independent time base period value for PWMxH and PWMxL

| U-0              | R/W-0                                                                | R/W-0                              | R/W-0           | R/W-0             | R/W-0                          | R/W-0                | R/W-0           |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------|------------------------------------|-----------------|-------------------|--------------------------------|----------------------|-----------------|--|--|--|--|--|--|

| _                | CLSRC4                                                               | CLSRC3                             | CLSRC2          | CLSRC1            | CLSRC0                         | CLPOL <sup>(2)</sup> | CLMOD           |  |  |  |  |  |  |

| bit 15           |                                                                      |                                    | •               |                   |                                |                      | bit 8           |  |  |  |  |  |  |

|                  | <b>D</b> 4 4                                                         | D 0.01 4                           | <b>D</b> 444    |                   | DAMA                           | DAMA                 | <b>D</b> 444.0  |  |  |  |  |  |  |

| R/W-1            | R/W-1                                                                | R/W-1                              | R/W-1           | R/W-1             | R/W-0<br>FLTPOL <sup>(2)</sup> | R/W-0                | R/W-0           |  |  |  |  |  |  |

| FLTSRC4<br>bit 7 | FLTSRC3                                                              | FLTSRC2                            | FLTSRC1         | FLTSRC0           | FLIPOL-                        | FLTMOD1              | FLTMOD0<br>bit  |  |  |  |  |  |  |

|                  |                                                                      |                                    |                 |                   |                                |                      | DI              |  |  |  |  |  |  |

| Legend:          |                                                                      |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

| R = Readable     | bit                                                                  | W = Writable                       | bit             | U = Unimpler      | mented bit, read               | l as '0'             |                 |  |  |  |  |  |  |

| -n = Value at I  | POR                                                                  | '1' = Bit is set                   |                 | '0' = Bit is cle  | ared                           | x = Bit is unkr      | nown            |  |  |  |  |  |  |

|                  |                                                                      |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

| bit 15           | Unimplemen                                                           | ted: Read as '                     | 0'              |                   |                                |                      |                 |  |  |  |  |  |  |

| bit 14-10        | CLSRC<4:0>                                                           | Current-Limit                      | Control Signa   | al Source Seleo   | ct for PWM Ger                 | nerator # bits       |                 |  |  |  |  |  |  |

|                  | 11111 = Fault 32                                                     |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | 11110 = Reserved                                                     |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | •                                                                    |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | •                                                                    |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | •<br>01100 = Reserved                                                |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | 01011 = Comparator 4                                                 |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | 01011 = Op Amp/Comparator 3                                          |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | 01001 = Op Amp/Comparator 2                                          |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | 01000 = Op Amp/Comparator 1                                          |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | 00111 = Reserved                                                     |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | 00110 = Reserved                                                     |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | 00101 = Reserved                                                     |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | 00100 = Reserved                                                     |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | 00011 <b>= Fault 4</b>                                               |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | 00010 = Fault 3                                                      |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | 00001 = Fault 2                                                      |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | 00000 = Fault 1 (default)                                            |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

| bit 9            | CLPOL: Current-Limit Polarity for PWM Generator # bit <sup>(2)</sup> |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | 1 = The selected current-limit source is active-low                  |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | 0 = The selec                                                        | cted current-lim                   | it source is ac | tive-high         |                                |                      |                 |  |  |  |  |  |  |

| bit 8            | CLMOD: Cur                                                           | rent-Limit Mode                    | e Enable for P  | WM Generator      | r # bit                        |                      |                 |  |  |  |  |  |  |

|                  |                                                                      | imit mode is er<br>imit mode is di |                 |                   |                                |                      |                 |  |  |  |  |  |  |

|                  | ne PWMLOCK                                                           |                                    |                 | <6>) is a '1', th | e IOCONx regi                  | ster can only be     | e written aftei |  |  |  |  |  |  |

| the              | unlock sequen                                                        | ce has been ex                     | ecuted.         |                   |                                |                      |                 |  |  |  |  |  |  |

|                  |                                                                      |                                    |                 |                   |                                |                      |                 |  |  |  |  |  |  |

# REGISTER 16-15: FCLCONx: PWMx FAULT CURRENT-LIMIT CONTROL REGISTER<sup>(1)</sup>

2: These bits should be changed only when PTEN = 0. Changing the clock selection during operation will yield unpredictable results.

|                                   | R/W-0 | R/W-0            | R/W-0                                 | R/W-0                                                            | R/W-0                                                                                                | R/W-0                                                                                                    |  |

|-----------------------------------|-------|------------------|---------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|

|                                   |       | QEIG             | EC<31:24>                             |                                                                  |                                                                                                      |                                                                                                          |  |

|                                   |       |                  |                                       |                                                                  |                                                                                                      | bit 8                                                                                                    |  |

|                                   | DAMO  |                  |                                       |                                                                  | DAMO                                                                                                 |                                                                                                          |  |

| R/W-U                             | R/W-0 |                  |                                       | R/W-U                                                            | R/W-U                                                                                                | R/W-0                                                                                                    |  |

|                                   |       | QEIGE            | EC<23:16>                             |                                                                  |                                                                                                      |                                                                                                          |  |

|                                   |       |                  |                                       |                                                                  |                                                                                                      | bit (                                                                                                    |  |

|                                   |       |                  |                                       |                                                                  |                                                                                                      |                                                                                                          |  |

| R = Readable bit W = Writable bit |       | t                | U = Unimplem                          | nented bit, rea                                                  | d as '0'                                                                                             |                                                                                                          |  |

| -n = Value at POR '1'             |       | '1' = Bit is set |                                       | ared                                                             | x = Bit is unknown                                                                                   |                                                                                                          |  |

|                                   |       | W = Writable bi  | R/W-0 R/W-0 QEIGI<br>W = Writable bit | R/W-0 R/W-0 R/W-0 QEIGEC<23:16><br>W = Writable bit U = Unimplem | R/W-0     R/W-0     R/W-0       QEIGEC<23:16>       W = Writable bit     U = Unimplemented bit, real | R/W-0       R/W-0       R/W-0       R/W-0         QEIGEC<23:16>       U = Unimplemented bit, read as '0' |  |

### REGISTER 17-15: QEI1GECH: QEI1 GREATER THAN OR EQUAL COMPARE HIGH WORD REGISTER

bit 15-0 QEIGEC<31:16>: High Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

### REGISTER 17-16: QEI1GECL: QEI1 GREATER THAN OR EQUAL COMPARE LOW WORD REGISTER

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|-----------------------------------|-------|------------------|------------------------------------|-----------------------------------------|-------|-------|-------|--|

|                                   |       |                  | QEIGE                              | C<15:8>                                 |       |       |       |  |

| bit 15                            |       |                  |                                    |                                         |       |       | bit 8 |  |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0                              | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|                                   |       |                  | QEIG                               | EC<7:0>                                 |       |       |       |  |

| bit 7                             |       |                  |                                    |                                         |       |       | bit 0 |  |

| Legend:                           |       |                  |                                    |                                         |       |       |       |  |

| R = Readable bit W = Writable bit |       |                  | U = Unimplemented bit, read as '0' |                                         |       |       |       |  |

| -n = Value at P                   | OR    | '1' = Bit is set |                                    | '0' = Bit is cleared x = Bit is unknowr |       |       | nown  |  |

bit 15-0 QEIGEC<15:0>: Low Word Used to Form 32-Bit Greater Than or Equal Compare Register (QEI1GEC) bits

| <b>Legend:</b><br>R = Readable | bit   | C = Writable b<br>W = Writable l |      |        | n to clear the bit<br>mented bit, read |       |       |

|--------------------------------|-------|----------------------------------|------|--------|----------------------------------------|-------|-------|

| bit 7                          |       |                                  |      |        |                                        |       | bit 0 |

| IVRIF                          | WAKIF | ERRIF                            | _    | FIFOIF | RBOVIF                                 | RBIF  | TBIF  |

| R/C-0                          | R/C-0 | R/C-0                            | U-0  | R/C-0  | R/C-0                                  | R/C-0 | R/C-0 |

|                                |       |                                  |      |        |                                        |       | 2 0   |

| bit 15                         |       |                                  |      |        |                                        |       | bit 8 |

| _                              | —     | ТХВО                             | TXBP | RXBP   | TXWAR                                  | RXWAR | EWARN |

| U-0                            | U-0   | R-0                              | R-0  | R-0    | R-0                                    | R-0   | R-0   |

'0' = Bit is cleared

x = Bit is unknown

### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER

'1' = Bit is set

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                   |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | <b>TXBO:</b> Transmitter in Error State Bus Off bit                                                                                          |

|           | 1 = Transmitter is in Bus Off state                                                                                                          |

|           | 0 = Transmitter is not in Bus Off state                                                                                                      |

| bit 12    | <b>TXBP:</b> Transmitter in Error State Bus Passive bit                                                                                      |

|           | <ul><li>1 = Transmitter is in Bus Passive state</li><li>0 = Transmitter is not in Bus Passive state</li></ul>                                |

| bit 11    | <b>RXBP:</b> Receiver in Error State Bus Passive bit                                                                                         |

|           | 1 = Receiver is in Bus Passive state<br>0 = Receiver is not in Bus Passive state                                                             |

| bit 10    | TXWAR: Transmitter in Error State Warning bit                                                                                                |

|           | 1 = Transmitter is in Error Warning state<br>0 = Transmitter is not in Error Warning state                                                   |

| bit 9     | RXWAR: Receiver in Error State Warning bit                                                                                                   |

|           | 1 = Receiver is in Error Warning state<br>0 = Receiver is not in Error Warning state                                                         |

| bit 8     | EWARN: Transmitter or Receiver in Error State Warning bit                                                                                    |

|           | <ul> <li>1 = Transmitter or receiver is in Error Warning state</li> <li>0 = Transmitter or receiver is not in Error Warning state</li> </ul> |

| bit 7     | IVRIF: Invalid Message Interrupt Flag bit                                                                                                    |

|           | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>                                       |

| bit 6     | WAKIF: Bus Wake-up Activity Interrupt Flag bit                                                                                               |

|           | 1 = Interrupt request has occurred<br>0 = Interrupt request has not occurred                                                                 |

| bit 5     | ERRIF: Error Interrupt Flag bit (multiple sources in CxINTF<13:8>)                                                                           |

|           | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>                                       |

| bit 4     | Unimplemented: Read as '0'                                                                                                                   |

| bit 3     | FIFOIF: FIFO Almost Full Interrupt Flag bit                                                                                                  |

|           | 1 = Interrupt request has occurred                                                                                                           |

|           | 0 = Interrupt request has not occurred                                                                                                       |

| bit 2     | RBOVIF: RX Buffer Overflow Interrupt Flag bit                                                                                                |

|           | 1 = Interrupt request has occurred                                                                                                           |

-n = Value at POR

### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

|--------|-----|-----|-----|-----|----------|----------|---------|

| —      | —   | —   | —   | -   | CH123NB1 | CH123NB0 | CH123SB |

| bit 15 |     |     |     |     |          |          | bit 8   |

|        |     |     |     |     |          |          |         |

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0    | R/W-0    | R/W-0   |

|-------|-----|-----|-----|-----|----------|----------|---------|

| —     | —   | —   | —   | —   | CH123NA1 | CH123NA0 | CH123SA |

| bit 7 |     |     |     |     |          |          | bit 0   |

## Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-11 Unimplemented: Read as '0'

bit 10-9

**CH123NB<1:0>:** Channel 1, 2, 3 Negative Input Select for Sample MUXB bits In 12-bit mode (AD21B = 1), CH123NB is Unimplemented and is Read as '0':

| Value           | ADC Channel |       |       |  |  |  |

|-----------------|-------------|-------|-------|--|--|--|

| Value           | CH1         | CH2   | CH3   |  |  |  |

| 11              | AN9         | AN10  | AN11  |  |  |  |

| 10 <b>(1,2)</b> | OA3/AN6     | AN7   | AN8   |  |  |  |

| 0x              | Vrefl       | VREFL | Vrefl |  |  |  |

bit 8 **CH123SB:** Channel 1, 2, 3 Positive Input Select for Sample MUXB bit In 12-bit mode (AD21B = 1), CH123SB is Unimplemented and is Read as '0':

| Value          | ADC Channel |         |         |  |  |  |

|----------------|-------------|---------|---------|--|--|--|

| value          | CH1         | CH2     | CH3     |  |  |  |

| 1 <b>(2)</b>   | OA1/AN3     | OA2/AN0 | OA3/AN6 |  |  |  |

| 0 <b>(1,2)</b> | OA2/AN0     | AN1     | AN2     |  |  |  |

bit 7-3 Unimplemented: Read as '0'

bit 2-1 **CH123NA<1:0>:** Channel 1, 2, 3 Negative Input Select for Sample MUXA bits In 12-bit mode (AD21B = 1), CH123NA is Unimplemented and is Read as '0':

| Value           | ADC Channel |       |       |  |  |  |

|-----------------|-------------|-------|-------|--|--|--|

| Value           | CH1         | CH2   | CH3   |  |  |  |

| 11              | AN9         | AN10  | AN11  |  |  |  |

| 10 <b>(1,2)</b> | OA3/AN6     | AN7   | AN8   |  |  |  |

| 0x              | VREFL       | VREFL | Vrefl |  |  |  |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

### REGISTER 23-6: AD1CHS0: ADC1 INPUT CHANNEL 0 SELECT REGISTER (CONTINUED)

| bit 4-0 | CH0SA<4:0>: Channel 0 Positive Input Select for Sample MUXA bits <sup>(1)</sup>                     |

|---------|-----------------------------------------------------------------------------------------------------|

|         | 11111 = Open; use this selection with CTMU capacitive and time measurement                          |

|         | 11110 = Channel 0 positive input is connected to the CTMU temperature measurement diode (CTMU TEMP) |

|         | 11101 = Reserved                                                                                    |

|         | 11100 = Reserved                                                                                    |

|         | 11011 = Reserved                                                                                    |

|         | 11010 = Channel 0 positive input is the output of OA3/AN6 <sup>(2,3)</sup>                          |

|         | 11001 = Channel 0 positive input is the output of OA2/AN0 <sup>(2)</sup>                            |

|         | 11000 = Channel 0 positive input is the output of OA1/AN3 <sup>(2)</sup>                            |

|         | 10110 = Reserved                                                                                    |

|         | •                                                                                                   |

|         | •                                                                                                   |

|         |                                                                                                     |

|         | 10000 = Reserved                                                                                    |

|         | 01111 = Channel 0 positive input is AN15 <sup>(1,3)</sup>                                           |

|         | 01110 = Channel 0 positive input is AN14 <sup>(1,3)</sup>                                           |

|         | 01101 = Channel 0 positive input is AN13 <sup>(1,3)</sup>                                           |

|         | •                                                                                                   |

|         |                                                                                                     |

|         | 00010 = Channel 0 positive input is AN2 <sup>(1,3)</sup>                                            |

|         | 00001 = Channel 0 positive input is AN1 <sup>(1,3)</sup>                                            |

|         | 00000 = Channel 0 positive input is AN0(1,3)                                                        |

|         |                                                                                                     |

- **Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

- 2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

- 3: See the "Pin Diagrams" section for the available analog channels for each device.

# 24.3 PTG Control Registers

#### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER

| R/W-0  | U-0  | R/W-0   | R/W-0   | U-0 | R/W-0                 | R/W-0                  | R/W-0   |

|--------|------|---------|---------|-----|-----------------------|------------------------|---------|

| PTGEN  | —    | PTGSIDL | PTGTOGL | _   | PTGSWT <sup>(2)</sup> | PTGSSEN <sup>(3)</sup> | PTGIVIS |

| bit 15 | •    |         |         |     |                       | · · · · ·              | bit 8   |

|        |      |         |         |     |                       |                        |         |

| R/W-0  | HS-0 | U-0     | U-0     | U-0 | U-0                   | R/W                    | /-0     |

| R/W-0   | HS-0    | U-0 | U-0 | U-0 | U-0 | R/V                    | V-0                    |

|---------|---------|-----|-----|-----|-----|------------------------|------------------------|

| PTGSTRT | PTGWDTO | —   | _   | —   | —   | PTGITM1 <sup>(1)</sup> | PTGITM0 <sup>(1)</sup> |

| bit 7   |         |     |     |     |     |                        | bit 0                  |

| Legend:           | HS = Hardware Settable bit |                                    |                    |  |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15  | PTGEN: Module Enable bit                                                                                                                                                                                                                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = PTG module is enabled                                                                                                                                                                                                                                                                                    |

|         | 0 = PTG module is disabled                                                                                                                                                                                                                                                                                   |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                   |

| bit 13  | PTGSIDL: PTG Stop in Idle Mode bit                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                                                                                                      |

| bit 12  | PTGTOGL: PTG TRIG Output Toggle Mode bit                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Toggle state of the PTGOx for each execution of the PTGTRIG command</li> <li>0 = Each execution of the PTGTRIG command will generate a single PTGOx pulse determined by the value in the PTGPWDx bits</li> </ul>                                                                                |

| bit 11  | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                   |

| bit 10  | PTGSWT: PTG Software Trigger bit <sup>(2)</sup>                                                                                                                                                                                                                                                              |

|         | <ul> <li>1 = Triggers the PTG module</li> <li>0 = No action (clearing this bit will have no effect)</li> </ul>                                                                                                                                                                                               |

| bit 9   | PTGSSEN: PTG Enable Single-Step bit <sup>(3)</sup>                                                                                                                                                                                                                                                           |

|         | 1 = Enables Single-Step mode<br>0 = Disables Single-Step mode                                                                                                                                                                                                                                                |

| bit 8   | PTGIVIS: PTG Counter/Timer Visibility Control bit                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the current values of their corresponding counter/timer registers (PTGSD, PTGCx, PTGTx)</li> <li>0 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the value previously written to those limit registers</li> </ul> |

| bit 7   | PTGSTRT: PTG Start Sequencer bit                                                                                                                                                                                                                                                                             |

|         | <ul><li>1 = Starts to sequentially execute commands (Continuous mode)</li><li>0 = Stops executing commands</li></ul>                                                                                                                                                                                         |

| bit 6   | PTGWDTO: PTG Watchdog Timer Time-out Status bit                                                                                                                                                                                                                                                              |

|         | <ul> <li>1 = PTG Watchdog Timer has timed out</li> <li>0 = PTG Watchdog Timer has not timed out.</li> </ul>                                                                                                                                                                                                  |

| bit 5-2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                   |

| Note 1: | These bits apply to the PTGWHI and PTGWLO commands only.                                                                                                                                                                                                                                                     |

| 2:      | This bit is only used with the PTGCTRL step command software trigger option.                                                                                                                                                                                                                                 |

|         |                                                                                                                                                                                                                                                                                                              |

3: Use of the PTG Single-Step mode is reserved for debugging tools only.

## REGISTER 24-4: PTGT0LIM: PTG TIMER0 LIMIT REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0        | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|-----------------|--------------|------------------|-------|-----------------------------------------|-------|-------|-------|--|--|

|                 |              |                  | PTGT0 | _IM<15:8>                               |       |       |       |  |  |

| bit 15          | bit 15 bit 8 |                  |       |                                         |       |       |       |  |  |

|                 |              |                  |       |                                         |       |       |       |  |  |

| R/W-0           | R/W-0        | R/W-0            | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |  |

|                 |              |                  | PTGT0 | LIM<7:0>                                |       |       |       |  |  |

| bit 7           |              |                  |       |                                         |       |       | bit 0 |  |  |

|                 |              |                  |       |                                         |       |       |       |  |  |

| Legend:         |              |                  |       |                                         |       |       |       |  |  |

| R = Readable    | bit          | W = Writable b   | bit   | U = Unimplemented bit, read as '0'      |       |       |       |  |  |

| -n = Value at P | POR          | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |       |       | nown  |  |  |

#### bit 15-0 **PTGT0LIM<15:0>:** PTG Timer0 Limit Register bits General Purpose Timer0 Limit register (effective only with a PTGT0 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

### REGISTER 24-5: PTGT1LIM: PTG TIMER1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0          | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|----------------|-------|-------|-------|-------|-------|-------|-------|--|

| PTGT1LIM<15:8> |       |       |       |       |       |       |       |  |

| bit 15         |       |       |       |       |       |       | bit 8 |  |

|                |       |       |       |       |       |       |       |  |

| R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|---------------|-------|-------|-------|-------|-------|-------|-------|--|

| PTGT1LIM<7:0> |       |       |       |       |       |       |       |  |

| bit 7 bit 0   |       |       |       |       |       |       |       |  |

| Legend:           |                  |                                                 |                    |  |  |

|-------------------|------------------|-------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                            | x = Bit is unknown |  |  |

bit 15-0 **PTGT1LIM<15:0>:** PTG Timer1 Limit Register bits

General Purpose Timer1 Limit register (effective only with a PTGT1 Step command).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

### REGISTER 25-3: CM4CON: COMPARATOR 4 CONTROL REGISTER (CONTINUED)

- bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator Reference Select bit (VIN+ input)<sup>(1)</sup>

- 1 = VIN+ input connects to internal CVREFIN voltage

- 0 = VIN+ input connects to C4IN1+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Channel Select bits<sup>(1)</sup>

- 11 = VIN- input of comparator connects to OA3/AN6

- 10 = VIN- input of comparator connects to OA2/AN0

- 01 = VIN- input of comparator connects to OA1/AN3

- 00 = VIN- input of comparator connects to C4IN1-

- Note 1: Inputs that are selected and not available will be tied to Vss. See the "Pin Diagrams" section for available inputs for each package.

| Bit Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| GCP                    | General Segment Code-Protect bit<br>1 = User program memory is not code-protected<br>0 = Code protection is enabled for the entire program memory space                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| GWRP                   | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| IESO                   | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Start up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start up device with user-selected oscillator source</li> </ul>                                                                                                                                                                                           |  |  |  |  |  |

| PWMLOCK <sup>(1)</sup> | PWM Lock Enable bit<br>1 = Certain PWM registers may only be written after a key sequence<br>0 = PWM registers may be written without a key sequence                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| FNOSC<2:0>             | Oscillator Selection bits<br>111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)<br>110 = Fast RC Oscillator with Divide-by-16 (FRCDIV16)<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved; do not use<br>011 = Primary Oscillator with PLL module (XT + PLL, HS + PLL, EC + PLL)<br>010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator with Divide-by-N with PLL module (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |  |  |  |  |  |

| FCKSM<1:0>             | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                                           |  |  |  |  |  |

| IOL1WAY                | Peripheral Pin Select Configuration bit<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| OSCIOFNC               | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is the clock output<br>0 = OSC2 is a general purpose digital I/O pin                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| POSCMD<1:0>            | Primary Oscillator Mode Select bits<br>11 = Primary Oscillator is disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                                                           |  |  |  |  |  |

| FWDTEN                 | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled. Clearing the SWDTEN bit in the RCON register will have no effect.)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                                                                                                 |  |  |  |  |  |

| WINDIS                 | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| PLLKEN                 | PLL Lock Enable bit<br>1 = PLL lock is enabled<br>0 = PLL lock is disabled<br>nly available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

### TABLE 27-2: CONFIGURATION BITS DESCRIPTION

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

2: When JTAGEN = 1, an internal pull-up resistor is enabled on the TMS pin. Erased devices default to JTAGEN = 1. Applications requiring I/O pins in a high-impedance state (tri-state) in Reset should use pins other than TMS for this purpose. Most instructions are a single word. Certain double-word instructions are designed to provide all the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it executes as a NOP.

The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the Program Counter is changed as a result of the instruction, or a PSV or Table Read is performed, or an SFR register is read. In these cases, the execution takes multiple instruction cycles with the additional instruction cycle(s) executed as a NOP. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note: For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157). For more information on instructions that take more than one instruction cycle to execute, refer to **"CPU"** (DS70359) in the *"dsPIC33/PIC24 Family Reference Manual"*, particularly the **"Instruction Flow Types"** section.

| Field               | Description                                                                          |  |  |  |  |  |

|---------------------|--------------------------------------------------------------------------------------|--|--|--|--|--|

| #text               | Means literal defined by "text"                                                      |  |  |  |  |  |

| (text)              | Means "content of text"                                                              |  |  |  |  |  |

| [text]              | Means "the location addressed by text"                                               |  |  |  |  |  |

| {}                  | Optional field or operation                                                          |  |  |  |  |  |

| $a \in \{b, c, d\}$ | a is selected from the set of values b, c, d                                         |  |  |  |  |  |

| <n:m></n:m>         | Register bit field                                                                   |  |  |  |  |  |

| .b                  | Byte mode selection                                                                  |  |  |  |  |  |

| .d                  | Double-Word mode selection                                                           |  |  |  |  |  |

| .S                  | Shadow register select                                                               |  |  |  |  |  |

| .w                  | Word mode selection (default)                                                        |  |  |  |  |  |

| Acc                 | One of two accumulators {A, B}                                                       |  |  |  |  |  |

| AWB                 | Accumulator write back destination address register ∈ {W13, [W13]+ = 2}              |  |  |  |  |  |

| bit4                | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$        |  |  |  |  |  |

| C, DC, N, OV, Z     | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |  |  |  |  |  |

| Expr                | Absolute address, label or expression (resolved by the linker)                       |  |  |  |  |  |

| f                   | File register address ∈ {0x00000x1FFF}                                               |  |  |  |  |  |

| lit1                | 1-bit unsigned literal $\in \{0,1\}$                                                 |  |  |  |  |  |

| lit4                | 4-bit unsigned literal ∈ {015}                                                       |  |  |  |  |  |

| lit5                | 5-bit unsigned literal ∈ {031}                                                       |  |  |  |  |  |

| lit8                | 8-bit unsigned literal ∈ {0255}                                                      |  |  |  |  |  |

| lit10               | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode               |  |  |  |  |  |

| lit14               | 14-bit unsigned literal ∈ {016384}                                                   |  |  |  |  |  |

| lit16               | 16-bit unsigned literal ∈ {065535}                                                   |  |  |  |  |  |

| lit23               | 23-bit unsigned literal ∈ {08388608}; LSb must be '0'                                |  |  |  |  |  |

| None                | Field does not require an entry, can be blank                                        |  |  |  |  |  |

| OA, OB, SA, SB      | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate          |  |  |  |  |  |

| PC                  | Program Counter                                                                      |  |  |  |  |  |

| Slit10              | 10-bit signed literal ∈ {-512511}                                                    |  |  |  |  |  |

| Slit16              | 16-bit signed literal ∈ {-3276832767}                                                |  |  |  |  |  |

| Slit6               | 6-bit signed literal ∈ {-1616}                                                       |  |  |  |  |  |

| Wb                  | Base W register ∈ {W0W15}                                                            |  |  |  |  |  |

| Wd                  | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                    |  |  |  |  |  |

| Wdo                 | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |  |  |  |  |  |

#### TABLE 28-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

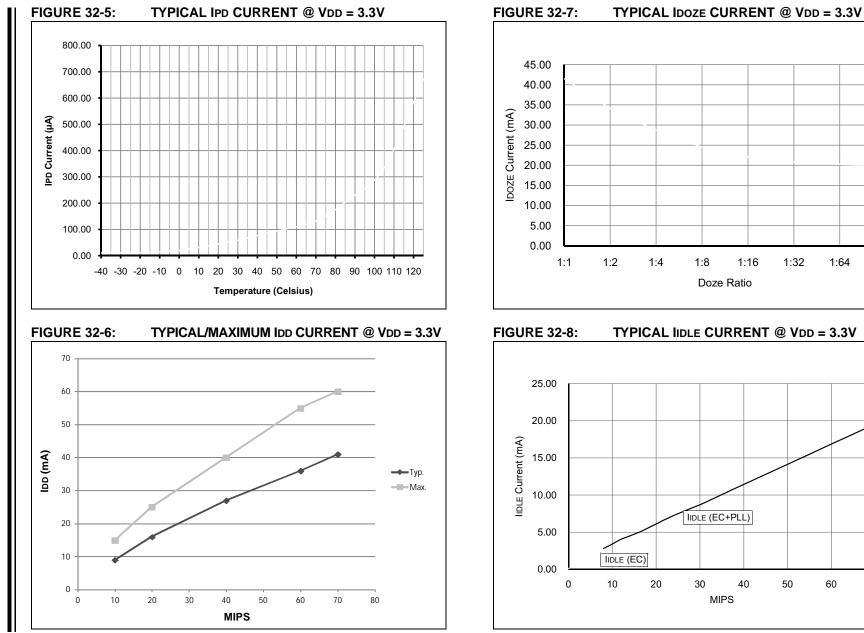

| DC CHARACTERISTICS |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |       |            |      |           |  |  |

|--------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|------|-----------|--|--|

| Parameter<br>No.   | Тур.                      | Max.                                                                                                                                                                                                                                                                                    | Units | Conditions |      |           |  |  |

| Operating Cur      | rent (IDD) <sup>(1)</sup> |                                                                                                                                                                                                                                                                                         |       |            |      |           |  |  |

| DC20d              | 9                         | 15                                                                                                                                                                                                                                                                                      | mA    | -40°C      |      |           |  |  |

| DC20a              | 9                         | 15                                                                                                                                                                                                                                                                                      | mA    | +25°C      | 3.3V | 10 MIPS   |  |  |

| DC20b              | 9                         | 15                                                                                                                                                                                                                                                                                      | mA    | +85°C      | 3.3V |           |  |  |

| DC20c              | 9                         | 15                                                                                                                                                                                                                                                                                      | mA    | +125°C     |      |           |  |  |

| DC22d              | 16                        | 25                                                                                                                                                                                                                                                                                      | mA    | -40°C      |      | 20 MIPS   |  |  |

| DC22a              | 16                        | 25                                                                                                                                                                                                                                                                                      | mA    | +25°C      | 3.3∨ |           |  |  |

| DC22b              | 16                        | 25                                                                                                                                                                                                                                                                                      | mA    | +85°C      | 3.3V |           |  |  |

| DC22c              | 16                        | 25                                                                                                                                                                                                                                                                                      | mA    | +125°C     |      |           |  |  |

| DC24d              | 27                        | 40                                                                                                                                                                                                                                                                                      | mA    | -40°C      |      | 40 MIPS   |  |  |

| DC24a              | 27                        | 40                                                                                                                                                                                                                                                                                      | mA    | +25°C      | 3.3V |           |  |  |

| DC24b              | 27                        | 40                                                                                                                                                                                                                                                                                      | mA    | +85°C      | 3.3V |           |  |  |

| DC24c              | 27                        | 40                                                                                                                                                                                                                                                                                      | mA    | +125°C     |      |           |  |  |

| DC25d              | 36                        | 55                                                                                                                                                                                                                                                                                      | mA    | -40°C      |      | 60 MIPS   |  |  |

| DC25a              | 36                        | 55                                                                                                                                                                                                                                                                                      | mA    | +25°C      | 3.3V |           |  |  |

| DC25b              | 36                        | 55                                                                                                                                                                                                                                                                                      | mA    | +85°C      | 3.3V | OU IVIIPS |  |  |

| DC25c              | 36                        | 55                                                                                                                                                                                                                                                                                      | mA    | +125°C     | 7    |           |  |  |

| DC26d              | 41                        | 60                                                                                                                                                                                                                                                                                      | mA    | -40°C      |      |           |  |  |

| DC26a              | 41                        | 60                                                                                                                                                                                                                                                                                      | mA    | +25°C      | 3.3V | 70 MIPS   |  |  |

| DC26b              | 41                        | 60                                                                                                                                                                                                                                                                                      | mA    | +85°C      |      |           |  |  |

#### TABLE 30-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)