Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 60 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

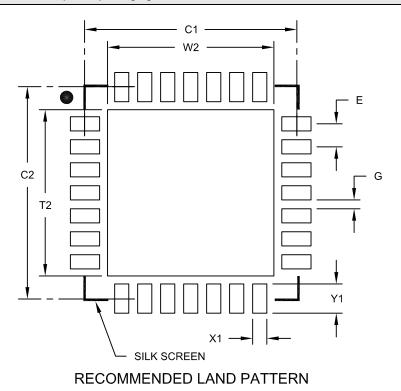

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc204-e-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

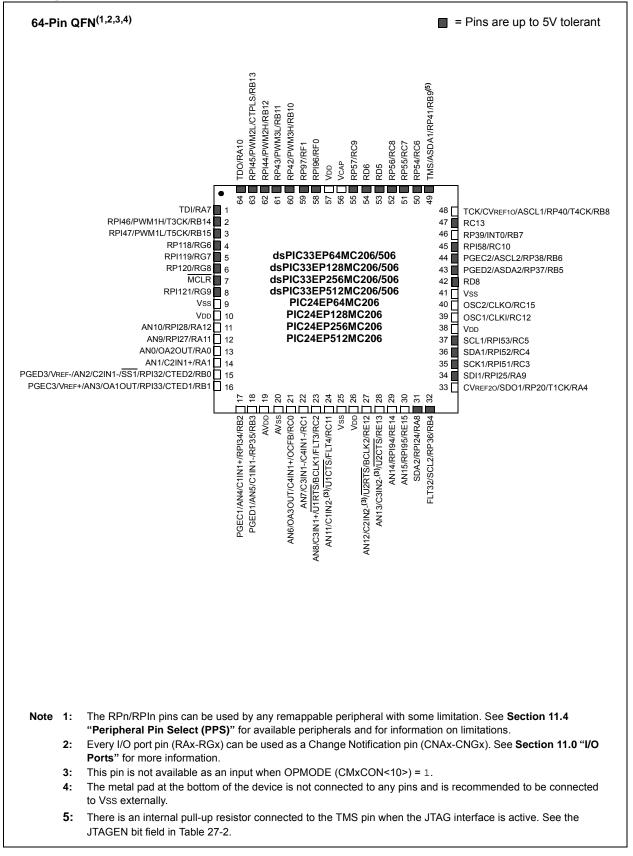

#### Pin Diagrams (Continued)

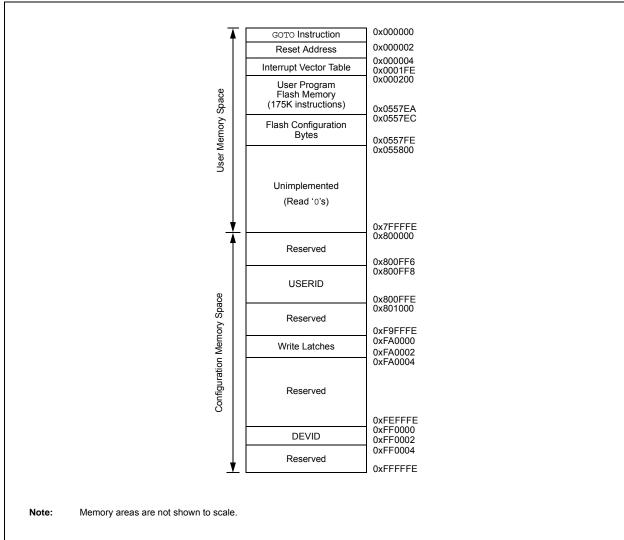

#### FIGURE 4-5: PROGRAM MEMORY MAP FOR dsPIC33EP512GP50X, dsPIC33EP512MC20X/50X AND PIC24EP512GP/MC20X DEVICES

### 4.4 Special Function Register Maps

### TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND dsPIC33EPXXXGP50X DEVICES ONLY

|           |       | 0.00   |        |        |              | 011 401    |        |       | 20/0/00/    |        |       |        |         |          |          | -     | r     |               |

|-----------|-------|--------|--------|--------|--------------|------------|--------|-------|-------------|--------|-------|--------|---------|----------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12       | Bit 11     | Bit 10 | Bit 9 | Bit 8       | Bit 7  | Bit 6 | Bit 5  | Bit 4   | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| W0        | 0000  |        |        |        |              |            |        |       | W0 (WR      | EG)    |       |        |         |          |          |       |       | xxxx          |

| W1        | 0002  |        |        |        |              |            |        |       | W1          |        |       |        |         |          |          |       |       | xxxx          |

| W2        | 0004  |        |        |        |              |            |        |       | W2          |        |       |        |         |          |          |       |       | xxxx          |

| W3        | 0006  |        |        |        |              |            |        |       | W3          |        |       |        |         |          |          |       |       | xxxx          |

| W4        | 8000  |        |        |        |              |            |        |       | W4          |        |       |        |         |          |          |       |       | xxxx          |

| W5        | 000A  |        |        |        |              |            |        |       | W5          |        |       |        |         |          |          |       |       | xxxx          |

| W6        | 000C  |        |        |        |              |            |        |       | W6          |        |       |        |         |          |          |       |       | xxxx          |

| W7        | 000E  |        |        |        |              |            |        |       | W7          |        |       |        |         |          |          |       |       | xxxx          |

| W8        | 0010  |        |        |        |              |            |        |       | W8          |        |       |        |         |          |          |       |       | xxxx          |

| W9        | 0012  |        |        |        |              |            |        |       | W9          |        |       |        |         |          |          |       |       | xxxx          |

| W10       | 0014  |        |        |        |              |            |        |       | W10         |        |       |        |         |          |          |       |       | xxxx          |

| W11       | 0016  |        |        |        |              |            |        |       | W11         |        |       |        |         |          |          |       |       | xxxx          |

| W12       | 0018  |        |        |        |              |            |        |       | W12         |        |       |        |         |          |          |       |       | xxxx          |

| W13       | 001A  |        |        |        |              |            |        |       | W13         |        |       |        |         |          |          |       |       | xxxx          |

| W14       | 001C  |        |        |        |              |            |        |       | W14         |        |       |        |         |          |          |       |       | xxxx          |

| W15       | 001E  |        |        |        |              |            |        |       | W15         |        |       |        |         |          |          |       |       | xxxx          |

| SPLIM     | 0020  |        |        |        |              |            |        |       | SPLI        | N      |       |        |         |          |          |       |       | 0000          |

| ACCAL     | 0022  |        |        |        |              |            |        |       | ACCA        | L      |       |        |         |          |          |       |       | 0000          |

| ACCAH     | 0024  |        |        |        |              |            |        |       | ACCA        | H      |       |        |         |          |          |       |       | 0000          |

| ACCAU     | 0026  |        |        | Si     | gn Extensior | n of ACCA< | 39>    |       |             |        |       |        | ACO     | CAU      |          |       |       | 0000          |

| ACCBL     | 0028  |        |        |        |              |            |        |       | ACCB        | L      |       |        |         |          |          |       |       | 0000          |

| ACCBH     | 002A  |        |        |        |              |            |        |       | ACCB        | Н      |       |        |         |          |          |       |       | 0000          |

| ACCBU     | 002C  |        |        | Si     | gn Extensior | n of ACCB< | 39>    |       |             |        |       |        | ACO     | CBU      |          |       |       | 0000          |

| PCL       | 002E  |        |        |        |              |            |        | F     | PCL<15:0>   |        |       |        |         |          |          |       |       | 0000          |

| PCH       | 0030  | _      | _      | _      | —            | _          | _      | —     | _           | _      |       |        |         | PCH<6:0> |          |       |       | 0000          |

| DSRPAG    | 0032  | _      | _      | _      | —            | _          | _      |       |             |        |       | DSRPAC | 6<9:0>  |          |          |       |       | 0001          |

| DSWPAG    | 0034  | _      |        | _      | —            |            | _      | _     |             |        |       | DS     | WPAG<8: | 0>       |          |       |       | 0001          |

| RCOUNT    | 0036  |        |        |        |              |            |        |       | RCOUNT<     | :15:0> |       |        |         |          |          |       |       | 0000          |

| DCOUNT    | 0038  |        |        |        |              |            |        |       | DCOUNT<     | :15:0> |       |        |         |          |          |       |       | 0000          |

| DOSTARTL  | 003A  |        |        |        |              |            |        | DOS   | STARTL<15:1 | >      |       |        |         |          |          |       |       | 0000          |

| DOSTARTH  | 003C  | _      | —      | —      | _            | —          | —      | —     | _           | _      | —     |        |         | DOSTAF   | RTH<5:0> |       |       | 0000          |

| DOENDL    | 003E  |        |        |        |              |            |        | DO    | ENDL<15:1>  | >      |       |        |         |          |          |       |       | 0000          |

| DOENDH    | 0040  | _      | —      | —      | —            | —          | —      | _     | —           | —      | —     |        |         | DOEND    | )H<5:0>  |       |       | 0000          |

|           |       |        |        |        |              |            |        |       |             |        |       |        |         |          |          |       |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-3**: INTERRUPT CONTROLLER REGISTER MAP FOR PIC24EPXXXGP20X DEVICES ONLY

| TADLL        | τу.   |        |        |            | VELEN  |        |        |            |        |       |         | DEVICE      |         |         |          |              |         |               |

|--------------|-------|--------|--------|------------|--------|--------|--------|------------|--------|-------|---------|-------------|---------|---------|----------|--------------|---------|---------------|

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8  | Bit 7 | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2    | Bit 1        | Bit 0   | All<br>Resets |

| IFS0         | 0800  |        | DMA1IF | AD1IF      | U1TXIF | U1RXIF | SPI1IF | SPI1EIF    | T3IF   | T2IF  | OC2IF   | IC2IF       | DMA0IF  | T1IF    | OC1IF    | IC1IF        | INTOIF  | 0000          |

| IFS1         | 0802  | U2TXIF | U2RXIF | INT2IF     | T5IF   | T4IF   | OC4IF  | OC3IF      | DMA2IF | _     | _       | —           | INT1IF  | CNIF    | CMIF     | MI2C1IF      | SI2C1IF | 0000          |

| IFS2         | 0804  |        | _      | _          | -      |        | _      | —          | _      | _     | IC4IF   | IC3IF       | DMA3IF  | _       | —        | SPI2IF       | SPI2EIF | 0000          |

| IFS3         | 0806  | _      | _      | _          | _      | _      | _      | _          | _      | _     | _       | _           | _       | _       | MI2C2IF  | SI2C2IF      | _       | 0000          |

| IFS4         | 0808  | _      | _      | CTMUIF     | _      | _      | _      | _          | _      | _     | _       | _           | _       | CRCIF   | U2EIF    | U1EIF        | _       | 0000          |

| IFS8         | 0810  | JTAGIF | ICDIF  |            | _      | _      | _      | _          | —      | _     | _       | _           | _       | _       | —        | —            | —       | 0000          |

| IFS9         | 0812  | _      | _      | _          | _      | _      | _      | _          | —      | _     | PTG3IF  | PTG2IF      | PTG1IF  | PTG0IF  | PTGWDTIF | PTGSTEPIF    | —       | 0000          |

| IEC0         | 0820  | _      | DMA1IE | AD1IE      | U1TXIE | U1RXIE | SPI1IE | SPI1EIE    | T3IE   | T2IE  | OC2IE   | IC2IE       | DMA0IE  | T1IE    | OC1IE    | IC1IE        | INT0IE  | 0000          |

| IEC1         | 0822  | U2TXIE | U2RXIE | INT2IE     | T5IE   | T4IE   | OC4IE  | OC3IE      | DMA2IE | _     | _       | _           | INT1IE  | CNIE    | CMIE     | MI2C1IE      | SI2C1IE | 0000          |

| IEC2         | 0824  | _      | _      | _          | _      | _      | _      | _          | _      | _     | IC4IE   | IC3IE       | DMA3IE  | _       | _        | SPI2IE       | SPI2EIE | 0000          |

| IEC3         | 0826  | _      | _      | _          | _      | _      | _      | _          | —      | _     | _       | _           | _       | _       | MI2C2IE  | SI2C2IE      | —       | 0000          |

| IEC4         | 0828  | _      | _      | CTMUIE     | _      | _      | _      | _          | _      | _     | _       | _           | _       | CRCIE   | U2EIE    | U1EIE        | _       | 0000          |

| IEC8         | 0830  | JTAGIE | ICDIE  | _          | _      | _      | _      | _          | _      | _     | _       | _           | _       | _       | _        | _            | _       | 0000          |

| IEC9         | 0832  | _      | _      | _          | _      | _      | _      | _          | —      | _     | PTG3IE  | PTG2IE      | PTG1IE  | PTG0IE  | PTGWDTIE | PTGSTEPIE    | —       | 0000          |

| IPC0         | 0840  | _      |        | T1IP<2:0>  |        | _      | (      | OC1IP<2:0  | >      | _     |         | IC1IP<2:0>  |         | —       |          | INT0IP<2:0>  |         | 4444          |

| IPC1         | 0842  | _      |        | T2IP<2:0>  |        | _      | (      | OC2IP<2:0  | >      | _     |         | IC2IP<2:0>  |         | _       | C        | 0MA0IP<2:0>  |         | 4444          |

| IPC2         | 0844  | _      | U      | J1RXIP<2:0 | >      | _      | ;      | SPI1IP<2:0 | >      | _     |         | SPI1EIP<2:0 | >       | _       |          | T3IP<2:0>    |         | 4444          |

| IPC3         | 0846  | _      | _      | _          | _      | _      | D      | )MA1IP<2:  | 0>     | _     |         | AD1IP<2:0>  |         | _       | ι        | J1TXIP<2:0>  |         | 0444          |

| IPC4         | 0848  |        |        | CNIP<2:0>  |        |        |        | CMIP<2:0   | >      | _     |         | MI2C1IP<2:0 | >       | _       | S        | SI2C1IP<2:0> |         | 4444          |

| IPC5         | 084A  | _      | _      | _          | _      | _      | _      | _          | _      | _     | _       | —           | _       | _       | I        | INT1IP<2:0>  |         | 0004          |

| IPC6         | 084C  | _      |        | T4IP<2:0>  |        | _      | (      | OC4IP<2:0  | >      | _     |         | OC3IP<2:0>  |         | _       | C        | )ma2IP<2:0>  |         | 4444          |

| IPC7         | 084E  |        | I      | U2TXIP<2:0 | >      |        | L      | J2RXIP<2:  | )>     | _     |         | INT2IP<2:0> |         | _       |          | T5IP<2:0>    |         | 4444          |

| IPC8         | 0850  |        | _      | _          | _      |        | _      | —          | —      | _     |         | SPI2IP<2:0> |         | _       | S        | SPI2EIP<2:0> |         | 0044          |

| IPC9         | 0852  |        | _      | _          | _      |        |        | IC4IP<2:0  | >      | _     |         | IC3IP<2:0>  |         | _       | C        | 0MA3IP<2:0>  |         | 0444          |

| IPC12        | 0858  |        | _      | _          | _      |        | N      | 112C2IP<2: | 0>     | _     |         | SI2C2IP<2:0 | >       | _       | _        | _            | _       | 0440          |

| IPC16        | 0860  |        |        | CRCIP<2:0> | >      |        |        | U2EIP<2:0  | >      | _     |         | U1EIP<2:0>  |         | _       | _        | _            | _       | 4440          |

| IPC19        | 0866  |        | _      | _          | _      | _      | _      | _          | _      | _     |         | CTMUIP<2:0  | >       | _       | _        | _            | _       | 0040          |

| IPC35        | 0886  |        |        | JTAGIP<2:0 | >      | _      |        | ICDIP<2:0  | >      | _     | _       | _           | _       | _       | _        | _            | _       | 4400          |

| IPC36        | 0888  | _      |        | PTG0IP<2:0 | >      | _      | PT     | GWDTIP<    | 2:0>   | _     | P       | TGSTEPIP<2  | :0>     | _       | _        | —            | _       | 4440          |

| IPC37        | 088A  | _      | _      | _          | _      | _      | F      | PTG3IP<2:  | )>     | _     |         | PTG2IP<2:0  | >       | _       | F        | PTG1IP<2:0>  |         | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | _      |        |        |            | —      | _     | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR   | OSCFAIL      |         | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | _      |        |        |            | _      | _     |         | —           | —       | _       | INT2EP   | INT1EP       | INT0EP  | 8000          |

| INTCON3      | 08C4  | _      | _      |            | _      |        |        | _          | _      | _     | _       | DAE         | DOOVR   | _       | _        | —            |         | 0000          |

| INTCON4      | 08C6  |        | _      | _          | _      | _      | _      | —          | _      | _     | _       | _           | _       | _       | _        |              | SGHT    | 0000          |

| INTTREG      | 08C8  | _      |        |            | _      |        | ILR<   | 3:0>       |        |       |         |             | VECN    | UM<7:0> |          |              |         | 0000          |

|              |       |        |        |            |        |        |        |            |        |       |         |             |         |         |          |              |         |               |

--- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

| IABLE 4-2  | 23: E | CAN1 I | REGIST | ER MA  | P WHE  | N WIN  | (CICIE | <l1<0></l1<0> | •) = 1 FC | OR dsPIC | 33EPX    | XXMC/G | P50X D | EVICES | ONLY ( |       | NUED) |               |

|------------|-------|--------|--------|--------|--------|--------|--------|---------------|-----------|----------|----------|--------|--------|--------|--------|-------|-------|---------------|

| File Name  | Addr  | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9         | Bit 8     | Bit 7    | Bit 6    | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

| C1RXF11EID | 046E  |        |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF12SID | 0470  |        |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | _      | EID<1 | 7:16> | xxxx          |

| C1RXF12EID | 0472  |        |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF13SID | 0474  |        |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF13EID | 0476  |        |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF14SID | 0478  |        |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | —      | EID<1 | 7:16> | xxxx          |

| C1RXF14EID | 047A  |        |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

| C1RXF15SID | 047C  |        |        |        | SID<   | :10:3> |        |               |           |          | SID<2:0> |        | _      | EXIDE  | _      | EID<1 | 7:16> | xxxx          |

| C1RXF15EID | 047E  |        |        |        | EID<   | :15:8> |        |               |           |          |          |        | EID<   | 7:0>   |        |       |       | xxxx          |

#### ECANI DECISTED MAD WHEN WIN (CICTDI 1 -0.) 1 EOD doDIC22EDXXXMC/CDE0X DEVICES ONLY (CONTINUED) TARIE 1 22.

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| U-0    | U-0 | U-0 | U-0 | U-0   | U-0   | U-0   | U-0   |

|--------|-----|-----|-----|-------|-------|-------|-------|

| _      |     |     |     | _     | —     |       | —     |

| bit 15 |     |     |     |       |       |       | bit 8 |

|        |     |     |     |       |       |       |       |

| U-0    | U-0 | U-0 | U-0 | R-0   | R-0   | R-0   | R-0   |

| —      | —   | —   | _   | PPST3 | PPST2 | PPST1 | PPST0 |

| bit 7  |     |     |     |       |       |       | bit 0 |

#### REGISTER 8-14: DMAPPS: DMA PING-PONG STATUS REGISTER

| Legend:      |         |                                                                                       |                       |                    |

|--------------|---------|---------------------------------------------------------------------------------------|-----------------------|--------------------|

| R = Readat   | ole bit | W = Writable bit                                                                      | U = Unimplemented bit | , read as '0'      |

| -n = Value a | at POR  | '1' = Bit is set                                                                      | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-4     | Unimplo | mented: Read as '0'                                                                   |                       |                    |

| bit 3        | •       | DMA Channel 3 Ping-Pong I                                                             | Modo Status Elag bit  |                    |

| bit 5        | 1 = DMA | ASTB3 register is selected<br>ASTA3 register is selected                              | vioue Status Flag bit |                    |

| bit 2        | 1 = DMA | DMA Channel 2 Ping-Pong I<br>ASTB2 register is selected<br>ASTA2 register is selected | Mode Status Flag bit  |                    |

| bit 1        | PPST1:  | DMA Channel 1 Ping-Pong I                                                             | Mode Status Flag bit  |                    |

|              |         | CTD1 register is calested                                                             |                       |                    |

- 1 = DMASTB1 register is selected0 = DMASTA1 register is selected

- bit 0 PPST0: DMA Channel 0 Ping-Pong Mode Status Flag bit

- 1 = DMASTB0 register is selected

- 0 = DMASTA0 register is selected

## 13.0 TIMER2/3 AND TIMER4/5

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Timers" (DS70362) of the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 operate in three modes:

- Two Independent 16-Bit Timers (e.g., Timer2 and Timer3) with all 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

- They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- Time Base for Input Capture and Output Compare Modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (32-bit timer pairs, and Timer3 and Timer5 only)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed previously, except for the event trigger; this is implemented only with Timer2/3. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, and T4CON, T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1. T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word (lsw); Timer3 and Timer5 are the most significant word (msw) of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 and Timer5 interrupt flags.

A block diagram for an example 32-bit timer pair (Timer2/3 and Timer4/5) is shown in Figure 13-3.

**Note:** Only Timer2, 3, 4 and 5 can trigger a DMA data transfer.

#### 14.1 Input Capture Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 14.1.1 KEY RESOURCES

- "Input Capture" (DS70352) in the "dsPIC33/ PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### **REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1 (CONTINUED)**

- bit 3 TRIGMODE: Trigger Status Mode Select bit

- 1 = TRIGSTAT (OCxCON2<6>) is cleared when OCxRS = OCxTMR or in software

- 0 = TRIGSTAT is cleared only by software

- bit 2-0 OCM<2:0>: Output Compare x Mode Select bits

- 111 = Center-Aligned PWM mode: Output set high when OCxTMR = OCxR and set low when OCxTMR = OCxRS<sup>(1)</sup>

- 110 = Edge-Aligned PWM mode: Output set high when OCxTMR = 0 and set low when OCxTMR = OCxR<sup>(1)</sup>

- 101 = Double Compare Continuous Pulse mode: Initializes OCx pin low, toggles OCx state continuously on alternate matches of OCxR and OCxRS

- 100 = Double Compare Single-Shot mode: Initializes OCx pin low, toggles OCx state on matches of OCxR and OCxRS for one cycle

- 011 = Single Compare mode: Compare event with OCxR, continuously toggles OCx pin

- 010 = Single Compare Single-Shot mode: Initializes OCx pin high, compare event with OCxR, forces OCx pin low

- 001 = Single Compare Single-Shot mode: Initializes OCx pin low, compare event with OCxR, forces OCx pin high

- 000 = Output compare channel is disabled

- Note 1: OCxR and OCxRS are double-buffered in PWM mode only.

- 2: Each Output Compare x module (OCx) has one PTG clock source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

- PTGO4 = OC1 PTGO5 = OC2

- PTGO6 = OC3 PTGO7 = OC4

| R/W-1           | R/W-1              | R/W-0                                  | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           | R/W-0  |

|-----------------|--------------------|----------------------------------------|----------------------------|----------------------|---------------------------|-----------------|--------|

| PENH            | PENL               | POLH                                   | POLL                       | PMOD1 <sup>(1)</sup> | PMOD0 <sup>(1)</sup>      | OVRENH          | OVRENL |

| bit 15          |                    | •                                      |                            |                      |                           |                 | bit    |

| R/W-0           | R/W-0              | R/W-0                                  | R/W-0                      | R/W-0                | R/W-0                     | R/W-0           |        |

| -               | -                  | -                                      |                            | -                    | -                         | -               | R/W-0  |

| OVRDAT1         | OVRDAT0            | FLTDAT1                                | FLTDAT0                    | CLDAT1               | CLDAT0                    | SWAP            | OSYNC  |

| bit 7           |                    |                                        |                            |                      |                           |                 | bit    |

| Legend:         |                    |                                        |                            |                      |                           |                 |        |

| R = Readable    | bit                | W = Writable                           | bit                        | U = Unimpler         | nented bit, read          | l as '0'        |        |

| -n = Value at F | POR                | '1' = Bit is set                       |                            | '0' = Bit is cle     | ared                      | x = Bit is unkr | nown   |

| bit 15          |                    | xH Output Pin                          | Ownorship hit              |                      |                           |                 |        |

| bit 15          |                    | odule controls                         | •                          |                      |                           |                 |        |

|                 |                    | dule controls F                        |                            |                      |                           |                 |        |

| bit 14          |                    | L Output Pin                           | •                          |                      |                           |                 |        |

|                 | 1 = PWMx mo        | odule controls                         | PWMxL pin                  |                      |                           |                 |        |

|                 | 0 = GPIO mo        | dule controls F                        | WMxL pin                   |                      |                           |                 |        |

| bit 13          | POLH: PWM          | xH Output Pin                          | Polarity bit               |                      |                           |                 |        |

|                 |                    | oin is active-low                      |                            |                      |                           |                 |        |

|                 |                    | oin is active-hig                      | •                          |                      |                           |                 |        |

| bit 12          |                    | L Output Pin F                         | •                          |                      |                           |                 |        |

|                 |                    | in is active-low<br>in is active-hig   |                            |                      |                           |                 |        |

| bit 11-10       | PMOD<1:0>:         | PWMx # I/O F                           | in Mode bits <sup>(1</sup> | )                    |                           |                 |        |

|                 | 11 = Reserve       | ,                                      |                            |                      |                           |                 |        |

|                 |                    | /O pin pair is ir<br>/O pin pair is ir |                            |                      |                           |                 |        |

|                 |                    | O pin pair is in<br>O pin pair is ir   |                            |                      |                           |                 |        |

| bit 9           |                    | verride Enable                         | •                          |                      |                           |                 |        |

|                 |                    | <1> controls or                        |                            |                      |                           |                 |        |

|                 |                    | nerator contro                         | •                          | •                    |                           |                 |        |

| bit 8           | OVRENL: Ov         | erride Enable                          | for PWMxL Pir              | n bit                |                           |                 |        |

|                 | 1 = OVRDAT         | <0> controls or                        | utput on PWM               | xL pin               |                           |                 |        |

|                 | •                  | nerator contro                         |                            |                      |                           |                 |        |

| bit 7-6         |                    |                                        |                            |                      | de is Enabled b           |                 |        |

|                 |                    |                                        |                            |                      | by OVRDAT<<br>by OVRDAT<0 |                 |        |

| bit 5-4         | FLTDAT<1:0         | >: Data for PW                         | MxH and PWN                | ۰<br>MxL Pins if FLT | MOD is Enable             | ed bits         |        |

|                 | If Fault is active | ve, PWMxH is                           | driven to the s            | tate specified       | by FLTDAT<1>.             |                 |        |

|                 | If Fault is active | ve, PWMxL is                           | driven to the s            | tate specified b     | by FLTDAT<0>.             |                 |        |

| bit 3-2         | CLDAT<1:0>         | : Data for PWN                         | /IxH and PWM               | xL Pins if CLM       | 10D is Enabled            | bits            |        |

|                 |                    |                                        |                            | •                    | ecified by CLDA           |                 |        |

|                 |                    | IS AULIVE. F VVI                       |                            |                      |                           |                 |        |

| Note 1: The     |                    |                                        |                            |                      | enabled (PTEN             |                 |        |

# REGISTER 16-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup>

2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

# **19.2** I<sup>2</sup>C Control Registers

#### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0        | U-0                          | R/W-0                                  | R/W-1, HC                  | R/W-0                        | R/W-0            | R/W-0           | R/W-0          |

|--------------|------------------------------|----------------------------------------|----------------------------|------------------------------|------------------|-----------------|----------------|

| I2CEN        | —                            | I2CSIDL                                | SCLREL                     | IPMIEN <sup>(1)</sup>        | A10M             | DISSLW          | SMEN           |

| bit 15       |                              |                                        |                            |                              |                  |                 | bit 8          |

|              |                              |                                        |                            |                              |                  |                 |                |

| R/W-0        | R/W-0                        | R/W-0                                  | R/W-0, HC                  | R/W-0, HC                    | R/W-0, HC        | R/W-0, HC       | R/W-0, HC      |

| GCEN         | STREN                        | ACKDT                                  | ACKEN                      | RCEN                         | PEN              | RSEN            | SEN            |

| bit 7        |                              |                                        |                            |                              |                  |                 | bit 0          |

| Legend:      |                              | HC = Hardware                          | Cloarable bit              |                              |                  |                 |                |

| R = Readab   | le hit                       | W = Writable bi                        |                            | II = I Inimpler              | mented bit, rea  | d as '0'        |                |

| -n = Value a |                              | '1' = Bit is set                       | L .                        | '0' = Bit is cle             |                  | x = Bit is unk  | nown           |

|              |                              |                                        |                            |                              |                  |                 | nown           |

| bit 15       | <b>12CEN:</b> 12Cx           | Enable bit                             |                            |                              |                  |                 |                |

|              |                              | he I2Cx module                         |                            |                              |                  |                 | ;              |

|              | 0 = Disables                 | the I2Cx module;                       | all l <sup>2</sup> C™ pins | are controlled               | by port functior | ıs              |                |

| bit 14       | Unimplemen                   | ted: Read as '0'                       |                            |                              |                  |                 |                |

| bit 13       |                              | x Stop in Idle Mo                      |                            |                              |                  |                 |                |

|              |                              | ues module oper<br>s module operation  |                            |                              | dle mode         |                 |                |

| bit 12       |                              | Lx Release Conf                        |                            | _                            | ( clave)         |                 |                |

|              | 1 = Releases                 |                                        |                            |                              | slave)           |                 |                |

|              |                              | Lx clock low (clo                      | ck stretch)                |                              |                  |                 |                |

|              | If STREN = 1                 | <u>:</u>                               | -                          |                              |                  |                 |                |

|              | •                            | ., software can w                      |                            |                              |                  | ,               |                |

|              |                              | ing of every slav<br>reception. Hardw  |                            |                              |                  |                 | t every slave  |

|              | If STREN = 0                 | -                                      |                            |                              |                  |                 |                |

|              |                              | <u>.</u><br>, software can or          | nly write '1' to re        | elease clock). I             | Hardware is cle  | ar at the begir | ning of every  |

|              | -                            | te transmission.                       |                            |                              | -                | address byte re | eception.      |

| bit 11       |                              | ligent Peripheral                      |                            |                              |                  |                 |                |

|              | 1 = IPMI mod<br>0 = IPMI mod | e is enabled; all                      | addresses are              | Acknowledged                 | 1                |                 |                |

| bit 10       |                              | Slave Address b                        | i+                         |                              |                  |                 |                |

|              |                              | is a 10-bit slave                      |                            |                              |                  |                 |                |

|              |                              | is a 7-bit slave a                     |                            |                              |                  |                 |                |

| bit 9        | DISSLW: Dis                  | able Slew Rate C                       | Control bit                |                              |                  |                 |                |

|              |                              | control is disable                     |                            |                              |                  |                 |                |

|              |                              | control is enable                      |                            |                              |                  |                 |                |

| bit 8        |                              | us Input Levels b                      |                            | 0145                         | <b>c</b>         |                 |                |

|              |                              | /O pin thresholds<br>SMBus input thre  |                            | n SMBus speci                | fication         |                 |                |

| bit 7        |                              | ral Call Enable b                      |                            | ing as I <sup>2</sup> C slav | /e)              |                 |                |

|              | 1 = Enables in               | terrupt when a ge<br>all address disat | neral call addre           | -                            |                  | dule is enabled | for reception) |

|              |                              |                                        |                            |                              |                  |                 |                |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| Legend:<br>R = Readable | bit   | C = Writable b<br>W = Writable |      |        | n to clear the bit<br>mented bit, read |       |       |

|-------------------------|-------|--------------------------------|------|--------|----------------------------------------|-------|-------|

| <b></b>                 |       |                                |      |        |                                        |       |       |

| bit 7                   |       |                                |      |        |                                        |       | bit 0 |

| IVRIF                   | WAKIF | ERRIF                          | _    | FIFOIF | RBOVIF                                 | RBIF  | TBIF  |

| R/C-0                   | R/C-0 | R/C-0                          | U-0  | R/C-0  | R/C-0                                  | R/C-0 | R/C-0 |

|                         |       |                                |      |        |                                        |       |       |

| bit 15                  | •     |                                |      |        |                                        |       | bit 8 |

| _                       | —     | ТХВО                           | TXBP | RXBP   | TXWAR                                  | RXWAR | EWARN |

| U-0                     | U-0   | R-0                            | R-0  | R-0    | R-0                                    | R-0   | R-0   |

'0' = Bit is cleared

x = Bit is unknown

#### REGISTER 21-6: CxINTF: ECANx INTERRUPT FLAG REGISTER

'1' = Bit is set

| bit 15-14 | Unimplemented: Read as '0'                                                                             |

|-----------|--------------------------------------------------------------------------------------------------------|

| bit 13    | <b>TXBO:</b> Transmitter in Error State Bus Off bit                                                    |

|           | 1 = Transmitter is in Bus Off state                                                                    |

|           | 0 = Transmitter is not in Bus Off state                                                                |

| bit 12    | <b>TXBP:</b> Transmitter in Error State Bus Passive bit                                                |

|           | 1 = Transmitter is in Bus Passive state                                                                |

|           | 0 = Transmitter is not in Bus Passive state                                                            |

| bit 11    | <b>RXBP:</b> Receiver in Error State Bus Passive bit                                                   |

|           | 1 = Receiver is in Bus Passive state                                                                   |

|           | 0 = Receiver is not in Bus Passive state                                                               |

| bit 10    | TXWAR: Transmitter in Error State Warning bit                                                          |

|           | 1 = Transmitter is in Error Warning state                                                              |

| h:+ 0     | 0 = Transmitter is not in Error Warning state                                                          |

| bit 9     | RXWAR: Receiver in Error State Warning bit                                                             |

|           | 1 = Receiver is in Error Warning state<br>0 = Receiver is not in Error Warning state                   |

| bit 8     | EWARN: Transmitter or Receiver in Error State Warning bit                                              |

| bit o     | 1 = Transmitter or receiver is in Error Warning state                                                  |

|           | 0 = Transmitter or receiver is not in Error Warning state                                              |

| bit 7     | IVRIF: Invalid Message Interrupt Flag bit                                                              |

|           | 1 = Interrupt request has occurred                                                                     |

|           | 0 = Interrupt request has not occurred                                                                 |

| bit 6     | WAKIF: Bus Wake-up Activity Interrupt Flag bit                                                         |

|           | 1 = Interrupt request has occurred                                                                     |

|           | 0 = Interrupt request has not occurred                                                                 |

| bit 5     | ERRIF: Error Interrupt Flag bit (multiple sources in CxINTF<13:8>)                                     |

|           | 1 = Interrupt request has occurred                                                                     |

|           | 0 = Interrupt request has not occurred                                                                 |

| bit 4     | Unimplemented: Read as '0'                                                                             |

| bit 3     | FIFOIF: FIFO Almost Full Interrupt Flag bit                                                            |

|           | 1 = Interrupt request has occurred                                                                     |

| hit O     | 0 = Interrupt request has not occurred                                                                 |

| bit 2     | RBOVIF: RX Buffer Overflow Interrupt Flag bit                                                          |

|           | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul> |

|           |                                                                                                        |

-n = Value at POR

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| R/W-0                                        | R/W-0                                                                                                               | R/W-0                                                                                                                                           | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                     | R/W-0                        | R/W-0  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------|--------|

| F15N                                         | 1SK<1:0>                                                                                                            | F14MS                                                                                                                                           | K<1:0>                                                                                                                                               | F13MS                                                                                                                     | SK<1:0>                                                                   | F12MS                        | K<1:0> |

| bit 15                                       |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              | bit 8  |

| R/W-0                                        | R/W-0                                                                                                               | R/W-0                                                                                                                                           | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                     | R/W-0                        | R/W-0  |

|                                              | 1SK<1:0>                                                                                                            | F10MS                                                                                                                                           |                                                                                                                                                      |                                                                                                                           | K<1:0>                                                                    |                              | K<1:0> |

| bit 7                                        |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              | bit C  |

|                                              |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              |        |

| Legend:                                      |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              |        |

| R = Readabl                                  | le bit                                                                                                              | W = Writable                                                                                                                                    | bit                                                                                                                                                  | U = Unimplem                                                                                                              | nented bit, read                                                          | l as '0'                     |        |

| -n = Value at                                | t POR                                                                                                               | '1' = Bit is set                                                                                                                                |                                                                                                                                                      | '0' = Bit is clea                                                                                                         | ared                                                                      | x = Bit is unkr              | nown   |

|                                              |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              |        |

|                                              |                                                                                                                     |                                                                                                                                                 |                                                                                                                                                      |                                                                                                                           |                                                                           |                              |        |

| bit 15-14                                    | F15MSK<1:                                                                                                           | 0>: Mask Sourc                                                                                                                                  | e for Filter 15                                                                                                                                      | bits                                                                                                                      |                                                                           |                              |        |

| bit 15-14                                    | 11 = Reserv                                                                                                         | ed                                                                                                                                              |                                                                                                                                                      |                                                                                                                           |                                                                           |                              |        |

| bit 15-14                                    | 11 = Reserv<br>10 = Accepta                                                                                         | ed<br>ance Mask 2 reg                                                                                                                           | gisters contair                                                                                                                                      | n mask                                                                                                                    |                                                                           |                              |        |

| bit 15-14                                    | 11 = Reserv<br>10 = Accepta<br>01 = Accepta                                                                         | ed                                                                                                                                              | gisters contair<br>gisters contair                                                                                                                   | n mask<br>n mask                                                                                                          |                                                                           |                              |        |

| bit 15-14<br>bit 13-12                       | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                         | ed<br>ance Mask 2 reg<br>ance Mask 1 reg                                                                                                        | gisters contair<br>gisters contair<br>gisters contair                                                                                                | n mask<br>n mask<br>n mask                                                                                                | ies as bits<15∷                                                           | 14>)                         |        |

|                                              | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:                                            | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg                                                                                     | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14                                                          | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu                                                                   |                                                                           |                              |        |

| bit 13-12                                    | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0                             | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Sourc                                                         | gisters contair<br>gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13                                       | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu                                                          | les as bits<15∷                                                           | 14>)                         |        |

| bit 13-12<br>bit 11-10                       | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:<br>F13MSK<1:<br>F12MSK<1:                  | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc                             | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12                                       | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu                                       | ies as bits<15:<br>ies as bits<15:                                        | 14>)<br>14>)                 |        |

| bit 13-12<br>bit 11-10<br>bit 9-8            | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:<br>F13MSK<1:<br>F12MSK<1:<br>F11MSK<1:     | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12<br>e for Filter 11                    | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu                    | ies as bits<15∷<br>ies as bits<15∷<br>es as bits<15:1                     | 14>)<br>14>)<br>14>)         |        |

| bit 13-12<br>bit 11-10<br>bit 9-8<br>bit 7-6 | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:0<br>F13MSK<1:0<br>F11MSK<1:0<br>F11MSK<1:0 | ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br>0>: Mask Sourc<br>0>: Mask Sourc<br>0>: Mask Sourc<br>0>: Mask Sourc             | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 13<br>e for Filter 11<br>e for Filter 10 | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu | ies as bits<15:<br>ies as bits<15:<br>es as bits<15:1<br>ies as bits<15:1 | 14>)<br>14>)<br>14>)<br>14>) |        |

#### REGISTER 23-5: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER (CONTINUED)

bit 0

**CH123SA:** Channel 1, 2, 3 Positive Input Select for Sample MUXA bit In 12-bit mode (AD21B = 1), CH123SA is Unimplemented and is Read as '0':

| Value          |             | ADC Channel |         |  |  |  |

|----------------|-------------|-------------|---------|--|--|--|

| value          | CH1 CH2 CH3 |             |         |  |  |  |

| 1 <b>(2)</b>   | OA1/AN3     | OA2/AN0     | OA3/AN6 |  |  |  |

| 0 <b>(1,2)</b> | OA2/AN0     | AN1         | AN2     |  |  |  |

**Note 1:** AN0 through AN7 are repurposed when comparator and op amp functionality is enabled. See Figure 23-1 to determine how enabling a particular op amp or comparator affects selection choices for Channels 1, 2 and 3.

2: The OAx input is used if the corresponding op amp is selected (OPMODE (CMxCON<10>) = 1); otherwise, the ANx input is used.

| U-0                                                          | U-0        | U-0              | R/W-0   | R/W-0                                   | R/W-0            | R/W-0    | R/W-0   |  |

|--------------------------------------------------------------|------------|------------------|---------|-----------------------------------------|------------------|----------|---------|--|

| _                                                            | —          | —                | DWIDTH4 | DWIDTH3                                 | DWIDTH2          | DWIDTH1  | DWIDTH0 |  |

| bit 15                                                       |            |                  |         |                                         |                  |          | bit 8   |  |

|                                                              |            |                  |         |                                         |                  |          |         |  |

| U-0                                                          | U-0        | U-0              | R/W-0   | R/W-0                                   | R/W-0            | R/W-0    | R/W-0   |  |

| —                                                            | —          | —                | PLEN4   | PLEN3                                   | PLEN2            | PLEN1    | PLEN0   |  |

| bit 7                                                        |            |                  |         |                                         |                  |          | bit 0   |  |

|                                                              |            |                  |         |                                         |                  |          |         |  |

| Legend:                                                      |            |                  |         |                                         |                  |          |         |  |

| R = Readable                                                 | e bit      | W = Writable     | bit     | U = Unimpler                            | mented bit, read | l as '0' |         |  |

| -n = Value at                                                | POR        | '1' = Bit is set |         | '0' = Bit is cleared x = Bit is unknown |                  |          |         |  |

|                                                              |            |                  |         |                                         |                  |          |         |  |

| bit 15-13                                                    | Unimplemen | ted: Read as '   | 0'      |                                         |                  |          |         |  |

| bit 12-8 DWIDTH<4:0>: Data Width Select bits                 |            |                  |         |                                         |                  |          |         |  |

| These bits set the width of the data word (DWIDTH<4:0> + 1). |            |                  |         |                                         |                  |          |         |  |

| bit 7-5                                                      | Unimplemen | ted: Read as '   | 0'      |                                         |                  |          |         |  |

|                                                              |            |                  |         |                                         |                  |          |         |  |

#### REGISTER 26-2: CRCCON2: CRC CONTROL REGISTER 2

bit 4-0 **PLEN<4:0>:** Polynomial Length Select bits

These bits set the length of the polynomial (Polynomial Length = PLEN<4:0> + 1).

| DC CHARACTER  | ISTICS |      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |            |       |  |  |  |

|---------------|--------|------|-------------------------------------------------------|------------|-------|--|--|--|

| Parameter No. | Тур.   | Max. | Units                                                 | Conditions |       |  |  |  |

| DC61d         | 8      |      | μΑ                                                    | -40°C      |       |  |  |  |

| DC61a         | 10     | —    | μA                                                    | +25°C      | 2.21/ |  |  |  |

| DC61b         | 12     | —    | μA                                                    | +85°C      | 3.3V  |  |  |  |

| DC61c         | 13     | —    | μA                                                    | +125°C     |       |  |  |  |

#### TABLE 30-9: DC CHARACTERISTICS: WATCHDOG TIMER DELTA CURRENT ( $\Delta$ Iwdt)<sup>(1)</sup>

**Note 1:** The  $\triangle$ IwDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

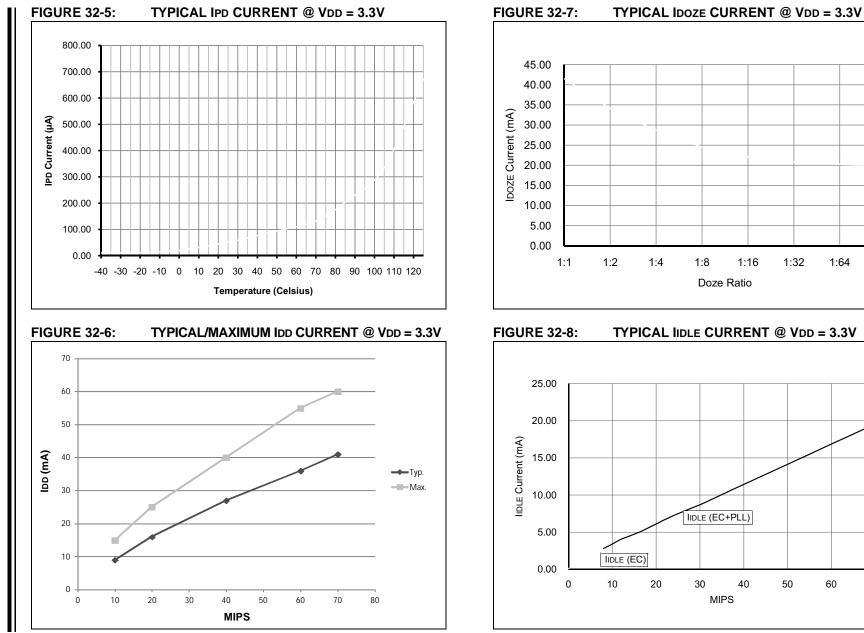

#### TABLE 30-10: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTER                        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |       |            |    |        |       |                 |  |

|-------------------------------------|-------------------------------------------------------|-------|------------|----|--------|-------|-----------------|--|

| Parameter No.                       | Doze<br>Ratio                                         | Units | Conditions |    |        |       |                 |  |

| Doze Current (IDOZE) <sup>(1)</sup> |                                                       |       |            |    |        |       |                 |  |

| DC73a <sup>(2)</sup>                | 35                                                    |       | 1:2        | mA | -40°C  | 3.3V  | Fosc = 140 MHz  |  |

| DC73g                               | 20                                                    | 30    | 1:128      | mA | -40 C  |       | FUSC - 140 MINZ |  |

| DC70a <sup>(2)</sup>                | 35                                                    | _     | 1:2        | mA | +25°C  | 3.3V  | Fosc = 140 MHz  |  |

| DC70g                               | 20                                                    | 30    | 1:128      | mA | +25 C  | 3.3V  | FUSC = 140 MITZ |  |

| DC71a <sup>(2)</sup>                | 35                                                    | _     | 1:2        | mA | 105%0  | 2.21/ |                 |  |

| DC71g                               | 20                                                    | 30    | 1:128      | mA | +85°C  | 3.3V  | Fosc = 140 MHz  |  |

| DC72a <sup>(2)</sup>                | 28                                                    | —     | 1:2        | mA | +125°C | 3.3V  | Ecco - 120 MH-  |  |

| DC72g                               | 15                                                    | 30    | 1:128      | mA | +125 C | 3.3V  | Fosc = 120 MHz  |  |

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) statement

- · JTAG is disabled

- 2: Parameter is characterized but not tested in manufacturing.

# FIGURE 30-11: TIMERQ (QEI MODULE) EXTERNAL CLOCK TIMING CHARACTERISTICS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

#### TABLE 30-30: QEI MODULE EXTERNAL CLOCK TIMING REQUIREMENTS (dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY)

| АС СНА       | ARACTERIS | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$        |                             |                                                |      |      |       |                                  |

|--------------|-----------|--------------------------------------------------------------|-----------------------------|------------------------------------------------|------|------|-------|----------------------------------|

| Param<br>No. | Symbol    | Charao                                                       | cteristic <sup>(1)</sup>    | Min.                                           | Тур. | Max. | Units | Conditions                       |

| TQ10         | TtQH      | TQCK High<br>Time                                            | Synchronous, with prescaler | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25 |      |      | ns    | Must also meet<br>Parameter TQ15 |

| TQ11         | TtQL      | TQCK Low<br>Time                                             | Synchronous, with prescaler | Greater of 12.5 + 25<br>or<br>(0.5 Tcy/N) + 25 | —    | _    | ns    | Must also meet<br>Parameter TQ15 |