Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-TQFP                                                                         |

| Supplier Device Package    | 44-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc204-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"dsPIC33/PIC24 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the dsPIC33EP64MC506 product page of the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

> In addition to parameters, features and other documentation, the resulting page provides links to the related family reference manual sections.

- "Introduction" (DS70573)

- "CPU" (DS70359)

- "Data Memory" (DS70595)

- "Program Memory" (DS70613)

- "Flash Programming" (DS70609)

- "Interrupts" (DS70600)

- "Oscillator" (DS70580)

- "Reset" (DS70602)

- "Watchdog Timer and Power-Saving Modes" (DS70615)

- "I/O Ports" (DS70598)

- "Timers" (DS70362)

- "Input Capture" (DS70352)

- "Output Compare" (DS70358)

- "High-Speed PWM" (DS70645)

- "Quadrature Encoder Interface (QEI)" (DS70601)

- "Analog-to-Digital Converter (ADC)" (DS70621)

- "UART" (DS70582)

- "Serial Peripheral Interface (SPI)" (DS70569)

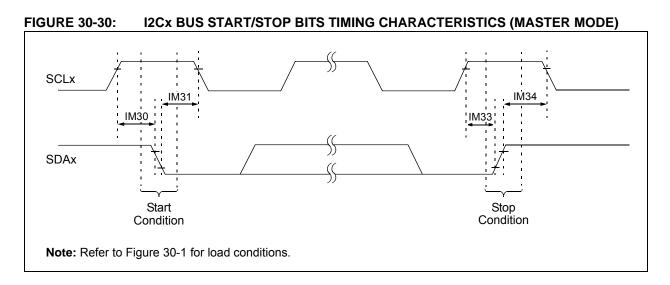

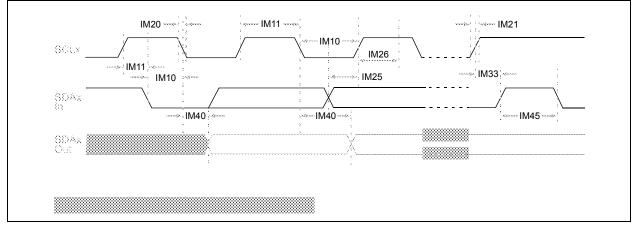

- "Inter-Integrated Circuit (I<sup>2</sup>C<sup>™</sup>)" (DS70330)

- "Enhanced Controller Area Network (ECAN™)" (DS70353)

- "Direct Memory Access (DMA)" (DS70348)

- "CodeGuard™ Security" (DS70634)

- "Programming and Diagnostics" (DS70608)

- "Op Amp/Comparator" (DS70357)

- "Programmable Cyclic Redundancy Check (CRC)" (DS70346)

- "Device Configuration" (DS70618)

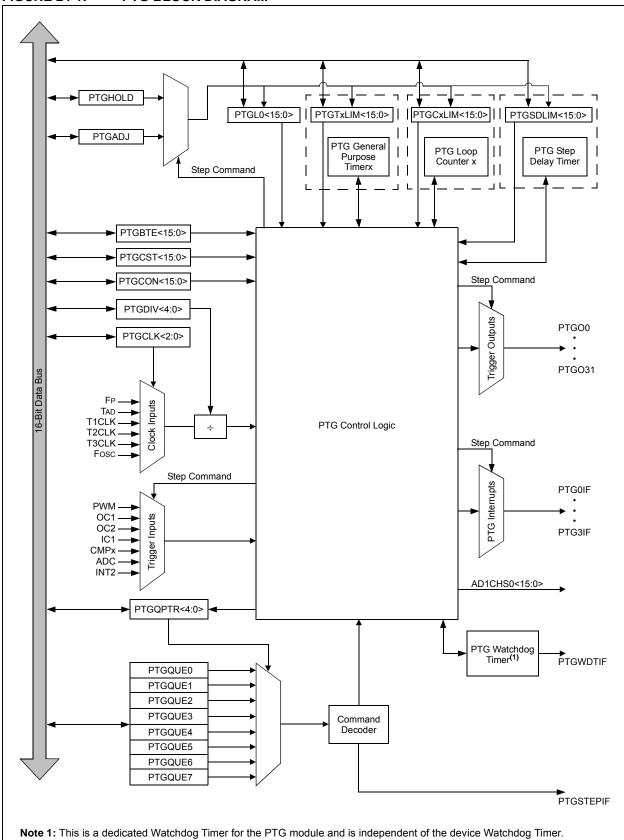

- "Peripheral Trigger Generator (PTG)" (DS70669)

- "Charge Time Measurement Unit (CTMU)" (DS70661)

| TABLE 4 | 4-31: | PER | IPHERA | L PIN S | ELECT | INPUT F | REGISTI | ER MAP | FOR ds | sPIC33E | EPXXXG | P50X D | EVICES | SONLY |  |

|---------|-------|-----|--------|---------|-------|---------|---------|--------|--------|---------|--------|--------|--------|-------|--|

|         |       |     |        |         |       |         |         |        |        |         |        |        |        |       |  |

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5 | Bit 4     | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|-----------|--------|------------|--------|-------|-------|-------|------------|-------|-----------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | —      |        |           |        | INT1R<6:0> |        |       |       | _     |            |       |           |            |       |       | _     | 0000          |

| RPINR1       | 06A2  |        | _      |           |        |            |        |       |       | _     |            |       |           | INT2R<6:0> | •     |       |       | 0000          |

| RPINR3       | 06A6  |        | _      |           |        |            |        |       | _     |       |            | ٦     | [2CKR<6:0 | >          |       |       | 0000  |               |

| RPINR7       | 06AE  |        |        | IC2R<6:0> |        |            |        |       |       | _     | IC1R<6:0>  |       |           |            |       |       |       | 0000          |

| RPINR8       | 06B0  |        |        |           |        | IC4R<6:0>  |        |       |       | _     |            |       |           | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6  |        | _      | _         | _      | _          | _      | _     | _     | _     |            |       | (         | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR18      | 06C4  |        | _      | _         | _      | _          | _      | _     | _     | _     | U1RXR<6:0> |       |           |            |       |       | 0000  |               |

| RPINR19      | 06C6  |        | _      | _         | _      | _          | _      | _     | _     | _     | U2RXR<6:0> |       |           |            |       |       |       | 0000          |

| RPINR22      | 06CC  |        |        |           | S      | CK2INR<6:0 | )>     |       |       | _     |            |       | :         | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23      | 06CE  | _      | _      | _         | —      | —          | _      | _     | —     | —     |            |       |           | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26      | 06D4  | —      | _      |           |        |            |        |       |       | —     |            |       | (         | C1RXR<6:0  | >     |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-32:** PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6      | Bit 5 | Bit 4     | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|-----------|--------|------------|--------|-------|-------|-------|------------|-------|-----------|------------|-------|-------|-------|---------------|

| RPINR0    | 06A0  | _      |        |           |        | INT1R<6:0> |        |       |       | —     |            |       |           |            |       |       | _     | 0000          |

| RPINR1    | 06A2  |        | _      | _         | _      | _          | _      | _     | _     | _     | INT2R<6:0> |       |           |            |       |       | 0000  |               |

| RPINR3    | 06A6  |        | _      | _         | _      | _          | _      | _     | _     | _     | T2CKR<6:0> |       |           |            |       |       | 0000  |               |

| RPINR7    | 06AE  |        |        |           |        | IC2R<6:0>  |        |       |       | _     |            |       |           | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8    | 06B0  |        |        | IC4R<6:0> |        |            |        |       | _     |       |            |       | IC3R<6:0> |            |       |       | 0000  |               |

| RPINR11   | 06B6  |        | _      |           |        |            |        |       | _     |       |            | (     | DCFAR<6:0 | >          |       |       | 0000  |               |

| RPINR12   | 06B8  |        |        |           |        | FLT2R<6:0> | •      |       |       | _     | FLT1R<6:0> |       |           |            |       |       | 0000  |               |

| RPINR14   | 06BC  |        |        |           | (      | QEB1R<6:0  | >      |       |       | _     |            |       | (         | QEA1R<6:0  | >     |       |       | 0000          |

| RPINR15   | 06BE  |        |        |           | Н      | OME1R<6:0  | )>     |       |       | _     |            |       | I         | NDX1R<6:0  | >     |       |       | 0000          |

| RPINR18   | 06C4  |        | _      | _         | _      | _          | _      | _     | _     | _     | U1RXR<6:0> |       |           |            |       |       | 0000  |               |

| RPINR19   | 06C6  |        | _      | _         | _      | _          | _      | _     | _     | _     | U2RXR<6:0> |       |           |            |       |       | 0000  |               |

| RPINR22   | 06CC  | _      |        |           | S      | CK2INR<6:( | )>     |       |       | —     |            |       |           | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23   | 06CE  | _      | —      | —         |        | —          | —      |       | —     | —     |            |       |           | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26   | 06D4  | _      | _      | _         |        | —          | —      |       | —     | —     |            |       | (         | C1RXR<6:0  | >     |       |       | 0000          |

| RPINR37   | 06EA  | _      |        |           | S      | YNCI1R<6:0 | )>     |       |       | —     | —          | —     | —         | —          |       |       |       | 0000          |

| RPINR38   | 06EC  | _      |        |           | D      | CMP1R<6:   | 0>     |       |       | —     | —          | —     | —         | _          |       |       |       | 0000          |

| RPINR39   | 06EE  | _      |        |           | D      | FCMP3R<6:  | 0>     |       |       | _     |            |       | D         | CMP2R<6:   | 0>    |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

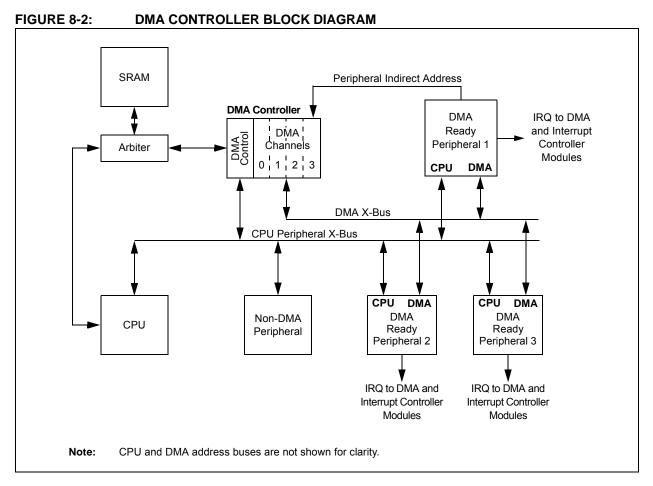

# 8.1 DMA Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 8.1.1 KEY RESOURCES

- Section 22. "Direct Memory Access (DMA)" (DS70348) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

# 8.2 DMAC Registers

Each DMAC Channel x (where x = 0 through 3) contains the following registers:

- 16-Bit DMA Channel Control register (DMAxCON)

- 16-Bit DMA Channel IRQ Select register (DMAxREQ)

- 32-Bit DMA RAM Primary Start Address register (DMAxSTA)

- 32-Bit DMA RAM Secondary Start Address register (DMAxSTB)

- 16-Bit DMA Peripheral Address register (DMAxPAD)

- 14-Bit DMA Transfer Count register (DMAxCNT)

Additional status registers (DMAPWC, DMARQC, DMAPPS, DMALCA and DSADR) are common to all DMAC channels. These status registers provide information on write and request collisions, as well as on last address and channel access information.

The interrupt flags (DMAxIF) are located in an IFSx register in the interrupt controller. The corresponding interrupt enable control bits (DMAxIE) are located in an IECx register in the interrupt controller, and the corresponding interrupt priority control bits (DMAxIP) are located in an IPCx register in the interrupt controller.

| R/W-0         | U-0                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                 | R/W-0                 | R/W-0                 | R/W-0                 | R/W-0                 |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| ROON          |                                                                                                                                                                                                                                              | ROSSLP                                                                                                                                                                                                                                                                                                                                                                                                   | ROSEL                                                                                                                                                                                                                 | RODIV3 <sup>(1)</sup> | RODIV2 <sup>(1)</sup> | RODIV1 <sup>(1)</sup> | RODIV0 <sup>(1)</sup> |

| bit 15        |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       | •                     | bit                   |

| U-0           | U-0                                                                                                                                                                                                                                          | U-0                                                                                                                                                                                                                                                                                                                                                                                                      | U-0                                                                                                                                                                                                                   | U-0                   | U-0                   | U-0                   | U-0                   |

|               | _                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                       | _                     |                       | _                     |                       |

| bit 7         |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       | bit                   |

| Legend:       |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       |                       |                       |                       |                       |

| R = Readable  | e bit                                                                                                                                                                                                                                        | W = Writable                                                                                                                                                                                                                                                                                                                                                                                             | bit                                                                                                                                                                                                                   | U = Unimpler          | nented bit, read      | l as '0'              |                       |

| -n = Value at |                                                                                                                                                                                                                                              | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       | '0' = Bit is cle      |                       | x = Bit is unkr       | iown                  |

| bit 14        | 0 = Reference                                                                                                                                                                                                                                | e oscillator outp<br>e oscillator outp<br>i <b>ted:</b> Read as '                                                                                                                                                                                                                                                                                                                                        | out is disabled                                                                                                                                                                                                       |                       | .K pin <sup>(2)</sup> |                       |                       |

| bit 13        | -                                                                                                                                                                                                                                            | ference Oscilla                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                       | en hit                |                       |                       |                       |

|               | 1 = Reference                                                                                                                                                                                                                                | e oscillator out<br>e oscillator out                                                                                                                                                                                                                                                                                                                                                                     | out continues                                                                                                                                                                                                         | to run in Sleep       |                       |                       |                       |

| bit 12        | 1 = Oscillator                                                                                                                                                                                                                               | erence Oscillato<br>crystal is used<br>lock is used as                                                                                                                                                                                                                                                                                                                                                   | as the refere                                                                                                                                                                                                         | nce clock             |                       |                       |                       |

| bit 11-8      | 1111 = Refer<br>1110 = Refer<br>1101 = Refer<br>1000 = Refer<br>1011 = Refer<br>1001 = Refer<br>1000 = Refer<br>0111 = Refer<br>0111 = Refer<br>0101 = Refer<br>0100 = Refer<br>0101 = Refer<br>0011 = Refer<br>0011 = Refer<br>0011 = Refer | Reference Os<br>rence clock divi<br>rence clock divi | ded by 32,763<br>ded by 16,384<br>ded by 8,192<br>ded by 4,096<br>ded by 2,048<br>ded by 1,024<br>ded by 512<br>ded by 512<br>ded by 256<br>ded by 128<br>ded by 64<br>ded by 32<br>ded by 16<br>ded by 8<br>ded by 4 | 8                     |                       |                       |                       |

|               | 0000 = Refer                                                                                                                                                                                                                                 | ence clock                                                                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                     |                       |                       |                       |                       |

#### REGISTER 9-5: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

- **Note 1:** The reference oscillator output must be disabled (ROON = 0) before writing to these bits.

- 2: This pin is remappable. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

# 15.2 Output Compare Control Registers

# REGISTER 15-1: OCxCON1: OUTPUT COMPARE x CONTROL REGISTER 1

| U-0           | U-0                          | R/W-0                                                                    | R/W-0             | R/W-0             | R/W-0                  | U-0              | R/W-0         |  |  |  |  |

|---------------|------------------------------|--------------------------------------------------------------------------|-------------------|-------------------|------------------------|------------------|---------------|--|--|--|--|

|               | 0-0                          | OCSIDL                                                                   | OCTSEL2           | OCTSEL1           | OCTSEL0                |                  | ENFLTB        |  |  |  |  |

| <br>bit 15    |                              | COOIDE                                                                   |                   | OUTOLLI           | OUTOLLU                |                  | bit 8         |  |  |  |  |

| Sit 10        |                              |                                                                          |                   |                   |                        |                  | bit 0         |  |  |  |  |

| R/W-0         | U-0                          | R/W-0, HSC                                                               | R/W-0, HSC        | R/W-0             | R/W-0                  | R/W-0            | R/W-0         |  |  |  |  |

| ENFLT         |                              | OCFLTB                                                                   | OCFLTA            | TRIGMODE          | OCM2                   | OCM1             | OCM0          |  |  |  |  |

| bit 7         |                              |                                                                          |                   |                   |                        |                  | bit 0         |  |  |  |  |

|               |                              |                                                                          |                   |                   |                        |                  |               |  |  |  |  |

| Legend:       |                              | HSC = Hardw                                                              | are Settable/Cl   | earable bit       |                        |                  |               |  |  |  |  |

| R = Read      | able bit                     | W = Writable I                                                           | oit               | U = Unimplem      | nented bit, read       | as '0'           |               |  |  |  |  |

| -n = Value    | e at POR                     | '1' = Bit is set                                                         |                   | '0' = Bit is clea | ared                   | x = Bit is unkn  | own           |  |  |  |  |

|               |                              |                                                                          |                   |                   |                        |                  |               |  |  |  |  |

| bit 15-14     | Unimplemen                   | ted: Read as 'o                                                          | )'                |                   |                        |                  |               |  |  |  |  |

| bit 13        | OCSIDL: Out                  | tput Compare x                                                           | Stop in Idle Mo   | de Control bit    |                        |                  |               |  |  |  |  |

|               |                              | ompare x Halts                                                           |                   |                   |                        |                  |               |  |  |  |  |

|               | •                            | compare x conti                                                          | •                 |                   | ode                    |                  |               |  |  |  |  |

| bit 12-10     |                              | )>: Output Com                                                           | pare x Clock S    | elect bits        |                        |                  |               |  |  |  |  |

|               | 111 = Periph<br>110 = Reserv | eral clock (FP)                                                          |                   |                   |                        |                  |               |  |  |  |  |

|               | 101 = PTGO                   |                                                                          |                   |                   |                        |                  |               |  |  |  |  |

|               |                              | is the clock so                                                          |                   |                   | hronous clock          | is supported)    |               |  |  |  |  |

|               |                              | is the clock so                                                          |                   |                   |                        |                  |               |  |  |  |  |

|               |                              | CLK is the clock source of the OCx<br>CLK is the clock source of the OCx |                   |                   |                        |                  |               |  |  |  |  |

|               |                              | K is the clock source of the OCx                                         |                   |                   |                        |                  |               |  |  |  |  |

| bit 9         | Unimplemen                   | mented: Read as '0'                                                      |                   |                   |                        |                  |               |  |  |  |  |

| bit 8         | ENFLTB: Fau                  | ault B Input Enable bit                                                  |                   |                   |                        |                  |               |  |  |  |  |

|               |                              | compare Fault B<br>compare Fault B                                       |                   |                   |                        |                  |               |  |  |  |  |

| bit 7         | -                            | ult A Input Enab                                                         |                   |                   |                        |                  |               |  |  |  |  |

|               | 1 = Output C                 | ompare Fault A<br>compare Fault A                                        | input (OCFA)      |                   |                        |                  |               |  |  |  |  |

| bit 6         | •                            | ted: Read as '0                                                          | • • •             |                   |                        |                  |               |  |  |  |  |

| bit 5         | OCFLTB: PW                   | M Fault B Con                                                            | dition Status bit |                   |                        |                  |               |  |  |  |  |

|               |                              | ult B condition of Fault B condition                                     |                   |                   |                        |                  |               |  |  |  |  |

| bit 4         |                              | /M Fault A Cond                                                          | •                 |                   |                        |                  |               |  |  |  |  |

|               |                              | ult A condition o                                                        |                   |                   |                        |                  |               |  |  |  |  |

| Note 1:       | OCxR and OCxF                | 29 are double h                                                          | uffered in D\\//  | / mode only       |                        |                  |               |  |  |  |  |

| Note 1.<br>2: | Each Output Cor              |                                                                          |                   | -                 | irce. See <b>Secti</b> | on 24.0 "Perin   | heral Trigger |  |  |  |  |

| 2.            | Generator (PTG               |                                                                          |                   |                   |                        | 5.1 2 7.0 1 611p |               |  |  |  |  |

|               | PTGO4 = OC1                  | -                                                                        |                   |                   |                        |                  |               |  |  |  |  |

|               | PTGO5 = OC2                  |                                                                          |                   |                   |                        |                  |               |  |  |  |  |

|               | PTGO6 = OC3<br>PTGO7 = OC4   |                                                                          |                   |                   |                        |                  |               |  |  |  |  |

|               |                              |                                                                          |                   |                   |                        |                  |               |  |  |  |  |

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

|                                                                                                          | lled low externally in order to clear and disable the fault<br>egister requires unlock sequence                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0x0000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |

| -                                                                                                        | d polarity using the IOCON1 register<br>gister requires unlock sequence                                                                                                                                                                                                                           |

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0xF000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |

| U-0                 | U-0                          | U-0              | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

|---------------------|------------------------------|------------------|---------------------------------------|----------------------|----------------------|----------------------|----------------------|

|                     | —                            | _                | DISSCK                                | DISSDO               | MODE16               | SMP                  | CKE <sup>(1)</sup>   |

| bit 15              |                              | •                |                                       | •                    | •                    | •                    | bit                  |

| R/W-0               | R/W-0                        | R/W-0            | R/W-0                                 | R/W-0                | R/W-0                | R/W-0                | R/W-0                |

| SSEN <sup>(2)</sup> | CKP                          | MSTEN            | SPRE2 <sup>(3)</sup>                  | SPRE1 <sup>(3)</sup> | SPRE0 <sup>(3)</sup> | PPRE1 <sup>(3)</sup> | PPRE0 <sup>(3)</sup> |

| bit 7               | CKF                          | WIGTEN           | SFREZ 7                               | SFREI?               | SFREU 7              | FFREN                | bit                  |

|                     |                              |                  |                                       |                      |                      |                      |                      |

| Legend:             |                              |                  |                                       |                      |                      |                      |                      |

| R = Readabl         | le bit                       | W = Writable     | bit                                   | U = Unimpler         | mented bit, read     | d as '0'             |                      |

| -n = Value at       | t POR                        | '1' = Bit is se  | t                                     | '0' = Bit is cle     | ared                 | x = Bit is unkr      | nown                 |

|                     |                              |                  |                                       |                      |                      |                      |                      |

| bit 15-13           | Unimplemen                   | ted: Read as     | 0'                                    |                      |                      |                      |                      |

| bit 12              |                              |                  | bit (SPIx Mas                         | -                    | ()                   |                      |                      |

|                     |                              | PIx clock is di  | sabled, pin fun                       | ctions as I/O        |                      |                      |                      |

| oit 11              |                              | able SDOx Pir    |                                       |                      |                      |                      |                      |

|                     |                              |                  | / the module; p                       | oin functions as     | s I/O                |                      |                      |

|                     |                              | is controlled b  |                                       |                      |                      |                      |                      |

| bit 10              | MODE16: Wo                   | ord/Byte Comn    | nunication Sele                       | ect bit              |                      |                      |                      |

|                     |                              | ication is word  | · · /                                 |                      |                      |                      |                      |

|                     |                              | ication is byte- | . ,                                   |                      |                      |                      |                      |

| bit 9               |                              | ata Input Sam    | ole Phase bit                         |                      |                      |                      |                      |

|                     | Master mode                  | -                | end of data o                         | utout time           |                      |                      |                      |

|                     |                              |                  | middle of data                        |                      |                      |                      |                      |

|                     | Slave mode:                  |                  |                                       |                      |                      |                      |                      |

|                     |                              |                  | SPIx is used i                        | n Slave mode.        |                      |                      |                      |

| bit 8               |                              | lock Edge Sele   |                                       |                      |                      |                      |                      |

|                     |                              |                  |                                       |                      |                      | lle clock state (r   |                      |

| bit 7               |                              |                  | bit (Slave mo                         |                      |                      | ve clock state (i    |                      |

|                     |                              | sused for Slav   |                                       |                      |                      |                      |                      |

|                     |                              |                  |                                       | is controlled b      | by port function     |                      |                      |

| bit 6               | CKP: Clock F                 | Polarity Select  | bit                                   |                      |                      |                      |                      |

|                     |                              |                  | nigh level; activ<br>ow level; active |                      |                      |                      |                      |

| bit 5               | MSTEN: Mas                   | ter Mode Enat    | ole bit                               |                      |                      |                      |                      |

|                     | 1 = Master m<br>0 = Slave mo |                  |                                       |                      |                      |                      |                      |

| Note 1: T           | he CKE bit is not            | used in Frame    | d SPI modes. I                        | Program this bi      | it to '0' for Fram   | ed SPI modes (       | FRMEN = 1            |

|                     | his bit must be cl           |                  |                                       |                      |                      |                      |                      |

| <b>0</b>            |                              |                  |                                       |                      |                      |                      |                      |

### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1

- **3:** Do not set both primary and secondary prescalers to the value of 1:1.

#### REGISTER 18-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(3)</sup> bit 4-2 111 = Secondary prescale 1:1 110 = Secondary prescale 2:1 000 = Secondary prescale 8:1 bit 1-0 PPRE<1:0>: Primary Prescale bits (Master mode)<sup>(3)</sup> 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- Note 1: The CKE bit is not used in Framed SPI modes. Program this bit to '0' for Framed SPI modes (FRMEN = 1).

- 2: This bit must be cleared when FRMEN = 1.

- 3: Do not set both primary and secondary prescalers to the value of 1:1.

#### 20.1 UART Helpful Tips

- 1. In multi-node, direct-connect UART networks, receive inputs UART react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UARTx module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

#### 20.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

#### 20.2.1 KEY RESOURCES

- "UART" (DS70582) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

#### FIGURE 22-1: CTMU BLOCK DIAGRAM

5: The switch connected to ADC CH0 is closed when IDISSEN (CTMUCON1<9>) = 1, and opened when IDISSEN = 0.

### 22.1 CTMU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 22.1.1 KEY RESOURCES

- "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

# REGISTER 24-8: PTGC1LIM: PTG COUNTER 1 LIMIT REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGC1L | IM<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

|        |       |       |        |          |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|        |       |       | PTGC1L | IM<7:0>  |       |       |       |

| bit 7  |       |       |        |          |       |       | bit C |

| Legena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGC1LIM<15:0>:** PTG Counter 1 Limit Register bits May be used to specify the loop count for the PTGJMPC1 Step command or as a limit register for the General Purpose Counter 1.

# REGISTER 24-9: PTGHOLD: PTG HOLD REGISTER<sup>(1)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0  | R/W-0    | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|--------|----------|-------|-------|-------|

|        |       |       | PTGHOL | _D<15:8> |       |       |       |

| bit 15 |       |       |        |          |       |       | bit 8 |

| R/W-0    | R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|----------|--------------|-------|-------|-------|-------|-------|-------|--|--|

|          | PTGHOLD<7:0> |       |       |       |       |       |       |  |  |

| bit 7 bi |              |       |       |       |       |       |       |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **PTGHOLD<15:0>:** PTG General Purpose Hold Register bits Holds user-supplied data to be copied to the PTGTxLIM, PTGCxLIM, PTGSDLIM or PTGL0 registers with the PTGCOPY command.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

#### 24.4 Step Commands and Format

#### TABLE 24-1: PTG STEP COMMAND FORMAT

| Step Command Byte: |             |             |

|--------------------|-------------|-------------|

|                    | STEPx<7:0>  |             |

| CMD<3:0>           |             | OPTION<3:0> |

| bit 7              | bit 4 bit 3 | bit 0       |

| bit 7-4 | CMD<3:0> | Step<br>Command | Command Description                                                                                                                                                                      |

|---------|----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 0000     | PTGCTRL         | Execute control command as described by OPTION<3:0>.                                                                                                                                     |

|         | 0001     | PTGADD          | Add contents of PTGADJ register to target register as described by<br>OPTION<3:0>.                                                                                                       |

|         |          | PTGCOPY         | Copy contents of PTGHOLD register to target register as described by<br>OPTION<3:0>.                                                                                                     |

|         | 001x     | PTGSTRB         | Copy the value contained in CMD<0>:OPTION<3:0> to the CH0SA<4:0> bits (AD1CHS0<4:0>).                                                                                                    |

|         | 0100     | PTGWHI          | Wait for a low-to-high edge input from the selected PTG trigger input as described by OPTION<3:0>.                                                                                       |

|         | 0101     | PTGWLO          | Wait for a high-to-low edge input from the selected PTG trigger input as described by OPTION<3:0>.                                                                                       |

|         | 0110     | Reserved        | Reserved.                                                                                                                                                                                |

|         | 0111     | PTGIRQ          | Generate individual interrupt request as described by OPTION3<:0>.                                                                                                                       |

|         | 100x     | PTGTRIG         | Generate individual trigger output as described by < <cmd<0>:OPTION&lt;3:0&gt;&gt;.</cmd<0>                                                                                              |

|         | 101x     | PTGJMP          | Copy the value indicated in < <cmd<0>:OPTION&lt;3:0&gt;&gt; to the Queue Pointer (PTGQPTR) and jump to that Step queue.</cmd<0>                                                          |

|         | 110x     | PTGJMPC0        | PTGC0 = PTGC0LIM: Increment the Queue Pointer (PTGQPTR).                                                                                                                                 |

|         |          |                 | $PTGC0 \neq PTGC0LIM$ : Increment Counter 0 (PTGC0) and copy the value indicated in < <cmd<0>:OPTION&lt;3:0&gt;&gt; to the Queue Pointer (PTGQPTR), and jump to that Step queue</cmd<0>  |

|         | 111x     | PTGJMPC1        | PTGC1 = PTGC1LIM: Increment the Queue Pointer (PTGQPTR).                                                                                                                                 |

|         |          |                 | $PTGC1 \neq PTGC1LIM$ : Increment Counter 1 (PTGC1) and copy the value indicated in < <cmd<0>:OPTION&lt;3:0&gt;&gt; to the Queue Pointer (PTGQPTR), and jump to that Step queue.</cmd<0> |

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

| Base<br>Instr<br># | Assembly<br>Mnemonic |         | Assembly Syntax             | Description                                     | # of<br>Words | # of<br>Cycles <sup>(2)</sup> | Status Flags<br>Affected |

|--------------------|----------------------|---------|-----------------------------|-------------------------------------------------|---------------|-------------------------------|--------------------------|

| 52                 | MUL                  | MUL.SS  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = signed(Wb) *<br>signed(Ws)     | 1             | 1                             | None                     |

|                    |                      | MUL.SS  | Wb,Ws,Acc <sup>(1)</sup>    | Accumulator = signed(Wb) * signed(Ws)           | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(Ws)   | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,Ws,Acc <sup>(1)</sup>    | Accumulator = signed(Wb) *<br>unsigned(Ws)      | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Acc <sup>(1)</sup> | Accumulator = signed(Wb) *<br>unsigned(lit5)    | 1             | 1                             | None                     |

|                    |                      | MUL.US  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)      | 1             | 1                             | None                     |

|                    |                      | MUL.US  | Wb,Ws,Acc <sup>(1)</sup>    | Accumulator = unsigned(Wb) *<br>signed(Ws)      | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,Ws,Wnd                   | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(Ws)    | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Acc <sup>(1)</sup> | Accumulator = unsigned(Wb) *<br>unsigned(lit5)  | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,Ws,Acc <sup>(1)</sup>    | Accumulator = unsigned(Wb) *<br>unsigned(Ws)    | 1             | 1                             | None                     |

|                    |                      | MULW.SS | Wb,Ws,Wnd                   | Wnd = signed(Wb) * signed(Ws)                   | 1             | 1                             | None                     |

|                    |                      | MULW.SU | Wb,Ws,Wnd                   | Wnd = signed(Wb) * unsigned(Ws)                 | 1             | 1                             | None                     |

|                    |                      | MULW.US | Wb,Ws,Wnd                   | Wnd = unsigned(Wb) * signed(Ws)                 | 1             | 1                             | None                     |

|                    |                      | MULW.UU | Wb,Ws,Wnd                   | Wnd = unsigned(Wb) * unsigned(Ws)               | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Wnd                | {Wnd + 1, Wnd} = signed(Wb) *<br>unsigned(lit5) | 1             | 1                             | None                     |

|                    |                      | MUL.SU  | Wb,#lit5,Wnd                | Wnd = signed(Wb) * unsigned(lit5)               | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Wnd                | {Wnd + 1, Wnd} = unsigned(Wb) * unsigned(lit5)  | 1             | 1                             | None                     |

|                    |                      | MUL.UU  | Wb,#lit5,Wnd                | Wnd = unsigned(Wb) * unsigned(lit5)             | 1             | 1                             | None                     |

|                    |                      | MUL     | f                           | W3:W2 = f * WREG                                | 1             | 1                             | None                     |

#### TABLE 28-2: INSTRUCTION SET OVERVIEW (CONTINUED)

Note 1: These instructions are available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: Read and Read-Modify-Write (e.g., bit operations and logical operations) on non-CPU SFRs incur an additional instruction cycle.

| DC CHARACTER  | ISTICS |      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |            |       |  |  |  |  |

|---------------|--------|------|-------------------------------------------------------|------------|-------|--|--|--|--|

| Parameter No. | Тур.   | Max. | Units Conditions                                      |            |       |  |  |  |  |

| DC61d         | 8      |      | μΑ                                                    | -40°C      |       |  |  |  |  |

| DC61a         | 10     | —    | μA                                                    | +25°C      | 2.21/ |  |  |  |  |

| DC61b         | 12     | —    | μA                                                    | +85°C 3.3V |       |  |  |  |  |

| DC61c         | 13     | —    | μA                                                    | +125°C     |       |  |  |  |  |

### TABLE 30-9: DC CHARACTERISTICS: WATCHDOG TIMER DELTA CURRENT ( $\Delta$ Iwdt)<sup>(1)</sup>

**Note 1:** The  $\triangle$ IwDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

#### TABLE 30-10: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTER                        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |       |       |     |            |       |                |  |  |

|-------------------------------------|-------------------------------------------------------|-------|-------|-----|------------|-------|----------------|--|--|

| Parameter No.                       | Doze<br>Ratio                                         | Units |       | Con | ditions    |       |                |  |  |

| Doze Current (IDOZE) <sup>(1)</sup> |                                                       |       |       |     |            |       |                |  |  |

| DC73a <sup>(2)</sup>                | 35                                                    |       | 1:2   | mA  | -40°C      | 3.3V  | Fosc = 140 MHz |  |  |

| DC73g                               | 20                                                    | 30    | 1:128 | mA  | -40 C      |       |                |  |  |

| DC70a <sup>(2)</sup>                | 35                                                    | _     | 1:2   | mA  | +25°C      | 3.3V  |                |  |  |

| DC70g                               | 20                                                    | 30    | 1:128 | mA  | +25 C      | 3.3V  | Fosc = 140 MHz |  |  |

| DC71a <sup>(2)</sup>                | 35                                                    | _     | 1:2   | mA  | 105%0      | 2.21/ |                |  |  |

| DC71g                               | 20                                                    | 30    | 1:128 | mA  | +85°C      | 3.3V  | Fosc = 140 MHz |  |  |

| DC72a <sup>(2)</sup>                | 28                                                    | —     | 1:2   | mA  | 125%0 2.21 |       |                |  |  |

| DC72g                               | 15                                                    | 30    | 1:128 | mA  | +125°C     | 3.3V  | Fosc = 120 MHz |  |  |

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) statement

- · JTAG is disabled

- 2: Parameter is characterized but not tested in manufacturing.

#### TABLE 30-18: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS                               |        |                                                                  | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |            |                    |  |

|--------------------------------------------------|--------|------------------------------------------------------------------|-------------------------------------------------------|------|-------|------------|--------------------|--|

| Param<br>No.                                     | Symbol | Min.                                                             | Typ. <sup>(1)</sup>                                   | Max. | Units | Conditions |                    |  |

| OS50                                             | Fplli  | PLL Voltage Controlled Oscillator<br>(VCO) Input Frequency Range | 0.8                                                   | _    | 8.0   | MHz        | ECPLL, XTPLL modes |  |

| OS51                                             | Fvco   | On-Chip VCO System Frequency                                     | 120                                                   | —    | 340   | MHz        |                    |  |

| OS52 TLOCK PLL Start-up Time (Lock Time)         |        | 0.9                                                              | 1.5                                                   | 3.1  | ms    |            |                    |  |

| OS53 DCLK CLKO Stability (Jitter) <sup>(2)</sup> |        |                                                                  | -3                                                    | 0.5  | 3     | %          |                    |  |

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: This jitter specification is based on clock cycle-by-clock cycle measurements. To get the effective jitter for individual time bases, or communication clocks used by the application, use the following formula:

$$Effective Jitter = \frac{DCLK}{\sqrt{\frac{FOSC}{Time Base or Communication Clock}}}$$

For example, if Fosc = 120 MHz and the SPIx bit rate = 10 MHz, the effective jitter is as follows:

Effective Jitter =

$$\frac{DCLK}{\sqrt{\frac{120}{10}}} = \frac{DCLK}{\sqrt{12}} = \frac{DCLK}{3.464}$$

#### TABLE 30-19: INTERNAL FRC ACCURACY

| AC CHA       | RACTERISTICS           |           | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |             |       |                                                              |                |  |

|--------------|------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|--------------------------------------------------------------|----------------|--|

| Param<br>No. | Characteristic         | Min.      | Тур.                                                                                                                                                                                                                                                                     | Max.        | Units | Conditions                                                   |                |  |

| Internal     | FRC Accuracy @ FRC Fre | equency = | : 7.37 MHz                                                                                                                                                                                                                                                               | <u>,(1)</u> |       |                                                              |                |  |

| F20a         | FRC                    | -1.5      | 0.5                                                                                                                                                                                                                                                                      | +1.5        | %     | $-40^{\circ}C \le TA \le -10^{\circ}C$                       | VDD = 3.0-3.6V |  |

|              |                        | -1        | 0.5                                                                                                                                                                                                                                                                      | +1          | %     | $-10^{\circ}C \le TA \le +85^{\circ}C \qquad VDD = 3.0-3.6V$ |                |  |

| F20b         | FRC                    | -2        | 1                                                                                                                                                                                                                                                                        | +2          | %     | $+85^{\circ}C \le TA \le +125^{\circ}C$ VDD = 3.0-3.6V       |                |  |

Note 1: Frequency is calibrated at +25°C and 3.3V. TUNx bits can be used to compensate for temperature drift.

#### TABLE 30-20: INTERNAL LPRC ACCURACY

| AC CH                       | ARACTERISTICS                                |      | <b>Operating</b><br>temperation | ure -40° | $C \le TA \le +$ | to 3.6V (unless otherw<br>85°C for Industrial<br>125°C for Extended | ise stated)    |  |

|-----------------------------|----------------------------------------------|------|---------------------------------|----------|------------------|---------------------------------------------------------------------|----------------|--|

| Param<br>No. Characteristic |                                              | Min. | Тур.                            | Max.     | Units            | Conditions                                                          |                |  |

| LPRC (                      | @ 32.768 kHz <sup>(1)</sup>                  |      |                                 |          |                  |                                                                     |                |  |

| F21a                        | LPRC                                         | -30  | —                               | +30      | %                | $-40^\circ C \le T A \le -10^\circ C$                               | VDD = 3.0-3.6V |  |

|                             | -20 — +20 % -10°C $\leq$ TA $\leq$ +85°C VDI |      | VDD = 3.0-3.6V                  |          |                  |                                                                     |                |  |

| F21b                        | LPRC                                         | -30  | _                               | +30      | %                | $+85^{\circ}C \leq TA \leq +125^{\circ}C$                           | VDD = 3.0-3.6V |  |

**Note 1:** The change of LPRC frequency as VDD changes.

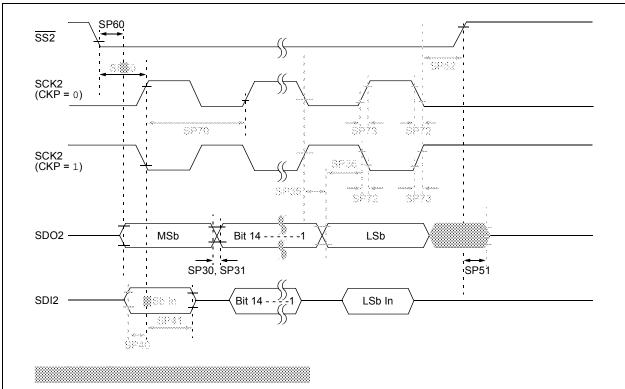

#### FIGURE 30-19: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING CHARACTERISTICS

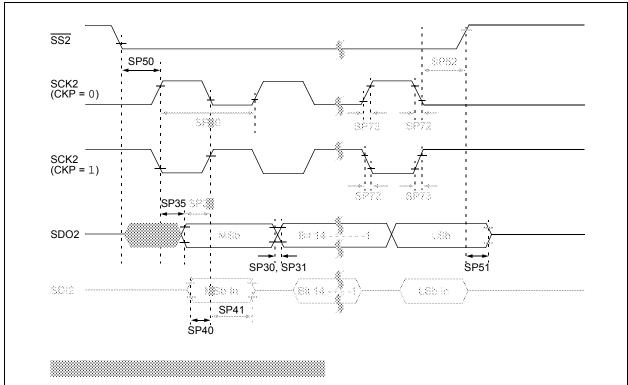

#### FIGURE 30-21: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

# TABLE 30-47:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                     |      |       |                             |