Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Becano                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 9x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

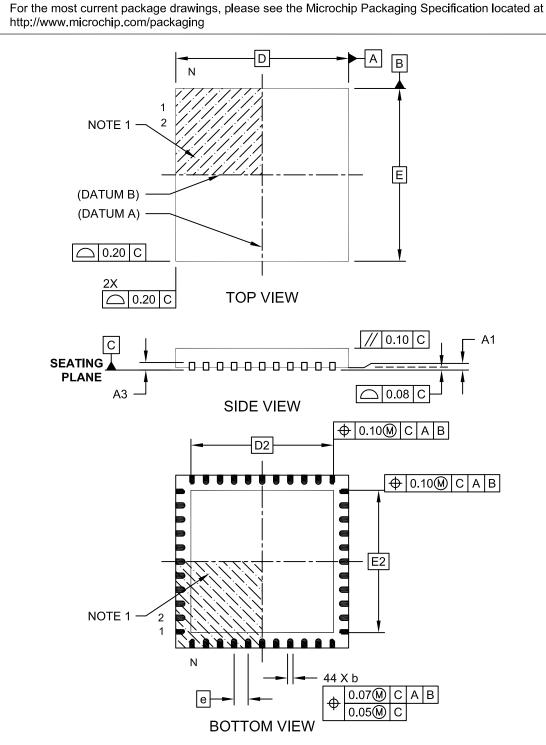

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 44-VFTLA Exposed Pad                                                            |

| Supplier Device Package    | 44-VTLA (6x6)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc204-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| R/W-0               | U-0                                                                                                           | R/W-0                                                    | R/W-0                   | R/W-0                       | R-0                       | R-0                | R-0                |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------|-----------------------------|---------------------------|--------------------|--------------------|--|--|--|

| VAR                 | —                                                                                                             | US1 <sup>(1)</sup>                                       | US0 <sup>(1)</sup>      | EDT <sup>(1,2)</sup>        | DL2 <sup>(1)</sup>        | DL1 <sup>(1)</sup> | DL0 <sup>(1)</sup> |  |  |  |

| bit 15              |                                                                                                               |                                                          |                         |                             |                           |                    | bit                |  |  |  |

| R/W-0               | R/W-0                                                                                                         | R/W-1                                                    | R/W-0                   | R/C-0                       | R-0                       | R/W-0              | R/W-0              |  |  |  |

| SATA <sup>(1)</sup> | SATB <sup>(1)</sup>                                                                                           | SATDW <sup>(1)</sup>                                     | ACCSAT <sup>(1)</sup>   | IPL3(3)                     | SFA                       | RND <sup>(1)</sup> | IF(1)              |  |  |  |

| bit 7               | I                                                                                                             |                                                          |                         |                             | I                         | 1                  | bit                |  |  |  |

| Legend:             |                                                                                                               | C = Clearable                                            | e bit                   |                             |                           |                    |                    |  |  |  |

| R = Readabl         | e bit                                                                                                         | W = Writable                                             | bit                     | U = Unimpler                | mented bit, read          | d as '0'           |                    |  |  |  |

| -n = Value at       | POR                                                                                                           | '1' = Bit is set                                         | t                       | '0' = Bit is cle            | ared                      | x = Bit is unkr    | nown               |  |  |  |

| bit 15              | 1 = Variable                                                                                                  | le Exception Pro<br>exception proce                      | essing latency          | is enabled                  |                           |                    |                    |  |  |  |

| bit 14              |                                                                                                               | nted: Read as '                                          |                         |                             |                           |                    |                    |  |  |  |

| bit 13-12           | -                                                                                                             | SP Multiply Uns                                          |                         | Control bits <sup>(1)</sup> |                           |                    |                    |  |  |  |

|                     | 01 = DSP er<br>00 = DSP er                                                                                    | ngine multiplies<br>ngine multiplies<br>ngine multiplies | are unsigned are signed |                             |                           |                    |                    |  |  |  |

| bit 11              | •                                                                                                             | O Loop Terminatives executing Dot<br>t                   |                         |                             | iteration                 |                    |                    |  |  |  |

| bit 10-8            | DL<2:0>: DO Loop Nesting Level Status bits <sup>(1)</sup><br>111 = 7 DO loops are active                      |                                                          |                         |                             |                           |                    |                    |  |  |  |

|                     | •                                                                                                             |                                                          |                         |                             |                           |                    |                    |  |  |  |

|                     | •                                                                                                             |                                                          |                         |                             |                           |                    |                    |  |  |  |

|                     | 001 = 1 DO k<br>000 = 0 DO k                                                                                  | oop is active<br>oops are active                         |                         |                             |                           |                    |                    |  |  |  |

| bit 7               | SATA: ACCA                                                                                                    | A Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |  |  |  |

|                     | <ul> <li>1 = Accumulator A saturation is enabled</li> <li>0 = Accumulator A saturation is disabled</li> </ul> |                                                          |                         |                             |                           |                    |                    |  |  |  |

| bit 6               | SATB: ACCE                                                                                                    | B Saturation En                                          | able bit <sup>(1)</sup> |                             |                           |                    |                    |  |  |  |

|                     |                                                                                                               | ator B saturatio<br>ator B saturatio                     |                         |                             |                           |                    |                    |  |  |  |

| bit 5               | SATDW: Dat                                                                                                    | ta Space Write                                           | from DSP Engi           | ne Saturation               | Enable bit <sup>(1)</sup> |                    |                    |  |  |  |

|                     |                                                                                                               | ace write satura<br>ace write satura                     |                         | I                           |                           |                    |                    |  |  |  |

| bit 4               | ACCSAT: Accumulator Saturation Mode Select bit <sup>(1)</sup>                                                 |                                                          |                         |                             |                           |                    |                    |  |  |  |

|                     |                                                                                                               | uration (super s<br>uration (normal                      | ,                       |                             |                           |                    |                    |  |  |  |

| bit 3               |                                                                                                               | nterrupt Priority                                        |                         |                             |                           |                    |                    |  |  |  |

|                     |                                                                                                               | errupt Priority Le<br>errupt Priority Le                 |                         |                             |                           |                    |                    |  |  |  |

|                     | nis bit is availabl                                                                                           |                                                          | PXXXMC20X/              | 50X and dsPl                | C33EPXXXGP                | 50X devices on     | ly.                |  |  |  |

| 2: Th               | nis bit is always                                                                                             | reau as 0.                                               |                         |                             |                           |                    |                    |  |  |  |

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER

**3:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

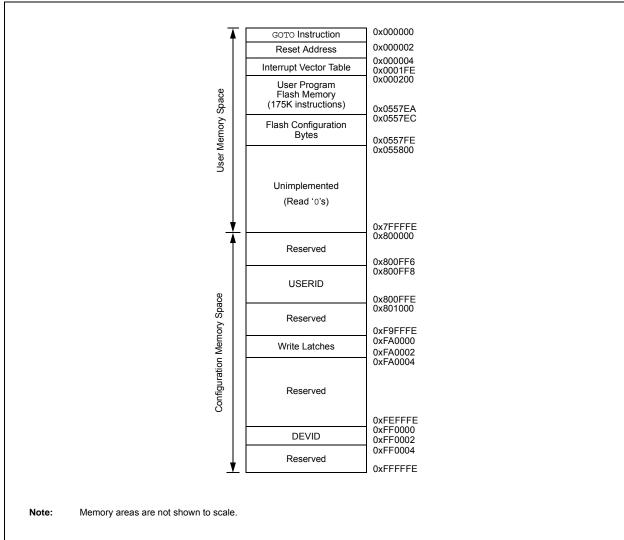

### FIGURE 4-5: PROGRAM MEMORY MAP FOR dsPIC33EP512GP50X, dsPIC33EP512MC20X/50X AND PIC24EP512GP/MC20X DEVICES

| REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6 |                                                |                            |                           |                                    |                       |                       |                       |  |

|-------------------------------------------------------------------|------------------------------------------------|----------------------------|---------------------------|------------------------------------|-----------------------|-----------------------|-----------------------|--|

| U-0                                                               | U-0                                            | U-0                        | U-0                       | U-0                                | R/W-0                 | R/W-0                 | R/W-0                 |  |

| —                                                                 | —                                              | —                          | —                         | _                                  | PWM3MD <sup>(1)</sup> | PWM2MD <sup>(1)</sup> | PWM1MD <sup>(1)</sup> |  |

| bit 15                                                            |                                                |                            |                           |                                    |                       |                       | bit 8                 |  |

|                                                                   |                                                |                            |                           |                                    |                       |                       |                       |  |

| U-0                                                               | U-0                                            | U-0                        | U-0                       | U-0                                | U-0                   | U-0                   | U-0                   |  |

|                                                                   |                                                |                            |                           |                                    |                       |                       |                       |  |

| bit 7                                                             |                                                |                            |                           |                                    |                       |                       | bit 0                 |  |

|                                                                   |                                                |                            |                           |                                    |                       |                       |                       |  |

| Legend:                                                           |                                                |                            |                           |                                    |                       |                       |                       |  |

| R = Readab                                                        | le bit                                         | W = Writable               | bit                       | U = Unimplemented bit, read as '0' |                       |                       |                       |  |

| -n = Value a                                                      | t POR                                          | '1' = Bit is set           |                           | '0' = Bit is cleared               |                       | x = Bit is unknown    |                       |  |

|                                                                   |                                                |                            |                           |                                    |                       |                       |                       |  |

| bit 15-11                                                         | Unimplement                                    | ted: Read as '             | כ'                        |                                    |                       |                       |                       |  |

| bit 10                                                            | PWM3MD: P\                                     | NM3 Module D               | isable bit <sup>(1)</sup> |                                    |                       |                       |                       |  |

|                                                                   | 1 = PWM3 mo                                    | odule is disable           | ed                        |                                    |                       |                       |                       |  |

|                                                                   | 0 = PWM3 mo                                    | odule is enable            | d                         |                                    |                       |                       |                       |  |

| bit 9                                                             | PWM2MD: P\                                     | NM2 Module D               | isable bit <sup>(1)</sup> |                                    |                       |                       |                       |  |

| 1 = PWM2 module is disabled                                       |                                                |                            | ed                        |                                    |                       |                       |                       |  |

|                                                                   | 0 = PWM2 mo                                    | odule is enable            | d                         |                                    |                       |                       |                       |  |

| bit 8                                                             | PWM1MD: PWM1 Module Disable bit <sup>(1)</sup> |                            |                           |                                    |                       |                       |                       |  |

|                                                                   |                                                | odule is disable           |                           |                                    |                       |                       |                       |  |

|                                                                   | 0 = PWM1 mo                                    | odule is enable            | d                         |                                    |                       |                       |                       |  |

| bit 7-0                                                           | Unimplement                                    | Unimplemented: Read as '0' |                           |                                    |                       |                       |                       |  |

# REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

Note 1: This bit is available on dsPIC33EPXXXMC50X/20X and PIC24EPXXXMC20X devices only.

### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

### EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

|                                                                                                          | lled low externally in order to clear and disable the fault<br>egister requires unlock sequence                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0x0000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |

| -                                                                                                        | d polarity using the IOCON1 register<br>gister requires unlock sequence                                                                                                                                                                                                                           |

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0xF000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |

| R/W-1           | R/W-1                                                                                                                                        | R/W-0                                                                                                                                                              | R/W-0           | R/W-0                | R/W-0                     | R/W-0           | R/W-0  |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|---------------------------|-----------------|--------|--|--|--|--|

| PENH            | PENL                                                                                                                                         | POLH                                                                                                                                                               | POLL            | PMOD1 <sup>(1)</sup> | PMOD0 <sup>(1)</sup>      | OVRENH          | OVRENL |  |  |  |  |

| bit 15          |                                                                                                                                              | •                                                                                                                                                                  |                 |                      |                           |                 | bit    |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                                        | R/W-0                                                                                                                                                              | R/W-0           | R/W-0                | R/W-0                     | R/W-0           |        |  |  |  |  |

| -               | -                                                                                                                                            | -                                                                                                                                                                  |                 | -                    | -                         | -               | R/W-0  |  |  |  |  |

| OVRDAT1         | OVRDAT0                                                                                                                                      | FLTDAT1                                                                                                                                                            | FLTDAT0         | CLDAT1               | CLDAT0                    | SWAP            | OSYNC  |  |  |  |  |

| bit 7           |                                                                                                                                              |                                                                                                                                                                    |                 |                      |                           |                 | bit    |  |  |  |  |

| Legend:         |                                                                                                                                              |                                                                                                                                                                    |                 |                      |                           |                 |        |  |  |  |  |

| R = Readable    | bit                                                                                                                                          | W = Writable                                                                                                                                                       | bit             | U = Unimpler         | nented bit, read          | l as '0'        |        |  |  |  |  |

| -n = Value at F | POR                                                                                                                                          | '1' = Bit is set                                                                                                                                                   |                 | '0' = Bit is cle     | ared                      | x = Bit is unkr | nown   |  |  |  |  |

| bit 15          |                                                                                                                                              | xH Output Pin                                                                                                                                                      | Ownorshin hit   |                      |                           |                 |        |  |  |  |  |

| bit 15          |                                                                                                                                              | odule controls                                                                                                                                                     | •               |                      |                           |                 |        |  |  |  |  |

|                 |                                                                                                                                              | dule controls F                                                                                                                                                    |                 |                      |                           |                 |        |  |  |  |  |

| bit 14          |                                                                                                                                              |                                                                                                                                                                    | •               |                      |                           |                 |        |  |  |  |  |

|                 | PENL: PWMxL Output Pin Ownership bit<br>1 = PWMx module controls PWMxL pin                                                                   |                                                                                                                                                                    |                 |                      |                           |                 |        |  |  |  |  |

|                 | 0 = GPIO mo                                                                                                                                  | dule controls F                                                                                                                                                    | WMxL pin        |                      |                           |                 |        |  |  |  |  |

| bit 13          | POLH: PWMxH Output Pin Polarity bit                                                                                                          |                                                                                                                                                                    |                 |                      |                           |                 |        |  |  |  |  |

|                 | 1 = PWMxH pin is active-low<br>0 = PWMxH pin is active-high                                                                                  |                                                                                                                                                                    |                 |                      |                           |                 |        |  |  |  |  |

|                 |                                                                                                                                              | -                                                                                                                                                                  | •               |                      |                           |                 |        |  |  |  |  |

| bit 12          | POLL: PWMxL Output Pin Polarity bit                                                                                                          |                                                                                                                                                                    |                 |                      |                           |                 |        |  |  |  |  |

|                 | 1 = PWMxL pin is active-low<br>0 = PWMxL pin is active-high                                                                                  |                                                                                                                                                                    |                 |                      |                           |                 |        |  |  |  |  |

| bit 11-10       | PMOD<1:0>: PWMx # I/O Pin Mode bits <sup>(1)</sup>                                                                                           |                                                                                                                                                                    |                 |                      |                           |                 |        |  |  |  |  |

|                 | 11 = Reserve                                                                                                                                 | ,                                                                                                                                                                  |                 |                      |                           |                 |        |  |  |  |  |

|                 |                                                                                                                                              | /O pin pair is ir<br>/O pin pair is ir                                                                                                                             |                 |                      |                           |                 |        |  |  |  |  |

|                 |                                                                                                                                              |                                                                                                                                                                    |                 |                      |                           |                 |        |  |  |  |  |

| bit 9           | 00 = PWMx I/O pin pair is in the Complementary Output mode<br><b>OVRENH:</b> Override Enable for PWMxH Pin bit                               |                                                                                                                                                                    |                 |                      |                           |                 |        |  |  |  |  |

|                 | 1 = OVRDAT<1> controls output on PWMxH pin                                                                                                   |                                                                                                                                                                    |                 |                      |                           |                 |        |  |  |  |  |

|                 |                                                                                                                                              | nerator contro                                                                                                                                                     | •               | •                    |                           |                 |        |  |  |  |  |

| bit 8           | OVRENL: Override Enable for PWMxL Pin bit                                                                                                    |                                                                                                                                                                    |                 |                      |                           |                 |        |  |  |  |  |

|                 | 1 = OVRDAT<0> controls output on PWMxL pin                                                                                                   |                                                                                                                                                                    |                 |                      |                           |                 |        |  |  |  |  |

|                 | •                                                                                                                                            | nerator contro                                                                                                                                                     |                 |                      |                           |                 |        |  |  |  |  |

| bit 7-6         |                                                                                                                                              |                                                                                                                                                                    |                 |                      | de is Enabled b           |                 |        |  |  |  |  |

|                 |                                                                                                                                              |                                                                                                                                                                    |                 |                      | by OVRDAT<<br>by OVRDAT<0 |                 |        |  |  |  |  |

| bit 5-4         | If OVERENL = 1, PWMxL is driven to the state specified by OVRDAT<0>.<br>FLTDAT<1:0>: Data for PWMxH and PWMxL Pins if FLTMOD is Enabled bits |                                                                                                                                                                    |                 |                      |                           |                 |        |  |  |  |  |

|                 | If Fault is active, PWMxH is driven to the state specified by FLTDAT<1>.                                                                     |                                                                                                                                                                    |                 |                      |                           |                 |        |  |  |  |  |

|                 | If Fault is active                                                                                                                           | ve, PWMxL is                                                                                                                                                       | driven to the s | tate specified b     | by FLTDAT<0>.             |                 |        |  |  |  |  |

| bit 3-2         | CLDAT<1:0>                                                                                                                                   | : Data for PWN                                                                                                                                                     | /IxH and PWM    | xL Pins if CLM       | 10D is Enabled            | bits            |        |  |  |  |  |

|                 |                                                                                                                                              | If current-limit is active, PWMxH is driven to the state specified by CLDAT<1>.<br>If current-limit is active, PWMxL is driven to the state specified by CLDAT<0>. |                 |                      |                           |                 |        |  |  |  |  |

|                 |                                                                                                                                              | IS AULIVE. F VVI                                                                                                                                                   |                 |                      |                           |                 |        |  |  |  |  |

| Note 1: The     |                                                                                                                                              |                                                                                                                                                                    |                 |                      | enabled (PTEN             |                 |        |  |  |  |  |

# REGISTER 16-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup>

2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

NOTES:

### 20.1 UART Helpful Tips

- 1. In multi-node, direct-connect UART networks, receive inputs UART react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the Idle state, the default of which is logic high (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a Start bit detection and will cause the first byte received, after the device has been initialized, to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UARTx module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock, relative to the incoming UxRX bit timing, is no longer synchronized, resulting in the first character being invalid; this is to be expected.

### 20.2 UART Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

### 20.2.1 KEY RESOURCES

- "UART" (DS70582) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

## REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0                              |       |                     |                                      |                                    |       |        |       |  |

|------------------------------------|-------|---------------------|--------------------------------------|------------------------------------|-------|--------|-------|--|

|                                    | R/W-0 | R/W-0               | R/W-0                                | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |  |

|                                    | F7BF  | °<3:0>              |                                      |                                    | F6BF  | P<3:0> |       |  |

| bit 15                             |       |                     |                                      |                                    |       |        | bit 8 |  |

| R/W-0                              | R/W-0 | R/W-0               | R/W-0                                | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |  |

|                                    | F5BF  | °<3:0>              |                                      | F4BP<3:0>                          |       |        |       |  |

| bit 7                              |       |                     |                                      |                                    |       |        | bit 0 |  |

| Legend:                            |       |                     |                                      |                                    |       |        |       |  |

| R = Readable bi                    | t     | W = Writable        | bit                                  | U = Unimplemented bit, read as '0' |       |        |       |  |

| -n = Value at POR '1' = Bit is set |       | '0' = Bit is cleare | '0' = Bit is cleared x = Bit is unkr |                                    | nown  |        |       |  |

|          | 1110 = Filter hits received in RX Buffer 14                              |

|----------|--------------------------------------------------------------------------|

|          |                                                                          |

|          | •                                                                        |

|          | 0001 = Filter hits received in RX Buffer 1                               |

|          | 0000 = Filter hits received in RX Buffer 0                               |

| bit 11-8 | F6BP<3:0>: RX Buffer Mask for Filter 6 bits (same values as bits<15:12>) |

| bit 7-4  | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits<15:12>) |

| bit 3-0  | F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits<15:12>) |

### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0                                   | R/W-0          | R/W-0  | R/W-0 |  |

|---------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------|----------------|--------|-------|--|

|               | F11BF                                              | P<3:0>                                                                                        |                                                | F10BP<3:0>                              |                |        |       |  |

| bit 15        |                                                    |                                                                                               |                                                |                                         |                |        | bit 8 |  |

| R/W-0         | R/W-0                                              | R/W-0                                                                                         | R/W-0                                          | R/W-0                                   | R/W-0          | R/W-0  | R/W-0 |  |

|               | F9BP                                               | 2<3:0>                                                                                        |                                                |                                         | F8B            | P<3:0> |       |  |

| bit 7         |                                                    |                                                                                               |                                                |                                         |                |        | bit 0 |  |

| Legend:       |                                                    |                                                                                               |                                                |                                         |                |        |       |  |

| R = Readabl   | le bit                                             | W = Writable                                                                                  | bit                                            | U = Unimplemented bit, read as '0'      |                |        |       |  |

| -n = Value at | t POR                                              | '1' = Bit is set                                                                              |                                                | '0' = Bit is cleared x = Bit is unknown |                |        | nown  |  |

| bit 15-12     | 1111 = Filter<br>1110 = Filter<br>•<br>•<br>•<br>• | RX Buffer Mar<br>hits received ir<br>hits received ir<br>hits received ir<br>hits received ir | n RX FIFO bu<br>n RX Buffer 1<br>n RX Buffer 1 | iffer<br>4                              |                |        |       |  |

| bit 11-8      | F10BP<3:0>                                         | : RX Buffer Ma                                                                                | sk for Filter 1                                | 0 bits (same val                        | ues as bits<1  | 5:12>) |       |  |

| bit 7-4       | F9BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 9 b                               | oits (same value                        | s as bits<15:1 | 2>)    |       |  |

| bit 3-0       | F8BP<3:0>:                                         | RX Buffer Mas                                                                                 | k for Filter 8 k                               | oits (same value                        | s as bits<15:1 | 2>)    |       |  |

|               |                                                    |                                                                                               |                                                |                                         |                |        |       |  |

© 2011-2013 Microchip Technology Inc.

### REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1 (CONTINUED)

| bit 7-5 | SSRC<2:0>: Sample Trigger Source Select bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | If SSRCG = 1:<br>111 = Reserved<br>110 = PTGO15 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>101 = PTGO14 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>100 = PTGO13 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>011 = PTGO12 primary trigger compare ends sampling and starts conversion <sup>(1)</sup><br>010 = PWM Generator 3 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>001 = PWM Generator 2 primary trigger compare ends sampling and starts conversion <sup>(2)</sup><br>000 = PWM Generator 1 primary trigger compare ends sampling and starts conversion <sup>(2)</sup> |

|         | If SSRCG = 0:<br>111 = Internal counter ends sampling and starts conversion (auto-convert)<br>110 = CTMU ends sampling and starts conversion<br>101 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|         | <ul> <li>101 - Reserved</li> <li>100 = Timer5 compare ends sampling and starts conversion</li> <li>011 = PWM primary Special Event Trigger ends sampling and starts conversion</li> <li>010 = Timer3 compare ends sampling and starts conversion</li> <li>001 = Active transition on the INT0 pin ends sampling and starts conversion</li> <li>000 = Clearing the Sample bit (SAMP) ends sampling and starts conversion (Manual mode)</li> </ul>                                                                                                                                                                                                                                                                        |

| bit 4   | SSRCG: Sample Trigger Source Group bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | See SSRC<2:0> for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| bit 3   | <ul> <li>SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS&lt;1:0&gt; = 01 or 1x)</li> <li><u>In 12-bit mode (AD21B = 1), SIMSAM is Unimplemented and is Read as '0':</u></li> <li>1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01)</li> <li>0 = Samples multiple channels individually in sequence</li> </ul>                                                                                                                                                                                                                                                                                              |

| bit 2   | ASAM: ADC1 Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>1 = Sampling begins immediately after the last conversion; SAMP bit is auto-set</li> <li>0 = Sampling begins when the SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| bit 1   | SAMP: ADC1 Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|         | <ul> <li>1 = ADC Sample-and-Hold amplifiers are sampling</li> <li>0 = ADC Sample-and-Hold amplifiers are holding</li> <li>If ASAM = 0, software can write '1' to begin sampling. Automatically set by hardware if ASAM = 1. If SSRC&lt;2:0&gt; = 000, software can write '0' to end sampling and start conversion. If SSRC&lt;2:0&gt; ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>                                                                                                                                                                                                                                                                                         |

| bit 0   | DONE: ADC1 Conversion Status bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = ADC conversion cycle has completed</li> <li>0 = ADC conversion has not started or is in progress</li> <li>Automatically set by hardware when the ADC conversion is complete. Software can write '0' to clear the DONE status bit (software is not allowed to write '1'). Clearing this bit does NOT affect any operation in progress. Automatically cleared by hardware at the start of a new conversion.</li> </ul>                                                                                                                                                                                                                                                                                       |

| Note 1: | See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for information on this selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

- 2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- **3:** Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

| R/W-0      | R/W-0                                                                  | R/W-0                                                                                                                                                                | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |  |  |  |  |

|------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------------------------|-----------------|--------|--|--|--|--|

| ADCTS4     | ADCTS3                                                                 | ADCTS2                                                                                                                                                               | ADCTS1         | IC4TSS           | IC3TSS                       | IC2TSS          | IC1TSS |  |  |  |  |

| bit 15     |                                                                        |                                                                                                                                                                      |                |                  |                              |                 | bit 8  |  |  |  |  |

| R/W-0      | R/W-0                                                                  | R/W-0                                                                                                                                                                | R/W-0          | R/W-0            | R/W-0                        | R/W-0           | R/W-0  |  |  |  |  |

| OC4CS      |                                                                        | OC2CS                                                                                                                                                                | OC1CS          | OC4TSS           | OC3TSS                       | OC2TSS          | OC1TSS |  |  |  |  |

| bit 7      |                                                                        | 00100                                                                                                                                                                |                |                  |                              |                 | bit (  |  |  |  |  |

| Legend:    |                                                                        |                                                                                                                                                                      |                |                  |                              |                 |        |  |  |  |  |

| R = Reada  | ble bit                                                                | W = Writable                                                                                                                                                         | bit            | U = Unimplei     | mented bit, read             | l as '0'        |        |  |  |  |  |

| -n = Value | at POR                                                                 | '1' = Bit is set                                                                                                                                                     |                | '0' = Bit is cle |                              | x = Bit is unkr | nown   |  |  |  |  |

|            |                                                                        |                                                                                                                                                                      |                |                  |                              |                 |        |  |  |  |  |

| bit 15     | ADCTS4: Sa                                                             | mple Trigger P                                                                                                                                                       | TGO15 for AE   | OC bit           |                              |                 |        |  |  |  |  |

|            | 1 = Generate                                                           | es Trigger wher                                                                                                                                                      | the broadcas   | t command is     | executed                     |                 |        |  |  |  |  |

|            | 0 = Does not                                                           | generate Trigg                                                                                                                                                       | er when the b  | roadcast com     | mand is execute              | ed              |        |  |  |  |  |

| bit 14     |                                                                        | mple Trigger P                                                                                                                                                       |                |                  |                              |                 |        |  |  |  |  |

|            |                                                                        | es Trigger wher                                                                                                                                                      |                |                  |                              | al              |        |  |  |  |  |

| bit 13     |                                                                        |                                                                                                                                                                      |                |                  | mand is execute              | a               |        |  |  |  |  |

| DIE 13     |                                                                        | ADCTS2: Sample Trigger PTGO13 for ADC bit<br>1 = Generates Trigger when the broadcast command is executed                                                            |                |                  |                              |                 |        |  |  |  |  |

|            |                                                                        |                                                                                                                                                                      |                |                  | mand is execute              | ed              |        |  |  |  |  |

| bit 12     |                                                                        | ADCTS1: Sample Trigger PTGO12 for ADC bit                                                                                                                            |                |                  |                              |                 |        |  |  |  |  |

|            | 1 = Generate                                                           | 1 = Generates Trigger when the broadcast command is executed                                                                                                         |                |                  |                              |                 |        |  |  |  |  |

|            |                                                                        |                                                                                                                                                                      |                |                  | mand is execute              | ed              |        |  |  |  |  |

| bit 11     | -                                                                      | IC4TSS: Trigger/Synchronization Source for IC4 bit                                                                                                                   |                |                  |                              |                 |        |  |  |  |  |

|            |                                                                        |                                                                                                                                                                      |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |

| bit 10     | IC3TSS: Trig                                                           | IC3TSS: Trigger/Synchronization Source for IC3 bit                                                                                                                   |                |                  |                              |                 |        |  |  |  |  |

|            |                                                                        |                                                                                                                                                                      |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |

| bit 9      | IC2TSS: Trig                                                           | IC2TSS: Trigger/Synchronization Source for IC2 bit                                                                                                                   |                |                  |                              |                 |        |  |  |  |  |

|            |                                                                        |                                                                                                                                                                      |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |

| bit 8      |                                                                        | <ul> <li>0 = Does not generate Trigger/Synchronization when the broadcast command is executed</li> <li>IC1TSS: Trigger/Synchronization Source for IC1 bit</li> </ul> |                |                  |                              |                 |        |  |  |  |  |

|            |                                                                        |                                                                                                                                                                      |                |                  | ast command is broadcast con |                 | ited   |  |  |  |  |

| bit 7      |                                                                        | <ul> <li>Does not generate Trigger/Synchronization when the broadcast command is executed</li> <li>OC4CS: Clock Source for OC4 bit</li> </ul>                        |                |                  |                              |                 |        |  |  |  |  |

|            |                                                                        | es clock pulse v<br>generate clock                                                                                                                                   |                |                  |                              | cuted           |        |  |  |  |  |

| bit 6      |                                                                        | <ul> <li>0 = Does not generate clock pulse when the broadcast command is executed</li> <li>OC3CS: Clock Source for OC3 bit</li> </ul>                                |                |                  |                              |                 |        |  |  |  |  |

|            |                                                                        | es clock pulse v<br>aenerate clock                                                                                                                                   |                |                  | d is executed command is exe | cuted           |        |  |  |  |  |

| bit 5      |                                                                        | ck Source for C                                                                                                                                                      | -              |                  |                              |                 |        |  |  |  |  |

|            | 1 = Generate                                                           | es clock pulse v                                                                                                                                                     | when the broad |                  | d is executed command is exe | cuted           |        |  |  |  |  |

|            | This register is rea<br>PTGSTRT = 1).                                  | -                                                                                                                                                                    |                |                  |                              |                 | and    |  |  |  |  |

|            | ,                                                                      | lv used with the                                                                                                                                                     | PTGCTRI. OI    | PTION = 1111     | Step command                 | L               |        |  |  |  |  |

|            | his register is only used with the PTGCTRL OPTION = 1111 Step command. |                                                                                                                                                                      |                |                  |                              |                 |        |  |  |  |  |

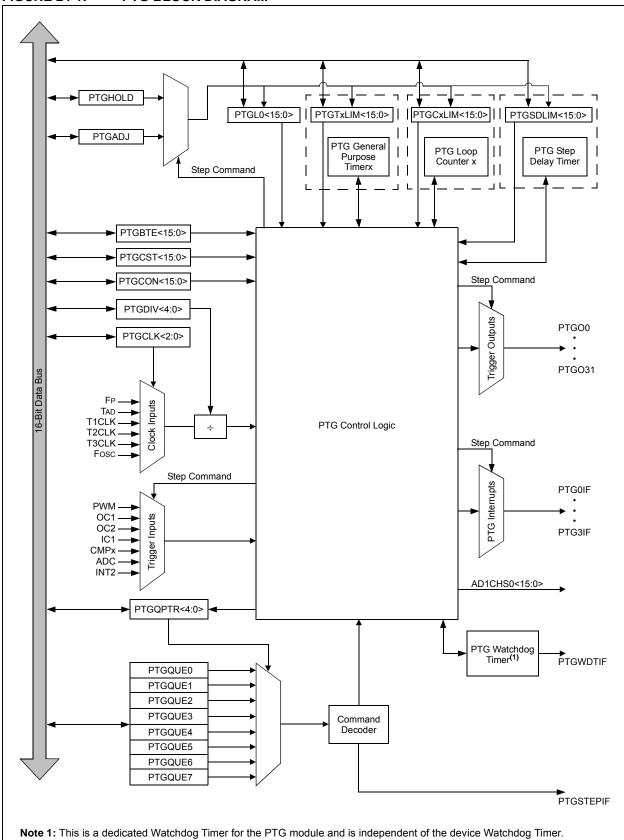

# **REGISTER 24-3: PTGBTE: PTG BROADCAST TRIGGER ENABLE REGISTER**<sup>(1,2)</sup>

# REGISTER 24-10: PTGADJ: PTG ADJUST REGISTER<sup>(1)</sup>

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|------------------------------------|-------|-------|-------|-----------------------------------------|-------|-------|-------|--|

|                                    |       |       | PTGA  | DJ<15:8>                                |       |       |       |  |

| bit 15                             |       |       |       |                                         |       |       | bit 8 |  |

|                                    |       |       |       |                                         |       |       |       |  |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0 | R/W-0                                   | R/W-0 | R/W-0 | R/W-0 |  |

|                                    |       |       | PTGA  | DJ<7:0>                                 |       |       |       |  |

| bit 7                              |       |       |       |                                         |       |       | bit 0 |  |

|                                    |       |       |       |                                         |       |       |       |  |

| Legend:                            |       |       |       |                                         |       |       |       |  |

| R = Readable bit W = Writable bit  |       |       |       | U = Unimplemented bit, read as '0'      |       |       |       |  |