Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I²C, IrDA, LINbus, QEI, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 44-QFN (8×8)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc204t-e-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name <sup>(4)</sup>       | Pin<br>Type | Buffer<br>Type | PPS     | Description                                                                      |  |  |  |  |  |  |  |

|-------------------------------|-------------|----------------|---------|----------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| C1IN1-                        | I           | Analog         | No      | Op Amp/Comparator 1 Negative Input 1.                                            |  |  |  |  |  |  |  |

| C1IN2-                        | I           | Analog         | No      | Comparator 1 Negative Input 2.                                                   |  |  |  |  |  |  |  |

| C1IN1+                        | I           | Analog         | No      | Op Amp/Comparator 1 Positive Input 1.                                            |  |  |  |  |  |  |  |

| OA1OUT                        | 0           | Analog         | No      | Op Amp 1 output.                                                                 |  |  |  |  |  |  |  |

| C1OUT                         | 0           | —              | Yes     | Comparator 1 output.                                                             |  |  |  |  |  |  |  |

| C2IN1-                        | I           | Analog         | No      | Op Amp/Comparator 2 Negative Input 1.                                            |  |  |  |  |  |  |  |

| C2IN2-                        | I           | Analog         | No      | Comparator 2 Negative Input 2.                                                   |  |  |  |  |  |  |  |

| C2IN1+                        | I           | Analog         | No      | Op Amp/Comparator 2 Positive Input 1.                                            |  |  |  |  |  |  |  |

| OA2OUT                        | 0           | Analog         | No      | Op Amp 2 output.                                                                 |  |  |  |  |  |  |  |

| C2OUT                         | 0           |                | Yes     | Comparator 2 output.                                                             |  |  |  |  |  |  |  |

| C3IN1-                        | I           | Analog         | No      | Op Amp/Comparator 3 Negative Input 1.                                            |  |  |  |  |  |  |  |

| C3IN2-                        | I           | Analog         | No      | Comparator 3 Negative Input 2.                                                   |  |  |  |  |  |  |  |

| C3IN1+                        | I           | Analog         | No      | Op Amp/Comparator 3 Positive Input 1.                                            |  |  |  |  |  |  |  |

| OA3OUT                        | 0           | Analog         | No      | Op Amp 3 output.                                                                 |  |  |  |  |  |  |  |

| C3OUT                         | 0           |                | Yes     | Comparator 3 output.                                                             |  |  |  |  |  |  |  |

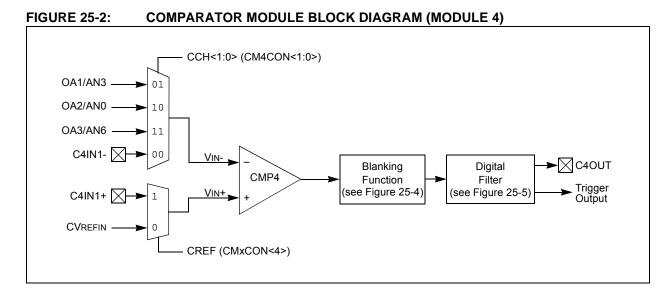

| C4IN1-                        | I.          | Analog         | No      | Comparator 4 Negative Input 1.                                                   |  |  |  |  |  |  |  |

| C4IN1+                        | I.          | Analog         | No      | Comparator 4 Positive Input 1.                                                   |  |  |  |  |  |  |  |

| C4OUT                         | 0           |                | Yes     | Comparator 4 output.                                                             |  |  |  |  |  |  |  |

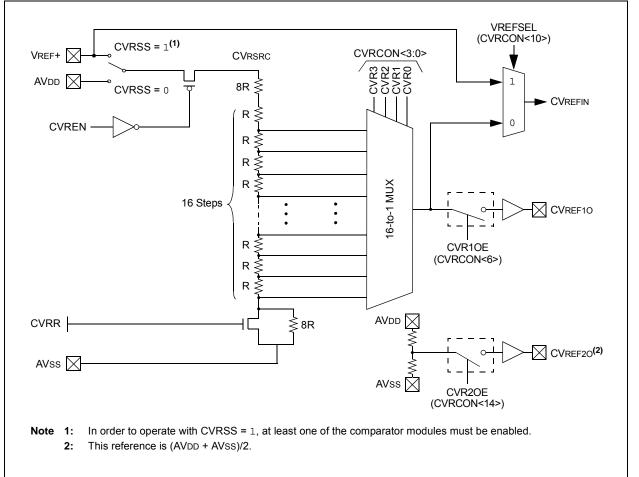

| CVREF10                       | 0           | Analog         | No      | Op amp/comparator voltage reference output.                                      |  |  |  |  |  |  |  |

| CVREF20                       | 0           | Analog         | No      | Op amp/comparator voltage reference divided by 2 output.                         |  |  |  |  |  |  |  |

| PGED1                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 1.                  |  |  |  |  |  |  |  |

| PGEC1                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 1.               |  |  |  |  |  |  |  |

| PGED2                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 2.                  |  |  |  |  |  |  |  |

| PGEC2                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 2.               |  |  |  |  |  |  |  |

| PGED3                         | I/O         | ST             | No      | Data I/O pin for Programming/Debugging Communication Channel 3.                  |  |  |  |  |  |  |  |

| PGEC3                         | I           | ST             | No      | Clock input pin for Programming/Debugging Communication Channel 3.               |  |  |  |  |  |  |  |

| MCLR                          | I/P         | ST             | No      | Master Clear (Reset) input. This pin is an active-low Reset to the device.       |  |  |  |  |  |  |  |

| AVDD                          | Р           | Р              | No      | Positive supply for analog modules. This pin must be connected at all times.     |  |  |  |  |  |  |  |

| AVss                          | Р           | Р              | No      | Ground reference for analog modules. This pin must be connected at all times.    |  |  |  |  |  |  |  |

| Vdd                           | Р           |                | No      |                                                                                  |  |  |  |  |  |  |  |

| VCAP                          | Р           |                | No      | CPU logic filter capacitor connection.                                           |  |  |  |  |  |  |  |

| Vss                           | Р           |                | No      |                                                                                  |  |  |  |  |  |  |  |

| VREF+                         | I           | Analog         | No      | Analog voltage reference (high) input.                                           |  |  |  |  |  |  |  |

| VREF-                         | Ι           | Analog         | No      |                                                                                  |  |  |  |  |  |  |  |

| Legend: CMOS = C<br>ST = Schn | nitt Trigg  | jer input v    | with CI | or output  Analog = Analog input  P = Power    MOS levels  O = Output  I = Input |  |  |  |  |  |  |  |

Note 1: This pin is available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

2: This pin is available on dsPIC33EPXXXGP/MC50X devices only.

PPS = Peripheral Pin Select

3: This is the default Fault on Reset for dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices. See Section 16.0 "High-Speed PWM Module (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X Devices Only)" for more information.

TTL = TTL input buffer

4: Not all pins are available in all packages variants. See the "Pin Diagrams" section for pin availability.

**5:** There is an internal pull-up resistor connected to the TMS pin when the JTAG interface is active. See the JTAGEN bit field in Table 27-2.

| IADLE 4   | LE 4-10: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 4 REGISTER MAP |        |                                                                      |          |        |           |        |       |             |             |              |        |        |          |           |          |       |               |

|-----------|-----------------------------------------------------------------|--------|----------------------------------------------------------------------|----------|--------|-----------|--------|-------|-------------|-------------|--------------|--------|--------|----------|-----------|----------|-------|---------------|

| File Name | Addr.                                                           | Bit 15 | Bit 14                                                               | Bit 13   | Bit 12 | Bit 11    | Bit 10 | Bit 9 | Bit 8       | Bit 7       | Bit 6        | Bit 5  | Bit 4  | Bit 3    | Bit 2     | Bit 1    | Bit 0 | All<br>Resets |

| OC1CON1   | 0900                                                            | —      | -                                                                    | OCSIDL   | C      | CTSEL<2:0 | )>     | —     | ENFLTB      | ENFLTA      | —            | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC1CON2   | 0902                                                            | FLTMD  | D FLTOUT FLTTRIEN OCINV OC32 OCTRIG TRIGSTAT OCTRIS SYNCSEL<4:0> 000 |          |        |           |        |       |             |             |              | 000C   |        |          |           |          |       |               |

| OC1RS     | 0904                                                            |        | Output Compare 1 Secondary Register                                  |          |        |           |        |       |             |             |              | xxxx   |        |          |           |          |       |               |

| OC1R      | 0906                                                            |        | Output Compare 1 Register                                            |          |        |           |        |       |             |             |              | xxxx   |        |          |           |          |       |               |

| OC1TMR    | 0908                                                            |        | Timer Value 1 Register                                               |          |        |           |        |       |             |             |              | xxxx   |        |          |           |          |       |               |

| OC2CON1   | 090A                                                            | _      | —                                                                    | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC2CON2   | 090C                                                            | FLTMD  | FLTOUT                                                               | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC2RS     | 090E                                                            |        | Output Compare 2 Secondary Register xxxx                             |          |        |           |        |       |             |             |              | xxxx   |        |          |           |          |       |               |

| OC2R      | 0910                                                            |        | Output Compare 2 Register                                            |          |        |           |        |       |             |             | xxxx         |        |        |          |           |          |       |               |

| OC2TMR    | 0912                                                            |        |                                                                      |          |        |           |        |       | Timer V     | alue 2 Regi | ster         |        |        |          |           |          |       | xxxx          |

| OC3CON1   | 0914                                                            | _      | —                                                                    | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC3CON2   | 0916                                                            | FLTMD  | FLTOUT                                                               | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC3RS     | 0918                                                            |        |                                                                      |          |        |           |        | Outp  | out Compare | e 3 Seconda | ary Register |        |        |          |           |          |       | xxxx          |

| OC3R      | 091A                                                            |        |                                                                      |          |        |           |        |       | Output Co   | mpare 3 Re  | gister       |        |        |          |           |          |       | xxxx          |

| OC3TMR    | 091C                                                            |        |                                                                      |          |        |           |        |       | Timer V     | alue 3 Regi | ster         |        |        |          |           |          |       | xxxx          |

| OC4CON1   | 091E                                                            | _      | —                                                                    | OCSIDL   | 0      | CTSEL<2:0 | )>     | _     | ENFLTB      | ENFLTA      | _            | OCFLTB | OCFLTA | TRIGMODE |           | OCM<2:0> |       | 0000          |

| OC4CON2   | 0920                                                            | FLTMD  | FLTOUT                                                               | FLTTRIEN | OCINV  | _         | _      | _     | OC32        | OCTRIG      | TRIGSTAT     | OCTRIS |        | SYN      | NCSEL<4:0 | >        |       | 000C          |

| OC4RS     | 0922                                                            |        |                                                                      |          |        |           |        | Outp  | out Compare | e 4 Seconda | ary Register |        |        |          |           |          |       | xxxx          |

| OC4R      | 0924                                                            |        | Output Compare 4 Register xxx                                        |          |        |           |        |       |             |             | xxxx         |        |        |          |           |          |       |               |

| OC4TMR    | 0926                                                            |        |                                                                      |          |        |           |        |       | Timer V     | alue 4 Regi | ster         |        |        |          |           |          |       | xxxx          |

# TABLE 4-10: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 4 REGISTER MAP

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-19: SPI1 AND SPI2 REGISTER MAP

| SFR Name | Addr. | Bit 15                                    | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10                                                 | Bit 9      | Bit 8        | Bit 7       | Bit 6      | Bit 5  | Bit 4     | Bit 3      | Bit 2     | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------|-------------------------------------------|--------|---------|--------|--------|--------------------------------------------------------|------------|--------------|-------------|------------|--------|-----------|------------|-----------|--------|--------|---------------|

| SPI1STAT | 0240  | SPIEN                                     | _      | SPISIDL | _      | _      | 5                                                      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |           | SISEL<2:0> |           | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242  | _                                         | _      | _       | DISSCK | DISSDO | MODE16                                                 | SMP        | CKE          | SSEN        | CKP        | MSTEN  | SPRE<2:0> |            | PPRE<1:0> |        | 0000   |               |

| SPI1CON2 | 0244  | FRMEN                                     | SPIFSD | FRMPOL  | _      | _      |                                                        | _          | _            | —           | _          | _      | _         | _          | _         | FRMDLY | SPIBEN | 0000          |

| SPI1BUF  | 0248  |                                           |        |         |        |        |                                                        | SPI1 Tra   | insmit and R | eceive Buff | er Registe | r      |           |            |           |        |        | 0000          |

| SPI2STAT | 0260  | SPIEN                                     | _      | SPISIDL | _      | _      | ŝ                                                      | SPIBEC<2:0 | >            | SRMPT       | SPIROV     | SRXMPT |           | SISEL<2:0> |           | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262  | _                                         | _      | _       | DISSCK | DISSDO | SSDO MODE16 SMP CKE SSEN CKP MSTEN SPRE<2:0> PPRE<1:0> |            |              |             |            |        | 0000      |            |           |        |        |               |

| SPI2CON2 | 0264  | FRMEN                                     | SPIFSD | FRMPOL  | _      | _      |                                                        | _          | _            | —           | _          | _      | _         | _          | _         | FRMDLY | SPIBEN | 0000          |

| SPI2BUF  | 0268  | SPI2 Transmit and Receive Buffer Register |        |         |        |        |                                                        |            |              |             | 0000       |        |           |            |           |        |        |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

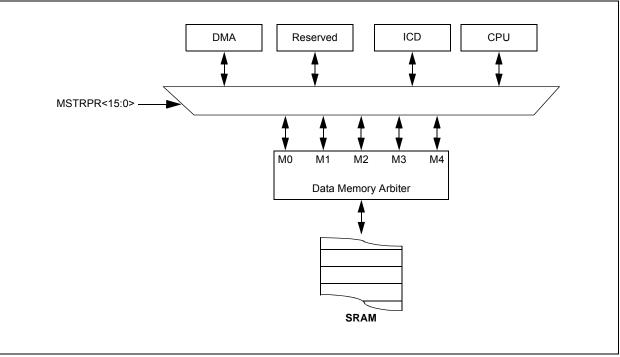

# 4.4.3 DATA MEMORY ARBITRATION AND BUS MASTER PRIORITY

EDS accesses from bus masters in the system are arbitrated.

The arbiter for data memory (including EDS) arbitrates between the CPU, the DMA and the ICD module. In the event of coincidental access to a bus by the bus masters, the arbiter determines which bus master access has the highest priority. The other bus masters are suspended and processed after the access of the bus by the bus master with the highest priority.

By default, the CPU is Bus Master 0 (M0) with the highest priority and the ICD is Bus Master 4 (M4) with the lowest priority. The remaining bus master (DMA Controller) is allocated to M3 (M1 and M2 are reserved and cannot be used). The user application may raise or lower the priority of the DMA Controller to be above that of the CPU by setting the appropriate bits in the EDS Bus Master Priority Control (MSTRPR) register. All bus masters with raised priorities will maintain the same priority relationship relative to each other (i.e., M1 being highest and M3 being lowest, with M2 in between). Also, all the bus masters with priorities below

# FIGURE 4-18: ARBITER ARCHITECTURE

that of the CPU maintain the same priority relationship relative to each other. The priority schemes for bus masters with different MSTRPR values are tabulated in Table 4-62.

This bus master priority control allows the user application to manipulate the real-time response of the system, either statically during initialization or dynamically in response to real-time events.

| TABLE 4-62: | DATA MEMORY BUS  |

|-------------|------------------|

|             | ARBITER PRIORITY |

| Drierity     | MSTRPR<15:0> Bit Setting <sup>(1)</sup> |          |  |  |  |  |  |

|--------------|-----------------------------------------|----------|--|--|--|--|--|

| Priority     | 0x0000                                  | 0x0020   |  |  |  |  |  |

| M0 (highest) | CPU                                     | DMA      |  |  |  |  |  |

| M1           | Reserved                                | CPU      |  |  |  |  |  |

| M2           | Reserved                                | Reserved |  |  |  |  |  |

| M3           | DMA                                     | Reserved |  |  |  |  |  |

| M4 (lowest)  | ICD                                     | ICD      |  |  |  |  |  |

**Note 1:** All other values of MSTRPR<15:0> are reserved.

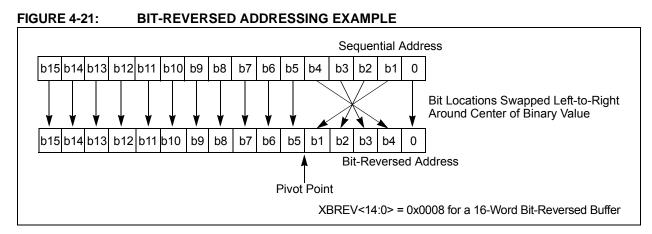

# TABLE 4-64: BIT-REVERSED ADDRESSING SEQUENCE (16-ENTRY)

|    |    | Norma | al Addres | SS      | Bit-Reversed Address |    |    |    |         |  |  |

|----|----|-------|-----------|---------|----------------------|----|----|----|---------|--|--|

| A3 | A2 | A1    | A0        | Decimal | A3                   | A2 | A1 | A0 | Decimal |  |  |

| 0  | 0  | 0     | 0         | 0       | 0                    | 0  | 0  | 0  | 0       |  |  |

| 0  | 0  | 0     | 1         | 1       | 1                    | 0  | 0  | 0  | 8       |  |  |

| 0  | 0  | 1     | 0         | 2       | 0                    | 1  | 0  | 0  | 4       |  |  |

| 0  | 0  | 1     | 1         | 3       | 1                    | 1  | 0  | 0  | 12      |  |  |

| 0  | 1  | 0     | 0         | 4       | 0                    | 0  | 1  | 0  | 2       |  |  |

| 0  | 1  | 0     | 1         | 5       | 1                    | 0  | 1  | 0  | 10      |  |  |

| 0  | 1  | 1     | 0         | 6       | 0                    | 1  | 1  | 0  | 6       |  |  |

| 0  | 1  | 1     | 1         | 7       | 1                    | 1  | 1  | 0  | 14      |  |  |

| 1  | 0  | 0     | 0         | 8       | 0                    | 0  | 0  | 1  | 1       |  |  |

| 1  | 0  | 0     | 1         | 9       | 1                    | 0  | 0  | 1  | 9       |  |  |

| 1  | 0  | 1     | 0         | 10      | 0                    | 1  | 0  | 1  | 5       |  |  |

| 1  | 0  | 1     | 1         | 11      | 1                    | 1  | 0  | 1  | 13      |  |  |

| 1  | 1  | 0     | 0         | 12      | 0                    | 0  | 1  | 1  | 3       |  |  |

| 1  | 1  | 0     | 1         | 13      | 1                    | 0  | 1  | 1  | 11      |  |  |

| 1  | 1  | 1     | 0         | 14      | 0                    | 1  | 1  | 1  | 7       |  |  |

| 1  | 1  | 1     | 1         | 15      | 1                    | 1  | 1  | 1  | 15      |  |  |

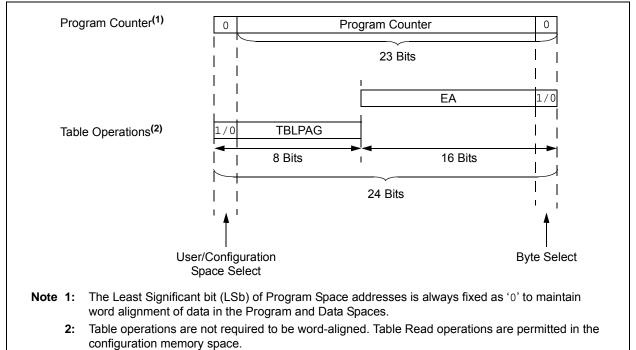

# 4.8 Interfacing Program and Data Memory Spaces

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture uses a 24-bit-wide Program Space (PS) and a 16-bit-wide Data Space (DS). The architecture is also a modified Harvard scheme, meaning that data can also be present in the Program Space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the architecture of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices provides two methods by which Program Space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the Program Space

- Remapping a portion of the Program Space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. The application can only access the least significant word of the program word.

# TABLE 4-65: PROGRAM SPACE ADDRESS CONSTRUCTION

|                        | Access        | Program Space Address        |            |               |               |     |  |  |  |  |

|------------------------|---------------|------------------------------|------------|---------------|---------------|-----|--|--|--|--|

| Access Type            | Space         | <23>                         | <22:16>    | <15>          | <14:1>        | <0> |  |  |  |  |

| Instruction Access     | User          | 0                            | 0 PC<22:1> |               |               |     |  |  |  |  |

| (Code Execution)       |               | 0xx xxxx xxxx xxxx xxxx xxx0 |            |               |               |     |  |  |  |  |

| TBLRD/TBLWT            | User          | TB                           | LPAG<7:0>  |               | Data EA<15:0> |     |  |  |  |  |

| (Byte/Word Read/Write) |               | 0                            | xxx xxxx   | XXXX XXX      |               |     |  |  |  |  |

|                        | Configuration | TB                           | LPAG<7:0>  | Data EA<15:0> |               |     |  |  |  |  |

|                        |               | 1                            | xxx xxxx   | XXXX XX       |               |     |  |  |  |  |

# FIGURE 4-22: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

# 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code, or a complete redesign, may be the only option.

Peripheral Pin Select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to any one of these I/O pins. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

## 11.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the label, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the Peripheral Pin Select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs. In comparison, some digital-only peripheral modules are never included in the Peripheral Pin Select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $I^2C^{TM}$  and the PWM. A similar requirement excludes all modules with analog inputs, such as the ADC Converter.

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral Pin Select features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheralselectable pin is handled in two different ways, depending on whether an input or output is being mapped.

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

|        |     |       |       | DD20  |         |       |       |

|--------|-----|-------|-------|-------|---------|-------|-------|

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

| bit 15 |     |       |       |       |         |       | bit 8 |

|        |     |       |       | RP35  | iR<5:0> |       |       |

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

# REGISTER 11-18: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|--------|-------|-------|

| —     | —   |       |       | RP20  | R<5:0> |       |       |

| bit 7 |     |       |       |       |        |       | bit 0 |

|       |     |       |       |       |        |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP35R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP35 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP20R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 11-19: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|--|--|

| —      | —   |       | RP37R<5:0> |       |       |       |       |  |  |  |

| bit 15 |     |       |            |       |       |       | bit 8 |  |  |  |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|--|

| —     | —   |       | RP36R<5:0> |       |       |       |       |  |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP37R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP37 Output Pin bits (see Table 11-3 for peripheral function numbers) |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                               |

| bit 5-0   | <b>RP36R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP36 Output Pin bits (see Table 11-3 for peripheral function numbers) |

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Input Source Select for Synchronization and Trigger Operation bits<sup>(4)</sup>

- 11111 = No Sync or Trigger source for ICx

- 11110 = Reserved

- 11101 = Reserved

- 11100 = CTMU module synchronizes or triggers ICx

- 11011 = ADC1 module synchronizes or triggers  $ICx^{(5)}$

- 11010 = CMP3 module synchronizes or triggers  $ICx^{(5)}$

- $11001 = CMP2 \text{ module synchronizes or triggers ICx}^{(5)}$

- 11000 = CMP1 module synchronizes or triggers  $ICx^{(5)}$

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Reserved

- 10100 = Reserved

- 10011 = IC4 module synchronizes or triggers ICx

- 10010 = IC3 module synchronizes or triggers ICx

- 10001 = IC2 module synchronizes or triggers ICx

- 10000 = IC1 module synchronizes or triggers ICx

- 01111 = Timer5 synchronizes or triggers ICx

- 01110 = Timer4 synchronizes or triggers ICx

- 01101 = Timer3 synchronizes or triggers ICx (default)

- 01100 = Timer2 synchronizes or triggers ICx

- 01011 = Timer1 synchronizes or triggers ICx

- 01010 = PTGOx module synchronizes or triggers  $ICx^{(6)}$

- 01001 = Reserved

- 01000 = Reserved

- 00111 = Reserved

- 00110 = Reserved

- 00101 = Reserved

- 00100 = OC4 module synchronizes or triggers ICx

- 00011 = OC3 module synchronizes or triggers ICx

- 00010 = OC2 module synchronizes or triggers ICx

- 00001 = OC1 module synchronizes or triggers ICx

- 00000 = No Sync or Trigger source for ICx

- **Note 1:** The IC32 bit in both the Odd and Even IC must be set to enable Cascade mode.

- 2: The input source is selected by the SYNCSEL<4:0> bits of the ICxCON2 register.

- **3:** This bit is set by the selected input source (selected by SYNCSEL<4:0> bits). It can be read, set and cleared in software.

- 4: Do not use the ICx module as its own Sync or Trigger source.

- 5: This option should only be selected as a trigger source and not as a synchronization source.

- Each Input Capture x (ICx) module has one PTG input source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information.

PTGO8 = IC1

PTGO9 = IC2 PTGO10 = IC3 PTGO11 = IC4

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

| bit 4-0 | SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits  |

|---------|--------------------------------------------------------------|

|         | 11111 = OCxRS compare event is used for synchronization      |

|         | 11110 = INT2 pin synchronizes or triggers OCx                |

|         | 11101 = INT1 pin synchronizes or triggers OCx                |

|         | 11100 = CTMU module synchronizes or triggers OCx             |

|         | 11011 = ADC1 module synchronizes or triggers OCx             |

|         | 11010 = CMP3 module synchronizes or triggers OCx             |

|         | 11001 = CMP2 module synchronizes or triggers OCx             |

|         | 11000 = CMP1 module synchronizes or triggers OCx             |

|         | 10111 = Reserved                                             |

|         | 10110 = Reserved                                             |

|         | 10101 = Reserved                                             |

|         | 10100 = Reserved                                             |

|         | 10011 = IC4 input capture event synchronizes or triggers OCx |

|         | 10010 = IC3 input capture event synchronizes or triggers OCx |

|         | 10001 = IC2 input capture event synchronizes or triggers OCx |

|         | 10000 = IC1 input capture event synchronizes or triggers OCx |

|         | 01111 = Timer5 synchronizes or triggers OCx                  |

|         | 01110 = Timer4 synchronizes or triggers OCx                  |

|         | 01101 = Timer3 synchronizes or triggers OCx                  |

|         | 01100 = Timer2 synchronizes or triggers OCx (default)        |

|         | 01011 = Timer1 synchronizes or triggers OCx $(2)$            |

|         | 01010 = PTGOx synchronizes or triggers $OCx^{(3)}$           |

|         | 01001 = Reserved                                             |

|         | 01000 = Reserved                                             |

|         | 00111 = Reserved                                             |

|         | 00110 = Reserved                                             |

|         | 00101 = Reserved                                             |

|         | 00100 = OC4 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00011 = OC3 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00010 = OC2 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00001 = OC1 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00000 = No Sync or Trigger source for OCx                    |

- **Note 1:** Do not use the OCx module as its own Synchronization or Trigger source.

- 2: When the OCy module is turned OFF, it sends a trigger out signal. If the OCx module uses the OCy module as a Trigger source, the OCy module must be unselected as a Trigger source prior to disabling it.

- Each Output Compare x module (OCx) has one PTG Trigger/Synchronization source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information. PTGO0 = OC1

PTGO0 = OC1 PTGO1 = OC2 PTGO2 = OC3PTGO3 = OC4

# REGISTER 17-4: POSICNTH: POSITION COUNTER 1 HIGH WORD REGISTER

| -n = Value at P                   | OR    | '1' = Bit is set |       | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |

|-----------------------------------|-------|------------------|-------|------------------------------------|-------|-----------------|-------|

| R = Readable bit W = Writable bit |       |                  | it    | U = Unimplemented bit, read as '0' |       |                 |       |

| Legend:                           |       |                  |       |                                    |       |                 |       |

|                                   |       |                  |       |                                    |       |                 |       |

| bit 7                             |       |                  |       |                                    |       |                 | bit 0 |

|                                   |       |                  | POSCN | IT<23:16>                          |       |                 |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

| bit 15                            |       |                  |       |                                    |       |                 | bit 8 |

|                                   |       |                  | POSCN | IT<31:24>                          |       |                 |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |

bit 15-0 **POSCNT<31:16>:** High Word Used to Form 32-Bit Position Counter Register (POS1CNT) bits

## REGISTER 17-5: POS1CNTL: POSITION COUNTER 1 LOW WORD REGISTER

| R/W-0        | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------------|-------|-------|-------|-------|-------|-------|-------|--|--|

| POSCNT<15:8> |       |       |       |       |       |       |       |  |  |

| bit 15       |       |       |       |       |       |       | bit 8 |  |  |

|              |       |       |       |       |       |       |       |  |  |

| R/W-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |

|-------|-------------|-------|-------|-------|-------|-------|-------|--|--|--|

|       | POSCNT<7:0> |       |       |       |       |       |       |  |  |  |

| bit 7 |             |       |       |       |       |       | bit 0 |  |  |  |

| Legend:           |                  |                        |                                    |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |

bit 15-0 POSCNT<15:0>: Low Word Used to Form 32-Bit Position Counter Register (POS1CNT) bits

# REGISTER 17-6: POS1HLD: POSITION COUNTER 1 HOLD REGISTER

| R/W-0                                                 | R/W-0 | R/W-0 | R/W-0 | R/W-0             | R/W-0    | R/W-0           | R/W-0 |

|-------------------------------------------------------|-------|-------|-------|-------------------|----------|-----------------|-------|

|                                                       |       |       | POSHI | _D<15:8>          |          |                 |       |

| bit 15                                                |       |       |       |                   |          |                 | bit 8 |

|                                                       |       |       |       |                   |          |                 |       |

| R/W-0                                                 | R/W-0 | R/W-0 | R/W-0 | R/W-0             | R/W-0    | R/W-0           | R/W-0 |

|                                                       |       |       | POSH  | LD<7:0>           |          |                 |       |

| bit 7                                                 |       |       |       |                   |          |                 | bit 0 |

|                                                       |       |       |       |                   |          |                 |       |

| Legend:                                               |       |       |       |                   |          |                 |       |

| R = Readable bit W = Writable bit U = Unimplemented b |       |       |       | nented bit, rea   | d as '0' |                 |       |

| -n = Value at POR '1' = Bit                           |       |       |       | '0' = Bit is clea | ared     | x = Bit is unkr | nown  |

bit 15-0 **POSHLD<15:0>:** Hold Register for Reading and Writing POS1CNTH bits

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

| R/W-0                             | R/W-0    | R/W-0            | U-0             | R/W-0, HC                          | R/W-0                | R-0             | R-1   |

|-----------------------------------|----------|------------------|-----------------|------------------------------------|----------------------|-----------------|-------|

| UTXISEL1                          | UTXINV   | UTXISEL0         | —               | UTXBRK                             | UTXEN <sup>(1)</sup> | UTXBF           | TRMT  |

| bit 15                            |          |                  |                 |                                    |                      |                 | bit 8 |

|                                   |          |                  |                 |                                    |                      |                 |       |

| R/W-0                             | R/W-0    | R/W-0            | R-1             | R-0                                | R-0                  | R/C-0           | R-0   |

| URXISEL1                          | URXISEL0 | ADDEN            | RIDLE           | PERR                               | FERR                 | OERR            | URXDA |

| bit 7                             |          |                  |                 |                                    |                      |                 | bit C |

|                                   |          |                  |                 |                                    |                      |                 |       |

| Legend:                           |          | HC = Hardward    | e Clearable bit | C = Clearable bit                  |                      |                 |       |

| R = Readable bit W = Writable bit |          |                  | bit             | U = Unimplemented bit, read as '0' |                      |                 |       |

| -n = Value at POR '1'             |          | '1' = Bit is set |                 | '0' = Bit is cleared               |                      | x = Bit is unki | nown  |

# REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR) and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: UARTx Transmit Polarity Inversion bit

- $\frac{If IREN = 0}{1 = UxTX Idle state is '0'}$

- 0 = UxTX Idle state is '1'

- If IREN = 1:

- 1 = IrDA encoded, UxTX Idle state is '1'

- 0 = IrDA encoded, UxTX Idle state is '0'

- bit 12 Unimplemented: Read as '0'

- bit 11 UTXBRK: UARTx Transmit Break bit

- 1 = Sends Sync Break on next transmission Start bit, followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Sync Break transmission is disabled or completed

- bit 10 UTXEN: UARTx Transmit Enable bit<sup>(1)</sup> 1 = Transmit is enabled, UxTX pin is controlled by UARTx

- 0 = Transmit is disabled, any pending transmission is aborted and buffer is reset; UxTX pin is controlled by the PORT

- bit 9 UTXBF: UARTx Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

- bit 8 TRMT: Transmit Shift Register Empty bit (read-only)

- 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit Shift Register is not empty, a transmission is in progress or queued

- bit 7-6 URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits

- 11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)

- 10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)

- 0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer; receive buffer has one or more characters

- **Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

# FIGURE 22-1: CTMU BLOCK DIAGRAM

5: The switch connected to ADC CH0 is closed when IDISSEN (CTMUCON1<9>) = 1, and opened when IDISSEN = 0.

# 22.1 CTMU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 22.1.1 KEY RESOURCES

- "Charge Time Measurement Unit (CTMU)" (DS70661) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related "dsPIC33/PIC24 Family Reference Manual" Sections

- · Development Tools

# 23.4 ADC Control Registers

## REGISTER 23-1: AD1CON1: ADC1 CONTROL REGISTER 1

| R/W-0         | U-0                                                                                                                                                                                    | R/W-0                             | R/W-0            | U-0               | R/W-0            | R/W-0             | R/W-0               |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|-------------------|------------------|-------------------|---------------------|--|--|

| ADON          | —                                                                                                                                                                                      | ADSIDL                            | ADDMABM          |                   | AD12B            | FORM1             | FORM0               |  |  |

| bit 15        | •                                                                                                                                                                                      |                                   |                  |                   |                  |                   | bit 8               |  |  |

| R/W-0         | R/W-0                                                                                                                                                                                  | R/W-0                             | R/W-0            | R/W-0             | R/W-0            | R/W-0, HC, HS     | R/C-0. HC. HS       |  |  |

| SSRC2         | SSRC1                                                                                                                                                                                  | SSRC0                             | SSRCG            | SIMSAM            | ASAM             | SAMP              | DONE <sup>(3)</sup> |  |  |

| bit 7         |                                                                                                                                                                                        |                                   |                  |                   |                  |                   | bit (               |  |  |

| Legend:       |                                                                                                                                                                                        | HC - Hardwar                      | e Clearable bit  | HS - Hardwa       | re Settable bit  | C = Clearable bi  | +                   |  |  |

| R = Readable  | a hit                                                                                                                                                                                  | W = Writable b                    |                  |                   | nented bit, read |                   | L                   |  |  |

| -n = Value at |                                                                                                                                                                                        | '1' = Bit is set                  | nt               | '0' = Bit is clea |                  | x = Bit is unknov | vp                  |  |  |

|               | FUR                                                                                                                                                                                    |                                   |                  |                   |                  | x – Bit is unknov |                     |  |  |

| bit 15        | ADON: ADO                                                                                                                                                                              | C1 Operating M                    | ode bit          |                   |                  |                   |                     |  |  |

|               | 1 = ADC mo<br>0 = ADC is 0                                                                                                                                                             | odule is operatir<br>off          | ng               |                   |                  |                   |                     |  |  |

| bit 14        | Unimpleme                                                                                                                                                                              | nted: Read as                     | ʻ0'              |                   |                  |                   |                     |  |  |

| bit 13        | ADSIDL: ADC1 Stop in Idle Mode bit                                                                                                                                                     |                                   |                  |                   |                  |                   |                     |  |  |

|               | 1 = Discontinues module operation when device enters Idle mode                                                                                                                         |                                   |                  |                   |                  |                   |                     |  |  |

|               | 0 = Continues module operation in Idle mode                                                                                                                                            |                                   |                  |                   |                  |                   |                     |  |  |

| bit 12        | ADDMABM: DMA Buffer Build Mode bit                                                                                                                                                     |                                   |                  |                   |                  |                   |                     |  |  |

|               | 1 = DMA buffers are written in the order of conversion; the module provides an address to the DMA                                                                                      |                                   |                  |                   |                  |                   |                     |  |  |

|               | channel that is the same as the address used for the non-DMA stand-alone buffer<br>0 = DMA buffers are written in Scatter/Gather mode; the module provides a Scatter/Gather address to |                                   |                  |                   |                  |                   |                     |  |  |

|               |                                                                                                                                                                                        |                                   |                  |                   |                  | size of the DMA b |                     |  |  |

| bit 11        |                                                                                                                                                                                        | nted: Read as                     |                  |                   |                  |                   |                     |  |  |

| bit 10        | AD12B: AD                                                                                                                                                                              | C1 10-Bit or 12                   | -Bit Operation I | Mode bit          |                  |                   |                     |  |  |

|               | 1 = 12-bit, 1-channel ADC operation                                                                                                                                                    |                                   |                  |                   |                  |                   |                     |  |  |

|               | 0 = 10-bit, 4                                                                                                                                                                          | -channel ADC                      | operation        |                   |                  |                   |                     |  |  |

| bit 9-8       | FORM<1:0>                                                                                                                                                                              | : Data Output I                   | Format bits      |                   |                  |                   |                     |  |  |

|               | For 10-Bit Operation:                                                                                                                                                                  |                                   |                  |                   |                  |                   |                     |  |  |

|               | 11 = Signed fractional (Dout = sddd dddd dd00 0000, where s = .NOT.d<9>)                                                                                                               |                                   |                  |                   |                  |                   |                     |  |  |

|               | 10 = Fractional (Dout = dddd dddd dd00 0000)<br>01 = Signed integer (Dout = ssss sssd dddd dddd, where s = .NOT.d<9>)                                                                  |                                   |                  |                   |                  |                   |                     |  |  |

|               | 00 = Integer (DOUT = 0000 00 dd dd dd dd d)                                                                                                                                            |                                   |                  |                   |                  |                   |                     |  |  |

|               | For 12-Bit Operation:                                                                                                                                                                  |                                   |                  |                   |                  |                   |                     |  |  |

|               | 11 = Signed fractional (Dout = sddd dddd dddd 0000, where s = .NOT.d<11>)                                                                                                              |                                   |                  |                   |                  |                   |                     |  |  |

|               |                                                                                                                                                                                        |                                   |                  |                   |                  |                   |                     |  |  |

|               |                                                                                                                                                                                        | nal (Dout = dd<br>I integer (Dout |                  |                   |                  | (<11>)            |                     |  |  |

- 2: This setting is available in dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices only.

- 3: Do not clear the DONE bit in software if Auto-Sample is enabled (ASAM = 1).

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

## REGISTER 26-3: CRCXORH: CRC XOR POLYNOMIAL HIGH REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 | R/W-0 |

|------------------------------------|-------|-------|------------------|------------------|-----------------|-------|-------|

|                                    |       |       | X<3              | 31:24>           |                 |       |       |

| bit 15                             |       |       |                  |                  |                 |       | bit 8 |

|                                    |       |       |                  |                  |                 |       |       |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0            | R/W-0            | R/W-0           | R/W-0 | R/W-0 |

|                                    |       |       | X<2              | 23:16>           |                 |       |       |

| bit 7                              |       |       |                  |                  |                 |       | bit 0 |

|                                    |       |       |                  |                  |                 |       |       |

| Legend:                            |       |       |                  |                  |                 |       |       |

| R = Readable bit W = Writable bit  |       |       | U = Unimpler     | mented bit, read | d as '0'        |       |       |

| -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |       |

|                                    | -     |       |                  |                  |                 |       | -     |

bit 15-0 X<31:16>: XOR of Polynomial Term X<sup>n</sup> Enable bits

#### REGISTER 26-4: CRCXORL: CRC XOR POLYNOMIAL LOW REGISTER

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0                | R/W-0 | R/W-0              | R/W-0 |

|------------------------------------|-------|-------|------------------------------------|----------------------|-------|--------------------|-------|

|                                    |       |       | Х<                                 | 15:8>                |       |                    |       |

| bit 15                             |       |       |                                    |                      |       |                    | bit 8 |

| R/W-0                              | R/W-0 | R/W-0 | R/W-0                              | R/W-0                | R/W-0 | R/W-0              | U-0   |

|                                    |       |       | X<7:1>                             |                      |       |                    | _     |

| bit 7                              |       |       |                                    |                      |       |                    | bit 0 |

| Legend:                            |       |       |                                    |                      |       |                    |       |

| R = Readable bit W = Writable bit  |       |       | U = Unimplemented bit, read as '0' |                      |       |                    |       |

| -n = Value at POR '1' = Bit is set |       |       |                                    | '0' = Bit is cleared |       | x = Bit is unknown |       |

bit 15-1X<15:1>: XOR of Polynomial Term X<sup>n</sup> Enable bitsbit 0Unimplemented: Read as '0'

| DC CHARACTER  | ISTICS |      | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |            |       |  |  |

|---------------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|--|--|

| Parameter No. | Тур.   | Max. | Units                                                                                                                                                                                                | Conditions |       |  |  |

| DC61d         | 8      |      | μΑ                                                                                                                                                                                                   | -40°C      |       |  |  |

| DC61a         | 10     | —    | μA                                                                                                                                                                                                   | +25°C      | 2.21/ |  |  |

| DC61b         | 12     | —    | μA                                                                                                                                                                                                   | +85°C      | 3.3V  |  |  |

| DC61c         | 13     | —    | μA                                                                                                                                                                                                   | +125°C     |       |  |  |

# TABLE 30-9: DC CHARACTERISTICS: WATCHDOG TIMER DELTA CURRENT ( $\Delta$ Iwdt)<sup>(1)</sup>

**Note 1:** The  $\triangle$ IwDT current is the additional current consumed when the module is enabled. This current should be added to the base IPD current. All parameters are characterized but not tested during manufacturing.

#### TABLE 30-10: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTER                        | ISTICS        | Standard C<br>(unless oth<br>Operating to | erwise st  | <b>ated)</b><br><sup>·</sup> e -40°C | ≤ TA ≤ +8 | <b>5°C for Industrial</b><br>25°C for Extended |                |

|-------------------------------------|---------------|-------------------------------------------|------------|--------------------------------------|-----------|------------------------------------------------|----------------|

| Parameter No.                       | Doze<br>Ratio | Units                                     | Conditions |                                      |           |                                                |                |

| Doze Current (IDOZE) <sup>(1)</sup> |               |                                           |            |                                      |           |                                                |                |

| DC73a <sup>(2)</sup>                | 35            |                                           | 1:2        | mA                                   | -40°C     | 3.3V                                           | Fosc = 140 MHz |

| DC73g                               | 20            | 30                                        | 1:128      | mA                                   | -40 C     |                                                |                |

| DC70a <sup>(2)</sup>                | 35            | _                                         | 1:2        | mA                                   | +25°C     | 3.3V                                           | Fosc = 140 MHz |

| DC70g                               | 20            | 30                                        | 1:128      | mA                                   | +25 C     |                                                | FUSC - 140 MHZ |

| DC71a <sup>(2)</sup>                | 35            | —                                         | 1:2        | mA                                   | 195%      | 3.3V                                           |                |

| DC71g                               | 20            | 30                                        | 1:128      | mA                                   | +85°C     |                                                | Fosc = 140 MHz |

| DC72a <sup>(2)</sup>                | 28            | —                                         | 1:2        | mA                                   | +125°C    | 2 21/                                          | Ecco - 120 MH- |

| DC72g                               | 15            | 30                                        | 1:128      | mA                                   | +125 C    | 3.3V                                           | Fosc = 120 MHz |

**Note 1:** IDOZE is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDOZE measurements are as follows:

- Oscillator is configured in EC mode and external clock is active, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)</li>

- CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) statement

- · JTAG is disabled

- 2: Parameter is characterized but not tested in manufacturing.

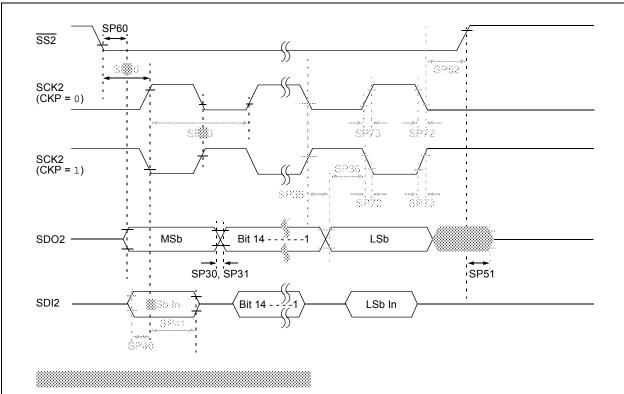

# FIGURE 30-18: SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

#### 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |                |           |      |  |

|--------------------------|-------------|----------------|-----------|------|--|

| D                        | MIN         | NOM            | MAX       |      |  |

| Number of Leads          | N           |                | 64        |      |  |

| Lead Pitch               | е           |                | 0.50 BSC  |      |  |

| Overall Height           | А           | -              | -         | 1.20 |  |

| Molded Package Thickness | A2          | 0.95           | 1.00      | 1.05 |  |

| Standoff                 | A1          | 0.05           | -         | 0.15 |  |

| Foot Length              | L           | 0.45           | 0.60      | 0.75 |  |

| Footprint                | L1          | 1.00 REF       |           |      |  |

| Foot Angle               | φ           | 0° 3.5° 7°     |           |      |  |

| Overall Width            | E           | 12.00 BSC      |           |      |  |

| Overall Length           | D           |                | 12.00 BSC |      |  |

| Molded Package Width     | E1          | 10.00 BSC      |           |      |  |

| Molded Package Length    | D1          | 10.00 BSC      |           |      |  |

| Lead Thickness           | С           | 0.09           | -         | 0.20 |  |

| Lead Width               | b           | 0.17 0.22 0.27 |           |      |  |

| Mold Draft Angle Top     | α           | 11° 12° 13°    |           |      |  |

| Mold Draft Angle Bottom  | β           | 11°            | 12°       | 13°  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B