Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-TQFP                                                                          |

| Supplier Device Package    | 44-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc204t-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 4-6: INTERRUPT CONTROLLER REGISTER MAP FOR dsPIC33EPXXXMC20X DEVICES ONLY (CONTINUED)

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11   | Bit 10 | Bit 9      | Bit 8       | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3   | Bit 2  | Bit 1       | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|------------|---------|----------|--------|------------|-------------|----------|---------|-------------|---------|---------|--------|-------------|--------|---------------|

| IPC35        | 0886  | _      |        | JTAGIP<2:0 | )>      | —        |        | ICDIP<2:0  | >           | _        | —       | —           | _       | —       | _      | -           |        | 4400          |

| IPC36        | 0888  | -      | l      | PTG0IP<2:0 | )>      | _        | PT     | GWDTIP<    | 2:0>        | _        | P       | TGSTEPIP<2  | :0>     | —       | —      |             |        | 4440          |

| IPC37        | 088A  |        | _      | _          | _       | _        | F      | PTG3IP<2:0 | )>          | _        |         | PTG2IP<2:0> | >       | _       | F      | PTG1IP<2:0> |        | 0444          |

| INTCON1      | 08C0  | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR  | OVATE  | OVBTE      | COVTE       | SFTACERR | DIV0ERR | DMACERR     | MATHERR | ADDRERR | STKERR | OSCFAIL     |        | 0000          |

| INTCON2      | 08C2  | GIE    | DISI   | SWTRAP     | —       | —        | _      |            |             | —        | _       | —           | —       | _       | INT2EP | INT1EP      | INT0EP | 8000          |

| INTCON3      | 08C4  | _      | _      | —          | —       | —        | _      |            |             | —        | _       | DAE         | DOOVR   | _       | —      |             |        | 0000          |

| INTCON4      | 08C6  | -      | _      | —          | _       | _        | _      |            | _           | _        | _       | —           | —       | —       | —      | _           | SGHT   | 0000          |

| INTTREG      | 08C8  | -      | —      | —          | _       | ILR<3:0> |        |            | VECNUM<7:0> |          |         |             |         |         |        |             | 0000   |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-17: I2C1 AND I2C2 REGISTER MAP

| File<br>Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                   | Bit 8 | Bit 7 | Bit 6 | Bit 5     | Bit 4        | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|---------|--------|---------|--------|--------|--------|-------------------------|-------|-------|-------|-----------|--------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 0200  | —       | —      | —       | —      | —      | —      | —                       | _     |       |       |           | I2C1 Recei   | ve Register  |       |       |       | 0000          |

| I2C1TRN      | 0202  | _       | _      | _       | _      | —      | _      | —                       | _     |       |       |           | I2C1 Transi  | mit Register |       |       |       | OOFF          |

| I2C1BRG      | 0204  | _       | _      | _       | _      | _      | _      | _                       |       |       |       | Bau       | d Rate Gene  | erator       |       |       |       | 0000          |

| I2C1CON      | 0206  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                  | SMEN  | GCEN  | STREN | ACKDT     | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT     | 0208  | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT                  | ADD10 | IWCOL | I2COV | D_A       | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 020A  | _       | _      | _       | _      | _      | _      | I2C1 Address Register 0 |       |       |       |           |              |              | 0000  |       |       |               |

| I2C1MSK      | 020C  | _       | _      | _       | _      | _      | _      |                         |       |       |       | I2C1 Add  | dress Mask   |              |       |       |       | 0000          |

| I2C2RCV      | 0210  | _       | _      | _       | _      | _      | _      | _                       | _     |       |       |           | I2C2 Recei   | ve Register  |       |       |       | 0000          |

| I2C2TRN      | 0212  | _       | _      | _       | _      | _      | _      | _                       | _     |       |       |           | I2C2 Transi  | mit Register |       |       |       | OOFF          |

| I2C2BRG      | 0214  | _       | _      | _       | _      | _      | _      | _                       |       |       |       | Bau       | d Rate Gene  | erator       |       |       |       | 0000          |

| I2C2CON      | 0216  | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                  | SMEN  | GCEN  | STREN | ACKDT     | ACKEN        | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT     | 0218  | ACKSTAT | TRSTAT | _       | _      | —      | BCL    | GCSTAT                  | ADD10 | IWCOL | I2COV | D_A       | Р            | S            | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 021A  | _       | _      | _       | _      | —      | _      |                         |       |       |       | I2C2 Addr | ess Register | r            |       |       |       | 0000          |

| I2C2MSK      | 021C  | _       | _      | _       | _      | _      | _      | I2C2 Address Mask 00    |       |       |       |           |              |              | 0000  |       |       |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-18: UART1 AND UART2 REGISTER MAP

| SFR<br>Name | Addr. | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9                           | Bit 8                  | Bit 7      | Bit 6    | Bit 5 | Bit 4      | Bit 3    | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-------------|-------|----------|--------|----------|--------|--------|--------|---------------------------------|------------------------|------------|----------|-------|------------|----------|-------|--------|-------|---------------|

| U1MODE      | 0220  | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _      | UEN<                            | :1:0>                  | WAKE       | LPBACK   | ABAUD | URXINV     | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U1STA       | 0222  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF                           | TRMT                   | URXIS      | SEL<1:0> | ADDEN | RIDLE      | PERR     | FERR  | OERR   | URXDA | 0110          |

| U1TXREG     | 0224  | _        | _      | _        | _      | _      | _      | _                               |                        |            |          | UART1 | Transmit F | Register |       |        |       | xxxx          |

| U1RXREG     | 0226  | _        | _      | _        | _      | _      | _      | _                               | UART1 Receive Register |            |          |       |            |          | 0000  |        |       |               |

| U1BRG       | 0228  |          |        |          |        |        |        | Baud Rate Generator Prescaler 0 |                        |            |          |       |            | 0000     |       |        |       |               |

| U2MODE      | 0230  | UARTEN   | _      | USIDL    | IREN   | RTSMD  | _      | UEN<                            | :1:0>                  | WAKE       | LPBACK   | ABAUD | URXINV     | BRGH     | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA       | 0232  | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF                           | TRMT                   | URXIS      | SEL<1:0> | ADDEN | RIDLE      | PERR     | FERR  | OERR   | URXDA | 0110          |

| U2TXREG     | 0234  | _        | _      | _        | _      | _      | _      | _                               |                        |            |          | UART2 | Transmit F | Register |       |        |       | xxxx          |

| U2RXREG     | 0236  | _        | _      | _        | _      | —      | _      | UART2 Receive Register 00       |                        |            |          |       |            |          | 0000  |        |       |               |

| U2BRG       | 0238  |          |        |          |        |        |        | Baud                            | Rate Gen               | erator Pre | scaler   |       |            |          |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-24: CRC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14                  | Bit 13 | Bit 13         Bit 12         Bit 11         Bit 10         Bit 9         Bit 8         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0         F |                                                |           |    |          |              |      |      |      | All<br>Resets |           |  |      |

|-----------|-------|--------|-------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------|----|----------|--------------|------|------|------|---------------|-----------|--|------|

| CRCCON1   | 0640  | CRCEN  | —                       | CSIDL  |                                                                                                                                                                                                           | VWORD<4:0> CRCFUL CRCMPT CRCISEL CRCGO LENDIAN |           |    |          |              |      |      |      |               | 0000      |  |      |

| CRCCON2   | 0642  |        | _                       | _      |                                                                                                                                                                                                           | D                                              | WIDTH<4:0 | )> |          | _            | -    | _    |      | F             | PLEN<4:0> |  | 0000 |

| CRCXORL   | 0644  |        | X<15:1>00               |        |                                                                                                                                                                                                           |                                                |           |    |          |              |      |      | 0000 |               |           |  |      |

| CRCXORH   | 0646  |        |                         |        |                                                                                                                                                                                                           |                                                |           |    | X·       | <31:16>      |      |      |      |               |           |  | 0000 |

| CRCDATL   | 0648  |        |                         |        |                                                                                                                                                                                                           |                                                |           |    | CRC Data | Input Low V  | Vord |      |      |               |           |  | 0000 |

| CRCDATH   | 064A  |        |                         |        |                                                                                                                                                                                                           |                                                |           |    | CRC Data | Input High \ | Vord |      |      |               |           |  | 0000 |

| CRCWDATL  | 064C  |        | CRC Result Low Word 00  |        |                                                                                                                                                                                                           |                                                |           |    |          |              |      |      | 0000 |               |           |  |      |

| CRCWDATH  | 064E  |        | CRC Result High Word 00 |        |                                                                                                                                                                                                           |                                                |           |    |          |              |      | 0000 |      |               |           |  |      |

Legend: — = unimplemented, read as '0'. Shaded bits are not used in the operation of the programmable CRC module.

# TABLE 4-25: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC202/502 AND PIC24EPXXXGP/MC202 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 13 Bit 12 Bit 11 Bit 10 Bit 9 Bit 8 Bit 7 Bit |       |       |  |  |   | Bit 6 | Bit 5      | Bit 4      | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |  |  |

|--------------|-------|--------|--------|--------|---------------------------------------------------|-------|-------|--|--|---|-------|------------|------------|-------|--------|-------|-------|---------------|--|--|

| RPOR0        | 0680  | —      | —      |        | RP35R<5:0>                                        |       |       |  |  |   | _     |            | RP20R<5:0> |       |        |       |       |               |  |  |

| RPOR1        | 0682  | _      | _      |        | RP37R<5:0>                                        |       |       |  |  |   | Ι     |            | RP36R<5:0> |       |        |       |       |               |  |  |

| RPOR2        | 0684  | _      | _      |        |                                                   | RP39F | <5:0> |  |  | _ | Ι     | RP38R<5:0> |            |       |        |       |       | 0000          |  |  |

| RPOR3        | 0686  | _      | _      |        | RP41R<5:0>                                        |       |       |  |  | _ | Ι     |            |            | RP40F | ۲<5:0> |       |       | 0000          |  |  |

| RPOR4        | 0688  | _      | _      |        | RP43R<5:0>                                        |       |       |  |  |   | _     |            |            | RP42F | R<5:0> |       |       | 0000          |  |  |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-26: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33EPXXXGP/MC203/503 AND PIC24EPXXXGP/MC203 DEVICES ONLY DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12     | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4      | Bit 3 | Bit 2  | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|------------|--------|--------|-------|-------|-------|-------|------------|------------|-------|--------|-------|-------|---------------|

| RPOR0        | 0680  |        | —      |        | RP35R<5:0> |        |        |       |       | _     | _     |            |            | RP20F | २<5:0> |       |       | 0000          |

| RPOR1        | 0682  | _      | _      |        | RP37R<5:0> |        |        |       |       | _     | _     |            | RP36R<5:0> |       |        |       |       |               |

| RPOR2        | 0684  | _      | _      |        |            | RP39F  | २<5:0> |       |       | _     | —     |            | RP38R<5:0> |       |        |       |       | 0000          |

| RPOR3        | 0686  | _      | _      |        |            | RP41F  | २<5:0> |       |       | _     | —     |            | RP40R<5:0> |       |        |       |       | 0000          |

| RPOR4        | 0688  | _      | _      |        |            | RP43F  | ۲<5:0> |       |       | _     | _     | RP42R<5:0> |            |       |        |       | 0000  |               |

| RPOR5        | 068A  | _      | _      | _      | _          | _      | _      |       | _     | _     | _     | _          | _          | _     | _      |       |       | 0000          |

| RPOR6        | 068C  | _      | —      |        |            |        |        |       |       | 0000  |       |            |            |       |        |       |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# **REGISTER 8-7:** DMAXPAD: DMA CHANNEL X PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0           | R/W-0                             | R/W-0            | R/W-0 | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |  |  |  |  |

|-----------------|-----------------------------------|------------------|-------|-----------------------------------------|------------------|----------|-------|--|--|--|--|

|                 |                                   |                  | PAD   | <15:8>                                  |                  |          |       |  |  |  |  |

| bit 15          |                                   |                  |       |                                         |                  |          | bit 8 |  |  |  |  |

|                 |                                   |                  |       |                                         |                  |          |       |  |  |  |  |

| R/W-0           | R/W-0                             | R/W-0            | R/W-0 | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |  |  |  |  |

|                 |                                   |                  | PAE   | )<7:0>                                  |                  |          |       |  |  |  |  |

| bit 7           |                                   |                  |       |                                         |                  |          | bit 0 |  |  |  |  |

|                 |                                   |                  |       |                                         |                  |          |       |  |  |  |  |

| Legend:         |                                   |                  |       |                                         |                  |          |       |  |  |  |  |

| R = Readable    | R = Readable bit W = Writable bit |                  |       |                                         | nented bit, read | d as '0' |       |  |  |  |  |

| -n = Value at P | POR                               | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                  |          |       |  |  |  |  |

#### bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

#### REGISTER 8-8: DMAXCNT: DMA CHANNEL X TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0             | U-0   | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |

|-----------------|-------|------------------|-------|-------------------|------------------|--------------------|-------|--|

| —               |       |                  |       | CNT<              | 13:8> <b>(2)</b> |                    |       |  |

| bit 15          |       |                  |       |                   |                  |                    | bit 8 |  |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |

|                 |       |                  | CNT<  | <7:0> <b>(2)</b>  |                  |                    |       |  |

| bit 7           |       |                  |       |                   |                  |                    | bit 0 |  |

| Legend:         |       |                  |       |                   |                  |                    |       |  |

| R = Readable b  | oit   | W = Writable b   | bit   | U = Unimplen      | nented bit, rea  | id as '0'          |       |  |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | ared             | x = Bit is unknown |       |  |

bit 15-14 Unimplemented: Read as '0'

bit 13-0 CNT<13:0>: DMA Transfer Count Register bits<sup>(2)</sup>

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

**2:** The number of DMA transfers = CNT<13:0> + 1.

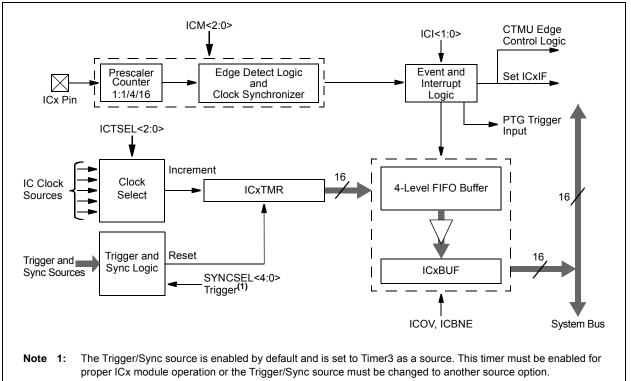

# 14.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Input Capture" (DS70352) in the "dsPIC33/dsPIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices support four input capture channels.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 19 user-selectable Trigger/Sync sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to six clock sources available for each module, driving a separate internal 16-bit counter

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2 (CONTINUED)

| bit 4-0 | SYNCSEL<4:0>: Trigger/Synchronization Source Selection bits  |

|---------|--------------------------------------------------------------|

|         | 11111 = OCxRS compare event is used for synchronization      |

|         | 11110 = INT2 pin synchronizes or triggers OCx                |

|         | 11101 = INT1 pin synchronizes or triggers OCx                |

|         | 11100 = CTMU module synchronizes or triggers OCx             |

|         | 11011 = ADC1 module synchronizes or triggers OCx             |

|         | 11010 = CMP3 module synchronizes or triggers OCx             |

|         | 11001 = CMP2 module synchronizes or triggers OCx             |

|         | 11000 = CMP1 module synchronizes or triggers OCx             |

|         | 10111 = Reserved                                             |

|         | 10110 = Reserved                                             |

|         | 10101 = Reserved                                             |

|         | 10100 = Reserved                                             |

|         | 10011 = IC4 input capture event synchronizes or triggers OCx |

|         | 10010 = IC3 input capture event synchronizes or triggers OCx |

|         | 10001 = IC2 input capture event synchronizes or triggers OCx |

|         | 10000 = IC1 input capture event synchronizes or triggers OCx |

|         | 01111 = Timer5 synchronizes or triggers OCx                  |

|         | 01110 = Timer4 synchronizes or triggers OCx                  |

|         | 01101 = Timer3 synchronizes or triggers OCx                  |

|         | 01100 = Timer2 synchronizes or triggers OCx (default)        |

|         | 01011 = Timer1 synchronizes or triggers OCx $(2)$            |

|         | 01010 = PTGOx synchronizes or triggers $OCx^{(3)}$           |

|         | 01001 = Reserved                                             |

|         | 01000 = Reserved                                             |

|         | 00111 = Reserved                                             |

|         | 00110 = Reserved                                             |

|         | 00101 = Reserved                                             |

|         | 00100 = OC4 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00011 = OC3 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00010 = OC2 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00001 = OC1 module synchronizes or triggers $OCx^{(1,2)}$    |

|         | 00000 = No Sync or Trigger source for OCx                    |

- **Note 1:** Do not use the OCx module as its own Synchronization or Trigger source.

- 2: When the OCy module is turned OFF, it sends a trigger out signal. If the OCx module uses the OCy module as a Trigger source, the OCy module must be unselected as a Trigger source prior to disabling it.

- Each Output Compare x module (OCx) has one PTG Trigger/Synchronization source. See Section 24.0 "Peripheral Trigger Generator (PTG) Module" for more information. PTGO0 = OC1

PTGO0 = OC1 PTGO1 = OC2 PTGO2 = OC3PTGO3 = OC4

# REGISTER 16-13: IOCONX: PWMx I/O CONTROL REGISTER<sup>(2)</sup> (CONTINUED)

- bit 1 SWAP: SWAP PWMxH and PWMxL Pins bit

1 = PWMxH output signal is connected to PWMxL pins; PWMxL output signal is connected to PWMxH pins

0 = PWMxH and PWMxL pins are mapped to their respective pins

bit 0 OSYNC: Output Override Synchronization bit

1 = Output overrides via the OVRDAT<1:0> bits are synchronized to the PWMx period boundary

- 0 = Output overrides via the OVDDAT<1:0> bits occur on the next CPU clock boundary

- Note 1: These bits should not be changed after the PWMx module is enabled (PTEN = 1).

- 2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

#### 22.2 **CTMU Control Registers**

| REGISTER                                                                                                                                                            | 22-1: CTM  | UCON1: CTM       | J CONTROI | - REGISTER       | 1                |                        |        |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------------|-----------|------------------|------------------|------------------------|--------|--|--|

| R/W-0                                                                                                                                                               | U-0        | R/W-0            | R/W-0     | R/W-0            | R/W-0            | R/W-0                  | R/W-0  |  |  |

| CTMUEN                                                                                                                                                              | _          | CTMUSIDL         | TGEN      | EDGEN            | EDGSEQEN         | IDISSEN <sup>(1)</sup> | CTTRIG |  |  |

| bit 15                                                                                                                                                              |            |                  |           |                  |                  |                        | bit 8  |  |  |

|                                                                                                                                                                     |            |                  |           |                  |                  |                        |        |  |  |

| U-0                                                                                                                                                                 | U-0        | U-0              | U-0       | U-0              | U-0              | U-0                    | U-0    |  |  |

|                                                                                                                                                                     | _          |                  | _         | <u> </u>         | <u> </u>         |                        | _      |  |  |

| bit 7                                                                                                                                                               |            |                  |           |                  |                  |                        | bit 0  |  |  |

|                                                                                                                                                                     |            |                  |           |                  |                  |                        |        |  |  |

| Legend:                                                                                                                                                             |            |                  |           |                  |                  |                        |        |  |  |

| R = Readable                                                                                                                                                        | e bit      | W = Writable b   | bit       | U = Unimplen     | nented bit, read | as '0'                 |        |  |  |

| -n = Value at                                                                                                                                                       | POR        | '1' = Bit is set |           | '0' = Bit is cle | ared             | x = Bit is unkn        | own    |  |  |

| bit 15 <b>CTMUEN:</b> CTMU Enable bit<br>1 = Module is enabled<br>0 = Module is disabled                                                                            |            |                  |           |                  |                  |                        |        |  |  |

| bit 14 Unimplemented: Read as '0'                                                                                                                                   |            |                  |           |                  |                  |                        |        |  |  |

| bit 13 <b>CTMUSIDL:</b> CTMU Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode<br>0 = Continues module operation in Idle mode |            |                  |           |                  |                  |                        |        |  |  |

| bit 12                                                                                                                                                              | TGEN: Time | Generation Ena   | ble bit   |                  |                  |                        |        |  |  |

#### DECISTED

| bit 9 | IDISSEN: Analog Current Source Control bit <sup>(1)</sup>                                                               |

|-------|-------------------------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Analog current source output is grounded</li><li>0 = Analog current source output is not grounded</li></ul> |

| bit 8 | CTTRIG: ADC Trigger Control bit                                                                                         |

|       | <ul><li>1 = CTMU triggers ADC start of conversion</li><li>0 = CTMU does not trigger ADC start of conversion</li></ul>   |

EDGSEQEN: Edge Sequence Enable bit

0 = No edge sequence is needed

1 = Enables edge delay generation 0 = Disables edge delay generation

EDGEN: Edge Enable bit

bit 7-0 Unimplemented: Read as '0'

bit 11

bit 10

Note 1: The ADC module Sample-and-Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitance measurement must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

1 = Hardware modules are used to trigger edges (TMRx, CTEDx, etc.) 0 = Software is used to trigger edges (manual set of EDGxSTAT)

1 = Edge 1 event must occur before Edge 2 event can occur

# 24.0 PERIPHERAL TRIGGER GENERATOR (PTG) MODULE

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Peripheral Trigger Generator (PTG)" (DS70669) in the "dsPIC33/PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

# 24.1 Module Introduction

The Peripheral Trigger Generator (PTG) provides a means to schedule complex high-speed peripheral operations that would be difficult to achieve using software. The PTG module uses 8-bit commands, called "Steps", that the user writes to the PTG Queue registers (PTGQUE0-PTGQUE7), which perform operations, such as wait for input signal, generate output trigger and wait for timer.

The PTG module has the following major features:

- Multiple clock sources

- Two 16-bit general purpose timers

- Two 16-bit general limit counters

- Configurable for rising or falling edge triggering

- Generates processor interrupts to include:

- Four configurable processor interrupts

- Interrupt on a Step event in Single-Step modeInterrupt on a PTG Watchdog Timer time-out

- Able to receive trigger signals from these peripherals:

- ADC

- PWM

- Output Compare

- Input Capture

- Op Amp/Comparator

- INT2

- Able to trigger or synchronize to these peripherals:

- Watchdog Timer

- Output Compare

- Input Capture

- ADC

- PWM

- Op Amp/Comparator

# dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### REGISTER 24-12: PTGQPTR: PTG STEP QUEUE POINTER REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | U-0   | U-0   | U-0         | U-0   | U-0   |

|--------|-----|-----|-------|-------|-------------|-------|-------|

| —      | —   | —   | —     | —     |             | _     | —     |

| bit 15 |     |     |       |       |             |       | bit 8 |

|        |     |     |       |       |             |       |       |

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0       | R/W-0 | R/W-0 |

| _      |     |     |       |       | PTGQPTR<4:0 | >     |       |

| bit 7  |     |     |       |       |             |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-5 Unimplemented: Read as '0'

bit 4-0 **PTGQPTR<4:0>:** PTG Step Queue Pointer Register bits This register points to the currently active Step command in the Step queue.

**Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

### **REGISTER 24-13: PTGQUEX: PTG STEP QUEUE REGISTER x (x = 0-7)**<sup>(1,3)</sup>

| R/W-0  | R/W-0 | R/W-0 | R/W-0     | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

|--------|-------|-------|-----------|----------------------|-------|-------|-------|

|        |       |       | STEP(2x + | - 1)<7:0> <b>(2)</b> |       |       |       |

| bit 15 |       |       |           |                      |       |       | bit 8 |

|        |       |       |           |                      |       |       |       |

| R/W-0  | R/W-0 | R/W-0 | R/W-0     | R/W-0                | R/W-0 | R/W-0 | R/W-0 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0                  | R/W-0 | R/W-0 | R/W-0 |

|-------|-------|-------|---------|------------------------|-------|-------|-------|

|       |       |       | STEP(2x | ()<7:0> <sup>(2)</sup> |       |       |       |

| bit 7 |       |       |         |                        |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-8 | STEP(2x + 1)<7:0>: PTG Step Queue Pointer Register bits <sup>(2)</sup> |

|----------|------------------------------------------------------------------------|

|          | A queue location for storage of the STEP(2x + 1) command byte.         |

| bit 7-0  | STEP(2x)<7:0>: PTG Step Queue Pointer Register bits <sup>(2)</sup>     |

|          | A queue location for storage of the STEP(2x) command byte.             |

- **Note 1:** This register is read-only when the PTG module is executing Step commands (PTGEN = 1 and PTGSTRT = 1).

- 2: Refer to Table 24-1 for the Step command encoding.

**3:** The Step registers maintain their values on any type of Reset.

| File<br>Name | Address          | Device<br>Memory<br>Size<br>(Kbytes) | Bits 23-8 | Bit 7                   | Bit 6                  | Bit 5   | Bit 4                   | Bit 3                   | Bit 2        | Bit 1     | Bit 0   |  |

|--------------|------------------|--------------------------------------|-----------|-------------------------|------------------------|---------|-------------------------|-------------------------|--------------|-----------|---------|--|

| Reserved     | 0057EC           | 32                                   |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 00AFEC           | 64                                   |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 0157EC           | 128                                  | _         | _                       | _                      | _       |                         | _                       | _            | _         | _       |  |

|              | 02AFEC           | 256                                  |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 0557EC           | 512                                  |           |                         |                        |         |                         |                         |              |           |         |  |

| Reserved     | 0057EE           | 32                                   |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 00AFEE           | 64                                   |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 0157EE           | 128                                  | _         | _                       | _                      | _       | _                       | _                       | _            | _         | _       |  |

|              | 02AFEE           | 256                                  |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 0557EE           | 512                                  |           |                         |                        |         |                         |                         |              |           |         |  |

| FICD         | 0057EE           | 32                                   |           |                         |                        |         |                         |                         |              |           |         |  |

| TIOD         | 00AFF0           | 64                                   |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 0157F0           | 128                                  | -         | Reserved <sup>(3)</sup> |                        | JTAGEN  | Reserved <sup>(2)</sup> | Reserved <sup>(3)</sup> |              | 1094      | 1.05    |  |

|              | 0137F0<br>02AFF0 | 256                                  |           | Reserveu                | _                      | JIAGEN  | Reserveu                | Reserveu                | _            | 1034      | S<1:0>  |  |

|              | 0557F0           | 512                                  | 4         |                         |                        |         |                         |                         |              |           |         |  |

| FROR         |                  |                                      |           |                         |                        |         |                         |                         |              |           |         |  |

| FPOR         | 0057F2           | 32                                   | -         |                         |                        |         |                         |                         |              |           |         |  |

|              | 00AFF2           | 64                                   | -         |                         |                        |         |                         | Reserved <sup>(3)</sup> |              |           |         |  |

|              | 0157F2           | 128                                  |           | VVDTV                   | VIN<1:0>               | ALTI2C2 | ALTI2C1                 | Reserved                | _            | _         | _       |  |

|              | 02AFF2           | 256                                  | 4         |                         |                        |         |                         |                         |              |           |         |  |

| EN DE        | 0557F2           | 512                                  |           |                         | r                      |         |                         |                         |              |           |         |  |

| FWDT         | 0057F4           | 32                                   | -         |                         |                        |         |                         |                         |              |           |         |  |

|              | 00AFF4           | 64                                   | -         |                         |                        |         |                         |                         |              |           |         |  |

|              | 0157F4           | 128                                  |           | FWDTEN                  | WINDIS                 | PLLKEN  | WDTPRE                  |                         | WDTPOST<3:0> |           |         |  |

|              | 02AFF4           | 256                                  | -         |                         |                        |         |                         |                         |              |           |         |  |

|              | 0557F4           | 512                                  |           |                         |                        |         |                         |                         |              |           |         |  |

| FOSC         | 0057F6           | 32                                   |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 00AFF6           | 64                                   | _         |                         |                        |         |                         |                         |              |           |         |  |

|              | 0157F6           | 128                                  | —         | FCKS                    | SM<1:0>                | IOL1WAY | —                       | —                       | OSCIOFNC     | POSCM     | iD<1:0> |  |

|              | 02AFF6           | 256                                  |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 0557F6           | 512                                  |           |                         |                        |         |                         |                         |              |           |         |  |

| FOSCSEL      | 0057F8           | 32                                   |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 00AFF8           | 64                                   |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 0157F8           | 128                                  | —         | IESO                    | PWMLOCK <sup>(1)</sup> | —       | —                       | -                       | F            | NOSC<2:0> |         |  |

|              | 02AFF8           | 256                                  |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 0557F8           | 512                                  |           |                         |                        |         |                         |                         |              |           |         |  |

| FGS          | 0057FA           | 32                                   |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 00AFFA           | 64                                   |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 0157FA           | 128                                  | _         | —                       | —                      | _       | —                       | —                       | —            | GCP       | GWRP    |  |

|              | 02AFFA           | 256                                  |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 0557FA           | 512                                  |           |                         |                        |         |                         |                         |              |           |         |  |

| Reserved     | 0057FC           | 32                                   |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 00AFFC           | 64                                   |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 0157FC           | 128                                  | _         | _                       | —                      | _       | —                       | _                       | _            | _         | —       |  |

|              | 02AFFC           | 256                                  |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 0557FC           | 512                                  |           |                         |                        |         |                         |                         |              |           |         |  |

| Reserved     | 057FFE           | 32                                   |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 00AFFE           | 64                                   |           |                         |                        |         |                         |                         |              |           |         |  |

|              |                  | 128                                  | _         | _                       | _                      | _       | _                       | _                       | _            | _         | _       |  |

| 1            | 015766           |                                      |           |                         |                        |         |                         |                         |              |           |         |  |

|              | 0157FE<br>02AFFE | 256                                  |           |                         |                        |         |                         |                         |              |           |         |  |

#### TABLE 27-1: CONFIGURATION BYTE REGISTER MAP

Legend: — = unimplemented, read as '1'.

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

**2:** This bit is reserved and must be programmed as '0'.

3: These bits are reserved and must be programmed as '1'.

| Bit Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCP                    | General Segment Code-Protect bit<br>1 = User program memory is not code-protected<br>0 = Code protection is enabled for the entire program memory space                                                                                                                                                                                                                                                                                     |

| GWRP                   | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                                                           |

| IESO                   | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Start up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start up device with user-selected oscillator source</li> </ul>                                                                                                                                                                                           |

| PWMLOCK <sup>(1)</sup> | PWM Lock Enable bit<br>1 = Certain PWM registers may only be written after a key sequence<br>0 = PWM registers may be written without a key sequence                                                                                                                                                                                                                                                                                        |

| FNOSC<2:0>             | Oscillator Selection bits<br>111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)<br>110 = Fast RC Oscillator with Divide-by-16 (FRCDIV16)<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved; do not use<br>011 = Primary Oscillator with PLL module (XT + PLL, HS + PLL, EC + PLL)<br>010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator with Divide-by-N with PLL module (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |

| FCKSM<1:0>             | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                                           |

| IOL1WAY                | Peripheral Pin Select Configuration bit<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                                                        |

| OSCIOFNC               | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is the clock output<br>0 = OSC2 is a general purpose digital I/O pin                                                                                                                                                                                                                                                                                                          |

| POSCMD<1:0>            | Primary Oscillator Mode Select bits<br>11 = Primary Oscillator is disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                                                           |

| FWDTEN                 | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled. Clearing the SWDTEN bit in the RCON register will have no effect.)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                                                                                                 |

| WINDIS                 | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                                                                              |

| PLLKEN                 | PLL Lock Enable bit<br>1 = PLL lock is enabled<br>0 = PLL lock is disabled<br>nly available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.                                                                                                                                                                                                                                                                                           |

#### TABLE 27-2: CONFIGURATION BITS DESCRIPTION

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

2: When JTAGEN = 1, an internal pull-up resistor is enabled on the TMS pin. Erased devices default to JTAGEN = 1. Applications requiring I/O pins in a high-impedance state (tri-state) in Reset should use pins other than TMS for this purpose.

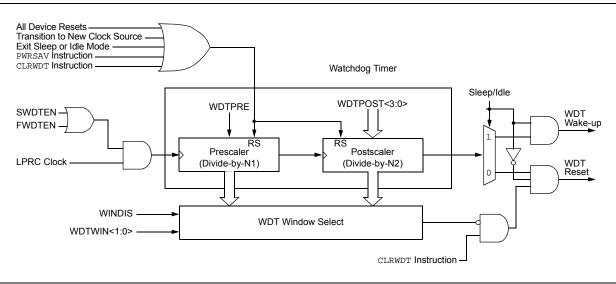

#### 27.5 Watchdog Timer (WDT)

For dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

#### 27.5.1 PRESCALER/POSTSCALER

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler that can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a WDT Timeout period (TWDT), as shown in Parameter SY12 in Table 30-22.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>), which allow the selection of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSCx bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

- Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

#### FIGURE 27-2: WDT BLOCK DIAGRAM

# 27.5.2 SLEEP AND IDLE MODES

If the WDT is enabled, it continues to run during Sleep or Idle modes. When the WDT time-out occurs, the device wakes the device and code execution continues from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bit (RCON<3,2>) needs to be cleared in software after the device wakes up.

## 27.5.3 ENABLING WDT

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user application to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

#### 27.5.4 WDT WINDOW

The Watchdog Timer has an optional Windowed mode, enabled by programming the WINDIS bit in the WDT Configuration register (FWDT<6>). In the Windowed mode (WINDIS = 0), the WDT should be cleared based on the settings in the programmable Watchdog Timer Window select bits (WDTWIN<1:0>).

# 29.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

#### 29.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- · Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

#### 29.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

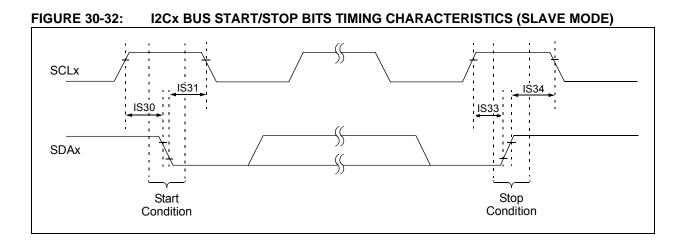

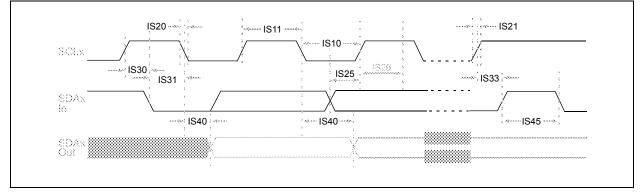

| AC CHA       | RACTER  | ISTICS           |                           | Standard Operatin<br>(unless otherwise<br>Operating tempera | stated)<br>iture -40 | )°C ≤ Ta ≤ | +85°C for Industrial   |

|--------------|---------|------------------|---------------------------|-------------------------------------------------------------|----------------------|------------|------------------------|

| Param<br>No. | Symbol  | Characte         | eristic <sup>(4)</sup>    | Min. <sup>(1)</sup>                                         | -40<br>Max.          | Units      | Conditions             |

| IM10         | TLO:SCL | Clock Low Time   | 100 kHz mode              | Tcy/2 (BRG + 2)                                             | _                    | μS         |                        |

|              |         |                  | 400 kHz mode              | TCY/2 (BRG + 2)                                             |                      | μS         |                        |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μs         |                        |

| IM11         | THI:SCL | Clock High Time  | 100 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μS         |                        |

|              |         | U U              | 400 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μ <b>S</b> |                        |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             |                      | μ <b>S</b> |                        |

| IM20         | TF:SCL  | SDAx and SCLx    | 100 kHz mode              |                                                             | 300                  | ns         | CB is specified to be  |

|              |         | Fall Time        | 400 kHz mode              | 20 + 0.1 Св                                                 | 300                  | ns         | from 10 to 400 pF      |

|              |         |                  | 1 MHz mode <sup>(2)</sup> |                                                             | 100                  | ns         | -                      |

| IM21         | TR:SCL  | SDAx and SCLx    | 100 kHz mode              |                                                             | 1000                 | ns         | CB is specified to be  |

|              |         | Rise Time        | 400 kHz mode              | 20 + 0.1 Св                                                 | 300                  | ns         | from 10 to 400 pF      |

|              |         |                  | 1 MHz mode <sup>(2)</sup> |                                                             | 300                  | ns         | -                      |

| IM25         | TSU:DAT | Data Input       | 100 kHz mode              | 250                                                         |                      | ns         |                        |

|              |         | Setup Time       | 400 kHz mode              | 100                                                         | _                    | ns         |                        |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 40                                                          |                      | ns         | -                      |

| IM26         | THD:DAT | Data Input       | 100 kHz mode              | 0                                                           | _                    | μS         |                        |

|              |         | Hold Time        | 400 kHz mode              | 0                                                           | 0.9                  | μS         |                        |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 0.2                                                         |                      | μs         | -                      |

| IM30         | TSU:STA | Start Condition  | 100 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μ <b>S</b> | Only relevant for      |

|              |         | Setup Time       | 400 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μS         | Repeated Start         |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                             | _                    | μs         | condition              |

| IM31         | THD:STA | Start Condition  | 100 kHz mode              | Tcy/2 (BRG + 2)                                             |                      | μ <b>s</b> | After this period, the |

|              |         | Hold Time        | 400 kHz mode              | Tcy/2 (BRG +2)                                              |                      | μS         | first clock pulse is   |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | Tcy/2 (BRG + 2)                                             | _                    | μS         | generated              |

| IM33         | Tsu:sto | Stop Condition   | 100 kHz mode              | Tcy/2 (BRG + 2)                                             | _                    | μs         |                        |

|              |         | Setup Time       | 400 kHz mode              | Tcy/2 (BRG + 2)                                             | _                    | μs         | 1                      |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             | —                    | μS         |                        |

| IM34         | THD:STO | Stop Condition   | 100 kHz mode              | Tcy/2 (BRG + 2)                                             | _                    | μs         |                        |

|              |         | Hold Time        | 400 kHz mode              | Tcy/2 (BRG + 2)                                             | —                    | μS         |                        |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | TCY/2 (BRG + 2)                                             | —                    | μS         |                        |

| IM40         | TAA:SCL | Output Valid     | 100 kHz mode              |                                                             | 3500                 | ns         |                        |

|              |         | From Clock       | 400 kHz mode              | —                                                           | 1000                 | ns         | İ.                     |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | —                                                           | 400                  | ns         | İ.                     |

| IM45         | TBF:SDA | Bus Free Time    | 100 kHz mode              | 4.7                                                         | —                    | μs         | Time the bus must be   |

|              |         |                  | 400 kHz mode              | 1.3                                                         | _                    | μ <b>s</b> | free before a new      |

|              |         |                  | 1 MHz mode <sup>(2)</sup> | 0.5                                                         | _                    | μ <b>s</b> | transmission can star  |

| IM50         | Св      | Bus Capacitive L |                           | _                                                           | 400                  | pF         |                        |

| IM51         | TPGD    | Pulse Gobbler De | -                         | 65                                                          | 390                  | ns         | (Note 3)               |

#### TABLE 30-49: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

Note 1: BRG is the value of the l<sup>2</sup>C<sup>™</sup> Baud Rate Generator. Refer to "Inter-Integrated Circuit (l<sup>2</sup>C<sup>™</sup>)" (DS70330) in the "dsPIC33/PIC24 Family Reference Manual". Please see the Microchip web site for the latest family reference manual sections.

- 2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

- **3:** Typical value for this parameter is 130 ns.

- 4: These parameters are characterized, but not tested in manufacturing.

NOTES:

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information: