Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 35                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | · ·                                                                              |

| RAM Size                   | 4K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 9x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 44-VFTLA Exposed Pad                                                             |

| Supplier Device Package    | 44-VTLA (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc204t-e-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

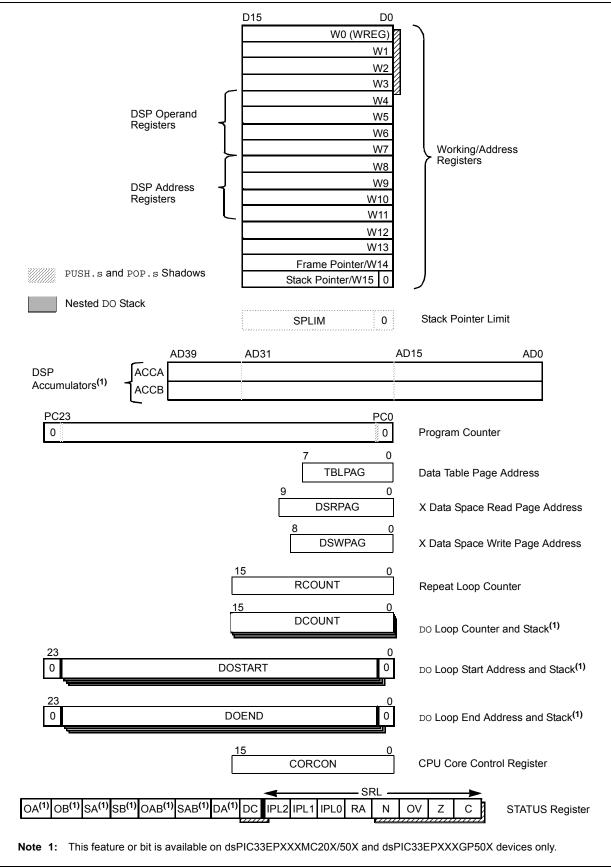

### 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X. dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for digital signal processing. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space.

An instruction prefetch mechanism helps maintain throughput and provides predictable execution. Most instructions execute in a single-cycle effective execution rate, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction, PSV accesses and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

### 3.1 Registers

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16th working register (W15) operates as a Software Stack Pointer for interrupts and calls.

### 3.2 Instruction Set

The instruction set for dsPIC33EPXXXGP50X and dsPIC33EPXXXMC20X/50X devices has two classes of instructions: the MCU class of instructions and the DSP class of instructions. The instruction set for PIC24EPXXXGP/MC20X devices has the MCU class of instructions only and does not support DSP instructions. These two instruction classes are seamlessly integrated into the architecture and execute from a single execution unit. The instruction set includes many addressing modes and was designed for optimum C compiler efficiency.

### 3.3 Data Space Addressing

The base Data Space can be addressed as 64 Kbytes (32K words).

The Data Space includes two ranges of memory, referred to as X and Y data memory. Each memory range is accessible through its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear Data Space. On dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y Data Spaces have memory locations that are device-specific, and are described further in the data memory maps in **Section 4.2 "Data Address Space"**.

The upper 32 Kbytes of the Data Space memory map can optionally be mapped into Program Space (PS) at any 32-Kbyte aligned program word boundary. The Program-to-Data Space mapping feature, known as Program Space Visibility (PSV), lets any instruction access Program Space as if it were Data Space. Moreover, the Base Data Space address is used in conjunction with a Read or Write Page register (DSRPAG or DSWPAG) to form an Extended Data Space (EDS) address. The EDS can be addressed as 8M words or 16 Mbytes. Refer to the "**Data Memory**" (DS70595) and "**Program Memory**" (DS70613) sections in the "*dsPIC33/PIC24 Family Reference Manual*" for more details on EDS, PSV and table accesses.

On the dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices, overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. The X AGU Circular Addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data re-ordering for radix-2 FFT algorithms. PIC24EPXXXGP/MC20X devices do not support Modulo and Bit-Reversed Addressing.

### 3.4 Addressing Modes

The CPU supports these addressing modes:

- Inherent (no operand)

- Relative

- Literal

- · Memory Direct

- Register Direct

- Register Indirect

Each instruction is associated with a predefined addressing mode group, depending upon its functional requirements. As many as six addressing modes are supported for each instruction.

### REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

| bit 2 | SFA: Stack Frame Active Status bit                                                        |

|-------|-------------------------------------------------------------------------------------------|

|       | 1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG and |

|       | DSWPAG values                                                                             |

|       | 0 = Stack frame is not active; W14 and W15 address of EDS or Base Data Space              |

| hit 1 | PND: Dounding Mode Select hit(1)                                                          |

- bit 1 **RND:** Rounding Mode Select bit<sup>(1)</sup>

- 1 = Biased (conventional) rounding is enabled

- 0 = Unbiased (convergent) rounding is enabled

bit 0 IF: Integer or Fractional Multiplier Mode Select bit<sup>(1)</sup> 1 = Integer mode is enabled for DSP multiply 0 = Fractional mode is enabled for DSP multiply

- Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

- **2:** This bit is always read as '0'.

- 3: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

### TABLE 4-45: DMAC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|---------|--------|--------|--------|---------------|

| DMA0CON   | 0B00  | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | _     | _      | _     | _     | AMOD  | E<1:0> | _       | _      | MODE   | <1:0>  | 0000          |

| DMA0REQ   | 0B02  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA0STAL  | 0B04  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STAH  | 0B06  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA0STBL  | 0B08  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STBH  | 0B0A  | _      | —      | _      | _      | _      | —      | —     | —      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA0PAD   | 0B0C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0CNT   | 0B0E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA1CON   | 0B10  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | —      | —     | —      | _     | —     | AMOD  | E<1:0> | —       | _      | MODE   | <1:0>  | 0000          |

| DMA1REQ   | 0B12  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA1STAL  | 0B14  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STAH  | 0B16  | _      | —      | _      | _      | _      | _      | —     | —      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA1STBL  | 0B18  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STBH  | 0B1A  | _      | —      | _      | _      |        | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA1PAD   | 0B1C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1CNT   | 0B1E  | _      | —      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA2CON   | 0B20  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> |         | —      | MODE   | <1:0>  | 0000          |

| DMA2REQ   | 0B22  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA2STAL  | 0B24  |        |        |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STAH  | 0B26  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA2STBL  | 0B28  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STBH  | 0B2A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA2PAD   | 0B2C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2CNT   | 0B2E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA3CON   | 0B30  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> | -       | —      | MODE   | <1:0>  | 0000          |

| DMA3REQ   | 0B32  | FORCE  | _      | _      | _      | _      | _      | _     | _      |       |       |       | IRQSE  | L<7:0>  |        |        |        | 00FF          |

| DMA3STAL  | 0B34  |        |        |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STAH  | 0B36  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA3STBL  | 0B38  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STBH  | 0B3A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA3PAD   | 0B3C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3CNT   | 0B3E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMAPWC    | 0BF0  | —      | —      | —      | —      | —      | —      |       | _      | —     | —     |       | —      | PWCOL3  | PWCOL2 | PWCOL1 | PWCOL0 | 0000          |

| DMARQC    | 0BF2  | _      | —      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | RQCOL3  | RQCOL2 | RQCOL1 | RQCOL0 | 0000          |

| DMAPPS    | 0BF4  | _      | —      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | PPST3   | PPST2  | PPST1  | PPST0  | 0000          |

| DMALCA    | 0BF6  | _      | _      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      |         | LSTCH  | 1<3:0> |        | 000F          |

| DSADRL    | 0BF8  |        |        |        |        |        |        |       | DSADR< | 15:0> |       |       |        |         |        |        |        | 0000          |

| DSADRH    | 0BFA  | _      | —      | —      | —      | —      | —      | —     | —      |       |       |       | DSADR• | <23:16> |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

### TABLE 4-59: PORTA REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA        | 0E00  | _      | —      | _      | _      | _      | -      | _     | _     | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA        | 0E02  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | 0000          |

| LATA         | 0E04  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | LATA4  | LATA3  | LATA2  | LA1TA1 | LA0TA0 | 0000          |

| ODCA         | 0E06  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

| CNENA        | 0E08  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNIEA4 | CNIEA3 | CNIEA2 | CNIEA1 | CNIEA0 | 0000          |

| CNPUA        | 0E0A  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPUA4 | CNPUA3 | CNPUA2 | CNPUA1 | CNPUA0 | 0000          |

| CNPDA        | 0E0C  | _      | _      | _      | _      | _      | _      | _     |       | _     | _     | _     | CNPDA4 | CNPDA3 | CNPDA2 | CNPDA1 | CNPDA0 | 0000          |

| ANSELA       | 0E0E  | _      | —      | _      | —      | _      | _      | _     | _     | _     | _     | _     | ANSA4  | _      | _      | ANSA1  | ANSA0  | 0013          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-60: PORTB REGISTER MAP FOR PIC24EPXXXGP/MC202 AND dsPIC33EPXXXGP/MC202/502 DEVICES ONLY

| File<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB        | 0E10  | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB        | 0E12  | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB         | 0E14  | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB         | 0E16  | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

| CNENB        | 0E18  | CNIEB15 | CNIEB14 | CNIEB13 | CNIEB12 | CNIEB11 | CNIEB10 | CNIEB9 | CNIEB8 | CNIEB7 | CNIEB6 | CNIEB5 | CNIEB4 | CNIEB3 | CNIEB2 | CNIEB1 | CNIEB0 | 0000          |

| CNPUB        | 0E1A  | CNPUB15 | CNPUB14 | CNPUB13 | CNPUB12 | CNPUB11 | CNPUB10 | CNPUB9 | CNPUB8 | CNPUB7 | CNPUB6 | CNPUB5 | CNPUB4 | CNPUB3 | CNPUB2 | CNPUB1 | CNPUB0 | 0000          |

| CNPDB        | 0E1C  | CNPDB15 | CNPDB14 | CNPDB13 | CNPDB12 | CNPDB11 | CNPDB10 | CNPDB9 | CNPDB8 | CNPDB7 | CNPDB6 | CNPDB5 | CNPDB4 | CNPDB3 | CNPDB2 | CNPDB1 | CNPDB0 | 0000          |

| ANSELB       | 0E1E  | _       | _       | _       | _       | _       | _       | -      | ANSB8  | _      |        | _      | _      | ANSB3  | ANSB2  | ANSB1  | ANSB0  | 010F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### 4.5 Instruction Addressing Modes

The addressing modes shown in Table 4-63 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions differ from those in the other instruction types.

### 4.5.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire Data Space.

#### 4.5.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 <function> Operand 2

where Operand 1 is always a working register (that is, the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register fetched from data memory or a 5-bit literal. The result location can either be a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-Bit or 10-Bit Literal

- Note: Not all instructions support all the addressing modes given above. Individual instructions can support different subsets of these addressing modes.

### TABLE 4-63: FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                                           | Description                                                                                           |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                             |

| Register Direct                                           | The contents of a register are accessed directly.                                                     |

| Register Indirect                                         | The contents of Wn form the Effective Address (EA).                                                   |

| Register Indirect Post-Modified                           | The contents of Wn form the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.            |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                    |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                             |

| R/W-0                  | R/W-0                          | R/W-0                 | R/W-0                             | R/W-0                                | R/W-0                 | R/W-0                | R/W-0                |

|------------------------|--------------------------------|-----------------------|-----------------------------------|--------------------------------------|-----------------------|----------------------|----------------------|

| NSTDIS                 | OVAERR <sup>(1)</sup>          | OVBERR <sup>(1)</sup> | COVAERR <sup>(1)</sup>            | COVBERR <sup>(1)</sup>               | OVATE <sup>(1)</sup>  | OVBTE <sup>(1)</sup> | COVTE <sup>(1)</sup> |

| pit 15                 |                                |                       |                                   |                                      |                       |                      | bit 8                |

|                        |                                |                       |                                   |                                      |                       |                      |                      |

| R/W-0                  | R/W-0                          | R/W-0                 | R/W-0                             | R/W-0                                | R/W-0                 | R/W-0                | U-0                  |

| SFTACERR <sup>(1</sup> | ) DIV0ERR                      | DMACERR               | MATHERR                           | ADDRERR                              | STKERR                | OSCFAIL              | —                    |

| pit 7                  |                                |                       |                                   |                                      |                       |                      | bit 0                |

|                        |                                |                       |                                   |                                      |                       |                      |                      |

| _egend:                |                                |                       |                                   |                                      |                       |                      |                      |

| R = Readable           |                                | W = Writable          |                                   | U = Unimpleme                        |                       |                      |                      |

| n = Value at           | POR                            | '1' = Bit is set      |                                   | '0' = Bit is clear                   | ed                    | x = Bit is unk       | nown                 |

| bit 15                 | NSTDIS: Inte                   | errupt Nesting        | Disable hit                       |                                      |                       |                      |                      |

|                        |                                | nesting is disa       |                                   |                                      |                       |                      |                      |

|                        | •                              | nesting is ena        |                                   |                                      |                       |                      |                      |

| pit 14                 | -                              | -                     | Overflow Trap F                   | lag bit <sup>(1)</sup>               |                       |                      |                      |

|                        |                                |                       | erflow of Accur                   |                                      |                       |                      |                      |

|                        | =                              |                       | overflow of A                     |                                      |                       |                      |                      |

| pit 13                 |                                |                       | Overflow Trap F                   | •                                    |                       |                      |                      |

|                        |                                |                       | erflow of Accur                   |                                      |                       |                      |                      |

| pit 12                 | -                              |                       |                                   | Overflow Trap Fla                    | ag bit <sup>(1)</sup> |                      |                      |

|                        | 1 = Trap was                   | caused by ca          | tastrophic over                   | flow of Accumula                     | ator A                |                      |                      |

| pit 11                 |                                |                       |                                   | Overflow Trap Fla                    |                       |                      |                      |

|                        |                                |                       | •                                 | flow of Accumula                     | •                     |                      |                      |

|                        | =                              |                       | -                                 | overflow of Accur                    | nulator B             |                      |                      |

| pit 10                 |                                |                       | erflow Trap Ena                   | able bit <sup>(1)</sup>              |                       |                      |                      |

|                        | 1 = Trap ove<br>0 = Trap is d  | rflow of Accum        | ulator A                          |                                      |                       |                      |                      |

| pit 9                  | OVBTE: Acc                     | umulator B Ov         | erflow Trap En                    | able bit <sup>(1)</sup>              |                       |                      |                      |

|                        | 1 = Trap ove<br>0 = Trap is d  | rflow of Accum        | ulator B                          |                                      |                       |                      |                      |

| oit 8                  | COVTE: Cat                     | astrophic Over        | flow Trap Enat                    | ole bit <sup>(1)</sup>               |                       |                      |                      |

|                        | 1 = Trap on o<br>0 = Trap is d |                       | erflow of Accu                    | mulator A or B is                    | enabled               |                      |                      |

| oit 7                  | SFTACERR:                      | Shift Accumul         | ator Error Statu                  | us bit <sup>(1)</sup>                |                       |                      |                      |

|                        |                                | •                     | •                                 | alid accumulator<br>invalid accumula |                       |                      |                      |

| oit 6                  | DIV0ERR: D                     | ivide-by-Zero I       | Error Status bit                  |                                      |                       |                      |                      |

|                        |                                |                       | used by a divide<br>caused by a d |                                      |                       |                      |                      |

|                        | DMACERR:                       |                       |                                   | -                                    |                       |                      |                      |

| oit 5                  |                                |                       |                                   |                                      |                       |                      |                      |

### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

### 10.2.1 SLEEP MODE

The following occurs in Sleep mode:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate, since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals can continue to operate. This includes items such as the Input Change Notification (ICN) on the I/O ports or peripherals that use an external clock input.

- Any peripheral that requires the system clock source for its operation is disabled.

The device wakes up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

On wake-up from Sleep mode, the processor restarts with the same clock source that was active when Sleep mode was entered.

For optimal power savings, the internal regulator and the Flash regulator can be configured to go into Standby when Sleep mode is entered by clearing the VREGS (RCON<8>) and VREGSF (RCON<11>) bits (default configuration).

If the application requires a faster wake-up time, and can accept higher current requirements, the VREGS (RCON<8>) and VREGSF (RCON<11>) bits can be set to keep the internal regulator and the Flash regulator active during Sleep mode.

### 10.2.2 IDLE MODE

The following occurs in Idle mode:

- The CPU stops executing instructions.

- · The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device wakes from Idle mode on any of these events:

- · Any interrupt that is individually enabled

- Any device Reset

- · A WDT time-out

On wake-up from Idle mode, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction or the first instruction in the Interrupt Service Routine (ISR).

All peripherals also have the option to discontinue operation when Idle mode is entered to allow for increased power savings. This option is selectable in the control register of each peripheral; for example, the TSIDL bit in the Timer1 Control register (T1CON<13>).

### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

| REGISTE       | R 16-7: PWMC                            | CONX: PWMX (                               | CONTROL R      | EGISTER          |                      |                      |                     |

|---------------|-----------------------------------------|--------------------------------------------|----------------|------------------|----------------------|----------------------|---------------------|

| HS/HC-        | 0 HS/HC-0                               | HS/HC-0                                    | R/W-0          | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

| FLTSTAT       | -(1) CLSTAT <sup>(1)</sup>              | TRGSTAT                                    | FLTIEN         | CLIEN            | TRGIEN               | ITB <sup>(2)</sup>   | MDCS <sup>(2)</sup> |

| bit 15        | ·                                       | •                                          |                | ÷                |                      |                      | bit                 |

| R/W-0         | R/W-0                                   | R/W-0                                      | U-0            | R/W-0            | R/W-0                | R/W-0                | R/W-0               |

| DTC1          |                                         | DTCP <sup>(3)</sup>                        | 0-0            | MTBS             | CAM <sup>(2,4)</sup> | XPRES <sup>(5)</sup> | IUE <sup>(2)</sup>  |

| bit 7         | DICO                                    | DICE                                       | _              | INT DO           | CAIN                 | AFRES'               | bit                 |

|               |                                         |                                            |                |                  |                      |                      | <u> </u>            |

| Legend:       |                                         | HC = Hardware                              | Clearable bit  | HS = Hardwa      | are Settable bit     |                      |                     |

| R = Reada     | able bit                                | W = Writable bi                            | t              | U = Unimple      | mented bit, rea      | ıd as '0'            |                     |

| -n = Value    | at POR                                  | '1' = Bit is set                           |                | '0' = Bit is cle | eared                | x = Bit is unk       | nown                |

| bit 15        | ELTSTAT: ES                             | ult Interrupt Statu                        | is hit(1)      |                  |                      |                      |                     |

| DIL 15        |                                         | rrupt is pending                           |                |                  |                      |                      |                     |

|               |                                         | interrupt is pendi                         | ng             |                  |                      |                      |                     |

|               |                                         | ared by setting F                          |                |                  |                      |                      |                     |

| bit 14        |                                         | rent-Limit Interru                         | •              |                  |                      |                      |                     |

|               |                                         | mit interrupt is pe                        |                |                  |                      |                      |                     |

|               |                                         | nt-limit interrupt is<br>ared by setting C |                |                  |                      |                      |                     |

| bit 13        |                                         | igger Interrupt S                          |                |                  |                      |                      |                     |

|               |                                         | terrupt is pendin                          |                |                  |                      |                      |                     |

|               |                                         | r interrupt is pen                         |                |                  |                      |                      |                     |

|               |                                         | ared by setting T                          |                |                  |                      |                      |                     |

| bit 12        |                                         | t Interrupt Enable                         | e bit          |                  |                      |                      |                     |

|               |                                         | rrupt is enabled rrupt is disabled         | and the FLTS   | TAT bit is clear | ed                   |                      |                     |

| bit 11        |                                         | ent-Limit Interrup                         |                |                  | cu .                 |                      |                     |

|               |                                         | mit interrupt is er                        |                |                  |                      |                      |                     |

|               |                                         | mit interrupt is di                        |                | e CLSTAT bit is  | s cleared            |                      |                     |

| bit 10        | TRGIEN: Trig                            | ger Interrupt En                           | able bit       |                  |                      |                      |                     |

|               |                                         | event generates                            |                |                  | T hit is cleared     |                      |                     |

| bit 9         |                                         | vent interrupts ar<br>dent Time Base I     |                |                  | i bit is cleared     |                      |                     |

| DIL 9         |                                         | register provides                          |                | riad for this PM | VM generator         |                      |                     |

|               |                                         | egister provides f                         | •              |                  | •                    |                      |                     |

| bit 8         |                                         | er Duty Cycle Re                           |                |                  |                      |                      |                     |

|               |                                         | ister provides du<br>jister provides du    |                |                  |                      | r                    |                     |

| Note 1:       | Software must clea                      |                                            |                |                  | -                    |                      | t controller        |

| Note 1.<br>2: | These bits should                       | -                                          |                | -                | -                    | the interrup         |                     |

| 3:            | DTC<1:0> = 11 fo                        | -                                          |                | -                | -                    |                      |                     |

| 4:            | The Independent T<br>CAM bit is ignored | Time Base (ITB =                           |                | •                |                      | igned mode. If       | TTB = 0, the        |

| 5:            | To operate in Exter                     |                                            | t mode, the IT | B bit must be '  | 1' and the CLM       | 10D bit in the I     | FCLCONx             |

### REGISTER 16-7: PWMCONx: PWMx CONTROL REGISTER

5: To operate in External Period Reset mode, the ITB bit must be '1' and the CLMOD bit in the FCLCONx register must be '0'.

| U-0                   | U-0                                | HS, R/C-0                          | R/W-0            | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

|-----------------------|------------------------------------|------------------------------------|------------------|------------------|------------------|-----------------------|----------|

| _                     | —                                  | PCHEQIRQ                           | PCHEQIEN         | PCLEQIRQ         | PCLEQIEN         | POSOVIRQ              | POSOVIEN |

| bit 15                |                                    |                                    |                  |                  |                  |                       | bit 8    |

|                       |                                    |                                    |                  |                  |                  |                       |          |

| HS, R/C-0             | R/W-0                              | HS, R/C-0                          | R/W-0            | HS, R/C-0        | R/W-0            | HS, R/C-0             | R/W-0    |

| PCIIRQ <sup>(1)</sup> | PCIIEN                             | VELOVIRQ                           | VELOVIEN         | HOMIRQ           | HOMIEN           | IDXIRQ                | IDXIEN   |

| bit 7                 |                                    |                                    |                  |                  |                  |                       | bit 0    |

| r                     |                                    |                                    |                  |                  |                  |                       |          |

| Legend:               |                                    | HS = Hardware                      |                  | C = Clearable    |                  |                       |          |

| R = Readable I        |                                    | W = Writable b                     | bit              | •                | nented bit, rea  |                       |          |

| -n = Value at P       | OR                                 | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unkr       | iown     |

|                       |                                    |                                    |                  |                  |                  |                       |          |

| bit 15-14             | -                                  | ted: Read as '0                    |                  |                  |                  | .,                    |          |

| bit 13                |                                    | Position Counte                    | er Greater Tha   | n or Equal Cor   | npare Status b   | it                    |          |

|                       |                                    | T ≥ QEI1GEC<br>T < QEI1GEC         |                  |                  |                  |                       |          |

| bit 12                |                                    | Position Counte                    | r Greater Tha    | n or Equal Con   | npare Interrupt  | Enable bit            |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    | s disabled                         |                  |                  |                  |                       |          |

| bit 11                |                                    | Position Counte                    | r Less Than o    | r Equal Compa    | are Status bit   |                       |          |

|                       | 1 = POS1CN                         |                                    |                  |                  |                  |                       |          |

| bit 10                |                                    | Position Counte                    | r Less Than or   | - Equal Compa    | ire Interrunt En | ahla hit              |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 9                 | POSOVIRQ:                          | Position Counte                    | er Overflow Sta  | itus bit         |                  |                       |          |

|                       | 1 = Overflow                       |                                    |                  |                  |                  |                       |          |

|                       |                                    | ow has occurred                    |                  |                  |                  |                       |          |

| bit 8                 |                                    | Position Counte                    | r Overflow Inte  | errupt Enable b  | Dit              |                       |          |

|                       | 1 = Interrupt i<br>0 = Interrupt i |                                    |                  |                  |                  |                       |          |

| bit 7                 | •                                  | tion Counter (H                    | oming) Initializ | ation Process    | Complete Stat    | us bit <sup>(1)</sup> |          |

|                       |                                    | T was reinitialize                 | •                |                  | · · · · · · · ·  |                       |          |

|                       | 0 = POS1CN                         | T was not reiniti                  | alized           |                  |                  |                       |          |

| bit 6                 | PCIIEN: Posi                       | tion Counter (He                   | oming) Initializ | ation Process    | Complete inter   | rupt Enable bit       |          |

|                       | 1 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 5                 | 0 = Interrupt i                    |                                    | r Overflow Sta   | tuo hit          |                  |                       |          |

| DIL 5                 | 1 = Overflow                       | Velocity Counter                   | I Overnow Sta    |                  |                  |                       |          |

|                       |                                    | ow has not occu                    | irred            |                  |                  |                       |          |

| bit 4                 | VELOVIEN:                          | /elocity Counter                   | Overflow Inte    | rrupt Enable bi  | it               |                       |          |

|                       | 1 = Interrupt i                    | s enabled                          |                  |                  |                  |                       |          |

|                       | 0 = Interrupt i                    |                                    |                  |                  |                  |                       |          |

| bit 3                 |                                    | atus Flag for Ho                   |                  | us bit           |                  |                       |          |

|                       |                                    | ent has occurred<br>event has occu |                  |                  |                  |                       |          |

|                       |                                    |                                    |                  |                  |                  |                       |          |

### REGISTER 17-3: QEI1STAT: QEI1 STATUS REGISTER

**Note 1:** This status bit is only applicable to PIMOD<2:0> modes, '011' and '100'.

### REGISTER 17-13: QEI1LECH: QEI1 LESS THAN OR EQUAL COMPARE HIGH WORD REGISTER

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|-------------------|----------------|-----------------|-------|

|                 |       |                  | QEILE | C<31:24>          |                |                 |       |

| bit 15          |       |                  |       |                   |                |                 | bit 8 |

|                 |       |                  |       |                   |                |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|                 |       |                  | QEILE | C<23:16>          |                |                 |       |

| bit 7           |       |                  |       |                   |                |                 | bit 0 |

|                 |       |                  |       |                   |                |                 |       |

| Legend:         |       |                  |       |                   |                |                 |       |

| R = Readable    | bit   | W = Writable b   | bit   | U = Unimplem      | ented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is clea | red            | x = Bit is unkr | nown  |

bit 15-0 QEILEC<31:16>: High Word Used to Form 32-Bit Less Than or Equal Compare Register (QEI1LEC) bits

### REGISTER 17-14: QEI1LECL: QEI1 LESS THAN OR EQUAL COMPARE LOW WORD REGISTER

| R = Readable bitW = Writable bitn = Value at POR'1' = Bit is set |       |       | U = Unimplen<br>'0' = Bit is cle |          | ead as '0'<br>x = Bit is unknown |       |       |

|------------------------------------------------------------------|-------|-------|----------------------------------|----------|----------------------------------|-------|-------|

| Legend:                                                          |       |       |                                  |          |                                  |       |       |

|                                                                  |       |       |                                  |          |                                  |       |       |

| bit 7                                                            |       |       |                                  |          |                                  |       | bit   |

|                                                                  |       |       | QEIL                             | EC<7:0>  |                                  |       |       |

| R/W-0                                                            | R/W-0 | R/W-0 | R/W-0                            | R/W-0    | R/W-0                            | R/W-0 | R/W-0 |

| bit 15                                                           |       |       |                                  |          |                                  |       | bit   |

|                                                                  |       |       | QEILE                            | EC<15:8> |                                  |       |       |

| R/W-0                                                            | R/W-0 | R/W-0 | R/W-0                            | R/W-0    | R/W-0                            | R/W-0 | R/W-0 |

bit 15-0 QEILEC<15:0>: Low Word Used to Form 32-Bit Less Than or Equal Compare Register (QEI1LEC) bits

# **19.2** I<sup>2</sup>C Control Registers

#### REGISTER 19-1: I2CxCON: I2Cx CONTROL REGISTER

| R/W-0            | U-0                             | R/W-0                                                               | R/W-1, HC            | R/W-0                        | R/W-0             | R/W-0           | R/W-0          |  |  |  |  |  |

|------------------|---------------------------------|---------------------------------------------------------------------|----------------------|------------------------------|-------------------|-----------------|----------------|--|--|--|--|--|

| I2CEN            | —                               | I2CSIDL                                                             | SCLREL               | IPMIEN <sup>(1)</sup>        | A10M              | DISSLW          | SMEN           |  |  |  |  |  |

| bit 15           |                                 |                                                                     |                      |                              |                   |                 | bit 8          |  |  |  |  |  |

|                  |                                 |                                                                     |                      |                              |                   |                 |                |  |  |  |  |  |

| R/W-0            | R/W-0                           | R/W-0                                                               | R/W-0, HC            | R/W-0, HC                    | R/W-0, HC         | R/W-0, HC       | R/W-0, HC      |  |  |  |  |  |

| GCEN             | STREN                           | ACKDT                                                               | ACKEN                | RCEN                         | PEN               | RSEN            | SEN            |  |  |  |  |  |

| bit 7            |                                 |                                                                     |                      |                              |                   |                 | bit 0          |  |  |  |  |  |

| Legend:          |                                 | HC = Hardware                                                       | Clearable bit        |                              |                   |                 |                |  |  |  |  |  |

| R = Readab       | le bit                          | W = Writable bi                                                     |                      | U = Unimpler                 | mented bit, rea   | d as '0'        |                |  |  |  |  |  |

| -n = Value a     | It POR                          | '1' = Bit is set                                                    |                      | '0' = Bit is cle             |                   | x = Bit is unk  | nown           |  |  |  |  |  |

|                  |                                 |                                                                     |                      |                              |                   |                 |                |  |  |  |  |  |

| bit 15           | I2CEN: I2Cx                     | Enable bit                                                          |                      |                              |                   |                 |                |  |  |  |  |  |

|                  |                                 | the I2Cx module                                                     |                      |                              |                   |                 | ;              |  |  |  |  |  |

| L:1 4 4          |                                 | the I2Cx module                                                     | ; all I-C ™ pins a   | are controlled               | by port function  | IS              |                |  |  |  |  |  |

| bit 14<br>bit 13 | -                               | ited: Read as '0'                                                   | do hit               |                              |                   |                 |                |  |  |  |  |  |

| DIC 13           |                                 | Stop in Idle Mo<br>ues module oper                                  |                      | rice enters an l             | dle mode          |                 |                |  |  |  |  |  |

|                  |                                 | s module operati                                                    |                      |                              |                   |                 |                |  |  |  |  |  |

| bit 12           | SCLREL: SC                      | Lx Release Con                                                      | rol bit (when op     | perating as I <sup>2</sup> C | slave)            |                 |                |  |  |  |  |  |

|                  |                                 | 1 = Releases SCLx clock<br>0 = Holds SCLx clock low (clock stretch) |                      |                              |                   |                 |                |  |  |  |  |  |

|                  |                                 | -                                                                   | ck stretch)          |                              |                   |                 |                |  |  |  |  |  |

|                  | If STREN = 1<br>Bit is R/W (i e | <u>.:</u><br>e., software can w                                     | rite '0' to initiate | e stretch and w              | rite '1' to relea | se clock) Harr  | lware is clear |  |  |  |  |  |

|                  | at the beginn                   | ing of every slav<br>reception. Hardv                               | ve data byte tra     | ansmission. Ha               | ardware is clea   | r at the end o  |                |  |  |  |  |  |

|                  | If STREN = 0                    |                                                                     |                      |                              |                   |                 |                |  |  |  |  |  |

|                  |                                 | ., software can or                                                  |                      |                              |                   |                 |                |  |  |  |  |  |

| hit 11           | -                               | te transmission.<br>Iligent Peripheral                              |                      |                              | -                 | address byte re | eception.      |  |  |  |  |  |

| bit 11           |                                 | le is enabled; all                                                  |                      |                              |                   |                 |                |  |  |  |  |  |

|                  | $0 = IPMI \mod$                 |                                                                     |                      | , lon no me agea             |                   |                 |                |  |  |  |  |  |

| bit 10           | A10M: 10-Bit                    | Slave Address b                                                     | oit                  |                              |                   |                 |                |  |  |  |  |  |

|                  |                                 | is a 10-bit slave                                                   |                      |                              |                   |                 |                |  |  |  |  |  |

|                  |                                 | is a 7-bit slave a                                                  |                      |                              |                   |                 |                |  |  |  |  |  |

| bit 9            |                                 | able Slew Rate (                                                    |                      |                              |                   |                 |                |  |  |  |  |  |

|                  |                                 | control is disable<br>control is enable                             |                      |                              |                   |                 |                |  |  |  |  |  |

| bit 8            |                                 | us Input Levels b                                                   |                      |                              |                   |                 |                |  |  |  |  |  |

|                  |                                 | /O pin thresholds                                                   |                      | SMBus speci                  | fication          |                 |                |  |  |  |  |  |

|                  |                                 | SMBus input thre                                                    |                      | ,                            |                   |                 |                |  |  |  |  |  |

| bit 7            | GCEN: Gene                      | eral Call Enable b                                                  | it (when operat      | ing as I <sup>2</sup> C slav | /e)               |                 |                |  |  |  |  |  |

|                  |                                 | nterrupt when a ge<br>call address disal                            |                      | ss is received ir            | n I2CxRSR (mo     | dule is enabled | for reception) |  |  |  |  |  |

|                  |                                 |                                                                     |                      |                              |                   |                 |                |  |  |  |  |  |

Note 1: When performing master operations, ensure that the IPMIEN bit is set to '0'.

| R/W-0                               | R/W-0    | R/W-0            | U-0             | R/W-0, HC                               | R/W-0                | R-0   | R-1   |

|-------------------------------------|----------|------------------|-----------------|-----------------------------------------|----------------------|-------|-------|

| UTXISEL1                            | UTXINV   | UTXISEL0         | —               | UTXBRK                                  | UTXEN <sup>(1)</sup> | UTXBF | TRMT  |

| bit 15                              |          |                  |                 |                                         |                      |       | bit 8 |

|                                     |          |                  |                 |                                         |                      |       |       |

| R/W-0                               | R/W-0    | R/W-0            | R-1             | R-0                                     | R-0                  | R/C-0 | R-0   |

| URXISEL1                            | URXISEL0 | ADDEN            | RIDLE           | PERR                                    | FERR                 | OERR  | URXDA |

| bit 7                               |          |                  |                 |                                         |                      |       | bit C |

|                                     |          |                  |                 |                                         |                      |       |       |

| Legend: HC = Hardware Clearable bit |          |                  | e Clearable bit | C = Clearable bit                       |                      |       |       |

| R = Readable                        | e bit    | W = Writable bit |                 | U = Unimplemented bit, read as '0'      |                      |       |       |

| -n = Value at                       | POR      | '1' = Bit is set |                 | '0' = Bit is cleared x = Bit is unknown |                      |       | nown  |

### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

bit 15,13 UTXISEL<1:0>: UARTx Transmission Interrupt Mode Selection bits

- 11 = Reserved; do not use

- 10 = Interrupt when a character is transferred to the Transmit Shift Register (TSR) and as a result, the transmit buffer becomes empty

- 01 = Interrupt when the last character is shifted out of the Transmit Shift Register; all transmit operations are completed

- 00 = Interrupt when a character is transferred to the Transmit Shift Register (this implies there is at least one character open in the transmit buffer)

- bit 14 UTXINV: UARTx Transmit Polarity Inversion bit

- $\frac{\text{If IREN = 0:}}{1 = \text{UxTX Idle state is '0'}}$

- 0 = UxTX Idle state is '1'

- If IREN = 1:

- 1 = IrDA encoded, UxTX Idle state is '1'

- 0 = IrDA encoded, UxTX Idle state is '0'

- bit 12 Unimplemented: Read as '0'

- bit 11 UTXBRK: UARTx Transmit Break bit

- 1 = Sends Sync Break on next transmission Start bit, followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Sync Break transmission is disabled or completed

- bit 10 UTXEN: UARTx Transmit Enable bit<sup>(1)</sup> 1 = Transmit is enabled, UxTX pin is controlled by UARTx

- 0 = Transmit is disabled, any pending transmission is aborted and buffer is reset; UxTX pin is controlled by the PORT

- bit 9 UTXBF: UARTx Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

- bit 8 TRMT: Transmit Shift Register Empty bit (read-only)

- 1 = Transmit Shift Register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit Shift Register is not empty, a transmission is in progress or queued

- bit 7-6 URXISEL<1:0>: UARTx Receive Interrupt Mode Selection bits

- 11 = Interrupt is set on UxRSR transfer, making the receive buffer full (i.e., has 4 data characters)

- 10 = Interrupt is set on UxRSR transfer, making the receive buffer 3/4 full (i.e., has 3 data characters)

- 0x = Interrupt is set when any character is received and transferred from the UxRSR to the receive buffer; receive buffer has one or more characters

- **Note 1:** Refer to the "**UART**" (DS70582) section in the "*dsPIC33/PIC24 Family Reference Manual*" for information on enabling the UARTx module for transmit operation.

| R-0 | R-0              | R-0                          | R-0                                                | R-0                                                                                            | R-0                                                                                       | R-0                                                                                                                  |  |

|-----|------------------|------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|

|     |                  | TERR                         | CNT<7:0>                                           |                                                                                                |                                                                                           |                                                                                                                      |  |

|     |                  |                              |                                                    |                                                                                                |                                                                                           | bit 8                                                                                                                |  |

|     |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |  |

| R-0 | R-0              | R-0                          | R-0                                                | R-0                                                                                            | R-0                                                                                       | R-0                                                                                                                  |  |

|     |                  | RERR                         | CNT<7:0>                                           |                                                                                                |                                                                                           |                                                                                                                      |  |

|     |                  |                              |                                                    |                                                                                                |                                                                                           | bit 0                                                                                                                |  |

|     |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |  |

|     |                  |                              |                                                    |                                                                                                |                                                                                           |                                                                                                                      |  |

| oit | W = Writable b   | it                           | U = Unimplemented bit, read as '0'                 |                                                                                                |                                                                                           |                                                                                                                      |  |

| OR  | '1' = Bit is set |                              | '0' = Bit is cleared x = Bit is unknow             |                                                                                                |                                                                                           | nown                                                                                                                 |  |

|     | R-0              | R-0 R-0<br>it W = Writable b | TERR<br>R-0 R-0 R-0<br>RERR<br>it W = Writable bit | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         RERRCNT<7:0> | TERRCNT<7:0>           R-0         R-0         R-0           RERRCNT<7:0>         RERRCNT | TERRCNT<7:0>         R-0       R-0       R-0       R-0         RERRCNT<7:0>       U = Unimplemented bit, read as '0' |  |

bit 7-0 **RERRCNT<7:0>:** Receive Error Count bits

### REGISTER 21-9: CxCFG1: ECANx BAUD RATE CONFIGURATION REGISTER 1

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| SJW1  | SJW0  | BRP5  | BRP4  | BRP3  | BRP2  | BRP1  | BRP0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-8 | Unimplemented: Read as '0' |

|----------|----------------------------|

|----------|----------------------------|

| bit 7-6 | SJW<1:0>: Synchronization Jump Width bits    |

|---------|----------------------------------------------|

|         | 11 = Length is 4 x TQ                        |

|         | $10 = \text{Length is } 3 \times \text{Tq}$  |

|         | $01 = \text{Length is } 2 \times \text{T} Q$ |

|         | $00 = \text{Length is } 1 \times \text{Tq}$  |

```

bit 5-0 BRP<5:0>: Baud Rate Prescaler bits

```

```

11 1111 = TQ = 2 x 64 x 1/FCAN

```

•

- 00 0010 = TQ = 2 x 3 x 1/FCAN 00 0001 = TQ = 2 x 2 x 1/FCAN

- 00 0000 = Tq = 2 x 1 x 1/FCAN