Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 70 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                   |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 4K x 16                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc206-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.5 **Programmer's Model**

The programmer's model for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X is shown in Figure 3-2. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions. Table 3-1 lists a description of each register.

In addition to the registers contained in the programmer's model, the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/

MC20X devices contain control registers for Modulo Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only), Bit-Reversed Addressing (dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only) and interrupts. These registers are described in subsequent sections of this document.

All registers associated with the programmer's model are memory mapped, as shown in Table 4-1.

| Register(s) Name                                      | Description                                               |

|-------------------------------------------------------|-----------------------------------------------------------|

| W0 through W15                                        | Working Register Array                                    |

| ACCA, ACCB                                            | 40-Bit DSP Accumulators                                   |

| PC                                                    | 23-Bit Program Counter                                    |

| SR                                                    | ALU and DSP Engine STATUS Register                        |

| SPLIM                                                 | Stack Pointer Limit Value Register                        |

| TBLPAG                                                | Table Memory Page Address Register                        |

| DSRPAG                                                | Extended Data Space (EDS) Read Page Register              |

| DSWPAG                                                | Extended Data Space (EDS) Write Page Register             |

| RCOUNT                                                | REPEAT Loop Count Register                                |

| DCOUNT <sup>(1)</sup>                                 | DO Loop Count Register                                    |

| DOSTARTH <sup>(1,2)</sup> , DOSTARTL <sup>(1,2)</sup> | DO Loop Start Address Register (High and Low)             |

| DOENDH <sup>(1)</sup> , DOENDL <sup>(1)</sup>         | DO Loop End Address Register (High and Low)               |

| CORCON                                                | Contains DSP Engine, DO Loop Control and Trap Status bits |

#### TABLE 3-1: PROGRAMMER'S MODEL REGISTER DESCRIPTIONS

Note 1: This register is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

2: The DOSTARTH and DOSTARTL registers are read-only.

## **REGISTER 3-1:** SR: CPU STATUS REGISTER (CONTINUED)

| bit 7-5       | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2,3)</sup><br>111 = CPU Interrupt Priority Level is 7 (15); user interrupts are disabled<br>110 = CPU Interrupt Priority Level is 6 (14)<br>101 = CPU Interrupt Priority Level is 5 (13)<br>100 = CPU Interrupt Priority Level is 4 (12)<br>011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)<br>001 = CPU Interrupt Priority Level is 1 (9)<br>000 = CPU Interrupt Priority Level is 0 (8) |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4         | RA: REPEAT Loop Active bit<br>1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 3         | N: MCU ALU Negative bit<br>1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                                                                                                                                                                                            |

| bit 2         | <ul> <li>OV: MCU ALU Overflow bit</li> <li>This bit is used for signed arithmetic (2's complement). It indicates an overflow of the magnitude that causes the sign bit to change state.</li> <li>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)</li> <li>0 = No overflow occurred</li> </ul>                                                                                                                                                                        |

| bit 1         | <ul> <li><b>Z:</b> MCU ALU Zero bit</li> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                                      |

| bit 0         | <b>C:</b> MCU ALU Carry/Borrow bit<br>1 = A carry-out from the Most Significant bit of the result occurred<br>0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                                                                                                                                             |

| Note 1:<br>2: | This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.<br>The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                                                                                                                                     |

- Level. The value in parentheses indicates the IPL, if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

3: The IPL<2:0> Status bits are read-only when the NSTDIS bit (INTCON1<15>) = 1.

- 4: A data write to the SR register can modify the SA and SB bits by either a data write to SA and SB or by clearing the SAB bit. To avoid a possible SA or SB bit write race condition, the SA and SB bits should not be modified using bit operations.

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

| bit 2 | SFA: Stack Frame Active Status bit                                                        |

|-------|-------------------------------------------------------------------------------------------|

|       | 1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG and |

|       | DSWPAG values                                                                             |

|       | 0 = Stack frame is not active; W14 and W15 address of EDS or Base Data Space              |

| hit 1 | PND: Dounding Mode Select hit(1)                                                          |

- bit 1 **RND:** Rounding Mode Select bit<sup>(1)</sup>

- 1 = Biased (conventional) rounding is enabled

- 0 = Unbiased (convergent) rounding is enabled

bit 0 IF: Integer or Fractional Multiplier Mode Select bit<sup>(1)</sup> 1 = Integer mode is enabled for DSP multiply 0 = Fractional mode is enabled for DSP multiply

- Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

- **2:** This bit is always read as '0'.

- 3: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXGP/MC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Program Memory" (DS70613) in the "dsPIC33/PIC24 Family Reference Manual', which is available from the Microchip web site (www.microchip.com).

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X architecture features separate program and data memory spaces, and buses. This architecture also allows the direct access of program memory from the Data Space (DS) during code execution.

## 4.1 Program Address Space

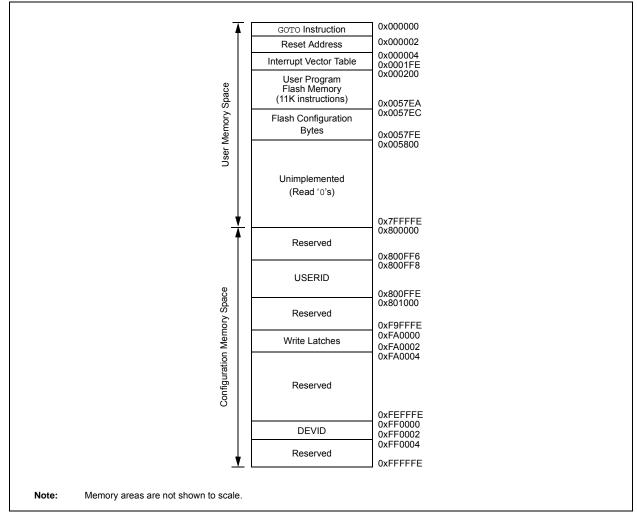

The program address memory space of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or Data Space remapping, as described in Section 4.8 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFF). The exception is the use of TBLRD operations, which use TBLPAG<7> to read Device ID sections of the configuration memory space.

The program memory maps, which are presented by device family and memory size, are shown in Figure 4-1 through Figure 4-5.

# FIGURE 4-1: PROGRAM MEMORY MAP FOR dsPIC33EP32GP50X, dsPIC33EP32MC20X/50X AND PIC24EP32GP/MC20X DEVICES

| TABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY |       |        |        |          |            |            |          |          |             | r      |        |            |          |        |        |        |        |               |

|------------------------------------------------------------------------------------------|-------|--------|--------|----------|------------|------------|----------|----------|-------------|--------|--------|------------|----------|--------|--------|--------|--------|---------------|

| File Name                                                                                | Addr. | Bit 15 | Bit 14 | Bit 13   | Bit 12     | Bit 11     | Bit 10   | Bit 9    | Bit 8       | Bit 7  | Bit 6  | Bit 5      | Bit 4    | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| QEI1CON                                                                                  | 01C0  | QEIEN  | —      | QEISIDL  |            | PIMOD<2:0> |          | IMV      | <1:0>       | -      |        | INTDIV<2:0 | >        | CNTPOL | GATEN  | CCM    | <1:0>  | 0000          |

| QEI1IOC                                                                                  | 01C2  | QCAPEN | FLTREN |          | QFDIV<2:0> |            | OUTFN    | NC<1:0>  | SWPAB       | HOMPOL | IDXPOL | QEBPOL     | QEAPOL   | HOME   | INDEX  | QEB    | QEA    | 000x          |

| <b>QEI1STAT</b>                                                                          | 01C4  | _      | _      | PCHEQIRQ | PCHEQIEN   | PCLEQIRQ   | PCLEQIEN | POSOVIRQ | POSOVIEN    | PCIIRQ | PCIIEN | VELOVIRQ   | VELOVIEN | HOMIRQ | HOMIEN | IDXIRQ | IDXIEN | 0000          |

| POS1CNTL                                                                                 | 01C6  |        |        |          |            |            |          |          | POSCNT<15   | :0>    |        |            |          |        |        |        |        | 0000          |

| POS1CNTH                                                                                 | 01C8  |        |        |          |            |            |          | ł        | POSCNT<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| POS1HLD                                                                                  | 01CA  |        |        |          |            |            |          |          | POSHLD<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| VEL1CNT                                                                                  | 01CC  |        |        |          |            |            |          |          | VELCNT<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| INT1TMRL                                                                                 | 01CE  |        |        |          |            |            |          |          | INTTMR<15:  | 0>     |        |            |          |        |        |        |        | 0000          |

| INT1TMRH                                                                                 | 01D0  |        |        |          |            |            |          |          | INTTMR<31:  | 6>     |        |            |          |        |        |        |        | 0000          |

| INT1HLDL                                                                                 | 01D2  |        |        |          |            |            |          |          | INTHLD<15:  | )>     |        |            |          |        |        |        |        | 0000          |

| INT1HLDH                                                                                 | 01D4  |        |        |          |            |            |          |          | INTHLD<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

| INDX1CNTL                                                                                | 01D6  |        |        |          |            |            |          |          | INDXCNT<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| INDX1CNTH                                                                                | 01D8  |        |        |          |            |            |          |          | NDXCNT<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| INDX1HLD                                                                                 | 01DA  |        |        |          |            |            |          |          | INDXHLD<15  | :0>    |        |            |          |        |        |        |        | 0000          |

| QEI1GECL                                                                                 | 01DC  |        |        |          |            |            |          |          | QEIGEC<15   | 0>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1ICL</b>                                                                           | 01DC  |        |        |          |            |            |          |          | QEIIC<15:0  | >      |        |            |          |        |        |        |        | 0000          |

| QEI1GECH                                                                                 | 01DE  |        |        |          |            |            |          |          | QEIGEC<31:  | 16>    |        |            |          |        |        |        |        | 0000          |

| QEI1ICH                                                                                  | 01DE  |        |        |          |            |            |          |          | QEIIC<31:16 | š>     |        |            |          |        |        |        |        | 0000          |

| QEI1LECL                                                                                 | 01E0  |        |        |          |            |            |          |          | QEILEC<15:  | )>     |        |            |          |        |        |        |        | 0000          |

| <b>QEI1LECH</b>                                                                          | 01E2  |        |        |          |            |            |          |          | QEILEC<31:1 | 6>     |        |            |          |        |        |        |        | 0000          |

TABLE 4-16: QEI1 REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND PIC24EPXXXMC20X DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 6.1 Reset Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the |

|-------|---------------------------------------------|

|       | product page using the link above, enter    |

|       | this URL in your browser:                   |

|       | http://www.microchip.com/wwwproducts/       |

|       | Devices.aspx?dDocName=en555464              |

#### 6.1.1 KEY RESOURCES

- "Reset" (DS70602) in the "dsPIC33/PIC24 Family Reference Manual"

- · Code Samples

- · Application Notes

- · Software Libraries

- Webinars

- All Related *"dsPIC33/PIC24 Family Reference Manual"* Sections

- Development Tools

NOTES:

## 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

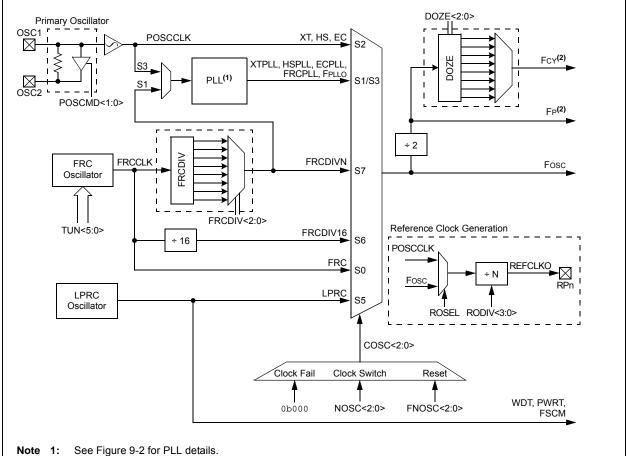

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

## FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

|                                    | REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3 |                |                   |              |                 |                |       |  |  |  |

|------------------------------------|-------------------------------------------------------------------|----------------|-------------------|--------------|-----------------|----------------|-------|--|--|--|

| U-0                                | U-0                                                               | U-0            | U-0               | U-0          | R/W-0           | U-0            | U-0   |  |  |  |

| —                                  | _                                                                 | —              | —                 | —            | CMPMD           | —              | —     |  |  |  |

| bit 15                             |                                                                   |                |                   |              |                 |                | bit 8 |  |  |  |

|                                    |                                                                   |                |                   |              |                 |                |       |  |  |  |

| R/W-0                              | U-0                                                               | U-0            | U-0               | U-0          | U-0             | R/W-0          | U-0   |  |  |  |

| CRCMD                              | —                                                                 | —              | _                 | —            | —               | I2C2MD         | —     |  |  |  |

| bit 7                              |                                                                   |                |                   |              |                 |                | bit C |  |  |  |

|                                    |                                                                   |                |                   |              |                 |                |       |  |  |  |

| Legend:                            |                                                                   |                |                   |              |                 |                |       |  |  |  |

| R = Readable                       | bit                                                               | W = Writable I | bit               | U = Unimplem | ented bit, read | l as '0'       |       |  |  |  |

| -n = Value at POR '1' = Bit is set |                                                                   |                | '0' = Bit is clea | ared         | x = Bit is unkn | Bit is unknown |       |  |  |  |

## REGISTER 10-3: PMD3: PERIPHERAL MODULE DISABLE CONTROL REGISTER 3

| bit 10  | CMPMD: Comparator Module Disable bit |

|---------|--------------------------------------|

|         | 1 = Comparator module is disabled    |

|         | 0 = Comparator module is enabled     |

| bit 9-8 | Unimplemented: Read as '0'           |

| bit 7   | CRCMD: CRC Module Disable bit        |

|         | 1 = CRC module is disabled           |

|         | 0 = CRC module is enabled            |

| bit 6-2 | Unimplemented: Read as '0'           |

| bit 1   | I2C2MD: I2C2 Module Disable bit      |

|         | 1 = I2C2 module is disabled          |

|         | 0 = I2C2 module is enabled           |

| bit 0   | Unimplemented: Read as '0'           |

|         |                                      |

#### REGISTER 10-4: PMD4: PERIPHERAL MODULE DISABLE CONTROL REGISTER 4

|        | -   |     |     |        |        |     |       |

|--------|-----|-----|-----|--------|--------|-----|-------|

| U-0    | U-0 | U-0 | U-0 | U-0    | U-0    | U-0 | U-0   |

| —      | —   |     |     | —      | —      | —   | —     |

| bit 15 |     |     |     |        |        |     | bit 8 |

|        |     |     |     |        |        |     |       |

| U-0    | U-0 | U-0 | U-0 | R/W-0  | R/W-0  | U-0 | U-0   |

| —      | —   | —   | —   | REFOMD | CTMUMD | —   | —     |

| bit 7  |     |     |     |        |        |     | bit 0 |

|        |     |     |     |        |        |     |       |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-4 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 3    | <b>REFOMD:</b> Reference Clock Module Disable bit          |

|          | <ol> <li>1 = Reference clock module is disabled</li> </ol> |

|          | 0 = Reference clock module is enabled                      |

| bit 2    | CTMUMD: CTMU Module Disable bit                            |

|          | 1 = CTMU module is disabled                                |

|          | 0 = CTMU module is enabled                                 |

| bit 1-0  | Unimplemented: Read as '0'                                 |

$\ensuremath{\textcircled{}^\circ}$  2011-2013 Microchip Technology Inc.

| REGISTER     | TU-5: PIVID6                                   | . PERIPHER       |                           | DISABLE C                          | UNIROL RE             | GISIER 6              |                       |  |

|--------------|------------------------------------------------|------------------|---------------------------|------------------------------------|-----------------------|-----------------------|-----------------------|--|

| U-0          | U-0                                            | U-0              | U-0                       | U-0                                | R/W-0                 | R/W-0                 | R/W-0                 |  |

| —            | —                                              | —                | —                         | _                                  | PWM3MD <sup>(1)</sup> | PWM2MD <sup>(1)</sup> | PWM1MD <sup>(1)</sup> |  |

| bit 15       |                                                |                  |                           |                                    |                       |                       | bit 8                 |  |

|              |                                                |                  |                           |                                    |                       |                       |                       |  |

| U-0          | U-0                                            | U-0              | U-0                       | U-0                                | U-0                   | U-0                   | U-0                   |  |

|              |                                                |                  |                           |                                    |                       |                       |                       |  |

| bit 7        |                                                |                  |                           |                                    |                       |                       | bit 0                 |  |

|              |                                                |                  |                           |                                    |                       |                       |                       |  |

| Legend:      |                                                |                  |                           |                                    |                       |                       |                       |  |

| R = Readab   | le bit                                         | W = Writable     | bit                       | U = Unimplemented bit, read as '0' |                       |                       |                       |  |

| -n = Value a | t POR                                          | '1' = Bit is set |                           | '0' = Bit is cleared               |                       | x = Bit is unknown    |                       |  |

|              |                                                |                  |                           |                                    |                       |                       |                       |  |

| bit 15-11    | Unimplement                                    | ted: Read as '   | כ'                        |                                    |                       |                       |                       |  |

| bit 10       | PWM3MD: P\                                     | NM3 Module D     | isable bit <sup>(1)</sup> |                                    |                       |                       |                       |  |

|              | 1 = PWM3 mo                                    | odule is disable | ed                        |                                    |                       |                       |                       |  |

|              | 0 = PWM3 mo                                    | odule is enable  | d                         |                                    |                       |                       |                       |  |

| bit 9        | PWM2MD: P\                                     | NM2 Module D     | isable bit <sup>(1)</sup> |                                    |                       |                       |                       |  |

|              | 1 = PWM2 module is disabled                    |                  | ed                        |                                    |                       |                       |                       |  |

|              | 0 = PWM2 mo                                    | odule is enable  | d                         |                                    |                       |                       |                       |  |

| bit 8        | PWM1MD: PWM1 Module Disable bit <sup>(1)</sup> |                  |                           |                                    |                       |                       |                       |  |

|              |                                                | odule is disable |                           |                                    |                       |                       |                       |  |

|              | 0 = PWM1 mo                                    | odule is enable  | d                         |                                    |                       |                       |                       |  |

| bit 7-0      | Unimplement                                    | ted: Read as '   | כ'                        |                                    |                       |                       |                       |  |

## REGISTER 10-5: PMD6: PERIPHERAL MODULE DISABLE CONTROL REGISTER 6

Note 1: This bit is available on dsPIC33EPXXXMC50X/20X and PIC24EPXXXMC20X devices only.

## REGISTER 11-26: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8

| U-0    | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | R/W-0 | R/W-0 |

|--------|-----|-------|-------|-------|---------|-------|-------|

| —      | —   |       |       | RP118 | 3R<5:0> |       |       |

| bit 15 |     |       |       |       |         |       | bit 8 |

|        |     |       |       |       |         |       |       |

| U-0    | U-0 | U-0   | U-0   | U-0   | U-0     | U-0   | U-0   |

| —      | —   |       | —     | _     | _       | —     | _     |

| bit 7  |     |       |       |       |         |       | bit 0 |

|        |     |       |       |       |         |       |       |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13-8  | <b>RP118R&lt;5:0&gt;:</b> Peripheral Output Function is Assigned to RP118 Output Pin bits (see Table 11-3 for peripheral function numbers) |

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 11-27: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | —   | —   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | R/W-0       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------------|-------|-------|-------|-------|-------|

| —     | —   | RP120R<5:0> |       |       |       |       |       |

| bit 7 |     |             |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-6 Unimplemented: Read as '0'

bit 5-0 **RP120R<5:0>:** Peripheral Output Function is Assigned to RP120 Output Pin bits (see Table 11-3 for peripheral function numbers)

## 24.3 PTG Control Registers

#### REGISTER 24-1: PTGCST: PTG CONTROL/STATUS REGISTER

| R/W-0      | U-0     | R/W-0   | R/W-0   | U-0 | R/W-0                 | R/W-0                  | R/W-0                  |  |

|------------|---------|---------|---------|-----|-----------------------|------------------------|------------------------|--|

| PTGEN      | —       | PTGSIDL | PTGTOGL | —   | PTGSWT <sup>(2)</sup> | PTGSSEN <sup>(3)</sup> | PTGIVIS                |  |

| bit 15 bit |         |         |         |     |                       |                        |                        |  |

|            |         |         |         |     |                       |                        |                        |  |

| R/W-0      | HS-0    | U-0     | U-0     | U-0 | U-0                   | R/W-0                  |                        |  |

| PTGSTRT    | PTGWDTO | _       | _       | _   | _                     | PTGITM1 <sup>(1)</sup> | PTGITM0 <sup>(1)</sup> |  |

| bit 7 |

|-------|

|-------|

| Legend:           | HS = Hardware Settable bi | t                           |                    |

|-------------------|---------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15  |       | PTGEN: Module Enable bit                                                                                                                                                                                                      |

|---------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |       | 1 = PTG module is enabled                                                                                                                                                                                                     |

|         |       | 0 = PTG module is disabled                                                                                                                                                                                                    |

| bit 14  |       | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 13  |       | PTGSIDL: PTG Stop in Idle Mode bit                                                                                                                                                                                            |

|         |       | <ul> <li>1 = Discontinues module operation when device enters Idle mode</li> <li>0 = Continues module operation in Idle mode</li> </ul>                                                                                       |

| bit 12  |       | PTGTOGL: PTG TRIG Output Toggle Mode bit                                                                                                                                                                                      |

|         |       | <ul> <li>1 = Toggle state of the PTGOx for each execution of the PTGTRIG command</li> <li>0 = Each execution of the PTGTRIG command will generate a single PTGOx pulse determined by the value in the PTGPWDx bits</li> </ul> |

| bit 11  |       | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| bit 10  |       | PTGSWT: PTG Software Trigger bit <sup>(2)</sup>                                                                                                                                                                               |

|         |       | 1 = Triggers the PTG module                                                                                                                                                                                                   |

|         |       | 0 = No action (clearing this bit will have no effect)                                                                                                                                                                         |

| bit 9   |       | PTGSSEN: PTG Enable Single-Step bit <sup>(3)</sup>                                                                                                                                                                            |

|         |       | 1 = Enables Single-Step mode                                                                                                                                                                                                  |

|         |       | 0 = Disables Single-Step mode                                                                                                                                                                                                 |

| bit 8   |       | PTGIVIS: PTG Counter/Timer Visibility Control bit                                                                                                                                                                             |

|         |       | 1 = Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the current values of their<br>corresponding counter/timer registers (PTGSD, PTGCx, PTGTx)                                                                   |

|         |       | <ul> <li>Reads of the PTGSDLIM, PTGCxLIM or PTGTxLIM registers return the value previously written<br/>to those limit registers</li> </ul>                                                                                    |

| bit 7   |       | PTGSTRT: PTG Start Sequencer bit                                                                                                                                                                                              |

|         |       | <ul><li>1 = Starts to sequentially execute commands (Continuous mode)</li><li>0 = Stops executing commands</li></ul>                                                                                                          |

| bit 6   |       | PTGWDTO: PTG Watchdog Timer Time-out Status bit                                                                                                                                                                               |

|         |       | 1 = PTG Watchdog Timer has timed out                                                                                                                                                                                          |

|         |       | 0 = PTG Watchdog Timer has not timed out.                                                                                                                                                                                     |

| bit 5-2 |       | Unimplemented: Read as '0'                                                                                                                                                                                                    |

| Note    | 1: Th | nese bits apply to the PTGWHI and PTGWLO commands only.                                                                                                                                                                       |

|         | 2: Th | is bit is only used with the PTGCTRL step command software trigger option.                                                                                                                                                    |

3: Use of the PTG Single-Step mode is reserved for debugging tools only.

bit 0

| bit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                                          |  |  |  |  |  |

|---------|------------------------|-------------|-------------------------------------------------------------|--|--|--|--|--|

|         | PTGWHI(1)              | 0000        | PWM Special Event Trigger. <sup>(3)</sup>                   |  |  |  |  |  |

|         | or (1)                 | 0001        | PWM master time base synchronization output. <sup>(3)</sup> |  |  |  |  |  |

|         | PTGWLO(1)              | 0010        | PWM1 interrupt. <sup>(3)</sup>                              |  |  |  |  |  |

|         |                        | 0011        | PWM2 interrupt. <sup>(3)</sup>                              |  |  |  |  |  |

|         |                        | 0100        | PWM3 interrupt. <sup>(3)</sup>                              |  |  |  |  |  |

|         |                        | 0101        | Reserved.                                                   |  |  |  |  |  |

|         |                        | 0110        | Reserved.                                                   |  |  |  |  |  |

|         |                        | 0111        | OC1 Trigger event.                                          |  |  |  |  |  |

|         |                        | 1000        | OC2 Trigger event.                                          |  |  |  |  |  |

|         |                        | 1001        | IC1 Trigger event.                                          |  |  |  |  |  |

|         |                        | 1010        | CMP1 Trigger event.                                         |  |  |  |  |  |

|         |                        | 1011        | CMP2 Trigger event.                                         |  |  |  |  |  |

|         |                        | 1100        | CMP3 Trigger event.                                         |  |  |  |  |  |

|         |                        | 1101        | CMP4 Trigger event.                                         |  |  |  |  |  |

|         |                        | 1110        | ADC conversion done interrupt.                              |  |  |  |  |  |

|         |                        | 1111        | INT2 external interrupt.                                    |  |  |  |  |  |

|         | PTGIRQ(1)              | 0000        | Generate PTG Interrupt 0.                                   |  |  |  |  |  |

|         |                        | 0001        | Generate PTG Interrupt 1.                                   |  |  |  |  |  |

|         |                        | 0010        | Generate PTG Interrupt 2.                                   |  |  |  |  |  |

|         |                        | 0011        | Generate PTG Interrupt 3.                                   |  |  |  |  |  |

|         |                        | 0100        | Reserved.                                                   |  |  |  |  |  |

|         |                        | •           | •                                                           |  |  |  |  |  |

|         |                        | •           | •                                                           |  |  |  |  |  |

|         |                        | •           | •                                                           |  |  |  |  |  |

|         | (2)                    | 1111        | Reserved.                                                   |  |  |  |  |  |

|         | PTGTRIG <sup>(2)</sup> | 00000       | PTGO0.                                                      |  |  |  |  |  |

|         |                        | 00001       | PTGO1.                                                      |  |  |  |  |  |

|         |                        | •           | •                                                           |  |  |  |  |  |

|         |                        | •           | •                                                           |  |  |  |  |  |

|         |                        | •           | •                                                           |  |  |  |  |  |

|         |                        | 11110       | PTGO30.                                                     |  |  |  |  |  |

|         |                        | 11111       | PTGO31.                                                     |  |  |  |  |  |

TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

| U-0          | U-0                           | U-0                                                                                 | U-0              | U-0              | U-0              | U-0            | U-0    |  |  |  |  |

|--------------|-------------------------------|-------------------------------------------------------------------------------------|------------------|------------------|------------------|----------------|--------|--|--|--|--|

|              | —                             | —                                                                                   | _                | —                |                  | —              | _      |  |  |  |  |

| bit 15       |                               |                                                                                     |                  |                  |                  |                | bit    |  |  |  |  |

|              |                               |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

| U-0          | R/W-0                         | R/W-0                                                                               | R/W-0            | R/W-0            | R/W-0            | R/W-0          | R/W-0  |  |  |  |  |

|              | CFSEL2                        | CFSEL1                                                                              | CFSEL0           | CFLTREN          | CFDIV2           | CFDIV1         | CFDIV0 |  |  |  |  |

| bit 7        |                               |                                                                                     |                  |                  |                  |                | bit    |  |  |  |  |

| Legend:      |                               |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

| R = Readab   | le bit                        | W = Writable                                                                        | bit              | U = Unimpler     | mented bit, read | as '0'         |        |  |  |  |  |

| -n = Value a |                               | '1' = Bit is set                                                                    |                  | '0' = Bit is cle |                  | x = Bit is unk | nown   |  |  |  |  |

|              |                               |                                                                                     |                  |                  |                  |                | -      |  |  |  |  |

| bit 15-7     | Unimplemen                    | ted: Read as                                                                        | ʻ0'              |                  |                  |                |        |  |  |  |  |

| oit 6-4      | CFSEL<2:0>                    | : Comparator                                                                        | Filter Input Clo | ock Select bits  |                  |                |        |  |  |  |  |

|              |                               | CFSEL<2:0>: Comparator Filter Input Clock Select bits<br>111 = T5CLK <sup>(1)</sup> |                  |                  |                  |                |        |  |  |  |  |

|              |                               | $110 = T4CLK^{(2)}$                                                                 |                  |                  |                  |                |        |  |  |  |  |

|              | 101 = T3CLK                   | $101 = T3CLK^{(1)}$                                                                 |                  |                  |                  |                |        |  |  |  |  |

|              | 100 = T2CLK                   | $100 = T2CLK^{(2)}$                                                                 |                  |                  |                  |                |        |  |  |  |  |

|              |                               | 011 = Reserved                                                                      |                  |                  |                  |                |        |  |  |  |  |

|              | 010 = SYNC                    | 01 <sup>(3)</sup>                                                                   |                  |                  |                  |                |        |  |  |  |  |

|              |                               | $001 = Fosc^{(4)}$                                                                  |                  |                  |                  |                |        |  |  |  |  |

|              | $000 = FP^{(4)}$              |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

| bit 3        |                               | CFLTREN: Comparator Filter Enable bit                                               |                  |                  |                  |                |        |  |  |  |  |

|              | 1 = Digital filter is enabled |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

|              | •                             | 0 = Digital filter is disabled                                                      |                  |                  |                  |                |        |  |  |  |  |

| bit 2-0      | CFDIV<2:0>:                   | : Comparator F                                                                      | ilter Clock Div  | vide Select bits |                  |                |        |  |  |  |  |

|              | 111 = Clock                   | Divide 1:128                                                                        |                  |                  |                  |                |        |  |  |  |  |

|              | 110 = Clock                   | Divide 1:64                                                                         |                  |                  |                  |                |        |  |  |  |  |

|              | 101 = Clock Divide 1:32       |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

|              | 100 = Clock                   | 100 = Clock Divide 1:16                                                             |                  |                  |                  |                |        |  |  |  |  |

|              | 011 = Clock Divide 1:8        |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

|              |                               | 010 = Clock Divide 1:4                                                              |                  |                  |                  |                |        |  |  |  |  |

|              | 001 = Clock                   |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

|              | 000 = Clock                   | Divide 1:1                                                                          |                  |                  |                  |                |        |  |  |  |  |

| Note 1: S    | See the Type C Ti             | mer Block Diag                                                                      | gram (Figure 1   | 3-2).            |                  |                |        |  |  |  |  |

|              | See the Type B Ti             |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

| •            |                               |                                                                                     |                  |                  |                  |                |        |  |  |  |  |

## REGISTER 25-6: CMxFLTR: COMPARATOR x FILTER CONTROL REGISTER

- 3: See the High-Speed PWMx Module Register Interconnection Diagram (Figure 16-2).

- 4: See the Oscillator System Diagram (Figure 9-1).

| Bit Field                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| GCP                          | General Segment Code-Protect bit<br>1 = User program memory is not code-protected<br>0 = Code protection is enabled for the entire program memory space                                                                                                                                                                                                                                                                                     |  |  |  |  |

| GWRP                         | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| IESO                         | <ul> <li>Two-Speed Oscillator Start-up Enable bit</li> <li>1 = Start up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start up device with user-selected oscillator source</li> </ul>                                                                                                                                                                                           |  |  |  |  |

| PWMLOCK <sup>(1)</sup>       | PWM Lock Enable bit<br>1 = Certain PWM registers may only be written after a key sequence<br>0 = PWM registers may be written without a key sequence                                                                                                                                                                                                                                                                                        |  |  |  |  |

| FNOSC<2:0>                   | Oscillator Selection bits<br>111 = Fast RC Oscillator with Divide-by-N (FRCDIVN)<br>110 = Fast RC Oscillator with Divide-by-16 (FRCDIV16)<br>101 = Low-Power RC Oscillator (LPRC)<br>100 = Reserved; do not use<br>011 = Primary Oscillator with PLL module (XT + PLL, HS + PLL, EC + PLL)<br>010 = Primary Oscillator (XT, HS, EC)<br>001 = Fast RC Oscillator with Divide-by-N with PLL module (FRCPLL)<br>000 = Fast RC Oscillator (FRC) |  |  |  |  |

| FCKSM<1:0>                   | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                                                           |  |  |  |  |

| IOL1WAY                      | Peripheral Pin Select Configuration bit<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| OSCIOFNC                     | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is the clock output<br>0 = OSC2 is a general purpose digital I/O pin                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| POSCMD<1:0>                  | Primary Oscillator Mode Select bits<br>11 = Primary Oscillator is disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                                                           |  |  |  |  |

| FWDTEN                       | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer is always enabled (LPRC oscillator cannot be disabled. Clearing the SWDTEN bit in the RCON register will have no effect.)</li> <li>0 = Watchdog Timer is enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                                                                                                 |  |  |  |  |

| WINDIS                       | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| PLLKEN Note 1: This bit is o | PLL Lock Enable bit<br>1 = PLL lock is enabled<br>0 = PLL lock is disabled                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

## TABLE 27-2: CONFIGURATION BITS DESCRIPTION

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

2: When JTAGEN = 1, an internal pull-up resistor is enabled on the TMS pin. Erased devices default to JTAGEN = 1. Applications requiring I/O pins in a high-impedance state (tri-state) in Reset should use pins other than TMS for this purpose.

| DC CHARACTERISTICS |                                        |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |                 |      |         |  |  |  |

|--------------------|----------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|---------|--|--|--|

| Parameter<br>No.   | Тур.                                   | Max. | Units                                                                                                                                                                                                                                                                                   | nits Conditions |      |         |  |  |  |

| Operating Cur      | Operating Current (IDD) <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                                         |                 |      |         |  |  |  |

| DC20d              | 9                                      | 15   | mA                                                                                                                                                                                                                                                                                      | -40°C           |      | 10 MIPS |  |  |  |

| DC20a              | 9                                      | 15   | mA                                                                                                                                                                                                                                                                                      | +25°C           | 3.3V |         |  |  |  |

| DC20b              | 9                                      | 15   | mA                                                                                                                                                                                                                                                                                      | +85°C           | 3.3V |         |  |  |  |

| DC20c              | 9                                      | 15   | mA                                                                                                                                                                                                                                                                                      | +125°C          |      |         |  |  |  |

| DC22d              | 16                                     | 25   | mA                                                                                                                                                                                                                                                                                      | -40°C           |      | 20 MIPS |  |  |  |

| DC22a              | 16                                     | 25   | mA                                                                                                                                                                                                                                                                                      | +25°C           | 3.3V |         |  |  |  |

| DC22b              | 16                                     | 25   | mA                                                                                                                                                                                                                                                                                      | +85°C           |      |         |  |  |  |

| DC22c              | 16                                     | 25   | mA                                                                                                                                                                                                                                                                                      | +125°C          |      |         |  |  |  |

| DC24d              | 27                                     | 40   | mA                                                                                                                                                                                                                                                                                      | -40°C           |      |         |  |  |  |

| DC24a              | 27                                     | 40   | mA                                                                                                                                                                                                                                                                                      | +25°C           | 3.3V | 40 MIPS |  |  |  |

| DC24b              | 27                                     | 40   | mA                                                                                                                                                                                                                                                                                      | +85°C           |      |         |  |  |  |

| DC24c              | 27                                     | 40   | mA                                                                                                                                                                                                                                                                                      | +125°C          |      |         |  |  |  |

| DC25d              | 36                                     | 55   | mA                                                                                                                                                                                                                                                                                      | -40°C           | 3.3V | 60 MIPS |  |  |  |

| DC25a              | 36                                     | 55   | mA                                                                                                                                                                                                                                                                                      | +25°C           |      |         |  |  |  |

| DC25b              | 36                                     | 55   | mA                                                                                                                                                                                                                                                                                      | +85°C           |      |         |  |  |  |

| DC25c              | 36                                     | 55   | mA                                                                                                                                                                                                                                                                                      | +125°C          | 7    |         |  |  |  |

| DC26d              | 41                                     | 60   | mA                                                                                                                                                                                                                                                                                      | -40°C           | 3.3V |         |  |  |  |

| DC26a              | 41                                     | 60   | mA                                                                                                                                                                                                                                                                                      | +25°C           |      | 70 MIPS |  |  |  |

| DC26b              | 41                                     | 60   | mA                                                                                                                                                                                                                                                                                      | +85°C           |      |         |  |  |  |

#### TABLE 30-6: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** IDD is primarily a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption. The test conditions for all IDD measurements are as follows:

• Oscillator is configured in EC mode with PLL, OSC1 is driven with external square wave from rail-to-rail (EC clock overshoot/undershoot < 250 mV required)

- · CLKO is configured as an I/O input pin in the Configuration Word

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD, WDT and FSCM are disabled

- CPU, SRAM, program memory and data memory are operational

- No peripheral modules are operating; however, every peripheral is being clocked (all PMDx bits are zeroed)

- CPU is executing while(1) {NOP(); } statement

- · JTAG is disabled

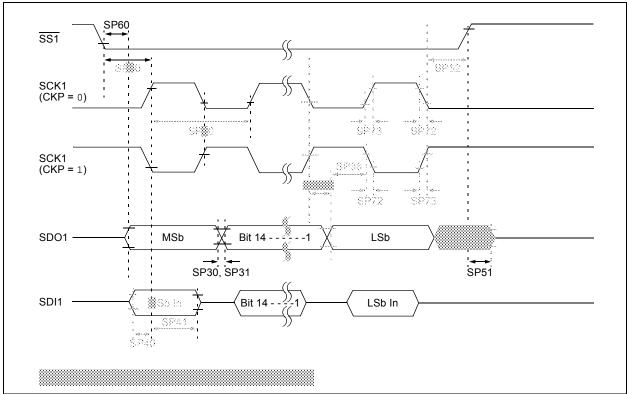

FIGURE 30-26: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

#### FIGURE 30-29: SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

## 33.0 PACKAGING INFORMATION

## 33.1 Package Marking Information

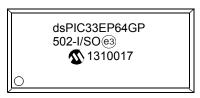

## 28-Lead SPDIP

#### 28-Lead SOIC (.300")

28-Lead SSOP

Example dsPIC33EP64GP 502-I/SP@3 1310017

## Example

#### Example

28-Lead QFN-S (6x6x0.9 mm)

Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                      | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|        | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                                |  |

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075