Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$= K \in$

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 4K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-VQFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc206t-e-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive resource. To complement the information in this data sheet, refer to the related section of the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com)

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This document contains device-specific information for the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X Digital Signal Controller (DSC) and Microcontroller (MCU) devices.

dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit MCU architecture.

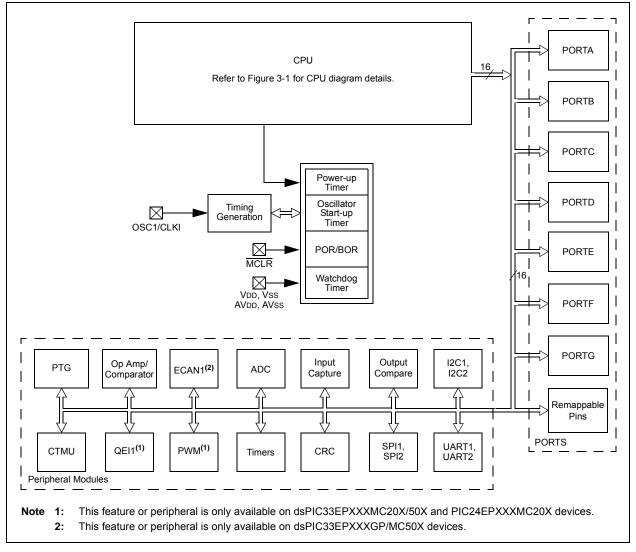

Figure 1-1 shows a general block diagram of the core and peripheral modules. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

#### FIGURE 1-1: dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X BLOCK DIAGRAM

## REGISTER 3-2: CORCON: CORE CONTROL REGISTER (CONTINUED)

| bit 2 | SFA: Stack Frame Active Status bit                                                        |

|-------|-------------------------------------------------------------------------------------------|

|       | 1 = Stack frame is active; W14 and W15 address 0x0000 to 0xFFFF, regardless of DSRPAG and |

|       | DSWPAG values                                                                             |

|       | 0 = Stack frame is not active; W14 and W15 address of EDS or Base Data Space              |

| hit 1 | PND: Dounding Mode Select hit(1)                                                          |

- bit 1 **RND:** Rounding Mode Select bit<sup>(1)</sup>

- 1 = Biased (conventional) rounding is enabled

- 0 = Unbiased (convergent) rounding is enabled

bit 0 IF: Integer or Fractional Multiplier Mode Select bit<sup>(1)</sup> 1 = Integer mode is enabled for DSP multiply 0 = Fractional mode is enabled for DSP multiply

- Note 1: This bit is available on dsPIC33EPXXXMC20X/50X and dsPIC33EPXXXGP50X devices only.

- **2:** This bit is always read as '0'.

- 3: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

## 4.4 Special Function Register Maps

## TABLE 4-1: CPU CORE REGISTER MAP FOR dsPIC33EPXXXMC20X/50X AND dsPIC33EPXXXGP50X DEVICES ONLY

|           |       | 0.00   |        |        |              | 011 401    |        |       | 20/00/      |        |       |        |         |          |          | -     | r     |               |

|-----------|-------|--------|--------|--------|--------------|------------|--------|-------|-------------|--------|-------|--------|---------|----------|----------|-------|-------|---------------|

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12       | Bit 11     | Bit 10 | Bit 9 | Bit 8       | Bit 7  | Bit 6 | Bit 5  | Bit 4   | Bit 3    | Bit 2    | Bit 1 | Bit 0 | All<br>Resets |

| W0        | 0000  |        |        |        |              |            |        |       | W0 (WR      | EG)    |       |        |         |          |          |       |       | xxxx          |

| W1        | 0002  |        |        |        |              |            |        |       | W1          |        |       |        |         |          |          |       |       | xxxx          |

| W2        | 0004  |        |        |        |              |            |        |       | W2          |        |       |        |         |          |          |       |       | xxxx          |

| W3        | 0006  |        |        |        |              |            |        |       | W3          |        |       |        |         |          |          |       |       | xxxx          |

| W4        | 8000  |        |        |        |              |            |        |       | W4          |        |       |        |         |          |          |       |       | xxxx          |

| W5        | 000A  |        |        |        |              |            |        |       | W5          |        |       |        |         |          |          |       |       | xxxx          |

| W6        | 000C  |        |        |        |              |            |        |       | W6          |        |       |        |         |          |          |       |       | xxxx          |

| W7        | 000E  |        |        |        |              |            |        |       | W7          |        |       |        |         |          |          |       |       | xxxx          |

| W8        | 0010  |        |        |        |              |            |        |       | W8          |        |       |        |         |          |          |       |       | xxxx          |

| W9        | 0012  |        |        |        |              |            |        |       | W9          |        |       |        |         |          |          |       |       | xxxx          |

| W10       | 0014  |        |        |        |              |            |        |       | W10         |        |       |        |         |          |          |       |       | xxxx          |

| W11       | 0016  |        |        |        |              |            |        |       | W11         |        |       |        |         |          |          |       |       | xxxx          |

| W12       | 0018  |        |        |        |              |            |        |       | W12         |        |       |        |         |          |          |       |       | xxxx          |

| W13       | 001A  |        |        |        |              |            |        |       | W13         |        |       |        |         |          |          |       |       | xxxx          |

| W14       | 001C  |        |        |        |              |            |        |       | W14         |        |       |        |         |          |          |       |       | xxxx          |

| W15       | 001E  |        |        |        |              |            |        |       | W15         |        |       |        |         |          |          |       |       | xxxx          |

| SPLIM     | 0020  |        |        |        |              |            |        |       | SPLI        | N      |       |        |         |          |          |       |       | 0000          |

| ACCAL     | 0022  |        |        |        |              |            |        |       | ACCA        | L      |       |        |         |          |          |       |       | 0000          |

| ACCAH     | 0024  |        |        |        |              |            |        |       | ACCA        | H      |       |        |         |          |          |       |       | 0000          |

| ACCAU     | 0026  |        |        | Si     | gn Extensior | n of ACCA< | 39>    |       |             |        |       |        | ACO     | CAU      |          |       |       | 0000          |

| ACCBL     | 0028  |        |        |        |              |            |        |       | ACCB        | L      |       |        |         |          |          |       |       | 0000          |

| ACCBH     | 002A  |        |        |        |              |            |        |       | ACCB        | Н      |       |        |         |          |          |       |       | 0000          |

| ACCBU     | 002C  |        |        | Si     | gn Extensior | n of ACCB< | 39>    |       |             |        |       |        | ACO     | CBU      |          |       |       | 0000          |

| PCL       | 002E  |        |        |        |              |            |        | F     | PCL<15:0>   |        |       |        |         |          |          |       |       | 0000          |

| PCH       | 0030  | _      | _      | _      | —            | _          | _      | —     | _           | _      |       |        |         | PCH<6:0> |          |       |       | 0000          |

| DSRPAG    | 0032  | _      | _      | _      | _            | _          | _      |       |             |        |       | DSRPAC | 6<9:0>  |          |          |       |       | 0001          |

| DSWPAG    | 0034  | _      |        | _      | —            |            | _      | _     |             |        |       | DS     | WPAG<8: | 0>       |          |       |       | 0001          |

| RCOUNT    | 0036  |        |        |        |              |            |        |       | RCOUNT<     | :15:0> |       |        |         |          |          |       |       | 0000          |

| DCOUNT    | 0038  |        |        |        |              |            |        |       | DCOUNT<     | :15:0> |       |        |         |          |          |       |       | 0000          |

| DOSTARTL  | 003A  |        |        |        |              |            |        | DOS   | STARTL<15:1 | >      |       |        |         |          |          |       |       | 0000          |

| DOSTARTH  | 003C  | _      | —      | —      | _            | —          | —      | _     | _           | _      | —     |        |         | DOSTAF   | RTH<5:0> |       |       | 0000          |

| DOENDL    | 003E  |        |        |        |              |            |        | DO    | ENDL<15:1>  | >      |       |        |         |          |          |       |       | 0000          |

| DOENDH    | 0040  | _      | —      | —      | —            | —          | —      | _     | —           | —      | —     |        |         | DOEND    | )H<5:0>  |       |       | 0000          |

|           |       |        |        |        |              |            |        |       |             |        |       |        |         |          |          |       |       |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4 | 4-31: | PER | IPHERA | L PIN S | ELECT | INPUT F | REGISTI | ER MAP | FOR de | sPIC33E | EPXXXG | P50X D | EVICES | SONLY |  |

|---------|-------|-----|--------|---------|-------|---------|---------|--------|--------|---------|--------|--------|--------|-------|--|

|         |       |     |        |         |       |         |         |        |        |         |        |        |        |       |  |

| File<br>Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|-------|--------|--------|--------|--------|------------|--------|-------|-------|-------|-------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0       | 06A0  | —      |        |        |        | INT1R<6:0> |        |       |       | _     | _     | —     | —     | —          | —     | —     | _     | 0000          |

| RPINR1       | 06A2  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       |       | INT2R<6:0> | •     |       |       | 0000          |

| RPINR3       | 06A6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ٦     | [2CKR<6:0  | >     |       |       | 0000          |

| RPINR7       | 06AE  |        |        |        |        | IC2R<6:0>  |        |       |       | _     |       |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8       | 06B0  |        |        |        |        | IC4R<6:0>  |        |       |       | _     |       |       |       | IC3R<6:0>  |       |       |       | 0000          |

| RPINR11      | 06B6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | (     | DCFAR<6:0  | >     |       |       | 0000          |

| RPINR18      | 06C4  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ι     | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19      | 06C6  |        | _      | _      | _      | _          | _      | _     | _     | _     |       |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22      | 06CC  |        |        |        | S      | CK2INR<6:0 | )>     |       |       | _     |       |       | :     | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23      | 06CE  | _      | _      | _      | —      | —          | _      | _     | —     | —     |       |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26      | 06D4  | —      | _      | _      | -      | _          | _      | —     |       | —     |       |       | (     | C1RXR<6:0  | >     |       |       | 0000          |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### **TABLE 4-32:** PERIPHERAL PIN SELECT INPUT REGISTER MAP FOR dsPIC33EPXXXMC50X DEVICES ONLY

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11     | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6          | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|------------|--------|-------|-------|-------|----------------|-------|-------|------------|-------|-------|-------|---------------|

| RPINR0    | 06A0  | _      |        |        |        | INT1R<6:0> |        |       |       | —     | —              | —     | —     | —          | —     | —     | _     | 0000          |

| RPINR1    | 06A2  |        | _      | _      | _      | _          | _      | _     | _     | _     |                |       |       | INT2R<6:0> |       |       |       | 0000          |

| RPINR3    | 06A6  |        | _      | _      | _      | _          | _      | _     | _     | _     |                |       | -     | F2CKR<6:0  | >     |       |       | 0000          |

| RPINR7    | 06AE  |        |        |        |        | IC2R<6:0>  |        |       |       | _     |                |       |       | IC1R<6:0>  |       |       |       | 0000          |

| RPINR8    | 06B0  |        |        |        |        | IC4R<6:0>  |        |       |       | _     | 10011-0.0      |       |       |            |       | 0000  |       |               |

| RPINR11   | 06B6  |        | _      | _      | _      | _          | _      | _     | _     | _     | OCFAR<6:0>     |       |       |            |       | 0000  |       |               |

| RPINR12   | 06B8  |        |        |        |        | FLT2R<6:0> | •      |       |       | _     |                |       |       |            | 0000  |       |       |               |

| RPINR14   | 06BC  |        |        |        | (      | QEB1R<6:0  | >      |       |       | _     |                |       | (     | QEA1R<6:0  | >     |       |       | 0000          |

| RPINR15   | 06BE  |        |        |        | Н      | OME1R<6:0  | )>     |       |       | _     |                |       | I     | NDX1R<6:0  | >     |       |       | 0000          |

| RPINR18   | 06C4  |        | _      | _      | _      | _          | _      | _     | _     | _     |                |       | ι     | J1RXR<6:0  | >     |       |       | 0000          |

| RPINR19   | 06C6  |        | _      | _      | _      | _          | _      | _     | _     | _     |                |       | ι     | J2RXR<6:0  | >     |       |       | 0000          |

| RPINR22   | 06CC  | _      |        |        | S      | CK2INR<6:( | )>     |       |       | —     |                |       |       | SDI2R<6:0> | •     |       |       | 0000          |

| RPINR23   | 06CE  | _      | —      | —      |        | —          | —      |       | —     | —     |                |       |       | SS2R<6:0>  |       |       |       | 0000          |

| RPINR26   | 06D4  | _      | _      | _      |        | —          | —      |       | —     | —     | - C1RXR<6:0>   |       |       |            |       | 0000  |       |               |

| RPINR37   | 06EA  | _      |        |        | S      | YNCI1R<6:0 | )>     |       |       | —     | —              | —     | —     | —          |       |       |       | 0000          |

| RPINR38   | 06EC  | _      |        |        | D      | CMP1R<6:   | 0>     |       |       | —     |                |       |       |            | 0000  |       |       |               |

| RPINR39   | 06EE  | _      |        |        | D      | FCMP3R<6:  | 0>     |       |       | _     | - DTCMP2R<6:0> |       |       |            |       | 0000  |       |               |

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X AND PIC24EPXXXGP/MC20X

#### TABLE 4-45: DMAC REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|-------|--------|--------|--------|--------|--------|--------|-------|--------|-------|-------|-------|--------|---------|--------|--------|--------|---------------|

| DMA0CON   | 0B00  | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | _     | _      | _     | _     | AMOD  | E<1:0> | _       | _      | MODE   | <1:0>  | 0000          |

| DMA0REQ   | 0B02  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA0STAL  | 0B04  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STAH  | 0B06  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA0STBL  | 0B08  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0STBH  | 0B0A  | _      | —      | —      | _      | _      | —      | —     | —      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA0PAD   | 0B0C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA0CNT   | 0B0E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA1CON   | 0B10  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | —      | —     | —      | _     | —     | AMOD  | E<1:0> | —       | _      | MODE   | <1:0>  | 0000          |

| DMA1REQ   | 0B12  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA1STAL  | 0B14  |        |        |        |        |        |        |       | STA<15 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STAH  | 0B16  | _      | —      | —      | _      | _      | —      | —     | —      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA1STBL  | 0B18  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1STBH  | 0B1A  | _      | —      | _      | _      |        | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA1PAD   | 0B1C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA1CNT   | 0B1E  | _      | —      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA2CON   | 0B20  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> |         | —      | MODE   | <1:0>  | 0000          |

| DMA2REQ   | 0B22  | FORCE  | _      | _      |        | _      | _      | _     | _      |       |       |       | IRQSE  | _<7:0>  | •      |        |        | 00FF          |

| DMA2STAL  | 0B24  |        |        |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STAH  | 0B26  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA2STBL  | 0B28  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2STBH  | 0B2A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA2PAD   | 0B2C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA2CNT   | 0B2E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMA3CON   | 0B30  | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _      | _     | _     | AMOD  | E<1:0> | -       | —      | MODE   | <1:0>  | 0000          |

| DMA3REQ   | 0B32  | FORCE  | _      | _      | _      | _      | _      | _     | _      |       |       |       | IRQSE  | L<7:0>  |        |        |        | 00FF          |

| DMA3STAL  | 0B34  |        |        |        |        |        |        |       | STA<18 | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STAH  | 0B36  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STA<2  | 3:16>   |        |        |        | 0000          |

| DMA3STBL  | 0B38  |        |        |        |        |        |        |       | STB<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3STBH  | 0B3A  | _      | _      | _      | _      | _      | _      | _     | _      |       |       |       | STB<2  | 3:16>   |        |        |        | 0000          |

| DMA3PAD   | 0B3C  |        |        |        |        |        |        |       | PAD<1  | 5:0>  |       |       |        |         |        |        |        | 0000          |

| DMA3CNT   | 0B3E  | _      | _      |        |        |        |        |       |        | CNT<1 | 3:0>  |       |        |         |        |        |        | 0000          |

| DMAPWC    | 0BF0  | _      | —      | —      | —      | —      | —      |       | _      | —     | —     |       | —      | PWCOL3  | PWCOL2 | PWCOL1 | PWCOL0 | 0000          |

| DMARQC    | 0BF2  | _      | —      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | RQCOL3  | RQCOL2 | RQCOL1 | RQCOL0 | 0000          |

| DMAPPS    | 0BF4  | _      | —      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      | PPST3   | PPST2  | PPST1  | PPST0  | 0000          |

| DMALCA    | 0BF6  | _      | _      | _      | _      | _      | _      | _     | _      | _     | _     | _     | _      |         | LSTCH  | 1<3:0> |        | 000F          |

| DSADRL    | 0BF8  |        |        |        |        |        |        |       | DSADR< | 15:0> |       |       |        |         |        |        |        | 0000          |

| DSADRH    | 0BFA  | _      | —      | —      | —      | —      | —      | —     | —      |       |       |       | DSADR• | <23:16> |        |        |        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2011-2013 Microchip Technology Inc.

| R/SO-0 <sup>(1</sup>         | ) R/W-0 <sup>(1)</sup>                     | R/W-0 <sup>(1)</sup>        | R/W-0                         | U-0                     | U-0                     | U-0                     | U-0                    |

|------------------------------|--------------------------------------------|-----------------------------|-------------------------------|-------------------------|-------------------------|-------------------------|------------------------|

| WR                           | WREN                                       | WRERR                       | NVMSIDL <sup>(2)</sup>        | _                       |                         | —                       |                        |

| bit 15                       | I                                          | 1                           | 1                             |                         |                         |                         | bit 8                  |

|                              |                                            |                             |                               |                         |                         |                         |                        |

| U-0                          | U-0                                        | U-0                         | U-0                           | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>   |

| _                            | —                                          | —                           | —                             | NVMOP3 <sup>(3,4)</sup> | NVMOP2 <sup>(3,4)</sup> | NVMOP1 <sup>(3,4)</sup> | NVMOP0 <sup>(3,4</sup> |

| bit 7                        |                                            |                             |                               |                         |                         |                         | bit (                  |

| lagandi                      |                                            | SO - Sottab                 | la Only hit                   |                         |                         |                         |                        |

| L <b>egend:</b><br>R = Reada | ble hit                                    | SO = Settab<br>W = Writable | -                             | II – I Inimplem         | nented bit, read        | ae 'O'                  |                        |

| -n = Value                   |                                            | '1' = Bit is se             |                               | '0' = Bit is clea       |                         | x = Bit is unkr         |                        |

|                              |                                            | 1 - Dit 13 30               |                               |                         |                         |                         | lowin                  |

| bit 15                       | WR: Write Co                               | ontrol bit(1)               |                               |                         |                         |                         |                        |

|                              |                                            |                             | ory program or                | erase operation         | on; the operatio        | n is self-timed         | and the bit is         |

|                              | cleared b                                  | y hardware o                | nce the operati               | on is complete          |                         |                         |                        |

|                              | -                                          |                             | ration is comple              | ete and inactive        | 9                       |                         |                        |

| bit 14                       | WREN: Write                                |                             | n/erase operati               | 000                     |                         |                         |                        |

|                              |                                            |                             | /erase operatio               |                         |                         |                         |                        |

| oit 13                       |                                            |                             | Error Flag bit <sup>(1)</sup> |                         |                         |                         |                        |

|                              | 1 = An impro                               | per program o               | r erase sequend               |                         | rmination has oc        | curred (bit is se       | t automatically        |

|                              |                                            | et attempt of th            | e WR bit)<br>operation com    | olotod pormally         |                         |                         |                        |

| bit 12                       |                                            |                             | le Control bit <sup>(2)</sup> | Sieteu normaliy         |                         |                         |                        |

|                              |                                            |                             | r goes into Star              | ndbv mode duri          | ina Idle mode           |                         |                        |

|                              |                                            |                             | r is active durin             |                         |                         |                         |                        |

| bit 11-4                     | Unimplemen                                 | ted: Read as                | '0'                           |                         |                         |                         |                        |

| bit 3-0                      | NVMOP<3:0>                                 | NVM Operation               | ation Select bits             | <sub>3</sub> (1,3,4)    |                         |                         |                        |

|                              | 1111 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1110 = Rese<br>1101 = Rese                 |                             |                               |                         |                         |                         |                        |

|                              | 1100 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1011 <b>= Rese</b>                         |                             |                               |                         |                         |                         |                        |

|                              | 1010 = Rese<br>0011 = Memo                 |                             | e operation                   |                         |                         |                         |                        |

|                              | 0010 = Rese                                | rved                        | -                             |                         |                         |                         |                        |

|                              |                                            |                             | ord program ope               | eration <sup>(5)</sup>  |                         |                         |                        |

|                              | 0000 <b>= Rese</b>                         | rvea                        |                               |                         |                         |                         |                        |

|                              | These bits can onl                         | -                           |                               |                         |                         |                         |                        |

|                              | If this bit is set, the (TVREG) before Fla |                             |                               |                         | d upon exiting lo       | dle mode, there         | is a delay             |

|                              | All other combinati                        |                             | •                             |                         |                         |                         |                        |

| <b>.</b> .                   |                                            |                             |                               | in ploinenteu.          |                         |                         |                        |

| 4:                           | Execution of the P                         | wrsav instruc               | tion is ianored               | while any of th         | e NVM operatio          | ns are in progr         | ess.                   |

## REGISTER 5-1: NVMCON: NONVOLATILE MEMORY (NVM) CONTROL REGISTER

## REGISTER 8-3: DMAXSTAH: DMA CHANNEL X START ADDRESS REGISTER A (HIGH)

| U-0            | U-0   | U-0            | U-0   | U-0          | U-0              | U-0    | U-0   |

|----------------|-------|----------------|-------|--------------|------------------|--------|-------|

| —              | _     | —              | —     | —            | —                | —      | —     |

| bit 15         |       |                |       |              |                  |        | bit 8 |

|                |       |                |       |              |                  |        |       |

| R/W-0          | R/W-0 | R/W-0          | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

|                |       |                | STA<  | 23:16>       |                  |        |       |

| bit 7          |       |                |       |              |                  |        | bit 0 |

|                |       |                |       |              |                  |        |       |

| Legend:        |       |                |       |              |                  |        |       |

| R = Readable b | oit   | W = Writable b | it    | U = Unimpler | mented bit, read | as '0' |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|-------------------|------------------|----------------------|--------------------|

|                   |                  |                      |                    |

## bit 15-8 Unimplemented: Read as '0'

bit 7-0 STA<23:16>: Primary Start Address bits (source or destination)

#### REGISTER 8-4: DMAXSTAL: DMA CHANNEL x START ADDRESS REGISTER A (LOW)

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | STA   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STA   | A<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimpler     | mented bit, rea | ad as '0'       |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unki | nown  |

bit 15-0 STA<15:0>: Primary Start Address bits (source or destination)

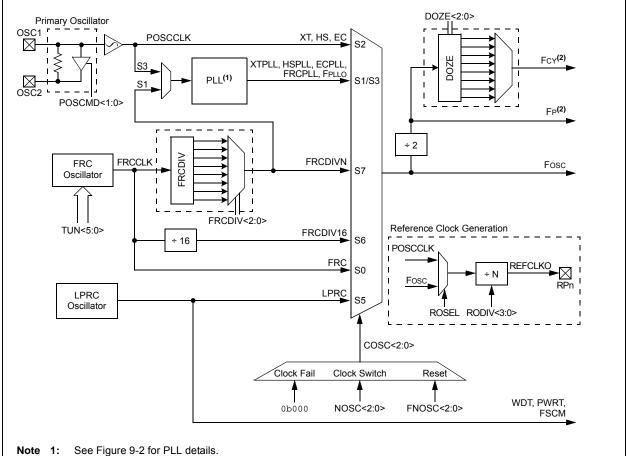

# 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/50X and PIC24EPXXXGP/MC20X families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Oscillator" (DS70580) in the "dsPIC33/ PIC24 Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X oscillator system provides:

- On-chip Phase-Locked Loop (PLL) to boost internal operating frequency on select internal and external oscillator sources

- On-the-fly clock switching between various clock sources

- · Doze mode for system power savings

- Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Configuration bits for clock source selection

- A simplified diagram of the oscillator system is shown in Figure 9-1.

## FIGURE 9-1: OSCILLATOR SYSTEM DIAGRAM

2: The term, FP, refers to the clock source for all peripherals, while FCY refers to the clock source for the CPU. Throughout this document, FCY and FP are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used with a doze ratio of 1:2 or lower.

## REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER (CONTINUED)

- **Note 1:** The DOZE<2:0> bits can only be written to when the DOZEN bit is clear. If DOZEN = 1, any writes to DOZE<2:0> are ignored.

- $\label{eq:constraint} \textbf{2:} \quad \text{This bit is cleared when the ROI bit is set and an interrupt occurs.}$

- **3:** The DOZEN bit cannot be set if DOZE<2:0> = 000. If DOZE<2:0> = 000, any attempt by user software to set the DOZEN bit is ignored.

| U-0    | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|--------|-------|-------|-------|------------|-------|-------|-------|

| —      | —     |       |       | —          | —     | —     | —     |

| bit 15 |       |       |       |            |       |       | bit 8 |

|        |       |       |       |            |       |       |       |

| U-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| —      |       |       |       | U1RXR<6:0> | >     |       |       |

| bit 7  |       |       |       |            |       |       | bit 0 |

|        |       |       |       |            |       |       |       |

#### REGISTER 11-10: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0' bit 6-0 U1RXR<6:0>: Assign UART1 Receive (U1RX) to the Corresponding RPn Pin bits (see Table 11-2 for input pin selection numbers) 1111001 = Input tied to RPI121 . . . . . . . . . .

#### REGISTER 11-11: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0     | U-0   | U-0   | U-0   | U-0        | U-0   | U-0   | U-0   |

|---------|-------|-------|-------|------------|-------|-------|-------|

| 0=0     | 0-0   | 0-0   | 0-0   | 0=0        | 0-0   | 0-0   | 0-0   |

| _       | —     |       | _     | _          | —     | —     | —     |

| bit 15  |       |       |       |            |       |       | bit 8 |

|         |       |       |       |            |       |       |       |

| U-0     | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |

| _       |       |       |       | U2RXR<6:0> | >     |       |       |

| bit 7   |       |       |       |            |       |       | bit 0 |

|         |       |       |       |            |       |       |       |

| Legend: |       |       |       |            |       |       |       |

|         |       |       |       |            |       |       |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-7 Unimplemented: Read as '0'

<sup>0000000 =</sup> Input tied to Vss

NOTES:

| R/W-1           | R/W-1           | R/W-0                                                                        | R/W-0                      | R/W-0                | R/W-0                           | R/W-0           | R/W-0        |

|-----------------|-----------------|------------------------------------------------------------------------------|----------------------------|----------------------|---------------------------------|-----------------|--------------|

| PENH            | PENL            | POLH                                                                         | POLL                       | PMOD1 <sup>(1)</sup> | PMOD0 <sup>(1)</sup>            | OVRENH          | OVRENL       |

| bit 15          |                 | •                                                                            |                            | •                    |                                 |                 | bit          |

| R/W-0           | R/W-0           | R/W-0                                                                        | R/W-0                      | R/W-0                | R/W-0                           | R/W-0           |              |

|                 | -               | -                                                                            |                            | -                    | -                               | -               | R/W-0        |

| OVRDAT1         | OVRDAT0         | FLTDAT1                                                                      | FLTDAT0                    | CLDAT1               | CLDAT0                          | SWAP            | OSYNC        |

| bit 7           |                 |                                                                              |                            |                      |                                 |                 | bit          |

| Legend:         |                 |                                                                              |                            |                      |                                 |                 |              |

| R = Readable    | bit             | W = Writable                                                                 | bit                        | U = Unimpler         | mented bit, read                | l as '0'        |              |

| -n = Value at I | POR             | '1' = Bit is set                                                             |                            | '0' = Bit is cle     | ared                            | x = Bit is unkr | nown         |

| bit 15          |                 | xH Output Pin                                                                | Ownershin hit              |                      |                                 |                 |              |

| bit 10          |                 | odule controls                                                               | •                          |                      |                                 |                 |              |

|                 |                 | dule controls P                                                              |                            |                      |                                 |                 |              |

| bit 14          | PENL: PWM       | L Output Pin                                                                 | Ownership bit              |                      |                                 |                 |              |

|                 |                 | odule controls                                                               |                            |                      |                                 |                 |              |

|                 | 0 = GPIO mo     | dule controls P                                                              | WMxL pin                   |                      |                                 |                 |              |

| bit 13          |                 | xH Output Pin                                                                | •                          |                      |                                 |                 |              |

|                 |                 | oin is active-lov<br>oin is active-hig                                       |                            |                      |                                 |                 |              |

| bit 12          | POLL: PWM       | kL Output Pin F                                                              | Polarity bit               |                      |                                 |                 |              |

|                 |                 | in is active-low<br>in is active-hig                                         |                            |                      |                                 |                 |              |

| bit 11-10       | PMOD<1:0>:      | PWMx # I/O F                                                                 | in Mode bits <sup>(1</sup> | )                    |                                 |                 |              |

|                 | 01 = PWMx I     | d; do not use<br>/O pin pair is in<br>/O pin pair is in<br>/O pin pair is in | the Redunda                | nt Output mod        | е                               |                 |              |

| bit 9           |                 | verride Enable                                                               | •                          |                      |                                 |                 |              |

|                 | 1 = OVRDAT      | <1> controls ou<br>enerator contro                                           | utput on PWM               | xH pin               |                                 |                 |              |

| bit 8           | OVRENL: Ov      | erride Enable                                                                | for PWMxL Pir              | n bit                |                                 |                 |              |

|                 | 1 = OVRDAT      | <0> controls ou                                                              | utput on PWM               | xL pin               |                                 |                 |              |

|                 | 0 = PWMx ge     | nerator contro                                                               | ls PWMxL pin               |                      |                                 |                 |              |

| bit 7-6         | OVRDAT<1:0      | D>: Data for PV                                                              | VMxH, PWMxI                | Pins if Overri       | ide is Enabled b                | oits            |              |

|                 |                 |                                                                              |                            |                      | d by OVRDAT<<br>by OVRDAT<0     |                 |              |

| bit 5-4         | FLTDAT<1:0      | >: Data for PW                                                               | MxH and PWN                | MxL Pins if FL       | rMOD is Enable                  | ed bits         |              |

|                 |                 |                                                                              |                            |                      | by FLTDAT<1><br>by FLTDAT<0>.   |                 |              |

| bit 3-2         | CLDAT<1:0>      | : Data for PWN                                                               | /IxH and PWM               | IxL Pins if CLM      | 10D is Enabled                  | bits            |              |

|                 |                 |                                                                              |                            | •                    | ecified by CLDA                 |                 |              |

|                 | ese bits should | -                                                                            |                            |                      | enabled (PTEN<br>le IOCONx regi | -               | written afte |

# REGISTER 16-13: IOCONx: PWMx I/O CONTROL REGISTER<sup>(2)</sup>

2: If the PWMLOCK Configuration bit (FOSCSEL<6>) is a '1', the IOCONx register can only be written after the unlock sequence has been executed.

| R/W-0                             | R/W-0                          | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |

|-----------------------------------|--------------------------------|-------|-------|------------------------------------|-------|--------------------|-------|

|                                   |                                |       | TRGC  | /IP<15:8>                          |       |                    |       |

| bit 15                            |                                |       |       |                                    |       |                    | bit 8 |

|                                   |                                |       |       |                                    |       |                    |       |

| R/W-0                             | R/W-0                          | R/W-0 | R/W-0 | R/W-0                              | R/W-0 | R/W-0              | R/W-0 |

|                                   |                                |       | TRGC  | MP<7:0>                            |       |                    |       |

| bit 7                             |                                |       |       |                                    |       |                    | bit 0 |

| Legend:                           |                                |       |       |                                    |       |                    |       |

| R = Readable bit W = Writable bit |                                |       | bit   | U = Unimplemented bit, read as '0' |       |                    |       |

| -n = Value at P                   | -n = Value at POR '1' = Bit is |       |       | '0' = Bit is cleared               |       | x = Bit is unknown |       |

## REGISTER 16-14: TRIGX: PWMx PRIMARY TRIGGER COMPARE VALUE REGISTER

bit 15-0 TRGCMP<15:0>: Trigger Control Value bits

When the primary PWMx functions in local time base, this register contains the compare values that can trigger the ADC module.

## REGISTER 21-16: CxRXFnSID: ECANx ACCEPTANCE FILTER n STANDARD IDENTIFIER REGISTER (n = 0-15)

| RW-x  R/W-x  R/W-x  R/W-x  R/W-x  R/W-x  R/W-x  R/W-x    SID10  SID9  SID8  SID7  SID6  SID5  SID4  SID3    bit 15  bit 15  bit 8  bit 8  bit 8  bit 8  bit 8    R/W-x  R/W-x  R/W-x  U-0  R/W-x  U-0  R/W-x  R/W-x    SID2  SID1  SID0  -  EXIDE  -  EID17  EID16    bit 7  bit 0  -  EXIDE  -  EID17  EID16    bit 7  bit 0  -  -  EXIDE  -  bit 0    Legend:    R = Readable bit  W = Writable bit  U = Unimplemented bit, read as '0'  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -  -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |                                                                                                                                                              |                                    |                     |                  |                  |                 |       |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------|------------------|------------------|-----------------|-------|--|--|--|

| bit 15 bit 2 bit 3 bit 8 bit 8 bit 8 bit 7 bit 7 bit 9 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 7 bit 0 bit 0 bit 0 bit 1 bit 9 bit 1 bit 9 bit 1 bit 1 bit 9 bit 1 | R/W-x         | R/W-x                                                                                                                                                        | R/W-x                              | R/W-x               | R/W-x            | R/W-x            | R/W-x           | R/W-x |  |  |  |

| R/W-x  R/W-x  U-0  R/W-x  U-0  R/W-x  R/W-x    SID2  SID1  SID0  -  EXIDE  -  EID17  EID16    bit 7  bit 0    Legend:    R = Readable bit  W = Writable bit  U = Unimplemented bit, read as '0'    -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-5  SID<10:>: Standard Identifier bits  1 = Message address bit, SIDx, must be '1' to match filter  0 = Message address bit, SIDx, must be '0' to match filter    bit 4  Unimplemented: Read as '0'  bit 3  EXIDE: Extended Identifier Enable bit    If MIDE = 1:  1 = Matches only messages with Extended Identifier addresses  0 = Matches only messages with Standard Identifier addresses    0 = Matches only messages with Standard Identifier addresses  Ignores EXIDE bit.  Ignores EXIDE bit.    bit 2  Unimplemented: Read as '0'  bit 1-0  EID  EID    bit 1-0  EID  Extended Identifier bits  1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SID10         | SID9                                                                                                                                                         | SID8                               | SID7                | SID6             | SID5             | SID4            | SID3  |  |  |  |

| SID2  SID1  SID0  —  EXIDE  —  EID17  EID16    bit 7  bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | bit 15        |                                                                                                                                                              |                                    |                     |                  |                  |                 | bit 8 |  |  |  |

| SID2  SID1  SID0  —  EXIDE  —  EID17  EID16    bit 7  bit 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |                                                                                                                                                              |                                    |                     |                  |                  |                 |       |  |  |  |

| bit 7  bit 0    Legend:  W = Writable bit  U = Unimplemented bit, read as '0'    -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-5  SID<10:0>: Standard Identifier bits  1 = Message address bit, SIDx, must be '1' to match filter  x = Bit is unknown    bit 15-5  SID<10:0>: Standard Identifier bits  1 = Message address bit, SIDx, must be '1' to match filter  x = Bit is unknown    bit 4  Unimplemented: Read as '0'  bit 3  EXIDE: Extended Identifier Enable bit  If MIDE = 1:    1 = Matches only messages with Extended Identifier addresses  0 = Matches only messages with Standard Identifier addresses    0 = Matches only messages with Standard Identifier addresses  If MIDE = 0:  Ignores EXIDE bit.    bit 2  Unimplemented: Read as '0'  bit 1-0  EID<17:16>: Extended Identifier bits    1 = Message address bit, EIDx, must be '1' to match filter  1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R/W-x         | R/W-x                                                                                                                                                        | R/W-x                              | U-0                 | R/W-x            | U-0              | R/W-x           | R/W-x |  |  |  |

| Legend:    R = Readable bit  W = Writable bit  U = Unimplemented bit, read as '0'    -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-5  SID<10:0>: Standard Identifier bits  1 = Message address bit, SIDx, must be '1' to match filter    0 = Message address bit, SIDx, must be '1' to match filter  0 = Message address bit, SIDx, must be '0' to match filter    bit 4  Unimplemented: Read as '0'    bit 3  EXIDE: Extended Identifier Enable bit    If MIDE = 1:  1 = Matches only messages with Extended Identifier addresses    0 = Matches only messages with Standard Identifier addresses    If MIDE = 0:  Ignores EXIDE bit.    bit 2  Unimplemented: Read as '0'    bit 1-0  EID<17:16>: Extended Identifier bits    1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SID2          | SID1                                                                                                                                                         | SID0                               | _                   | EXIDE            |                  | EID17           | EID16 |  |  |  |

| R = Readable bit  W = Writable bit  U = Unimplemented bit, read as '0'    -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-5  SID<10:0>: Standard Identifier bits  1 = Message address bit, SIDx, must be '1' to match filter    0 = Message address bit, SIDx, must be '1' to match filter  0 = Message address bit, SIDx, must be '0' to match filter    bit 4  Unimplemented: Read as '0'    bit 3  EXIDE: Extended Identifier Enable bit    If MIDE = 1:  1 = Matches only messages with Extended Identifier addresses    0 = Matches only messages with Standard Identifier addresses  0 = Matches only messages with Standard Identifier addresses    1f MIDE = 0:  Ignores EXIDE bit.    bit 2  Unimplemented: Read as '0'    bit 1-0  EID    1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 7         |                                                                                                                                                              |                                    |                     |                  |                  |                 | bit 0 |  |  |  |

| R = Readable bit  W = Writable bit  U = Unimplemented bit, read as '0'    -n = Value at POR  '1' = Bit is set  '0' = Bit is cleared  x = Bit is unknown    bit 15-5  SID<10:0>: Standard Identifier bits  1 = Message address bit, SIDx, must be '1' to match filter    0 = Message address bit, SIDx, must be '1' to match filter  0 = Message address bit, SIDx, must be '0' to match filter    bit 4  Unimplemented: Read as '0'    bit 3  EXIDE: Extended Identifier Enable bit    If MIDE = 1:  1 = Matches only messages with Extended Identifier addresses    0 = Matches only messages with Standard Identifier addresses  0 = Matches only messages with Standard Identifier addresses    1f MIDE = 0:  Ignores EXIDE bit.    bit 2  Unimplemented: Read as '0'    bit 1-0  EID    1 = Message address bit, EIDx, must be '1' to match filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |                                                                                                                                                              |                                    |                     |                  |                  |                 |       |  |  |  |