Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XEI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 60 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, QEI, SPI, UART/USART                             |

| Peripherals                | Brown-out Detect/Reset, DMA, Motor Control PWM, POR, PWM, WDT                    |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 64KB (22K x 24)                                                                  |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 4K x 16                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 16x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33ep64mc206t-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.6 CPU Resources

Many useful resources are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter |

|-------|--------------------------------------------------------------------------------------|

|       | this URL in your browser:                                                            |

|       | http://www.microchip.com/wwwproducts/                                                |

|       | Devices.aspx?dDocName=en555464                                                       |

## 3.6.1 KEY RESOURCES

- "CPU" (DS70359) in the "dsPIC33/PIC24 Family Reference Manual"

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related "dsPIC33/PIC24 Family Reference Manual" Sections

- Development Tools

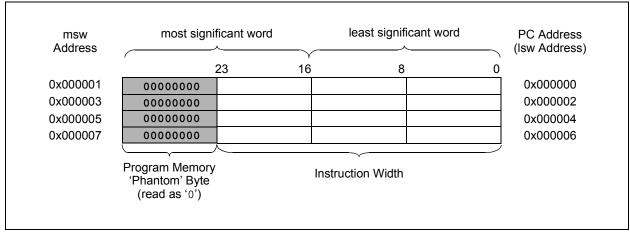

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

The program memory space is organized in wordaddressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-6).

Program memory addresses are always word-aligned on the lower word and addresses are incremented, or decremented by two, during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

# 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33EPXXXGP50X, dsPIC33EPXXXMC20X/ 50X and PIC24EPXXXGP/MC20X devices reserve the addresses between 0x000000 and 0x000200 for hardcoded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at address, 0x000000, of Flash memory, with the actual address for the start of code at address, 0x000002, of Flash memory.

A more detailed discussion of the Interrupt Vector Tables (IVTs) is provided in **Section 7.1** "Interrupt Vector Table".

#### FIGURE 4-6: PROGRAM MEMORY ORGANIZATION

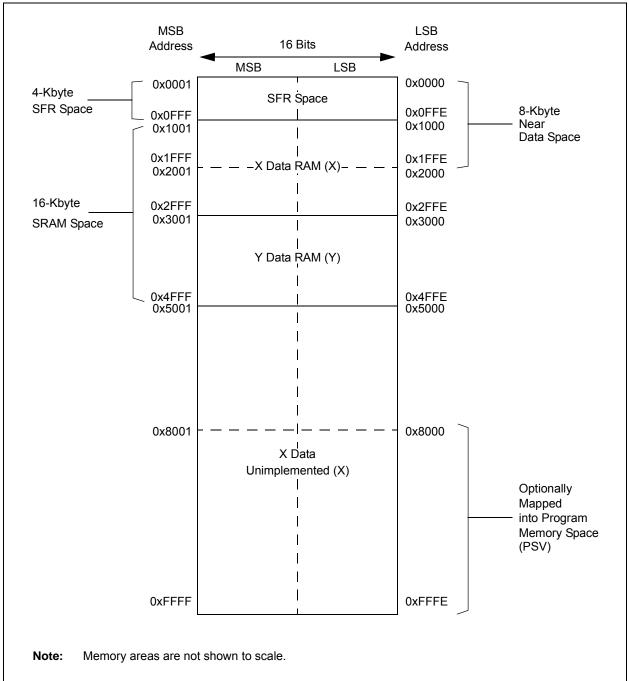

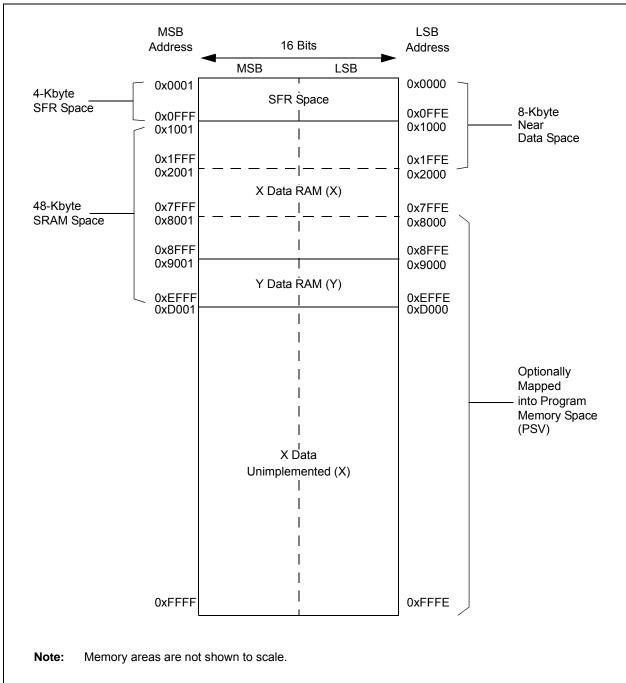

# FIGURE 4-9: DATA MEMORY MAP FOR dsPIC33EP128MC20X/50X AND dsPIC33EP128GP50X DEVICES

| Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment | Peripheral Pin<br>Select Input<br>Register Value | Input/<br>Output | Pin Assignment |

|--------------------------------------------------|------------------|----------------|--------------------------------------------------|------------------|----------------|

| 010 1000                                         | I/O              | RP40           | 101 0101                                         | —                | _              |

| 010 1001                                         | I/O              | RP41           | 101 0110                                         | —                | —              |

| 010 1010                                         | I/O              | RP42           | 101 0111                                         | —                | —              |

| 010 1011                                         | I/O              | RP43           | 101 1000                                         |                  | —              |

| 010 1100                                         | I                | RPI44          | 101 1001                                         |                  | —              |

| 101 1010                                         | —                | _              | 110 1101                                         | —                | _              |

| 101 1011                                         | —                | —              | 110 1110                                         |                  | —              |

| 101 1100                                         | —                | —              | 110 1111                                         |                  | —              |

| 101 1101                                         | —                | _              | 111 0000                                         | —                | _              |

| 101 1110                                         | 1                | RPI94          | 111 0001                                         |                  | _              |

| 101 1111                                         | I                | RP195          | 111 0010                                         |                  | —              |

| 110 0000                                         | I                | RPI96          | 111 0011                                         | —                | —              |

| 110 0001                                         | I/O              | RP97           | 111 0100                                         |                  | —              |

| 110 0010                                         | —                | —              | 111 0101                                         |                  | —              |

| 110 0011                                         | —                | —              | 111 0110                                         | I/O              | RP118          |

| 110 0100                                         | —                | —              | 111 0111                                         | Ι                | RPI119         |

| 110 0101                                         | —                | —              | 111 1000                                         | I/O              | RP120          |

| 110 0110                                         | _                |                | 111 1001                                         | Ι                | RPI121         |

| 110 0111                                         |                  |                | 111 1010                                         | —                |                |

| 110 1000                                         | —                | _              | 111 1011                                         | —                | _              |

| 110 1001                                         | —                |                | 111 1100                                         | —                |                |

| 110 1010                                         |                  |                | 111 1101                                         | —                |                |

| 110 1011                                         | —                | _              | 111 1110                                         | —                |                |

| 110 1100                                         | —                | _              | 111 1111                                         | _                |                |

### TABLE 11-2: INPUT PIN SELECTION FOR SELECTABLE INPUT SOURCES (CONTINUED)

Legend: Shaded rows indicate PPS Input register values that are unimplemented.

Note 1: See Section 11.4.4.1 "Virtual Connections" for more information on selecting this pin assignment.

2: These inputs are available on dsPIC33EPXXXGP/MC50X devices only.

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

|--------------|--------------|----------------------------------------------------------|---------------|-------------------|-----------------|-----------------|-------|

| —            |              |                                                          |               | IC4R<6:0>         |                 |                 |       |

| bit 15       |              |                                                          |               |                   |                 |                 | bit 8 |

|              |              |                                                          |               |                   |                 |                 |       |

| U-0          | R/W-0        | R/W-0                                                    | R/W-0         | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| —            |              |                                                          |               | IC3R<6:0>         |                 |                 |       |

| bit 7        |              |                                                          |               |                   |                 |                 | bit C |

|              |              |                                                          |               |                   |                 |                 |       |

| Legend:      |              |                                                          |               |                   |                 |                 |       |

| R = Readab   | ole bit      | W = Writable I                                           | bit           | U = Unimplem      | nented bit, rea | d as '0'        |       |

| -n = Value a | at POR       | '1' = Bit is set                                         |               | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              | 0000001 =    | nput tied to RPI<br>nput tied to CMI<br>nput tied to Vss | ⊃1            |                   |                 |                 |       |

| bit 7        | Unimpleme    | nted: Read as 'o                                         | )'            |                   |                 |                 |       |

| bit 6-0      | (see Table 1 | Assign Input Ca<br>1-2 for input pin<br>nput tied to RPI | selection nun |                   | onding RPn Pi   | n bits          |       |

## REGISTER 11-5: RPINR8: PERIPHERAL PIN SELECT INPUT REGISTER 8

### REGISTER 11-9: RPINR15: PERIPHERAL PIN SELECT INPUT REGISTER 15 (dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X DEVICES ONLY)

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0                | R/W-0           | R/W-0           | R/W-0  |

|--------------|--------------|--------------------------------------------------------|---------------|----------------------|-----------------|-----------------|--------|

| _            |              |                                                        |               | HOME1R<6:0           | >               |                 |        |

| bit 15       |              |                                                        |               |                      |                 |                 | bit 8  |

|              |              | <b>D</b> # 4 4 0                                       | 54446         | 5444.0               | 5444.0          |                 | 5444.6 |

| U-0          | R/W-0        | R/W-0                                                  | R/W-0         | R/W-0                | R/W-0           | R/W-0           | R/W-0  |

|              |              |                                                        |               | INDX1R<6:0>          | >               |                 |        |

| bit 7        |              |                                                        |               |                      |                 |                 | bit C  |

| Legend:      |              |                                                        |               |                      |                 |                 |        |

| R = Readab   | le bit       | W = Writable                                           | bit           | U = Unimplen         | nented bit, rea | ad as '0'       |        |

| -n = Value a | t POR        | '1' = Bit is set                                       |               | '0' = Bit is cleared |                 | x = Bit is unkr | nown   |

|              |              | nput tied to RPI                                       |               |                      |                 |                 |        |

|              |              | nput tied to CM<br>nput tied to Vss                    |               |                      |                 |                 |        |

| bit 7        |              | nted: Read as '                                        |               |                      |                 |                 |        |

| bit 6-0      | (see Table 1 | : Assign QEI1<br>1-2 for input pin<br>nput tied to RPI | selection nun | ,                    | responding RI   | Pn Pin bits     |        |

|              |              | nput tied to CM                                        |               |                      |                 |                 |        |

| U-0           | U-0                                                                              | R/W-0            | R/W-0 | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |

|---------------|----------------------------------------------------------------------------------|------------------|-------|-----------------------------------------|------------------|----------|-------|

| _             | —                                                                                |                  |       | RP39                                    | R<5:0>           |          |       |

| bit 15        |                                                                                  |                  |       |                                         |                  |          | bit 8 |

|               |                                                                                  |                  |       |                                         |                  |          |       |

| U-0           | U-0                                                                              | R/W-0            | R/W-0 | R/W-0                                   | R/W-0            | R/W-0    | R/W-0 |

| —             | —                                                                                |                  |       | RP38                                    | R<5:0>           |          |       |

| bit 7         |                                                                                  |                  |       |                                         |                  |          | bit 0 |

|               |                                                                                  |                  |       |                                         |                  |          |       |

| Legend:       |                                                                                  |                  |       |                                         |                  |          |       |

| R = Readable  | e bit                                                                            | W = Writable     | bit   | U = Unimplen                            | nented bit, read | d as '0' |       |

| -n = Value at | POR                                                                              | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                  |          |       |

|               |                                                                                  |                  |       |                                         |                  |          |       |

| bit 15-14     | Unimplemer                                                                       | nted: Read as '  | 0'    |                                         |                  |          |       |

| bit 13-8      | .     RP39R<5:0>: Peripheral Output Function is Assigned to RP39 Output Pin bits |                  |       |                                         |                  |          |       |

#### REGISTER 11-20: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2

|         | (see Table 11-3 for peripheral function numbers)                           |

|---------|----------------------------------------------------------------------------|

| bit 7-6 | Unimplemented: Read as '0'                                                 |

| bit 5-0 | RP38R<5:0>: Peripheral Output Function is Assigned to RP38 Output Pin bits |

|         | (see Table 11-3 for peripheral function numbers)                           |

#### REGISTER 11-21: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3

| U-0    | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|--------|-----|-------|------------|-------|-------|-------|-------|--|--|

| —      | —   |       | RP41R<5:0> |       |       |       |       |  |  |

| bit 15 |     |       |            |       |       |       |       |  |  |

| U-0   | U-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |

|-------|-----|-------|------------|-------|-------|-------|-------|--|--|

| —     | —   |       | RP40R<5:0> |       |       |       |       |  |  |

| bit 7 |     |       |            |       |       |       | bit 0 |  |  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-14 Unimplemented: Read as '0'

- bit 13-8 **RP41R<5:0>:** Peripheral Output Function is Assigned to RP41 Output Pin bits (see Table 11-3 for peripheral function numbers)

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 **RP40R<5:0>:** Peripheral Output Function is Assigned to RP40 Output Pin bits (see Table 11-3 for peripheral function numbers)

#### 16.1.2 WRITE-PROTECTED REGISTERS

On dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices, write protection is implemented for the IOCONx and FCLCONx registers. The write protection feature prevents any inadvertent writes to these registers. This protection feature can be controlled by the PWMLOCK Configuration bit (FOSCSEL<6>). The default state of the write protection feature is enabled (PWMLOCK = 1). The write protection feature can be disabled by configuring, PWMLOCK = 0. To gain write access to these locked registers, the user application must write two consecutive values of (0xABCD and 0x4321) to the PWMKEY register to perform the unlock operation. The write access to the IOCONx or FCLCONx registers must be the next SFR access following the unlock process. There can be no other SFR accesses during the unlock process and subsequent write access. To write to both the IOCONx and FCLCONx registers requires two unlock operations.

The correct unlocking sequence is described in Example 16-1.

#### EXAMPLE 16-1: PWMx WRITE-PROTECTED REGISTER UNLOCK SEQUENCE

|                                                                                                          | lled low externally in order to clear and disable the fault<br>egister requires unlock sequence                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0x0000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,FCLCON1</pre> | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of FCLCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to FCLCON1 register</pre> |

| -                                                                                                        | d polarity using the IOCON1 register<br>gister requires unlock sequence                                                                                                                                                                                                                           |

| <pre>mov #0xabcd,w10 mov #0x4321,w11 mov #0xF000,w0 mov w10, PWMKEY mov w11, PWMKEY mov w0,IOCON1</pre>  | <pre>; Load first unlock key to w10 register<br/>; Load second unlock key to w11 register<br/>; Load desired value of IOCON1 register in w0<br/>; Write first unlock key to PWMKEY register<br/>; Write second unlock key to PWMKEY register<br/>; Write desired value to IOCON1 register</pre>   |

# REGISTER 21-13: CxBUFPNT2: ECANx FILTER 4-7 BUFFER POINTER REGISTER 2

| R/W-0                              |       |                  |                                         |                                    |       |        |       |  |

|------------------------------------|-------|------------------|-----------------------------------------|------------------------------------|-------|--------|-------|--|

|                                    | R/W-0 | R/W-0            | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |  |

|                                    | F7BF  | P<3:0>           |                                         |                                    | F6BF  | P<3:0> |       |  |

| bit 15                             |       |                  |                                         |                                    |       |        | bit 8 |  |

| R/W-0                              | R/W-0 | R/W-0            | R/W-0                                   | R/W-0                              | R/W-0 | R/W-0  | R/W-0 |  |

|                                    | F5BF  | °<3:0>           |                                         | F4BP<3:0>                          |       |        |       |  |

| bit 7                              |       |                  |                                         |                                    |       |        | bit 0 |  |

| Legend:                            |       |                  |                                         |                                    |       |        |       |  |

| R = Readable bi                    | t     | W = Writable     | bit                                     | U = Unimplemented bit, read as '0' |       |        |       |  |

| -n = Value at POR '1' = Bit is set |       | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |                                    |       | nown   |       |  |

|          | 1110 = Filter hits received in RX Buffer 14                              |

|----------|--------------------------------------------------------------------------|

|          |                                                                          |

|          | •                                                                        |

|          | 0001 = Filter hits received in RX Buffer 1                               |

|          | 0000 = Filter hits received in RX Buffer 0                               |

| bit 11-8 | F6BP<3:0>: RX Buffer Mask for Filter 6 bits (same values as bits<15:12>) |

| bit 7-4  | F5BP<3:0>: RX Buffer Mask for Filter 5 bits (same values as bits<15:12>) |

| bit 3-0  | F4BP<3:0>: RX Buffer Mask for Filter 4 bits (same values as bits<15:12>) |

### REGISTER 21-14: CxBUFPNT3: ECANx FILTER 8-11 BUFFER POINTER REGISTER 3

| R/W-0         | R/W-0                                              | R/W-0                                                                                          | R/W-0                         | R/W-0                                  | R/W-0          | R/W-0   | R/W-0 |  |  |

|---------------|----------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------|----------------------------------------|----------------|---------|-------|--|--|

|               | F11BF                                              | P<3:0>                                                                                         |                               |                                        | F10B           | SP<3:0> |       |  |  |

| bit 15        |                                                    |                                                                                                |                               |                                        |                |         | bit 8 |  |  |

| R/W-0         | R/W-0                                              | R/W-0                                                                                          | R/W-0                         | R/W-0                                  | R/W-0          | R/W-0   | R/W-0 |  |  |

|               | F9BP                                               | <3:0>                                                                                          |                               |                                        | F8B            | P<3:0>  |       |  |  |

| bit 7         |                                                    |                                                                                                |                               |                                        |                |         | bit 0 |  |  |

| Legend:       |                                                    |                                                                                                |                               |                                        |                |         |       |  |  |

| R = Readabl   | R = Readable bit W = Writable bit                  |                                                                                                |                               | U = Unimplemented bit, read as '0'     |                |         |       |  |  |

| -n = Value at | t POR                                              | '1' = Bit is set                                                                               |                               | '0' = Bit is cleared x = Bit is unknow |                |         | nown  |  |  |

| bit 15-12     | 1111 = Filter<br>1110 = Filter<br>•<br>•<br>•<br>• | : RX Buffer Ma<br>hits received in<br>hits received in<br>hits received in<br>hits received in | n RX FIFO bu<br>n RX Buffer 1 | iffer<br>4                             |                |         |       |  |  |

| bit 11-8      | F10BP<3:0>                                         | : RX Buffer Ma                                                                                 | sk for Filter 1               | 0 bits (same val                       | ues as bits<1  | 5:12>)  |       |  |  |

| bit 7-4       | F9BP<3:0>:                                         | RX Buffer Mas                                                                                  | k for Filter 9 b              | oits (same value                       | s as bits<15:1 | 2>)     |       |  |  |

| bit 3-0       | F8BP<3:0>:                                         | RX Buffer Mas                                                                                  | k for Filter 8 k              | oits (same value                       | s as bits<15:1 | 2>)     |       |  |  |

|               |                                                    |                                                                                                |                               |                                        |                |         |       |  |  |

© 2011-2013 Microchip Technology Inc.

#### REGISTER 21-19: CxFMSKSEL2: ECANx FILTER 15-8 MASK SELECTION REGISTER 2

| R/W-0                                        | R/W-0                                                                                                                        | R/W-0                                                                                                                                            | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0 |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------|-------|

| F15N                                         | /SK<1:0>                                                                                                                     | F14MS                                                                                                                                            | K<1:0>                                                                                                                                               | F13MS                                                                                                                     | K<1:0>                                                                  | F12MSK<1:0>                  |       |

| bit 15                                       |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit 8 |

| R/W-0                                        | R/W-0                                                                                                                        | R/W-0                                                                                                                                            | R/W-0                                                                                                                                                | R/W-0                                                                                                                     | R/W-0                                                                   | R/W-0                        | R/W-0 |

|                                              | 1SK<1:0>                                                                                                                     | F10MS                                                                                                                                            |                                                                                                                                                      |                                                                                                                           | K<1:0>                                                                  |                              | <1:0> |

| bit 7                                        |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              | bit C |

|                                              |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |       |

| Legend:                                      |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |       |

| R = Readabl                                  | le bit                                                                                                                       | W = Writable                                                                                                                                     | bit                                                                                                                                                  | U = Unimplem                                                                                                              | nented bit, read                                                        | l as '0'                     |       |

| -n = Value at                                | t POR                                                                                                                        | '1' = Bit is set                                                                                                                                 |                                                                                                                                                      | '0' = Bit is cleared x = Bit                                                                                              |                                                                         |                              | nown  |

|                                              |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |       |

|                                              |                                                                                                                              |                                                                                                                                                  |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |       |

| bit 15-14                                    | F15MSK<1:                                                                                                                    | 0>: Mask Sourc                                                                                                                                   | e for Filter 15                                                                                                                                      | bits                                                                                                                      |                                                                         |                              |       |

| bit 15-14                                    | 11 = Reserv                                                                                                                  | ed                                                                                                                                               |                                                                                                                                                      |                                                                                                                           |                                                                         |                              |       |

| bit 15-14                                    | 11 = Reserv<br>10 = Accepta                                                                                                  | ed<br>ance Mask 2 reg                                                                                                                            | gisters contair                                                                                                                                      | n mask                                                                                                                    |                                                                         |                              |       |

| bit 15-14                                    | 11 = Reserv<br>10 = Accept<br>01 = Accept                                                                                    | ed                                                                                                                                               | gisters contair<br>gisters contair                                                                                                                   | n mask<br>n mask                                                                                                          |                                                                         |                              |       |

| bit 15-14<br>bit 13-12                       | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta                                                                  | red<br>ance Mask 2 reg<br>ance Mask 1 reg                                                                                                        | gisters contair<br>gisters contair<br>gisters contair                                                                                                | n mask<br>n mask<br>n mask                                                                                                | les as bits<15∷                                                         | 14>)                         |       |

|                                              | 11 = Reserv<br>10 = Accept<br>01 = Accept<br>00 = Accept<br>F14MSK<1:                                                        | red<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg                                                                                     | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14                                                                             | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu                                                                   |                                                                         |                              |       |

| bit 13-12                                    | 11 = Reserv<br>10 = Accept<br>01 = Accept<br>00 = Accept<br>F14MSK<1:<br>F13MSK<1:                                           | red<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Sourc                                                         | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13                                                          | n mask<br>n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu                                                | ies as bits<15:                                                         | 14>)                         |       |

| bit 13-12<br>bit 11-10                       | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:<br>F13MSK<1:<br>F12MSK<1:                           | red<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc                             | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12                                       | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu                                       | ies as bits<15:<br>ies as bits<15:                                      | 14>)<br>14>)                 |       |

| bit 13-12<br>bit 11-10<br>bit 9-8            | 11 = Reserv<br>10 = Accept<br>01 = Accept<br>00 = Accept<br>F14MSK<1:<br>F13MSK<1:<br>F12MSK<1:                              | red<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 12<br>e for Filter 11                    | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu                    | ies as bits<15:<br>ies as bits<15:<br>es as bits<15:′                   | 14>)<br>14>)<br>14>)         |       |

| bit 13-12<br>bit 11-10<br>bit 9-8<br>bit 7-6 | 11 = Reserv<br>10 = Accepta<br>01 = Accepta<br>00 = Accepta<br>F14MSK<1:<br>F13MSK<1:<br>F12MSK<1:<br>F11MSK<1:<br>F10MSK<1: | red<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc<br><b>0&gt;:</b> Mask Sourc | gisters contair<br>gisters contair<br>gisters contair<br>e for Filter 14<br>e for Filter 13<br>e for Filter 13<br>e for Filter 11<br>e for Filter 10 | n mask<br>n mask<br>n mask<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu<br>bits (same valu | ies as bits<15:<br>ies as bits<15:<br>es as bits<15:<br>ies as bits<15: | 14>)<br>14>)<br>14>)<br>14>) |       |

| oit 3-0 | Step<br>Command        | OPTION<3:0> | Option Description                                                                                             |

|---------|------------------------|-------------|----------------------------------------------------------------------------------------------------------------|

|         | PTGCTRL(1)             | 0000        | Reserved.                                                                                                      |

|         |                        | 0001        | Reserved.                                                                                                      |

|         |                        | 0010        | Disable Step Delay Timer (PTGSD).                                                                              |

|         |                        | 0011        | Reserved.                                                                                                      |

|         |                        | 0100        | Reserved.                                                                                                      |

|         |                        | 0101        | Reserved.                                                                                                      |

|         |                        | 0110        | Enable Step Delay Timer (PTGSD).                                                                               |

|         |                        | 0111        | Reserved.                                                                                                      |

|         |                        | 1000        | Start and wait for the PTG Timer0 to match the Timer0 Limit Register.                                          |

|         |                        | 1001        | Start and wait for the PTG Timer1 to match the Timer1 Limit Register.                                          |

|         |                        | 1010        | Reserved.                                                                                                      |

|         |                        | 1011        | Wait for the software trigger bit transition from low-to-high before continuing $(PTGSWT = 0 \text{ to } 1)$ . |

|         |                        | 1100        | Copy contents of the Counter 0 register to the AD1CHS0 register.                                               |

|         |                        | 1101        | Copy contents of the Counter 1 register to the AD1CHS0 register.                                               |

|         |                        | 1110        | Copy contents of the Literal 0 register to the AD1CHS0 register.                                               |

|         |                        | 1111        | Generate triggers indicated in the Broadcast Trigger Enable register (PTGBTE).                                 |

|         | PTGADD <sup>(1)</sup>  | 0000        | Add contents of the PTGADJ register to the Counter 0 Limit register (PTGC0LIM).                                |

|         |                        | 0001        | Add contents of the PTGADJ register to the Counter 1 Limit register (PTGC1LIM).                                |

|         |                        | 0010        | Add contents of the PTGADJ register to the Timer0 Limit register (PTGT0LIM).                                   |

|         |                        | 0011        | Add contents of the PTGADJ register to the Timer1 Limit register (PTGT1LIM).                                   |

|         |                        | 0100        | Add contents of the PTGADJ register to the Step Delay Limit register (PTGSDLIM)                                |

|         |                        | 0101        | Add contents of the PTGADJ register to the Literal 0 register (PTGL0).                                         |

|         |                        | 0110        | Reserved.                                                                                                      |

|         |                        | 0111        | Reserved.                                                                                                      |

|         | PTGCOPY <sup>(1)</sup> | 1000        | Copy contents of the PTGHOLD register to the Counter 0 Limit register (PTGC0LIM).                              |

|         |                        | 1001        | Copy contents of the PTGHOLD register to the Counter 1 Limit register (PTGC1LIM).                              |

|         |                        | 1010        | Copy contents of the PTGHOLD register to the Timer0 Limit register (PTGT0LIM).                                 |

|         |                        | 1011        | Copy contents of the PTGHOLD register to the Timer1 Limit register (PTGT1LIM).                                 |

|         |                        | 1100        | Copy contents of the PTGHOLD register to the Step Delay Limit register (PTGSDLIM).                             |

|         |                        | 1101        | Copy contents of the PTGHOLD register to the Literal 0 register (PTGL0).                                       |

|         |                        | 1110        | Reserved.                                                                                                      |

|         |                        | 1111        | Reserved.                                                                                                      |

## TABLE 24-1: PTG STEP COMMAND FORMAT (CONTINUED)

Note 1: All reserved commands or options will execute but have no effect (i.e., execute as a NOP instruction).

2: Refer to Table 24-2 for the trigger output descriptions.

3: This feature is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

| File<br>Name | Address           | Device<br>Memory<br>Size<br>(Kbytes) | Bits 23-8 | Bit 7                   | Bit 6                  | Bit 5    | Bit 4                   | Bit 3                   | Bit 2                   | Bit 1     | Bit 0  |   |  |  |  |

|--------------|-------------------|--------------------------------------|-----------|-------------------------|------------------------|----------|-------------------------|-------------------------|-------------------------|-----------|--------|---|--|--|--|

| Reserved     | 0057EC            | 32                                   |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 00AFEC            | 64                                   |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0157EC            | 128                                  | _         | _                       | —                      | _        | _                       | _                       | _                       | _         | _      |   |  |  |  |

|              | 02AFEC            | 256                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0557EC            | 512                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

| Reserved     | 0057EE            | 32                                   |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 00AFEE            | 64                                   |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0157EE            | 128                                  |           | _                       | _                      | _        | _                       | _                       | _                       | _         | _      |   |  |  |  |

|              | 02AFEE            | 256                                  | -         |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0557EE            | 512                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

| FICD         | 0057F0            | 32                                   |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

| TIOD         | 00AFF0            | 64                                   | -         |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0157F0            | 128                                  | -         | Reserved <sup>(3)</sup> |                        | JTAGEN   | Reserved <sup>(2)</sup> | Reserved <sup>(3)</sup> |                         | ICS<      | 1.0>   |   |  |  |  |

|              | 01371 0<br>02AFF0 | 256                                  | _         | Reserveu.               | _                      | JIAGEN   | Keselveu.               | Keselveu.               | _                       | 1034      | 1.0~   |   |  |  |  |

|              | 02AFF0<br>0557F0  | 512                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

| 5000         |                   |                                      |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

| FPOR         | 0057F2            | 32                                   |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 00AFF2            | 64                                   | -         |                         |                        |          |                         | - ·(3)                  |                         |           |        |   |  |  |  |

|              | 0157F2            | 128                                  | —         | —                       | WDTV                   | VIN<1:0> | ALTI2C2                 | ALTI2C1                 | Reserved <sup>(3)</sup> | —         | —      | _ |  |  |  |

|              | 02AFF2            | 256                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0557F2            | 512                                  |           |                         | 1                      |          |                         |                         |                         |           |        |   |  |  |  |

| FWDT         | 0057F4            | 32                                   | -         |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 00AFF4            | 64                                   |           |                         |                        |          |                         |                         | WDTPOST<3:0>            |           |        |   |  |  |  |

|              | 0157F4            | 128                                  | —         | FWDTEN                  | WINDIS                 | PLLKEN   | WDTPRE                  |                         |                         |           |        |   |  |  |  |

|              | 02AFF4            | 256                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0557F4            | 512                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

| FOSC         | 0057F6            | 32                                   |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 00AFF6            | 64                                   |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0157F6            | 128                                  | _         | FCKS                    | SM<1:0>                | IOL1WAY  | _                       | _                       | OSCIOFNC                | POSCM     | D<1:0> |   |  |  |  |

|              | 02AFF6            | 256                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0557F6            | 512                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

| FOSCSEL      | 0057F8            | 32                                   |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 00AFF8            | 64                                   |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0157F8            | 128                                  | _         | IESO                    | PWMLOCK <sup>(1)</sup> | _        | _                       | _                       | F                       | NOSC<2:0> |        |   |  |  |  |

|              | 02AFF8            | 256                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0557F8            | 512                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

| FGS          | 0057FA            | 32                                   |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 00AFFA            | 64                                   |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0157FA            | 128                                  |           | _                       | _                      | _        | _                       | _                       | _                       | GCP       | GWRP   |   |  |  |  |

|              | 02AFFA            | 256                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0557FA            | 512                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

| Reserved     | 0057FC            | 312                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

| 1 10301 1000 | 0037FC            | 64                                   |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              |                   |                                      |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0157FC<br>02AFFC  | 128                                  |           | _                       |                        | _        | _                       | _                       | _                       | _         | _      |   |  |  |  |

|              |                   | 256                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0557FC            | 512                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

| Reserved     | 057FFE            | 32                                   |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 00AFFE            | 64                                   |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0157FE            | 128                                  | —         | —                       | —                      | —        | —                       | —                       | —                       | —         | —      |   |  |  |  |

|              | 02AFFE            | 256                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

|              | 0557FE            | 512                                  |           |                         |                        |          |                         |                         |                         |           |        |   |  |  |  |

#### TABLE 27-1: CONFIGURATION BYTE REGISTER MAP

Legend: — = unimplemented, read as '1'.

Note 1: This bit is only available on dsPIC33EPXXXMC20X/50X and PIC24EPXXXMC20X devices.

**2:** This bit is reserved and must be programmed as '0'.

3: These bits are reserved and must be programmed as '1'.

# TABLE 30-40:SPI2 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| АС СНА |                       | Standard Op<br>(unless othe<br>Operating te  | erwise st    | <b>ated)</b><br>e -40° | C ≤ TA ≤ | <b>V to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |                                |

|--------|-----------------------|----------------------------------------------|--------------|------------------------|----------|-----------------------------------------------------------------|--------------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                | Min.         | Typ. <sup>(2)</sup>    | Max.     | Units                                                           | Conditions                     |

| SP70   | FscP                  | Maximum SCK2 Input Frequency                 | —            | —                      | 11       | MHz                                                             | (Note 3)                       |

| SP72   | TscF                  | SCK2 Input Fall Time                         | —            | —                      | _        | ns                                                              | See Parameter DO32 (Note 4)    |

| SP73   | TscR                  | SCK2 Input Rise Time                         | —            | —                      | _        | ns                                                              | See Parameter DO31 (Note 4)    |

| SP30   | TdoF                  | SDO2 Data Output Fall Time                   | —            | _                      | _        | ns                                                              | See Parameter DO31<br>(Note 4) |

| SP31   | TdoR                  | SDO2 Data Output Rise Time                   | —            | _                      | _        | ns                                                              | See Parameter DO31 (Note 4)    |

| SP35   | TscH2doV,<br>TscL2doV | SDO2 Data Output Valid after<br>SCK2 Edge    | —            | 6                      | 20       | ns                                                              |                                |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO2 Data Output Setup to<br>First SCK2 Edge | 30           | —                      | _        | ns                                                              |                                |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI2 Data Input to SCK2 Edge   | 30           | —                      | _        | ns                                                              |                                |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI2 Data Input to SCK2 Edge    | 30           | —                      | _        | ns                                                              |                                |

| SP50   | TssL2scH,<br>TssL2scL | SS2 ↓ to SCK2 ↑ or SCK2 ↓<br>Input           | 120          | —                      | _        | ns                                                              |                                |

| SP51   | TssH2doZ              | SS2 ↑ to SDO2 Output<br>High-Impedance       | 10           | —                      | 50       | ns                                                              | (Note 4)                       |

| SP52   | TscH2ssH<br>TscL2ssH  | SS2 ↑ after SCK2 Edge                        | 1.5 TCY + 40 | —                      |          | ns                                                              | (Note 4)                       |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK2 is 91 ns. Therefore, the SCK2 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI2 pins.

# TABLE 30-47:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 1, SMP = 0)TIMING REQUIREMENTS

| АС СНА |                       | Standard Op<br>(unless othe<br>Operating te  | erwise st    | <b>ated)</b><br>e -40° | C ≤ TA ≤ | <b>V to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |                             |

|--------|-----------------------|----------------------------------------------|--------------|------------------------|----------|-----------------------------------------------------------------|-----------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                | Min.         | Typ. <sup>(2)</sup>    | Max.     | Units                                                           | Conditions                  |

| SP70   | FscP                  | Maximum SCK1 Input Frequency                 | —            | —                      | 15       | MHz                                                             | (Note 3)                    |

| SP72   | TscF                  | SCK1 Input Fall Time                         | —            | —                      | _        | ns                                                              | See Parameter DO32 (Note 4) |

| SP73   | TscR                  | SCK1 Input Rise Time                         | —            | —                      | _        | ns                                                              | See Parameter DO31 (Note 4) |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                   | —            | _                      | _        | ns                                                              | See Parameter DO32 (Note 4) |

| SP31   | TdoR                  | SDO1 Data Output Rise Time                   | —            | —                      | _        | ns                                                              | See Parameter DO31 (Note 4) |

| SP35   | TscH2doV,<br>TscL2doV | SDO1 Data Output Valid after<br>SCK1 Edge    | —            | 6                      | 20       | ns                                                              |                             |

| SP36   | TdoV2scH,<br>TdoV2scL | SDO1 Data Output Setup to<br>First SCK1 Edge | 30           | —                      | _        | ns                                                              |                             |

| SP40   | TdiV2scH,<br>TdiV2scL | Setup Time of SDI1 Data Input to SCK1 Edge   | 30           | —                      | _        | ns                                                              |                             |

| SP41   | TscH2diL,<br>TscL2diL | Hold Time of SDI1 Data Input to SCK1 Edge    | 30           | —                      | _        | ns                                                              |                             |

| SP50   | TssL2scH,<br>TssL2scL | SS1 ↓ to SCK1 ↑ or SCK1 ↓<br>Input           | 120          | —                      | _        | ns                                                              |                             |

| SP51   | TssH2doZ              | SS1 ↑ to SDO1 Output<br>High-Impedance       | 10           | —                      | 50       | ns                                                              | (Note 4)                    |

| SP52   | TscH2ssH,<br>TscL2ssH | SS1                                          | 1.5 Tcy + 40 | —                      |          | ns                                                              | (Note 4)                    |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated.

**3:** The minimum clock period for SCK1 is 66.7 ns. Therefore, the SCK1 clock generated by the master must not violate this specification.

4: Assumes 50 pF load on all SPI1 pins.

# TABLE 30-48:SPI1 SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0)TIMING REQUIREMENTS

| АС СНА |                       | Standard Op<br>(unless othe<br>Operating ter | erwise st    | <b>ated)</b><br>e -40° | C ≤ TA ≤ | <b>V to 3.6V</b><br>+85°C for Industrial<br>+125°C for Extended |                             |

|--------|-----------------------|----------------------------------------------|--------------|------------------------|----------|-----------------------------------------------------------------|-----------------------------|

| Param. | Symbol                | Characteristic <sup>(1)</sup>                | Min.         | Typ. <sup>(2)</sup>    | Max.     | Units                                                           | Conditions                  |

| SP70   | FscP                  | Maximum SCK1 Input Frequency                 | —            |                        | 11       | MHz                                                             | (Note 3)                    |

| SP72   | TscF                  | SCK1 Input Fall Time                         | —            | —                      | _        | ns                                                              | See Parameter DO32 (Note 4) |

| SP73   | TscR                  | SCK1 Input Rise Time                         | —            | —                      | _        | ns                                                              | See Parameter DO31 (Note 4) |

| SP30   | TdoF                  | SDO1 Data Output Fall Time                   | —            | _                      | _        | ns                                                              | See Parameter DO32 (Note 4) |